#

### NXP USA Inc. - MC9S12XS128CAE Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                 |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 40MHz                                                                  |

| Connectivity               | CANbus, SCI, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 44                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                |                                                                        |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                           |

| Data Converters            | A/D 8x12b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12xs128cae |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2.3.18 PM[7:6] — Port M I/O Pins 7-6

PM[7:6] are a general-purpose input or output pins.

### 1.2.3.19 PM5 / SCK0 — Port M I/O Pin 5

PM5 is a general-purpose input or output pin. It can be configured as the serial clock pin SCK of the serial peripheral interface 0 (SPI0).

## 1.2.3.20 PM4 / MOSI0 — Port M I/O Pin 4

PM4 is a general-purpose input or output pin. It can be configured as the master output (during master mode) or slave input pin (during slave mode) MOSI for the serial peripheral interface 0 (SPI0).

## 1.2.3.21 PM3 / SSO — Port M I/O Pin 3

PM3 is a general-purpose input or output pin. It can be configured as the slave select pin  $\overline{SS}$  of the serial peripheral interface 0 (SPI0).

## 1.2.3.22 PM2 / MISO0 — Port M I/O Pin 2

PM2 is a general-purpose input or output pin. It can be configured as the master input (during master mode) or slave output pin (during slave mode) MISO for the serial peripheral interface 0 (SPI0).

## 1.2.3.23 PM1 / TXCAN0 / TXD1 — Port M I/O Pin 1

PM1 is a general-purpose input or output pin. It can be configured as the transmit pin TXCAN of the scalable controller area network controller 0 (CAN0). It can be configured as the transmit pin TXD of serial communication interface 1 (SCI1).

## 1.2.3.24 PM0 / RXCAN0 / RXD1 — Port M I/O Pin 0

PM0 is a general-purpose input or output pin. It can be configured as the receive pin RXCAN of the scalable controller area network controller 0 (CAN0). It can be configured as the receive pin RXD of serial communication interface 1 (SCI1).

## 1.2.3.25 PP7 / KWP7 / PWM7 — Port P I/O Pin 7

PP7 is a general-purpose input or output pin. It can be configured as keypad wakeup input. It can be configured as pulse width modulator (PWM) channel 7 output or emergency shutdown input.

## 1.2.3.26 PP[6:3] / KWP[6:3] / PWM[6:3] — Port P I/O Pins 6-3

PP[6:3] are a general-purpose input or output pins. They can be configured as keypad wakeup inputs. They can be configured as pulse width modulator (PWM) channel 6-3 output.

### Table 2-22. PTTRR Register Field Descriptions

| Field      | Description                                                                        |

|------------|------------------------------------------------------------------------------------|

| 7<br>PTTRR | Port T peripheral routing—<br>This register controls the routing of PWM channel 7. |

|            | 1 PWM7 routed to PT7<br>0 PWM7 routed to PP7                                       |

| 6<br>PTTRR | Port T peripheral routing—<br>This register controls the routing of PWM channel 6. |

|            | 1 PWM6 routed to PT6<br>0 PWM6 routed to PP6                                       |

| 5<br>PTTRR | Port T peripheral routing—<br>This register controls the routing of PWM channel 5. |

|            | 1 PWM5 routed to PT5<br>0 PWM5 routed to PP5                                       |

| 4<br>PTTRR | Port T peripheral routing—<br>This register controls the routing of PWM channel 4. |

|            | 1 PWM4 routed to PT4<br>0 PWM4 routed to PP4                                       |

| 2<br>PTTRR | Port T peripheral routing—<br>This register controls the routing of TIM channel 2. |

|            | 1 IOC2 routed to PP2<br>0 IOC2 routed to PT2                                       |

| 1<br>PTTRR | Port T peripheral routing—<br>This register controls the routing of TIM channel 1. |

|            | 1 IOC1 routed to PP1<br>0 IOC1 routed to PT1                                       |

| 0<br>PTTRR | Port T peripheral routing—<br>This register controls the routing of TIM channel 0. |

|            | 1 IOC0 routed to PP0<br>0 IOC0 routed to PT0                                       |

# Chapter 8 S12XE Clocks and Reset Generator (S12XECRGV1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected           | Description of Changes                                                                                                                           |  |  |  |

|--------------------|------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V01.00             | 26 Oct. 2005     |                                | Initial release                                                                                                                                  |  |  |  |

| V01.01             | 02 Nov 2006      | 8.4.1.1/8-254                  | Table "Examples of IPLL Divider settings": corrected \$32 to \$31                                                                                |  |  |  |

| V01.02             | 4 Mar. 2008      | 8.4.1.4/8-257<br>8.4.3.3/8-261 | Corrected details                                                                                                                                |  |  |  |

| V01.03             | 1 Sep. 2008      | Table 8-14                     | added 100MHz example for PLL                                                                                                                     |  |  |  |

| V01.04             | 20 Nov. 2008     | 8.3.2.4/8-243                  | S12XECRG Flags Register: corrected address to Module Base + 0x0003                                                                               |  |  |  |

| V01.05             | 19. Sep 2009     | 8.5.1/8-263                    | Modified Note below Table 8-17./8-263                                                                                                            |  |  |  |

| V01.06             | 18. Sep 2012     | Table 8-14<br>8.5.1            | Added footnote concerning maximum clock frequencies to table<br>Removed redundant examples from table<br>Replaced reference to MMC documentation |  |  |  |

Table 8-1. Revision History

# 8.1 Introduction

This specification describes the function of the Clocks and Reset Generator (S12XECRG).

## 8.1.1 Features

The main features of this block are:

- Phase Locked Loop (IPLL) frequency multiplier with internal filter

- Reference divider

- Post divider

- Configurable internal filter (no external pin)

- Optional frequency modulation for defined jitter and reduced emission

- Automatic frequency lock detector

- Interrupt request on entry or exit from locked condition

- Self Clock Mode in absence of reference clock

- System Clock Generator

- Clock Quality Check

- User selectable fast wake-up from Stop in Self-Clock Mode for power saving and immediate program execution

- Clock switch for either Oscillator or PLL based system clocks

- Computer Operating Properly (COP) watchdog timer with time-out clear window.

### S12XS Family Reference Manual, Rev. 1.13

# **10.2 Signal Description**

This section lists all inputs to the ADC12B16C block.

## **10.2.1** Detailed Signal Descriptions

## 10.2.1.1 ANx (x = 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0)

This pin serves as the analog input Channel *x*. It can also be configured as digital port or external trigger for the ATD conversion.

## 10.2.1.2 ETRIG3, ETRIG2, ETRIG1, ETRIG0

These inputs can be configured to serve as an external trigger for the ATD conversion.

Refer to device specification for availability and connection of these inputs!

# 10.2.1.3 V<sub>RH</sub>, V<sub>RL</sub>

$V_{RH}$  is the high reference voltage,  $V_{RL}$  is the low reference voltage for ATD conversion.

## 10.2.1.4 V<sub>DDA</sub>, V<sub>SSA</sub>

These pins are the power supplies for the analog circuitry of the ADC12B16C block.

# **10.3** Memory Map and Register Definition

This section provides a detailed description of all registers accessible in the ADC12B16C.

## 10.3.1 Module Memory Map

Figure 10-3 gives an overview on all ADC12B16C registers.

### NOTE

Register Address = Base Address + Address Offset, where the Base Address is defined at the MCU level and the Address Offset is defined at the module level.

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1<br>OVRIF              | Overrun Interrupt Flag — This flag is set when a data overrun condition occurs. If not masked, an error interrupt is pending while this flag is set.         0       No data overrun condition         1       A data overrun detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 0<br>RXF <sup>(2)</sup> | Receive Buffer Full Flag — RXF is set by the MSCAN when a new message is shifted in the receiver FIFO.         This flag indicates whether the shifted buffer is loaded with a correctly received message (matching identifier, matching cyclic redundancy code (CRC) and no other errors detected). After the CPU has read that message from the RxFG buffer in the receiver FIFO, the RXF flag must be cleared to release the buffer. A set RXF flag prohibits the shifting of the next FIFO entry into the foreground buffer (RxFG). If not masked, a receive interrupt is pending while this flag is set.         0       No new message available within the RxFG         1       The receiver FIFO is not empty. A new message is available in the RxFG |  |  |  |  |

#### Table 11-11. CANRFLG Register Field Descriptions (continued)

Redundant Information for the most critical CAN bus status which is "bus-off". This only occurs if the Tx error counter exceeds a number of 255 errors. Bus-off affects the receiver state. As soon as the transmitter leaves its bus-off state the receiver state skips to RxOK too. Refer also to TSTAT[1:0] coding in this register.

2. To ensure data integrity, do not read the receive buffer registers while the RXF flag is cleared. For MCUs with dual CPUs, reading the receive buffer registers while the RXF flag is cleared may result in a CPU fault condition.

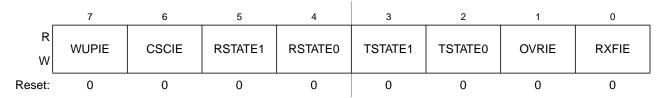

### 11.3.2.6 MSCAN Receiver Interrupt Enable Register (CANRIER)

This register contains the interrupt enable bits for the interrupt flags described in the CANRFLG register.

Module Base + 0x0005

Access: User read/write<sup>(1)</sup>

#### Figure 11-9. MSCAN Receiver Interrupt Enable Register (CANRIER)

1. Read: Anytime

Write: Anytime when not in initialization mode

#### NOTE

The CANRIER register is held in the reset state when the initialization mode is active (INITRQ=1 and INITAK=1). This register is writable when not in initialization mode (INITRQ=0 and INITAK=0).

The RSTATE[1:0], TSTATE[1:0] bits are not affected by initialization mode.

#### Freescale's Scalable Controller Area Network (S12MSCANV3)

1. Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

### Table 11-25. CANIDMR4–CANIDMR7 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AM[7:0] | <ul> <li>Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.</li> <li>Match corresponding acceptance code register and identifier bits</li> <li>Ignore corresponding acceptance code register bit</li> </ul> |

## 11.3.3 Programmer's Model of Message Storage

The following section details the organization of the receive and transmit message buffers and the associated control registers.

To simplify the programmer interface, the receive and transmit message buffers have the same outline. Each message buffer allocates 16 bytes in the memory map containing a 13 byte data structure.

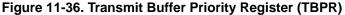

An additional transmit buffer priority register (TBPR) is defined for the transmit buffers. Within the last two bytes of this memory map, the MSCAN stores a special 16-bit time stamp, which is sampled from an internal timer after successful transmission or reception of a message. This feature is only available for transmit and receiver buffers, if the TIME bit is set (see Section 11.3.2.1, "MSCAN Control Register 0 (CANCTL0)").

The time stamp register is written by the MSCAN. The CPU can only read these registers.

• The transmission buffer with the lowest local priority field wins the prioritization.

In cases of more than one buffer having the same lowest priority, the message buffer with the lower index number wins.

Access: User read/write<sup>(1)</sup> Module Base + 0x00XD 7 6 5 4 3 2 1 0 R PRIO7 PRIO6 PRIO4 PRIO3 PRIO2 PRIO1 PRIO0 PRIO5 W 0 0 0 0 Reset: 0 0 0 0

Read: Anytime when TXEx flag is set (see Section 11.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 11.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

Write: Anytime when TXEx flag is set (see Section 11.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 11.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

## 11.3.3.5 Time Stamp Register (TSRH–TSRL)

If the TIME bit is enabled, the MSCAN will write a time stamp to the respective registers in the active transmit or receive buffer right after the EOF of a valid message on the CAN bus (see Section 11.3.2.1, "MSCAN Control Register 0 (CANCTL0)"). In case of a transmission, the CPU can only read the time stamp after the respective transmit buffer has been flagged empty.

The timer value, which is used for stamping, is taken from a free running internal CAN bit clock. A timer overrun is not indicated by the MSCAN. The timer is reset (all bits set to 0) during initialization mode. The CPU can only read the time stamp registers.

Module Base + 0x00XE

Access: User read/write<sup>(1)</sup>

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|--------|-------|-------|-------|-------|-------|-------|------|------|

| R      | TSR15 | TSR14 | TSR13 | TSR12 | TSR11 | TSR10 | TSR9 | TSR8 |

| w      |       |       |       |       |       |       |      |      |

| Reset: | х     | х     | х     | х     | х     | х     | х    | Х    |

Figure 11-37. Time Stamp Register — High Byte (TSRH)

Read: Anytime when TXEx flag is set (see Section 11.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 11.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

Write: Unimplemented

# Chapter 13 Pulse-Width Modulator (S12PWM8B8CV1)

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                                                               |

|-------------------|------------------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| 01.17             |                  | 08-01-2004        |        | Added clarification of PWMIF operation in STOP and WAIT mode.<br>Added notes on minimum pulse width of emergency shutdown<br>signal. |

# 13.1 Introduction

The PWM definition is based on the HC12 PWM definitions. It contains the basic features from the HC11 with some of the enhancements incorporated on the HC12: center aligned output mode and four available clock sources. The PWM module has eight channels with independent control of left and center aligned outputs on each channel.

Each of the eight channels has a programmable period and duty cycle as well as a dedicated counter. A flexible clock select scheme allows a total of four different clock sources to be used with the counters. Each of the modulators can create independent continuous waveforms with software-selectable duty rates from 0% to 100%. The PWM outputs can be programmed as left aligned outputs or center aligned outputs.

# 13.1.1 Features

The PWM block includes these distinctive features:

- Eight independent PWM channels with programmable period and duty cycle

- Dedicated counter for each PWM channel

- Programmable PWM enable/disable for each channel

- Software selection of PWM duty pulse polarity for each channel

- Period and duty cycle are double buffered. Change takes effect when the end of the effective period is reached (PWM counter reaches zero) or when the channel is disabled.

- Programmable center or left aligned outputs on individual channels

- Eight 8-bit channel or four 16-bit channel PWM resolution

- Four clock sources (A, B, SA, and SB) provide for a wide range of frequencies

- Programmable clock select logic

- Emergency shutdown

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3<br>OR | <ul> <li>Overrun Flag — OR is set when software fails to read the SCI data register before the receive shift register receives the next frame. The OR bit is set immediately after the stop bit has been completely received for the second frame. The data in the shift register is lost, but the data already in the SCI data registers is not affected. Clear OR by reading SCI status register 1 (SCISR1) with OR set and then reading SCI data register low (SCIDRL).</li> <li>0 No overrun</li> <li>1 Overrun</li> <li>Note: OR flag may read back as set when RDRF flag is clear. This may happen if the following sequence of events occurs:</li> </ul>    |  |  |  |  |

|         | <ol> <li>After the first frame is received, read status register SCISR1 (returns RDRF set and OR flag clear);</li> <li>Receive second frame without reading the first frame in the data register (the second frame is not received and OR flag is set);</li> <li>Read data register SCIDRL (returns first frame and clears RDRF flag in the status register);</li> <li>Read status register SCISR1 (returns RDRF clear and OR set).</li> <li>Event 3 may be at exactly the same time as event 2 or any time after. When this happens, a dummy SCIDRL read following event 4 will be required to clear the OR flag if further frames are to be received.</li> </ol> |  |  |  |  |

| 2<br>NF | <ul> <li>Noise Flag — NF is set when the SCI detects noise on the receiver input. NF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear NF by reading SCI status register 1(SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No noise</li> <li>1 Noise</li> </ul>                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 1<br>FE | <ul> <li>Framing Error Flag — FE is set when a logic 0 is accepted as the stop bit. FE bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. FE inhibits further data reception until it is cleared. Clear FE by reading SCI status register 1 (SCISR1) with FE set and then reading the SCI data register low (SCIDRL).</li> <li>0 No framing error</li> <li>1 Framing error</li> </ul>                                                                                                                                                                                                                               |  |  |  |  |

| 0<br>PF | <ul> <li>Parity Error Flag — PF is set when the parity enable bit (PE) is set and the parity of the received data does not match the parity type bit (PT). PF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear PF by reading SCI status register 1 (SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No parity error</li> <li>1 Parity error</li> </ul>                                                                                                                                                                                                                                 |  |  |  |  |

### Table 14-11. SCISR1 Field Descriptions (continued)

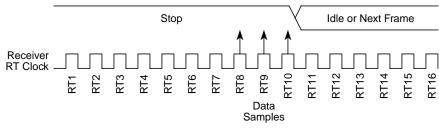

### 14.4.6.5.2 Fast Data Tolerance

Figure 14-29 shows how much a fast received frame can be misaligned. The fast stop bit ends at RT10 instead of RT16 but is still sampled at RT8, RT9, and RT10.

For an 8-bit data character, it takes the receiver 9 bit times x 16 RTr cycles + 10 RTr cycles = 154 RTr cycles to finish data sampling of the stop bit.

With the misaligned character shown in Figure 14-29, the receiver counts 154 RTr cycles at the point when the count of the transmitting device is 10 bit times x 16 RTt cycles = 160 RTt cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is:

$((160 - 154) / 160) \ge 100 = 3.75\%$

For a 9-bit data character, it takes the receiver 10 bit times x 16 RTr cycles + 10 RTr cycles = 170 RTr cycles to finish data sampling of the stop bit.

With the misaligned character shown in Figure 14-29, the receiver counts 170 RTr cycles at the point when the count of the transmitting device is 11 bit times x 16 RTt cycles = 176 RTt cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is:

$((176 - 170) / 176) \ge 100 = 3.40\%$

### 14.4.6.6 Receiver Wakeup

To enable the SCI to ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCI control register 2 (SCICR2) puts the receiver into standby state during which receiver interrupts are disabled. The SCI will still load the receive data into the SCIDRH/L registers, but it will not set the RDRF flag.

The transmitting device can address messages to selected receivers by including addressing information in the initial frame or frames of each message.

The WAKE bit in SCI control register 1 (SCICR1) determines how the SCI is brought out of the standby state to process an incoming message. The WAKE bit enables either idle line wakeup or address mark wakeup.

Voltage Regulator (S12VREGL3V3V1)

# 17.2 External Signal Description

Due to the nature of VREG\_3V3 being a voltage regulator providing the chip internal power supply voltages, most signals are power supply signals connected to pads.

Table 17-2 shows all signals of VREG\_3V3 associated with pins.

| Name                   | Function                                       | Reset State | Pull Up |

|------------------------|------------------------------------------------|-------------|---------|

| VDDR                   | Power input (positive supply)                  | —           | —       |

| VDDA                   | Quiet input (positive supply)                  | —           | —       |

| VSSA                   | Quiet input (ground)                           | —           | —       |

| VDDX                   | Power input (positive supply)                  | —           | —       |

| VDD                    | Primary output (positive supply)               | —           | —       |

| VSS                    | Primary output (ground)                        | —           | —       |

| VDDF                   | Secondary output (positive supply)             | —           | —       |

| VDDPLL                 | Tertiary output (positive supply)              | —           | —       |

| VSSPLL                 | Tertiary output (ground)                       | —           | —       |

| VREGEN (optional)      | Optional Regulator Enable                      | —           | —       |

| VREG_API<br>(optional) | VREG Autonomous Periodical<br>Interrupt output |             | —       |

Table 17-2. Signal Properties

## NOTE

Check device level specification for connectivity of the signals.

# 17.2.1 VDDR — Regulator Power Input Pins

Signal VDDR is the power input of VREG\_3V3. All currents sourced into the regulator loads flow through this pin. A chip external decoupling capacitor (100 nF...220 nF, X7R ceramic) between VDDR and VSSR (if VSSR is not available VSS) can smooth ripple on VDDR.

For entering Shutdown Mode, pin VDDR should also be tied to ground on devices without VREGEN pin.

# 17.2.2 VDDA, VSSA — Regulator Reference Supply Pins

Signals VDDA/VSSA, which are supposed to be relatively quiet, are used to supply the analog parts of the regulator. Internal precision reference circuits are supplied from these signals. A chip external decoupling capacitor (100 nF...220 nF, X7R ceramic) between VDDA and VSSA can further improve the quality of this supply.

# 17.2.3 VDD, VSS — Regulator Output1 (Core Logic) Pins

Signals VDD/VSS are the primary outputs of VREG\_3V3 that provide the power supply for the core logic. These signals are connected to device pins to allow external decoupling capacitors (220 nF, X7R ceramic).

#### Voltage Regulator (S12VREGL3V3V1)

It is possible to generate with the API a waveform at an external pin by enabling the API by setting APIFE and enabling the external access with setting APIEA. By setting APIES the waveform can be selected. If APIES is set, then at the external pin a clock is visible with 2 times the selected API Period (Table 17-10). If APIES is not set, then at the external pin will be a high pulse at the end of every selected period with the size of half of the min period (Table 17-10). See device level specification for connectivity.

## 17.4.9 Resets

This section describes how VREG\_3V3 controls the reset of the MCU. The reset values of registers and signals are provided in Section 17.3, "Memory Map and Register Definition". Possible reset sources are listed in Table 17-13.

| Reset Source      | Local Enable                            |

|-------------------|-----------------------------------------|

| Power-on reset    | Always active                           |

| Low-voltage reset | Available only in Full Performance Mode |

Table 17-13. Reset Sources

# 17.4.10 Description of Reset Operation

## 17.4.10.1 Power-On Reset (POR)

During chip power-up the digital core may not work if its supply voltage  $V_{DD}$  is below the POR deassertion level ( $V_{PORD}$ ). Therefore, signal POR, which forces the other blocks of the device into reset, is kept high until  $V_{DD}$  exceeds  $V_{PORD}$ . The MCU will run the start-up sequence after POR deassertion. The power-on reset is active in all operation modes of VREG\_3V3.

## 17.4.10.2 Low-Voltage Reset (LVR)

For details on low-voltage reset, see Section 17.4.5, "Low-Voltage Reset (LVR)".

## 17.4.11 Interrupts

This section describes all interrupts originated by VREG\_3V3.

The interrupt vectors requested by VREG\_3V3 are listed in Table 17-14. Vector addresses and interrupt priorities are defined at MCU level.

| Interrupt Source                      | Local Enable                                         |

|---------------------------------------|------------------------------------------------------|

| Low-voltage interrupt (LVI)           | LVIE = 1; available only in Full Performance<br>Mode |

| High Temperature Interrupt (HTI)      | HTIE=1;<br>available only in Full Performance Mode   |

| Autonomous periodical interrupt (API) | APIE = 1                                             |

Table 17-14. Interrupt Vectors

| Address<br>& Name |                             | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------|-----------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0x0010<br>FOPT    | R<br>W                      | NV7 | NV6 | NV5 | NV4 | NV3 | NV2 | NV1 | NV0 |

| 0x0011<br>FRSV2   | R<br>W                      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0x0012<br>FRSV3   | R<br>W                      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0x0013<br>FRSV4   | R<br>W                      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|                   | = Unimplemented or Reserved |     |     |     |     |     |     |     |     |

#### 256 KByte Flash Module (S12XFTMR256K1V1)

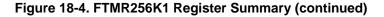

## 18.3.2.1 Flash Clock Divider Register (FCLKDIV)

The FCLKDIV register is used to control timed events in program and erase algorithms.

### Figure 18-5. Flash Clock Divider Register (FCLKDIV)

All bits in the FCLKDIV register are readable, bits 6–0 are write once and bit 7 is not writable.

### Table 18-6. FCLKDIV Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                                                                                                                             |

| 6–0<br>FDIV[6:0] | <b>Clock Divider Bits</b> — FDIV[6:0] must be set to effectively divide OSCCLK down to generate an internal Flash clock, FCLK, with a target frequency of 1 MHz for use by the Flash module to control timed events during program and erase algorithms. Table 18-7 shows recommended values for FDIV[6:0] based on OSCCLK frequency. Please refer to Section 18.4.1, "Flash Command Operations," for more information. |

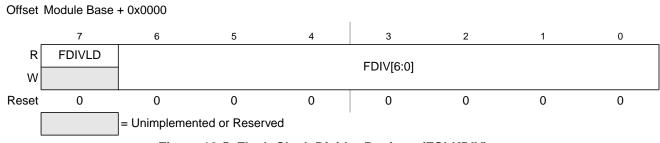

#### 128 KByte Flash Module (S12XFTMR128K1V1)

All assigned bits in the FERCNFG register are readable and writable.

### Table 19-14. FERCNFG Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIE | <ul> <li>Double Bit Fault Detect Interrupt Enable — The DFDIE bit controls interrupt generation when a double bit fault is detected during a Flash block read operation.</li> <li>0 DFDIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the DFDIF flag is set (see Section 19.3.2.8)</li> </ul>                                                       |

| 0<br>SFDIE | <ul> <li>Single Bit Fault Detect Interrupt Enable — The SFDIE bit controls interrupt generation when a single bit fault is detected during a Flash block read operation.</li> <li>0 SFDIF interrupt disabled whenever the SFDIF flag is set (see Section 19.3.2.8)</li> <li>1 An interrupt will be requested whenever the SFDIF flag is set (see Section 19.3.2.8)</li> </ul> |

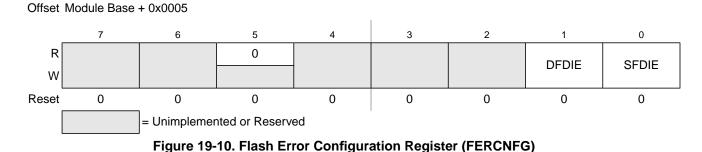

## 19.3.2.7 Flash Status Register (FSTAT)

The FSTAT register reports the operational status of the Flash module.

Offset Module Base + 0x0006

### Figure 19-11. Flash Status Register (FSTAT)

<sup>1</sup> Reset value can deviate from the value shown if a double bit fault is detected during the reset sequence (see Section 19.6).

CCIF, ACCERR, and FPVIOL bits are readable and writable, MGBUSY and MGSTAT bits are readable but not writable, while remaining bits read 0 and are not writable.

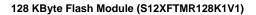

Figure 19-25. Flash Reserved4 Register (FRSV4)

All bits in the FRSV4 register read 0 and are not writable.

# **19.4 Functional Description**

# 19.4.1 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

Offset Module Base + 0x0013

- How to write the FCLKDIV register that is used to generate a time base (FCLK) derived from OSCCLK for Flash program and erase command operations

- The command write sequence used to set Flash command parameters and launch execution

- Valid Flash commands available for execution

## 19.4.1.1 Writing the FCLKDIV Register

Prior to issuing any Flash program or erase command after a reset, the user is required to write the FCLKDIV register to divide OSCCLK down to a target FCLK of 1 MHz. Table 19-7 shows recommended values for the FDIV field based on OSCCLK frequency.

## NOTE

Programming or erasing the Flash memory cannot be performed if the bus clock runs at less than 1 MHz. Setting FDIV too high can destroy the Flash memory due to overstress. Setting FDIV too low can result in incomplete programming or erasure of the Flash memory cells.

When the FCLKDIV register is written, the FDIVLD bit is set automatically. If the FDIVLD bit is 0, the FCLKDIV register has not been written since the last reset. If the FCLKDIV register has not been written, any Flash program or erase command loaded during a command write sequence will not execute and the ACCERR bit in the FSTAT register will set.

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

Valid margin level settings for the Set User Margin Level command are defined in Table 19-54.

Table 19-54. Valid Set User Margin Level Settings

| CCOB<br>(CCOBIX=001) | Level Description                |

|----------------------|----------------------------------|

| 0x0000               | Return to Normal Level           |

| 0x0001               | User Margin-1 Level <sup>1</sup> |

| 0x0002               | User Margin-0 Level <sup>2</sup> |

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

| Table 19-55. | Set User Margin | Level Command | Error Handling |

|--------------|-----------------|---------------|----------------|

|--------------|-----------------|---------------|----------------|

| Register | Error Bit | Error Condition                                                |

|----------|-----------|----------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                    |

|          |           | Set if command not available in current mode (see Table 19-28) |

|          |           | Set if an invalid global address [22:16] is supplied           |

| FSTAT    |           | Set if an invalid margin level setting is supplied             |

|          | FPVIOL    | None                                                           |

|          | MGSTAT1   | None                                                           |

|          | MGSTAT0   | None                                                           |

### NOTE

User margin levels can be used to check that Flash memory contents have adequate margin for normal level read operations. If unexpected results are encountered when checking Flash memory contents at user margin levels, a potential loss of information has been detected.

## 19.4.2.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of a specific P-Flash or D-Flash block.

| CCOBIX[2:0] | FCCOB Parameters     |                                                       |  |

|-------------|----------------------|-------------------------------------------------------|--|

| 000         | 0x0E                 | Global address [22:16] to identify the Flash<br>block |  |

| 001         | Margin level setting |                                                       |  |

Table 19-59. Erase Verify D-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                       |                                                      |

|-------------|--------------------------------------------------------|------------------------------------------------------|

| 000         | 0x10                                                   | Global address [22:16] to identify the D-Flash block |

| 001         | Global address [15:0] of the first word to be verified |                                                      |

| 010         | Number of words to be verified                         |                                                      |

Upon clearing CCIF to launch the Erase Verify D-Flash Section command, the Memory Controller will verify the selected section of D-Flash memory is erased. The CCIF flag will set after the Erase Verify D-Flash Section operation has completed.

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                             |

|          |           | Set if command not available in current mode (see Table 19-28)          |

|          |           | Set if an invalid global address [22:0] is supplied                     |

| FOTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)  |

| FSTAT    |           | Set if the requested section breaches the end of the D-Flash block      |

|          | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

Table 19-60. Erase Verify D-Flash Section Command Error Handling

## 19.4.2.15 Program D-Flash Command

The Program D-Flash operation programs one to four previously erased words in the D-Flash block. The Program D-Flash operation will confirm that the targeted location(s) were successfully programmed upon completion.

### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

Table 19-61. Program D-Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                               |                                                      |  |

|-------------|------------------------------------------------|------------------------------------------------------|--|

| 000         | 0x11                                           | Global address [22:16] to identify the D-Flash block |  |

| 001         | Global address [15:0] of word to be programmed |                                                      |  |

| 010         | Word 0 program value                           |                                                      |  |

| 011         | Word 1 program value, if desired               |                                                      |  |

| 100         | Word 2 program value, if desired               |                                                      |  |

<sup>1</sup> Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 20.5.

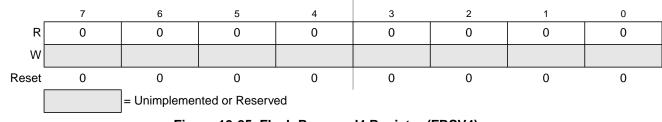

## 20.3.2.3 Flash CCOB Index Register (FCCOBIX)

The FCCOBIX register is used to index the FCCOB register for Flash memory operations.

Offset Module Base + 0x0002

### Figure 20-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

### Table 20-11. FCCOBIX Field Descriptions

| Field              | Description                                                                                                                                                                                                                            |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2–0<br>CCOBIX[1:0] | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See Section 20.3.2.11, "Flash Common Command Object Register (FCCOB)," for more details. |

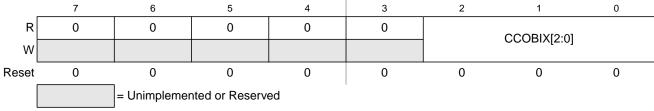

## 20.3.2.4 Flash ECCR Index Register (FECCRIX)

The FECCRIX register is used to index the FECCR register for ECC fault reporting.

Offset Module Base + 0x0003

### Figure 20-8. FECCR Index Register (FECCRIX)

ECCRIX bits are readable and writable while remaining bits read 0 and are not writable.

### Table 20-12. FECCRIX Field Descriptions

| Field              | Description                                                                                                                                                                                                     |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0<br>ECCRIX[2:0] | <b>ECC Error Register Index</b> — The ECCRIX bits are used to select which word of the FECCR register array is being read. See Section 20.3.2.14, "Flash ECC Error Results Register (FECCR)," for more details. |

S12XS Family Reference Manual, Rev. 1.13

## NOTE

Field margin levels can be used to check that Flash memory contents have adequate margin for data retention at the normal level setting. If unexpected results are encountered when checking Flash memory contents at field margin levels, the Flash memory contents should be erased and reprogrammed.

## 20.4.2.14 Erase Verify D-Flash Section Command

The Erase Verify D-Flash Section command will verify that a section of code in the D-Flash is erased. The Erase Verify D-Flash Section command defines the starting point of the data to be verified and the number of words.

Table 20-59. Erase Verify D-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                       |                                                      |

|-------------|--------------------------------------------------------|------------------------------------------------------|

| 000         | 0x10                                                   | Global address [22:16] to identify the D-Flash block |

| 001         | Global address [15:0] of the first word to be verified |                                                      |

| 010         | Number of words to be verified                         |                                                      |

Upon clearing CCIF to launch the Erase Verify D-Flash Section command, the Memory Controller will verify the selected section of D-Flash memory is erased. The CCIF flag will set after the Erase Verify D-Flash Section operation has completed.

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                             |

|          |           | Set if command not available in current mode (see Table 20-28)          |

|          |           | Set if an invalid global address [22:0] is supplied                     |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)  |

|          |           | Set if the requested section breaches the end of the D-Flash block      |

|          | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

## 20.4.2.15 Program D-Flash Command

The Program D-Flash operation programs one to four previously erased words in the D-Flash block. The Program D-Flash operation will confirm that the targeted location(s) were successfully programmed upon completion.

#### 64 KByte Flash Module (S12XFTMR64K1V1)

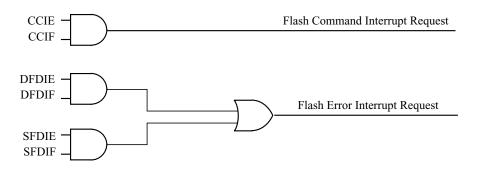

the DFDIE and SFDIE interrupt enable bits to generate the Flash error interrupt request. For a detailed description of the register bits involved, refer to Section 20.3.2.5, "Flash Configuration Register (FCNFG)", Section 20.3.2.6, "Flash Error Configuration Register (FERCNFG)", Section 20.3.2.7, "Flash Status Register (FSTAT)", and Section 20.3.2.8, "Flash Error Status Register (FERSTAT)".

The logic used for generating the Flash module interrupts is shown in Figure 20-27.

Figure 20-27. Flash Module Interrupts Implementation

## 20.4.4 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 20.4.3, "Interrupts").

## 20.4.5 Stop Mode

If a Flash command is active (CCIF = 0) when the MCU requests stop mode, the current Flash operation will be completed before the CPU is allowed to enter stop mode.

# 20.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 20-10). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x7F\_FF0F.

The security state out of reset can be permanently changed by programming the security byte of the Flash configuration field. This assumes that you are starting from a mode where the necessary P-Flash erase and program commands are available and that the upper region of the P-Flash is unprotected. If the Flash security byte is successfully programmed, its new value will take affect after the next MCU reset.

The following subsections describe these security-related subjects:

- Unsecuring the MCU using Backdoor Key Access

- Unsecuring the MCU in Special Single Chip Mode using BDM

- Mode and Security Effects on Flash Command Availability