Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | HCS12X                                                      |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 40MHz                                                       |

| Connectivity               | CANbus, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 59                                                          |

| Program Memory Size        | 128KB (128K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 8K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                |

| Data Converters            | A/D 8x12b                                                   |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 80-QFP                                                      |

| Supplier Device Package    | 80-QFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12xs128maa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 1 Device Overview S12XS Family

| 1.1  | Introduction | on                                   | 19 |

|------|--------------|--------------------------------------|----|

|      | 1.1.1 Fe     | eatures                              | 19 |

|      | 1.1.2 M      | Iodes of Operation                   | 23 |

|      | 1.1.3 B      | lock Diagram                         | 24 |

|      | 1.1.4 D      | evice Memory Map                     | 25 |

|      | 1.1.5 A      | ddress Mapping                       | 26 |

|      | 1.1.6 D      | etailed Register Map                 | 28 |

|      | 1.1.7 Pa     | art ID Assignments                   | 28 |

| 1.2  | Signal Des   | scription                            | 29 |

|      | 1.2.1 D      | evice Pinout                         | 29 |

|      | 1.2.2 Pi     | in Assignment Overview               | 33 |

|      | 1.2.3 D      | etailed Signal Descriptions          | 41 |

|      | 1.2.4 Po     | ower Supply Pins                     | 45 |

| 1.3  | System Clo   | ock Description                      | 48 |

| 1.4  | Modes of 0   | Operation                            | 49 |

|      |              | hip Configuration Summary            |    |

|      |              | ower Modes                           |    |

|      |              | reeze Mode                           |    |

| 1.5  | _            |                                      |    |

| 1.6  |              | Interrupts                           |    |

|      |              | esets                                |    |

|      |              | ectors                               |    |

|      |              | ffects of Reset                      |    |

| 1.7  |              | figuration                           |    |

|      |              | xternal Trigger Input Connection     |    |

|      |              | TD0 Channel[17] Connection           |    |

| 1.8  |              | nfiguration                          |    |

|      |              | emperature Sensor Configuration      |    |

| 1.9  |              | ck Configuration                     |    |

| 1.10 | Oscillator ( | Configuration                        | 56 |

|      |              | Chantar 0                            |    |

|      |              | Chapter 2                            |    |

|      |              | Port Integration Module (S12XSPIMV1) |    |

| 2.1  |              | on                                   |    |

|      |              | verview                              |    |

|      |              | eatures                              |    |

| 2.2  |              | ignal Description                    |    |

| 2.3  | Memory M     | Map and Register Definition          | 64 |

|      |              |                                      |    |

|       | 12.1.2 Features                           | 349 |

|-------|-------------------------------------------|-----|

|       | 12.1.3 Modes of Operation                 | 349 |

|       | 12.1.4 Block Diagram                      | 350 |

| 12.2  | External Signal Description               | 350 |

|       | Register Definition                       |     |

| 12.4  | Functional Description                    | 360 |

|       | 12.4.1 Timer                              | 360 |

|       | 12.4.2 Interrupt Interface                | 361 |

|       | 12.4.3 Hardware Trigger                   | 362 |

| 12.5  | Initialization                            | 362 |

|       | 12.5.1 Startup                            | 362 |

|       | 12.5.2 Shutdown                           | 362 |

|       | 12.5.3 Flag Clearing                      |     |

| 12.6  | Application Information                   | 363 |

|       |                                           |     |

|       | Chapter 13                                |     |

|       | Pulse-Width Modulator (S12PWM8B8CV1)      |     |

| 13.1  | Introduction                              | 365 |

|       | 13.1.1 Features                           | 365 |

|       | 13.1.2 Modes of Operation                 | 366 |

|       | 13.1.3 Block Diagram                      | 366 |

| 13.2  | External Signal Description               |     |

|       | 13.2.1 PWM7 — PWM Channel 7               |     |

|       | 13.2.2 PWM6 — PWM Channel 6               |     |

|       | 13.2.3 PWM5 — PWM Channel 5               |     |

|       | 13.2.4 PWM4 — PWM Channel 4               |     |

|       | 13.2.5 PWM3 — PWM Channel 3               |     |

|       | 13.2.6 PWM3 — PWM Channel 2               |     |

|       | 13.2.7 PWM3 — PWM Channel 1               |     |

|       | 13.2.8 PWM3 — PWM Channel 0               |     |

| 13.3  | Memory Map and Register Definition        |     |

|       | 13.3.1 Module Memory Map                  |     |

| 12.4  | 13.3.2 Register Descriptions              |     |

| 13.4  | Functional Description                    |     |

|       | 13.4.1 PWM Clock Select                   |     |

| 12.5  | 13.4.2 PWM Channel Timers                 |     |

|       | Interrupts                                |     |

| 13.0  | interrupts                                | 393 |

|       | Chapter 14                                |     |

|       | Serial Communication Interface (S12SCIV5) |     |

| 1 / 1 |                                           | 207 |

| 14.1  | Introduction                              |     |

|       | 14.1.1 Glossary                           |     |

|       | 14.1.2 Teaules                            | 398 |

|       |                                           |     |

S12XS Family Reference Manual, Rev. 1.13

Freescale Semiconductor

34

Table 1-6 provides a pin out summary listing the availability and functionality of individual pins for each package option.

Table 1-6. Pin-Out Summary<sup>1</sup>

# S12XS Family Reference Manual, Rev. 1.13

Freescale Semiconductor

| Pack        | Package Terminal |            |      |              | Function     |              |              | Power            | Internal<br>Resist |                | Decarintian                                               |

|-------------|------------------|------------|------|--------------|--------------|--------------|--------------|------------------|--------------------|----------------|-----------------------------------------------------------|

| LQFP<br>112 | QFP<br>80        | LQFP<br>64 | Pin  | 2nd<br>Func. | 3rd<br>Func. | 4th<br>Func. | 5th<br>Func. | Supply           | CTRL               | Reset<br>State | Description                                               |

| 1           | 1                | 1          | PP3  | KWP3         | PWM3         | _            | _            | V <sub>DDX</sub> | PERP/PPSP          | Disabled       | Port P I/O, interrupt,<br>PWM channel                     |

| 2           | 2                | 2          | PP2  | KWP2         | PWM2         | IOC2         | TXD1         | V <sub>DDX</sub> | PERP/PPSP          | Disabled       | Port P I/O, interrupt,<br>PWM/TIM channel, TXD<br>of SCI1 |

| 3           | 3                | 3          | PP1  | KWP1         | PWM1         | IOC1         | _            | V <sub>DDX</sub> | PERP/PPSP          | Disabled       | Port P I/O, interrupt,<br>PWM/TIM channel                 |

| 4           | 4                | 4          | PP0  | KWP0         | PWM0         | IOC0         | RXD1         | V <sub>DDX</sub> | PERP/PPSP          | Disabled       | Port P I/O, interrupt,<br>PWM/TIM channel,<br>RXD of SCI1 |

| 5           | -                | -          | PK3  | _            | _            | _            | _            | V <sub>DDX</sub> | PUCR               | Up             | Port K I/O                                                |

| 6           | -                | -          | PK2  | _            | _            | _            | _            | V <sub>DDX</sub> | PUCR               | Up             | Port K I/O                                                |

| 7           | -                | -          | PK1  | _            | _            | _            | _            | V <sub>DDX</sub> | PUCR               | Up             | Port K I/O                                                |

| 8           | -                | -          | PK0  | _            | _            | _            | _            | V <sub>DDX</sub> | PUCR               | Up             | Port K I/O                                                |

| 9           | 5                | 5          | PT0  | IOC0         | _            | _            | _            | V <sub>DDX</sub> | PERT/PPST          | Disabled       | Port T I/O, TIM channel                                   |

| 10          | 6                | 6          | PT1  | IOC1         | _            | _            | _            | V <sub>DDX</sub> | PERT/PPST          | Disabled       | Port T I/O, TIM channel                                   |

| 11          | 7                | 7          | PT2  | IOC2         | _            | _            | _            | V <sub>DDX</sub> | PERT/PPST          | Disabled       | Port T I/O, TIM channel                                   |

| 12          | 8                | 8          | PT3  | IOC3         | _            | _            | _            | V <sub>DDX</sub> | PERT/PPST          | Disabled       | Port T I/O, TIM channel                                   |

| 13          | 9                | 9          | VDDF | _            | _            | _            | _            | _                | _                  | _              | _                                                         |

| 14          | 10               | 10         | VSS1 | _            | _            | _            | _            | _                | _                  | _              | _                                                         |

| 15          | 11               | 11         | PT4  | IOC4         | PWM4         | _            | _            | V <sub>DDX</sub> | PERT/PPST          | Disabled       | Port T I/O, PWM/TIM channel                               |

The selected oscillator configuration is frozen with the rising edge of the  $\overline{RESET}$  pin in any of these above described reset cases.

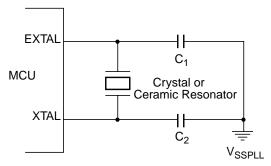

Figure 1-7. Loop Controlled Pierce Oscillator Connections (XCLKS = 1)

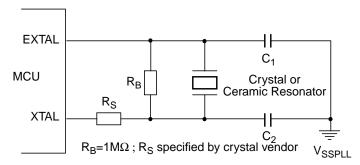

Figure 1-8. Full Swing Pierce Oscillator Connections (XCLKS = 0)

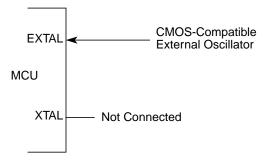

Figure 1-9. External Clock Connections (XCLKS = 0)

### Port Integration Module (S12XSPIMV1)

Read: Anytime Write: Anytime

Table 2-19. RDRT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>RDRT | Port T reduced drive—Select reduced drive for output pin This bit configures the drive strength of the associated output pin as either full or reduced. If a pin is used as input this bit has no effect. The reduced drive function is independent of which function is being used on a particular pin. |

|             | 1 Reduced drive selected (approx. 1/5 of the full drive strength) 0 Full drive strength enabled                                                                                                                                                                                                          |

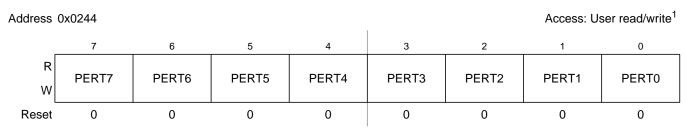

# 2.3.22 Port T Pull Device Enable Register (PERT)

Figure 2-20. Port T Pull Device Enable Register (PERT)

Table 2-20. PERT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PERT | Port T pull device enable—Enable pull device on input pin This bit controls whether a pull device on the associated port input pin is active. If a pin is used as output this bit has no effect. The polarity is selected by the related polarity select register bit.  1 Pull device enabled 0 Pull device disabled |

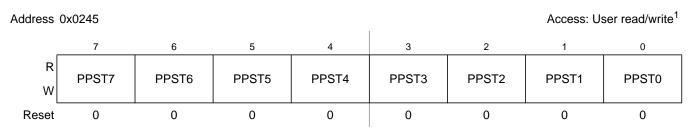

# 2.3.23 Port T Polarity Select Register (PPST)

Figure 2-21. Port T Polarity Select Register (PPST)

S12XS Family Reference Manual, Rev. 1.13

Read: Anytime Write: Anytime

Read: Anytime Write: Anytime

### Port Integration Module (S12XSPIMV1)

Table 2-37. SCI1 Routing

| MODRRx |   | MODRRx Related Pins   |                       |

|--------|---|-----------------------|-----------------------|

| 0      | 0 | PS3                   | PS2                   |

| 0      | 1 | PP2                   | PP0                   |

| 1      | 0 | PM1                   | PM0                   |

| 1      | 1 | Reserved <sup>1</sup> | Reserved <sup>1</sup> |

Defaults to reset value

Table 2-38. SPI0 Routing

| MODRRx | Related Pins |       |      |     |  |  |  |

|--------|--------------|-------|------|-----|--|--|--|

| 4      | MISO0        | MOSI0 | SCK0 | SS0 |  |  |  |

| 0      | PS4          | PS5   | PS6  | PS7 |  |  |  |

| 1      | PM2          | PM4   | PM5  | PM3 |  |  |  |

# 2.3.42 Port P Data Register (PTP)

Access: User read/write<sup>1</sup> Address 0x0258 7 6 5 4 3 2 0 R PTP7 PTP6 PTP5 PTP4 PTP2 PTP1 PTP0 PTP3 W PWM1 Altern. PWM7 PWM6 PWM5 PWM4 PWM3 PWM2 PWM0 **Function** (IOC2) (IOC1) (IOC0) (TXD1) (RXD1) Reset 0 0 0 0 0 0

Figure 2-40. Port P Data Register (PTP)

Read: Anytime, the data source depends on the data direction value Write: Anytime

### Table 2-39. PTP Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PTP   | Port P general purpose input/output data—Data Register, PWM input/output, pin interrupt input/output When not used with the alternative function, the associated pin can be used as general purpose I/O. In general purpose output mode the register bit value is driven to the pin. If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered pin input state is read.  • The PWM function takes precedence over the general purpose I/O function if the related channel or the |

|            | emergency shut-down feature is enabled.     Pin interrupts can be generated if enabled in input or output mode.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6-3<br>PTP | Port P general purpose input/output data—Data Register, PWM output, pin interrupt input/output When not used with the alternative function, the associated pin can be used as general purpose I/O. In general purpose output mode the register bit value is driven to the pin. If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered pin input state is read.  • The PWM function takes precedence over the general purpose I/O function if the related channel is enabled.  |

|            | <ul> <li>Pin interrupts can be generated if enabled in input or output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2<br>PTP   | Port P general purpose input/output data—Data Register, PWM output, routed TIM output, routed SCI1 TXD output, pin interrupt input/output When not used with the alternative function, the associated pin can be used as general purpose I/O. In general purpose output mode the register bit value is driven to the pin.  If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered pin input state is read.                                                                    |

|            | <ul> <li>The PWM function takes precedence over the TIM, SCI1 and general purpose I/O function if the related channel is enabled.</li> <li>The TIM function takes precedence over SCI1 and the general purpose I/O function if the related channel is enabled.</li> <li>The SCI1 function takes precedence over the general purpose I/O function if enabled.</li> <li>Pin interrupts can be generated if enabled in input or output mode.</li> </ul>                                                                                               |

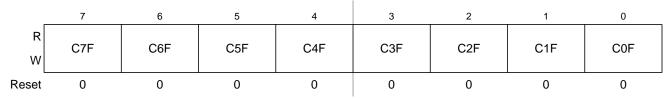

### Memory Mapping Control (S12XMMCV4)

Write: Anytime

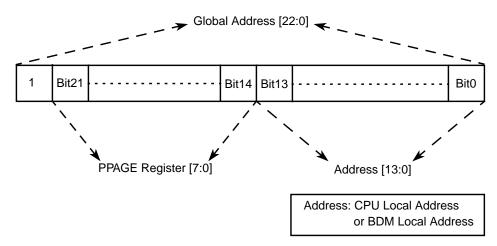

These eight index bits are used to page 16KB blocks into the Flash page window located in the local (CPU or BDM) memory map from address 0x8000 to address 0xBFFF (see Figure 3-12). This supports accessing up to 4MB of Flash (in the Global map) within the 64KB Local map. The PPAGE register is effectively used to construct paged Flash addresses in the Local map format. The CPU has special access to read and write this register directly during execution of CALL and RTC instructions..

Figure 3-12. PPAGE Address Mapping

### **NOTE**

Writes to this register using the special access of the CALL and RTC instructions will be complete before the end of the instruction execution.

**Table 3-7. PPAGE Field Descriptions**

| Field | Description                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Program Page Index Bits 7–0</b> — These page index bits are used to select which of the 256 FLASH or ROM array pages is to be accessed in the Program Page Window. |

The reset value of 0xFE ensures that there is linear Flash space available between addresses 0x4000 and 0xFFFF out of reset.

The fixed 16K page from 0xC000-0xFFFF is the page number 0xFF.

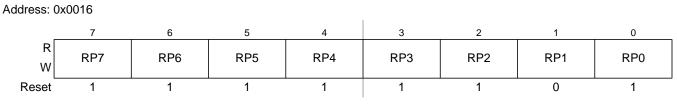

# 3.3.2.6 RAM Page Index Register (RPAGE)

Figure 3-13. RAM Page Index Register (RPAGE)

S12XS Family Reference Manual, Rev. 1.13

| Table 4-6. | XGATE Int | errupt Prio | rity Levels |

|------------|-----------|-------------|-------------|

|            |           |             |             |

| Priority | XILVL2 | XILVL1 | XILVL0 | Meaning                       |

|----------|--------|--------|--------|-------------------------------|

|          | 0      | 0      | 0      | Interrupt request is disabled |

| low      | 0      | 0      | 1      | Priority level 1              |

|          | 0      | 1      | 0      | Priority level 2              |

|          | 0      | 1      | 1      | Priority level 3              |

|          | 1      | 0      | 0      | Priority level 4              |

|          | 1      | 0      | 1      | Priority level 5              |

|          | 1      | 1      | 0      | Priority level 6              |

| high     | 1      | 1      | 1      | Priority level 7              |

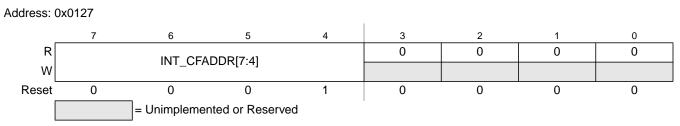

### 4.3.2.3 Interrupt Request Configuration Address Register (INT\_CFADDR)

Figure 4-5. Interrupt Configuration Address Register (INT\_CFADDR)

Read: Anytime Write: Anytime

Table 4-7. INT\_CFADDR Field Descriptions

| Field                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–4<br>INT_CFADDR[7:4] | Interrupt Request Configuration Data Register Select Bits — These bits determine which of the 128 configuration data registers are accessible in the 8 register window at INT_CFDATA0-7. The hexadecimal value written to this register corresponds to the upper nibble of the lower byte of the address of the interrupt vector, i.e., writing 0xE0 to this register selects the configuration data register block for the 8 interrupt vector requests starting with vector at address (vector base + 0x00E0) to be accessible as INT_CFDATA0-7.  Note: Writing all 0s selects non-existing configuration registers. In this case write accesses to INT_CFDATA0-7 will be ignored and read accesses will return all 0. |

# 4.3.2.4 Interrupt Request Configuration Data Registers (INT\_CFDATA0-7)

The eight register window visible at addresses INT\_CFDATA0-7 contains the configuration data for the block of eight interrupt requests (out of 128) selected by the interrupt configuration address register (INT\_CFADDR) in ascending order. INT\_CFDATA0 represents the interrupt configuration data register of the vector with the lowest address in this block, while INT\_CFDATA7 represents the interrupt configuration data register of the vector with the highest address, respectively.

Interrupt (S12XINTV2)

# 4.4.1 S12X Exception Requests

The CPU handles both reset requests and interrupt requests. The XINT module contains registers to configure the priority level of each I bit maskable interrupt request which can be used to implement an interrupt priority scheme. This also includes the possibility to nest interrupt requests. A priority decoder is used to evaluate the priority of a pending interrupt request.

## 4.4.2 Interrupt Prioritization

After system reset all interrupt requests with a vector address lower than or equal to (vector base +0x00F2) are enabled, are set up to be handled by the CPU and have a pre-configured priority level of 1. Exceptions to this rule are the non-maskable interrupt requests and the spurious interrupt vector request at (vector base +0x0010) which cannot be disabled, are always handled by the CPU and have a fixed priority levels. A priority level of 0 effectively disables the associated I bit maskable interrupt request.

If more than one interrupt request is configured to the same interrupt priority level the interrupt request with the higher vector address wins the prioritization.

The following conditions must be met for an I bit maskable interrupt request to be processed.

- 1. The local interrupt enabled bit in the peripheral module must be set.

- 2. The setup in the configuration register associated with the interrupt request channel must meet the following conditions:

- a) The XGATE request enable bit must be 0 to have the CPU handle the interrupt request.

- b) The priority level must be set to non zero.

- c) The priority level must be greater than the current interrupt processing level in the condition code register (CCR) of the CPU (PRIOLVL[2:0] > IPL[2:0]).

- 3. The I bit in the condition code register (CCR) of the CPU must be cleared.

- 4. There is no access violation interrupt request pending.

- 5. There is no SYS, SWI, BDM, TRAP, or  $\overline{\text{XIRO}}$  request pending.

### NOTE

All non I bit maskable interrupt requests always have higher priority than I bit maskable interrupt requests. If an I bit maskable interrupt request is interrupted by a non I bit maskable interrupt request, the currently active interrupt processing level (IPL) remains unaffected. It is possible to nest non I bit maskable interrupt requests, e.g., by nesting SWI or TRAP calls.

# 4.4.2.1 Interrupt Priority Stack

The current interrupt processing level (IPL) is stored in the condition code register (CCR) of the CPU. This way the current IPL is automatically pushed to the stack by the standard interrupt stacking procedure. The new IPL is copied to the CCR from the priority level of the highest priority active interrupt request channel which is configured to be handled by the CPU. The copying takes place when the interrupt vector is fetched. The previous IPL is automatically restored by executing the RTI instruction.

| Address | Name          |    | Bit 7 | 6          | 5              | 4           | 3               | 2             | 1       | Bit 0 |

|---------|---------------|----|-------|------------|----------------|-------------|-----------------|---------------|---------|-------|

| 0x001E  | ATDDR7        | R  |       |            |                |             |                 | esult Data (D | ,       |       |

| 0,0012  | / (I D D I (I | W  |       | and Se     | ection 10.3.2  | .12.2, "Rig | ht Justified R  | esult Data (D | )JM=1)" |       |

| 0x0020  | ATDDR8        | R  |       |            |                |             |                 | esult Data (D | ,       |       |

| 000020  | 7.1.22.1.0    | W  |       | and Se     | ection 10.3.2  | .12.2, "Rig | ht Justified R  | esult Data (D | )JM=1)" |       |

| 0x0022  | ATDDR9        | R  |       |            |                |             |                 | esult Data (D |         |       |

| ONCOLL  | 7.1.2.2.1.0   | W_ |       | and Se     | ection 10.3.2  | .12.2, "Rig | ht Justified R  | esult Data (D | )JM=1)" |       |

| 0x0024  | ATDDR10       | R  |       |            |                |             |                 | esult Data (D | ,       |       |

| 0,0021  | ALDDITIO      | W  |       | and Se     | ection 10.3.2  | .12.2, "Rig | ht Justified R  | esult Data (D | )JM=1)" |       |

| 0x0026  | 6 ATDDR11     | R  |       |            |                |             |                 | esult Data (D | ,       |       |

| 000020  |               | W  |       | and Se     | ection 10.3.2  | .12.2, "Rig | ht Justified R  | esult Data (D | )JM=1)" |       |

| 0x0028  | 3 ATDDR12     | R  |       |            |                |             |                 | esult Data (D | ,       |       |

| 0.0020  |               | W  |       | and Se     | ection 10.3.2  | .12.2, "Rig | ht Justified R  | esult Data (D | )JM=1)" |       |

| 0x002A  | ATDDR13       | R  |       |            |                |             |                 | esult Data (D | ,       |       |

| 000271  | ALDDITIO      | W  |       | and Se     | ection 10.3.2  | .12.2, "Rig | ht Justified R  | esult Data (D | )JM=1)" |       |

| 0x002C  | ATDDR14       | R  |       | See S      | Section 10.3.2 | 2.12.1, "Le | ft Justified Re | esult Data (D | JM=0)"  |       |

| 0,0020  | AIDDITIT      | W  |       | and Se     | ection 10.3.2  | .12.2, "Rig | ht Justified R  | esult Data (D | )JM=1)" |       |

| 0x002E  | ATDDR15       | R  |       |            |                |             |                 | esult Data (D |         |       |

| ONOUZL  | AIDDINIO      | W  |       | and Se     | ection 10.3.2  | .12.2, "Rig | ht Justified R  | esult Data (D | )JM=1)" |       |

|         |               |    |       | = Unimpler | mented or Re   | eserved     |                 |               |         |       |

Figure 10-3. ADC12B16C Register Summary (Sheet 2 of 2)

# 10.3.2 Register Descriptions

This section describes in address order all the ADC12B16C registers and their individual bits.

# 10.3.2.1 ATD Control Register 0 (ATDCTL0)

Writes to this register will abort current conversion sequence.

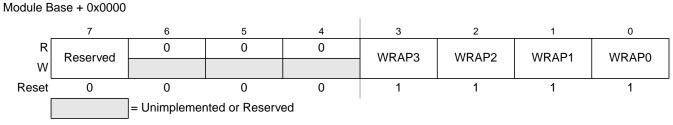

Figure 10-4. ATD Control Register 0 (ATDCTL0)

Read: Anytime

Write: Anytime, in special modes always write 0 to Reserved Bit 7.

Table 10-2. ATDCTL0 Field Descriptions

| Field | Description                                                                                                                                                      |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                  |

|       | Wrap Around Channel Select Bits — These bits determine the channel for wrap around when doing multi-channel conversions. The coding is summarized in Table 10-3. |

S12XS Family Reference Manual, Rev. 1.13

Freescale's Scalable Controller Area Network (S12MSCANV3)

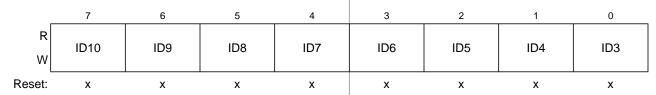

### 11.3.3.1.2 IDR0-IDR3 for Standard Identifier Mapping

Module Base + 0x00X0

Figure 11-30. Identifier Register 0 — Standard Mapping

Table 11-31. IDR0 Register Field Descriptions — Standard

| Field | Description                                                                                                                                                                                                                                                                                                                                   |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Standard Format Identifier</b> — The identifiers consist of 11 bits (ID[10:0]) for the standard format. ID10 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. See also ID bits in Table 11-32. |

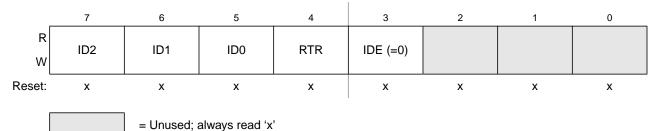

Module Base + 0x00X1

Figure 11-31. Identifier Register 1 — Standard Mapping

Table 11-32. IDR1 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5<br>ID[2:0] | <b>Standard Format Identifier</b> — The identifiers consist of 11 bits (ID[10:0]) for the standard format. ID10 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. See also ID bits in Table 11-31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4<br>RTR       | Remote Transmission Request — This flag reflects the status of the Remote Transmission Request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.  O Data frame Remote Transmission Request — This flag reflects the status of the Remote Transmission Request bit in the CAN frame and supports the transmission of the Remote Transmission Request bit in the CAN frame and supports the transmission of the Remote Transmission Request bit in the CAN frame and supports the transmission of the received frame and supports the transmission of the Remote Transmission Request bit in the CAN frame. |

| 3<br>IDE       | ID Extended — This flag indicates whether the extended or standard identifier format is applied in this buffer. In the case of a receive buffer, the flag is set as received and indicates to the CPU how to process the buffer identifier registers. In the case of a transmit buffer, the flag indicates to the MSCAN what type of identifier to send.  O Standard format (11 bit)  Extended format (29 bit)                                                                                                                                                                                                                                                                                                                                                                                                           |

S12XS Family Reference Manual, Rev. 1.13

# 12.6 Application Information

To get started quickly with the PIT24B8C module this section provides a small code example how to use the block. Please note that the example provided is only one specific case out of the possible configurations and implementations.

Functionality: Generate an PIT interrupt on channel 0 every 500 PIT clock cycles.

|                                        | ORG<br>LDS<br>MOVW                   | CODESTART  RAMEND #CH0_ISR,VEC_PIT_CH0                                                 | ; place the program into specific<br>; range (to be selected)<br>; load stack pointer to top of RAM<br>; Change value of channel 0 ISR adr                                                                                                         |

|----------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| . ***********                          | **** Start PI                        | Γ Initialization *********                                                             | *************                                                                                                                                                                                                                                      |

| ,**********                            | CLR MOVB CLR MOVB MOVW MOVB MOVB CLI | PITCFLMT #\$01,PITCE PITMUX #\$63,PITMTLD0 #\$0004,PITLD0 #\$01,PITINTE #\$80,PITCFLMT | ; disable PIT ; enable timer channel 0 ; ch0 connected to micro timer 0 ; micro time base 0 equals 100 clock cycles ; time base 0 eq. 5 micro time bases 0 =5*100 = 500 ; enable interupt channel 0 ; enable PIT ; clear Interupt disable Mask bit |

| MAIN:                                  | BRA *                                |                                                                                        | ; loop until interrupt                                                                                                                                                                                                                             |

| .************************************* | **** Channel                         | 0 Interupt Routine ******                                                              | *************                                                                                                                                                                                                                                      |

| CH0_ISR:                               | LDAA<br>MOVB<br>RTI                  | PITTF<br>#\$01,PITTF                                                                   | ; 8 bit read of PIT time out flags<br>; clear PIT channel 0 time out flag<br>; return to MAIN                                                                                                                                                      |

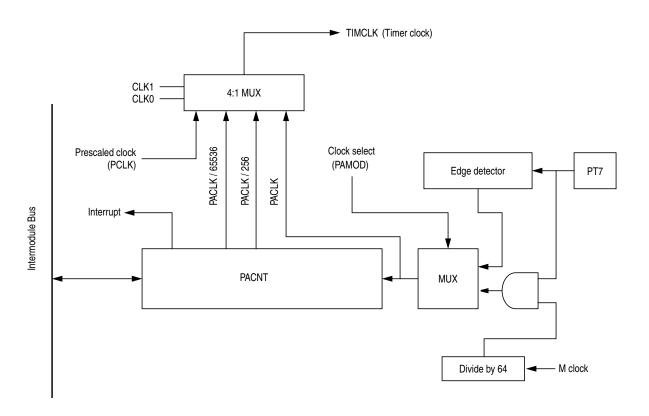

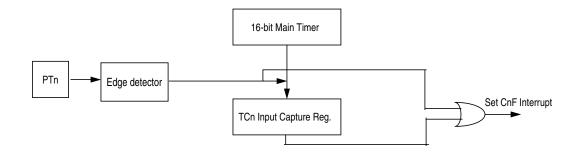

### Timer Module (TIM16B8CV2)

Figure 16-2. 16-Bit Pulse Accumulator Block Diagram

Figure 16-3. Interrupt Flag Setting

Timer Module (TIM16B8CV2)

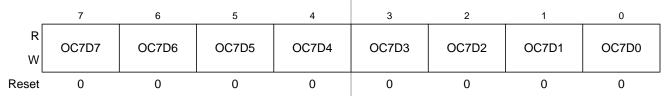

### 16.3.2.4 Output Compare 7 Data Register (OC7D)

Module Base + 0x0003

Figure 16-9. Output Compare 7 Data Register (OC7D)

Read: Anytime Write: Anytime

Table 16-5. OC7D Field Descriptions

| Field     | Description                                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------------------|

| 7:0       | Output Compare 7 Data — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a             |

| OC7D[7:0] | successful output compare on channel 7, can cause bits in the output compare 7 data register to transfer to the |

|           | timer port data register depending on the output compare 7 mask register.                                       |

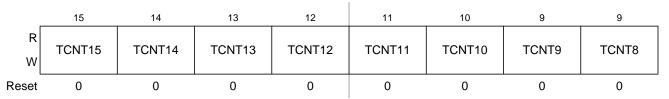

### 16.3.2.5 Timer Count Register (TCNT)

Module Base + 0x0004

Figure 16-10. Timer Count Register High (TCNTH)

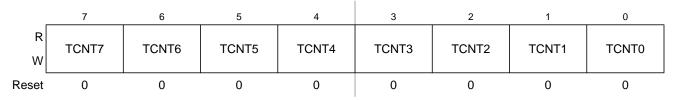

Module Base + 0x0005

Figure 16-11. Timer Count Register Low (TCNTL)

The 16-bit main timer is an up counter.

A full access for the counter register should take place in one clock cycle. A separate read/write for high byte and low byte will give a different result than accessing them as a word.

Read: Anytime

### **NOTE**

The newly selected prescale factor will not take effect until the next synchronized edge where all prescale counter stages equal zero.

### 16.3.2.12 Main Timer Interrupt Flag 1 (TFLG1)

Module Base + 0x000E

Figure 16-20. Main Timer Interrupt Flag 1 (TFLG1)

Read: Anytime

Write: Used in the clearing mechanism (set bits cause corresponding bits to be cleared). Writing a zero will not affect current status of the bit.

**Table 16-16. TRLG1 Field Descriptions**

| Field          | Description                                                                                                                                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>C[7:0]F | Input Capture/Output Compare Channel "x" Flag — These flags are set when an input capture or output compare event occurs. Clearing requires writing a one to the corresponding flag bit while TEN or PAEN is set to one. |

|                | When TFFCA bit in TSCR register is set, a read from an input capture or a write into an output compare channel (0x0010–0x001F) will cause the corresponding channel flag CxF to be cleared.                              |

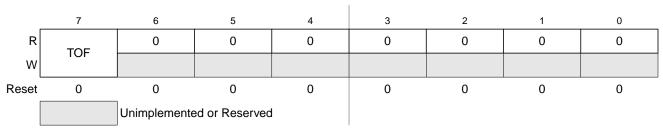

### 16.3.2.13 Main Timer Interrupt Flag 2 (TFLG2)

Module Base + 0x000F

Figure 16-21. Main Timer Interrupt Flag 2 (TFLG2)

TFLG2 indicates when interrupt conditions have occurred. To clear a bit in the flag register, write the bit to one while TEN bit of TSCR1 or PAEN bit of PACTL is set to one.

Read: Anytime

Write: Used in clearing mechanism (set bits cause corresponding bits to be cleared).

Any access to TCNT will clear TFLG2 register if the TFFCA bit in TSCR register is set.

S12XS Family Reference Manual Rev. 1.13

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 18-28)                      |  |  |

|          |           | Set if an invalid global address [22:0] is supplied                                 |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |

| TOTAL    | FPVIOL    | Set if the selected area of the D-Flash memory is protected                         |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

Table 18-64. Erase D-Flash Sector Command Error Handling

# 18.4.3 Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Interrupt Source                   | Interrupt Flag              | Local Enable                | Global (CCR)<br>Mask |

|------------------------------------|-----------------------------|-----------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | l Bit                |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register) | DFDIE<br>(FERCNFG register) | I Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | I Bit                |

**Table 18-65. Flash Interrupt Sources**

### **NOTE**

Vector addresses and their relative interrupt priority are determined at the MCU level.

# 18.4.3.1 Description of Flash Interrupt Operation

The Flash module uses the CCIF flag in combination with the CCIE interrupt enable bit to generate the Flash command interrupt request. The Flash module uses the DFDIF and SFDIF flags in combination with the DFDIE and SFDIE interrupt enable bits to generate the Flash error interrupt request. For a detailed description of the register bits involved, refer to Section 18.3.2.5, "Flash Configuration Register (FCNFG)", Section 18.3.2.6, "Flash Error Configuration Register (FERCNFG)", Section 18.3.2.7, "Flash Status Register (FSTAT)", and Section 18.3.2.8, "Flash Error Status Register (FERSTAT)".

The logic used for generating the Flash module interrupts is shown in Figure 18-27.

Freescale Semiconductor 553

S12XS Family Reference Manual, Rev. 1.13

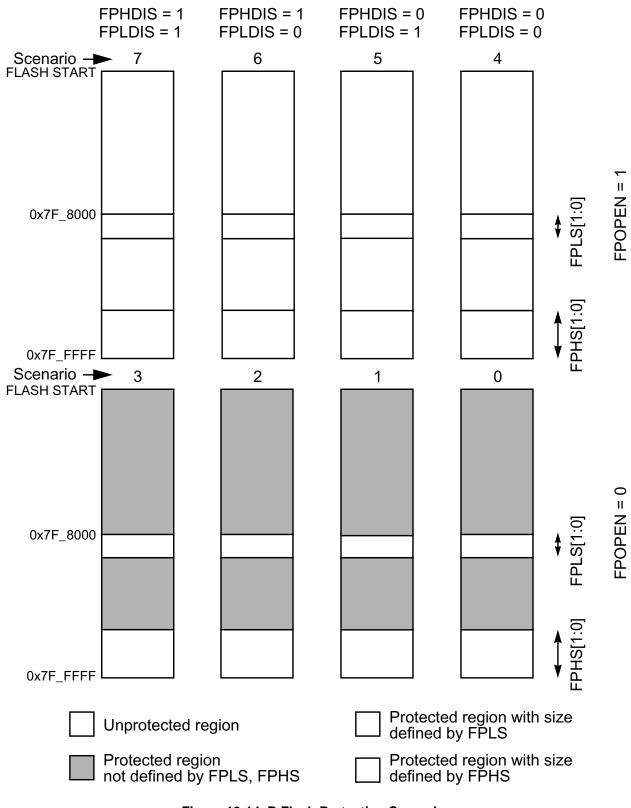

Figure 19-14. P-Flash Protection Scenarios

S12XS Family Reference Manual, Rev. 1.13

### **A.2** ATD Characteristics

This section describes the characteristics of the analog-to-digital converter.

### **ATD Operating Characteristics** A.2.1

The Table A-14 and Table A-15 show conditions under which the ATD operates.

The following constraints exist to obtain full-scale, full range results:

$$V_{SSA} \le V_{RL} \le V_{IN} \le V_{RH} \le V_{DDA}$$

.

This constraint exists since the sample buffer amplifier can not drive beyond the power supply levels that it ties to. If the input level goes outside of this range it will effectively be clipped.

**Table A-14. ATD Operating Characteristics**

| Conditions are shown in Table A-4 unless otherwise noted, supply voltage 3.13 V < V <sub>DDA</sub> < 5.5 V |   |                                                                                                     |                                                                  |                                         |             |                                         |                        |

|------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------|-------------|-----------------------------------------|------------------------|

| Num                                                                                                        | С | Rating                                                                                              | Symbol                                                           | Min                                     | Тур         | Max                                     | Unit                   |

| 1                                                                                                          | D | Reference potential<br>Low<br>High                                                                  | V <sub>RL</sub><br>V <sub>RH</sub>                               | V <sub>SSA</sub><br>V <sub>DDA</sub> /2 | _<br>_      | V <sub>DDA</sub> /2<br>V <sub>DDA</sub> | V                      |

| 2                                                                                                          | D | Voltage difference V <sub>DDX</sub> to V <sub>DDA</sub>                                             | $\Delta_{VDDX}$                                                  | -2.35                                   | 0           | 0.1                                     | V                      |

| 3                                                                                                          | D | Voltage difference V <sub>SSX</sub> to V <sub>SSA</sub>                                             | $\Delta_{VSSX}$                                                  | -0.1                                    | 0           | 0.1                                     | V                      |

| 4                                                                                                          | С | Differential reference voltage <sup>1</sup>                                                         | V <sub>RH</sub> -V <sub>RL</sub>                                 | 3.13                                    | 5.0         | 5.5                                     | V                      |

| 5                                                                                                          | С | ATD Clock Frequency (derived from bus clock via the prescaler bus)                                  | f <sub>ATDCLk</sub>                                              | 0.25                                    | _           | 8.3                                     | MHz                    |

| 6                                                                                                          | Р | ATD Clock Frequency in Stop mode (internal generated temperature and voltage dependent clock, ICLK) |                                                                  | 0.6                                     | 1           | 1.7                                     | MHz                    |

| 7                                                                                                          | D | ADC conversion in stop, recovery time <sup>2</sup>                                                  | t <sub>ATDSTPRCV</sub>                                           | _                                       | _           | 1.5                                     | μs                     |

| 8                                                                                                          | D | ATD Conversion Period <sup>3</sup> 12 bit resolution: 10 bit resolution: 8 bit resolution:          | N <sub>CONV12</sub><br>N <sub>CONV10</sub><br>N <sub>CONV8</sub> | 20<br>19<br>17                          | _<br>_<br>_ | 42<br>41<br>39                          | ATD<br>clock<br>cycles |

Full accuracy is not guaranteed when differential voltage is less than 4.50 V

### A.2.2 **Factors Influencing Accuracy**

Source resistance, source capacitance and current injection have an influence on the accuracy of the ATD. A further factor is that PortAD pins that are configured as output drivers switching.

### A.2.2.1 **Port AD Output Drivers Switching**

PortAD output drivers switching can adversely affect the ATD accuracy whilst converting the analog voltage on other PortAD pins because the output drivers are supplied from the VDDA/VSSA ATD supply pins. Although internal design measures are implemented to minimize the affect of output driver noise, it

S12XS Family Reference Manual, Rev. 1.13

When converting in Stop Mode (ICLKSTP=1) an ATD Stop Recovery time tATDSTPRCV is required to switch back to bus clock

based ATDCLK when leaving Stop Mode. Do not access ATD registers during this time.

The minimum time assumes a sample time of 4 ATD clock cycles. The maximum time assumes a sample time of 24 ATD clock cycles and the discharge feature (SMP\_DIS) enabled, which adds 2 ATD clock cycles.

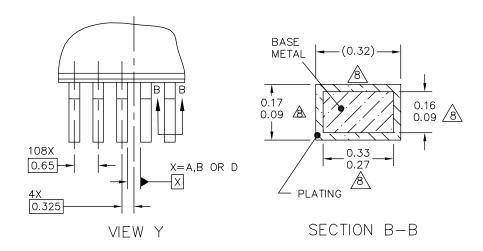

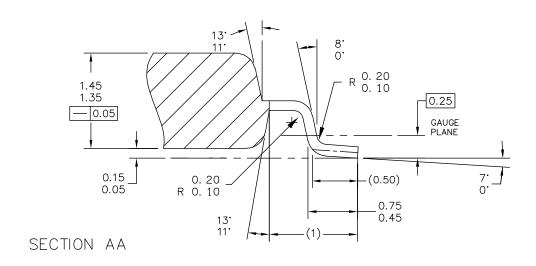

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. |  |              | PRINT VERSION NOT TO SCALE |             |

|------------------------------------------------------|--|--------------|----------------------------|-------------|

| TITLE: 112LD LQFP                                    |  | DOCUMENT NO  | ): 98ASS23330W             | REV: F      |

| 20 X 20 X 1.4                                        |  | CASE NUMBER  | R: 987–03                  | 15 DEC 2006 |

| 0.65 PITCH                                           |  | STANDARD: JE | DEC MS-026 BFA             |             |

Figure B-2. 112-pin LQFP (case no. 987) - page 2

S12XS Family Reference Manual, Rev. 1.13