Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | HCS12X                                                     |

| Core Size                  | 16-Bit                                                     |

| Speed                      | 40MHz                                                      |

| Connectivity               | CANbus, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 44                                                         |

| Program Memory Size        | 64KB (64K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 4K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                               |

| Data Converters            | A/D 8x12b                                                  |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 64-LQFP                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12xs64mae |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 1 Device Overview S12XS Family

# 1.1 Introduction

The new S12XS family of 16-bit micro controllers is a compatible, reduced version of the S12XE family. These families provide an easy approach to develop common platforms from low-end to high-end applications, minimizing the redesign of software and hardware.

Targeted at generic automotive applications and CAN nodes, some typical examples of these applications are: Body Controllers, Occupant Detection, Door Modules, RKE Receivers, Smart Actuators, Lighting Modules and Smart Junction Boxes amongst many others.

The S12XS family retains many of the features of the S12XE family including Error Correction Code (ECC) on Flash memory, a separate Data-Flash Module for code or data storage, a Frequency Modulated Locked Loop (IPLL) that improves the EMC performance and a fast ATD converter.

S12XS family delivers 32-bit performance with all the advantages and efficiencies of a 16-bit MCU while retaining the low cost, power consumption, EMC and code-size efficiency advantages currently enjoyed by users of Freescale's existing 16-bit S12 and S12X MCU families. Like members of other S12X families, the S12XS family runs 16-bit wide accesses without wait states for all peripherals and memories.

The S12XS family is available in 112-pin LQFP, 80-pin QFP, 64-pin LQFP package options and maintains a high level of pin compatibility with the S12XE family. In addition to the I/O ports available in each module, up to 18 further I/O ports are available with interrupt capability allowing Wake-Up from stop or wait modes.

The peripheral set includes MSCAN, SPI, two SCIs, an 8-channel 24-bit periodic interrupt timer, 8-channel 16-bit Timer, 8-channel PWM and up to 16- channel 12-bit ATD converter.

Software controlled peripheral-to-port routing enables access to a flexible mix of the peripheral modules in the lower pin count package options.

### 1.1.1 Features

Features of the S12XS Family are listed here. Please see Table D-1 for memory options and Table D-2 for the peripheral features that are available on the different family members.

- 16-bit CPU12X

- Upward compatible with S12 instruction set with the exception of five Fuzzy instructions (MEM, WAV, WAVR, REV, REVW) which have been removed

- Enhanced indexed addressing

- Access to large data segments independent of PPAGE

# NP

#### **Device Overview S12XS Family**

- INT (interrupt module)

- Seven levels of nested interrupts

- Flexible assignment of interrupt sources to each interrupt level.

- External non-maskable high priority interrupt (XIRQ)

- The following inputs can act as Wake-up Interrupts

- IRQ and non-maskable XIRQ

- CAN receive pins

- SCI receive pins

- Depending on the package option up to 20 pins on ports J, H and P configurable as rising or falling edge sensitive

- MMC (module mapping control)

- DBG (debug module)

- Monitoring of CPU bus with tag-type or force-type breakpoint requests

- 64 x 64-bit circular trace buffer captures change-of-flow or memory access information

- BDM (background debug mode)

- OSC\_LCP (oscillator)

- Low power loop control Pierce oscillator utilizing a 4MHz to 16MHz crystal

- Good noise immunity

- Full-swing Pierce option utilizing a 2MHz to 40MHz crystal

- Transconductance sized for optimum start-up margin for typical crystals

- IPLL (Internally filtered, frequency modulated phase-locked-loop clock generation)

- No external components required

- Configurable option to spread spectrum for reduced EMC radiation (frequency modulation)

- CRG (clock and reset generation)

- COP watchdog

- Real time interrupt

- Clock monitor

- Fast wake up from STOP in self clock mode

- Memory Options

- 64, 128 and 256 Kbyte Flash

- Flash General Features

- 64 data bits plus 8 syndrome ECC (Error Correction Code) bits allow single bit failure correction and double fault detection

- Erase sector size 1024 bytes

- Automated program and erase algorithm

- Protection scheme to prevent accidental program or erase

- Security option to prevent unauthorized access

- Sense-amp margin level setting for reads

- 4 and 8 Kbyte Data Flash space

#### S12XS Family Reference Manual, Rev. 1.13

# NP

#### **Device Overview S12XS Family**

- Time-out interrupt and peripheral triggers

- Start of timers can be aligned

- Up to 8 channel x 8-bit or 4 channel x 16-bit Pulse Width Modulator

- Programmable period and duty cycle per channel

- Center- or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

- Serial Peripheral Interface Module (SPI)

- Configurable for 8 or 16-bit data size

- Full-duplex or single-wire bidirectional

- Double-buffered transmit and receive

- Master or Slave mode

- MSB-first or LSB-first shifting

- Serial clock phase and polarity options

- Two Serial Communication Interfaces (SCI)

- Full-duplex or single wire operation

- Standard mark/space non-return-to-zero (NRZ) format

- Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

- 13-bit baud rate selection

- Programmable character length

- Programmable polarity for transmitter and receiver

- Receive wakeup on active edge

- Break detect and transmit collision detect supporting LIN

- On-Chip Voltage Regulator

- Two parallel, linear voltage regulators with bandgap reference

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR) circuit

- Low-voltage reset (LVR)

- Low-power wake-up timer (API)

- Internal oscillator driving a down counter

- Trimmable to +/-5% accuracy

- Time-out periods range from 0.2ms to ~13s with a 0.2ms resolution

- Input/Output

- Up to 91 general-purpose input/output (I/O) pins depending on the package option and 2 inputonly pins

- Hysteresis and configurable pull up/pull down device on all input pins

- Configurable drive strength on all output pins

- Package Options

- 112-pin low-profile quad flat-pack (LQFP)

- 80-pin quad flat-pack (QFP)

### **1.7 ATD0 Configuration**

### 1.7.1 External Trigger Input Connection

The ATD module includes four external trigger inputs ETRIG0, ETRIG1, ETRIG2, and ETRIG3. The external trigger allows the user to synchronize ATD conversion to external trigger events. Table 1-13 shows the connection of the external trigger inputs.

| External Trigger<br>Input | Connectivity                                |

|---------------------------|---------------------------------------------|

| ETRIG0                    | Pulse width modulator channel 1             |

| ETRIG1                    | Pulse width modulator channel 3             |

| ETRIG2                    | Periodic interrupt timer hardware trigger 0 |

| ETRIG3                    | Periodic interrupt timer hardware trigger 1 |

Table 1-13. ATD0 External Trigger Sources

Consult the ATD section for information about the analog-to-digital converter module. References to freeze mode are equivalent to active BDM mode.

### 1.7.2 ATD0 Channel[17] Connection

Further to the 16 externally available channels, ATD0 features an extra channel[17] that is connected to the internal temperature sensor at device level. To access this channel ATD0 must use the channel encoding SC:CD:CC:CB:CA = 1:0:0:0:1 in ATDCTL5. For more temperature sensor information, please refer to 1.8.1 Temperature Sensor Configuration.

# 1.8 VREG Configuration

The device must be configured with the internal voltage regulator enabled. Operation in conjunction with an external voltage regulator is not supported.

The API trimming register APITR is loaded from the Flash IFR option field at global address 0x40\_00F0 bits[5:0] during the reset sequence. Currently factory programming of this IFR range is not supported.

Read access to reserved VREG register space returns "0". Write accesses have no effect. This device does not support access abort of reserved VREG register space.

### **1.8.1** Temperature Sensor Configuration

The VREG high temperature trimming register bits VREGHTTR[3:0] are loaded from the internal Flash during the reset sequence. To use the high temperature interrupt within the specified limits ( $T_{HTIA}$  and  $T_{HTID}$ ) these bits must be loaded with 0x8. Currently factory programming is not supported.

The device temperature can be monitored on ATD0 channel[17]. The internal bandgap reference voltage can also be mapped to ATD0 analog input channel[17]. The voltage regulator VSEL bit when set, maps the bandgap and, when clear, maps the temperature sensor to ATD0 channel[17].

| Command    | Opcode<br>(hex) | Data | Description                                                                                    |

|------------|-----------------|------|------------------------------------------------------------------------------------------------|

| WRITE_WORD | C8              |      | Write to memory with standard BDM firmware lookup table out of map.<br>Must be aligned access. |

NOTE:

If enabled, ACK will occur when data is ready for transmission for all BDM READ commands and will occur after the write is complete for all BDM WRITE commands.

### 5.4.4 Standard BDM Firmware Commands

Firmware commands are used to access and manipulate CPU resources. The system must be in active BDM to execute standard BDM firmware commands, see Section 5.4.2, "Enabling and Activating BDM". Normal instruction execution is suspended while the CPU executes the firmware located in the standard BDM firmware lookup table. The hardware command BACKGROUND is the usual way to activate BDM.

As the system enters active BDM, the standard BDM firmware lookup table and BDM registers become visible in the on-chip memory map at 0x7FFF00–0x7FFFFF, and the CPU begins executing the standard BDM firmware. The standard BDM firmware watches for serial commands and executes them as they are received.

The firmware commands are shown in Table 5-7.

### 6.4.5.3 Trace Buffer Organization

Referring to Table 6-40. ADRH, ADRM, ADRL denote address high, middle and low byte respectively. INF bytes contain control information (R/W, S/D etc.). The numerical suffix indicates which tracing step. The information format for Loop1 Mode and PurePC Mode is the same as that of Normal Mode. Whilst tracing in Normal or Loop1 modes each array line contains 2 data entries, thus in this case the DBGCNT[0] is incremented after each separate entry. In Detail mode DBGCNT[0] remains cleared whilst the other DBGCNT bits are incremented on each trace buffer entry.

When a COF occurs a trace buffer entry is made and the corresponding CDV bit is set.

Single byte data accesses in Detail Mode are always stored to the low byte of the trace buffer (CDATAL) and the high byte is cleared. When tracing word accesses, the byte at the lower address is always stored to trace buffer byte3 and the byte at the higher address is stored to byte2.

| Mada        |        |        |        | 8-Byte Wide | Word Buffer |         |       |       |  |

|-------------|--------|--------|--------|-------------|-------------|---------|-------|-------|--|

| Mode        | 7      | 6      | 5      | 4           | 3           | 2       | 1     | 0     |  |

| S12XCPU     | CXINF1 | CADRH1 | CADRM1 | CADRL1      | CDATAH1     | CDATAL1 |       |       |  |

| Detail      | CXINF2 | CADRH2 | CADRM2 | CADRL2      | CDATAH2     | CDATAL2 |       |       |  |

| CPU12X      | CINF1  | CPCH1  | CPCM1  | CPCL1       | CINF0       | CPCH0   | CPCM0 | CPCL0 |  |

| Other Modes | CINF3  | CPCH3  | CPCM3  | CPCL3       | CINF2       | CPCH2   | CPCM2 | CPCL2 |  |

#### Table 6-40. Trace Buffer Organization

| BRK | TALIGN   | DBGBRK | Breakpoint Alignment                                                                                                       |  |  |  |

|-----|----------|--------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0   | 00       | 0      | Fill Trace Buffer until trigger<br>(no breakpoints — keep running)                                                         |  |  |  |

| 0   | 00       | 1      | Fill Trace Buffer until trigger, then breakpoint request occurs                                                            |  |  |  |

| 0   | 01       | 0      | Start Trace Buffer at trigger<br>(no breakpoints — keep running)                                                           |  |  |  |

| 0   | 01       | 1      | Start Trace Buffer at trigger<br>A breakpoint request occurs when Trace Buffer is full                                     |  |  |  |

| 0   | 10       | 0      | Store a further 32 Trace Buffer line entries after trigger<br>(no breakpoints — keep running)                              |  |  |  |

| 0   | 10       | 1      | Store a further 32 Trace Buffer line entries after trigger<br>Request breakpoint after the 32 further Trace Buffer entries |  |  |  |

| 1   | 00,01,10 | 1      | Terminate tracing and generate breakpoint immediately on trigger                                                           |  |  |  |

| 1   | 00,01,10 | 0      | Terminate tracing immediately on trigger                                                                                   |  |  |  |

| х   | 11       | x      | Reserved                                                                                                                   |  |  |  |

#### Table 6-43. Breakpoint Setup

### 6.4.7.2 Breakpoints Generated Via The TRIG Bit

If a TRIG triggers occur, the Final State is entered. If a tracing session is selected by TSOURCE, breakpoints are requested when the tracing session has completed, thus if Begin or Mid aligned triggering is selected, the breakpoint is requested only on completion of the subsequent trace (see Table 6-43). If no tracing session is selected, breakpoints are requested immediately. TRIG breakpoints are possible even if the S12XDBG module is disarmed.

#### 6.4.7.3 S12XDBG Breakpoint Priorities

If a TRIG trigger occurs after Begin or Mid aligned tracing has already been triggered by a comparator instigated transition to Final State, then TRIG no longer has an effect. When the associated tracing session is complete, the breakpoint occurs. Similarly if a TRIG is followed by a subsequent trigger from a comparator channel, it has no effect, since tracing has already started.

#### 6.4.7.3.1 S12XDBG Breakpoint Priorities And BDM Interfacing

Breakpoint operation is dependent on the state of the S12XBDM module. If the S12XBDM module is active, the CPU12X is executing out of BDM firmware and S12X breakpoints are disabled. In addition, while executing a BDM TRACE command, tagging into BDM is disabled. If BDM is not active, the breakpoint will give priority to BDM requests over SWI requests if the breakpoint coincides with a SWI instruction in the user's code. On returning from BDM, the SWI from user code gets executed.

| DBGBRK<br>(DBGC1[3]) | BDM Bit<br>(DBGC1[4]) | BDM<br>Enabled | BDM<br>Active | S12X Breakpoint<br>Mapping |

|----------------------|-----------------------|----------------|---------------|----------------------------|

| 0                    | Х                     | Х              | Х             | No Breakpoint              |

| 1                    | 0                     | Х              | 0             | Breakpoint to SWI          |

| 1                    | 0                     | Х              | 1             | No Breakpoint              |

### 8.3.2 Register Descriptions

This section describes in address order all the S12XECRG registers and their individual bits.

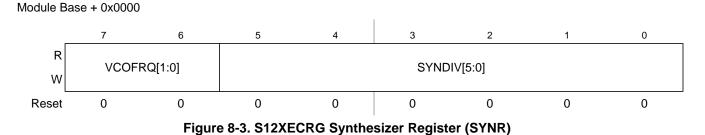

#### 8.3.2.1 S12XECRG Synthesizer Register (SYNR)

The SYNR register controls the multiplication factor of the IPLL and selects the VCO frequency range.

Read: Anytime

Write: Anytime except if PLLSEL = 1

#### NOTE

Write to this register initializes the lock detector bit.

$$f_{VCO} = 2 \times f_{OSC} \times \frac{(SYNDIV + 1)}{(REFDIV + 1)}$$

$$f_{PLL} = \frac{f_{VCO}}{2 \times POSTDIV}$$

$$f_{BUS} = \frac{f_{PLL}}{2}$$

#### NOTE

$f_{VCO}$  must be within the specified VCO frequency lock range. F.<sub>BUS</sub> (Bus Clock) must not exceed the specified maximum. If POSTDIV = \$00 then  $f_{PLL}$  is same as  $f_{VCO}$  (divide by one).

The VCOFRQ[1:0] bit are used to configure the VCO gain for optimal stability and lock time. For correct IPLL operation the VCOFRQ[1:0] bits have to be selected according to the actual target VCOCLK frequency as shown in Table 8-2. Setting the VCOFRQ[1:0] bits wrong can result in a non functional IPLL (no locking and/or insufficient stability).

| VCOCLK Frequency Ranges            | VCOFRQ[1:0] |

|------------------------------------|-------------|

| 32MHz <= f <sub>VCO</sub> <= 48MHz | 00          |

| 48MHz < f <sub>VCO</sub> <= 80MHz  | 01          |

| Reserved                           | 10          |

| 80MHz < f <sub>VCO</sub> <= 120MHz | 11          |

Table 8-2. VCO Clock Frequency Selection

S12XE Clocks and Reset Generator (S12XECRGV1)

|            | RTR[6:4] =                  |                             |                             |                              |                              |                              |                               |                               |  |  |

|------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------------------------------|-------------------------------|-------------------------------|--|--|

| RTR[3:0]   | 000<br>(1x10 <sup>3</sup> ) | 001<br>(2x10 <sup>3</sup> ) | 010<br>(5x10 <sup>3</sup> ) | 011<br>(10x10 <sup>3</sup> ) | 100<br>(20x10 <sup>3</sup> ) | 101<br>(50x10 <sup>3</sup> ) | 110<br>(100x10 <sup>3</sup> ) | 111<br>(200x10 <sup>3</sup> ) |  |  |

| 0110 (÷7)  | 7x10 <sup>3</sup>           | 14x10 <sup>3</sup>          | 35x10 <sup>3</sup>          | 70x10 <sup>3</sup>           | 140x10 <sup>3</sup>          | 350x10 <sup>3</sup>          | 700x10 <sup>3</sup>           | 1.4x10 <sup>6</sup>           |  |  |

| 0111 (÷8)  | 8x10 <sup>3</sup>           | 16x10 <sup>3</sup>          | 40x10 <sup>3</sup>          | 80x10 <sup>3</sup>           | 160x10 <sup>3</sup>          | 400x10 <sup>3</sup>          | 800x10 <sup>3</sup>           | 1.6x10 <sup>6</sup>           |  |  |

| 1000 (÷9)  | 9x10 <sup>3</sup>           | 18x10 <sup>3</sup>          | 45x10 <sup>3</sup>          | 90x10 <sup>3</sup>           | 180x10 <sup>3</sup>          | 450x10 <sup>3</sup>          | 900x10 <sup>3</sup>           | 1.8x10 <sup>6</sup>           |  |  |

| 1001 (÷10) | 10 x10 <sup>3</sup>         | 20x10 <sup>3</sup>          | 50x10 <sup>3</sup>          | 100x10 <sup>3</sup>          | 200x10 <sup>3</sup>          | 500x10 <sup>3</sup>          | 1x10 <sup>6</sup>             | 2x10 <sup>6</sup>             |  |  |

| 1010 (÷11) | 11 x10 <sup>3</sup>         | 22x10 <sup>3</sup>          | 55x10 <sup>3</sup>          | 110x10 <sup>3</sup>          | 220x10 <sup>3</sup>          | 550x10 <sup>3</sup>          | 1.1x10 <sup>6</sup>           | 2.2x10 <sup>6</sup>           |  |  |

| 1011 (÷12) | 12x10 <sup>3</sup>          | 24x10 <sup>3</sup>          | 60x10 <sup>3</sup>          | 120x10 <sup>3</sup>          | 240x10 <sup>3</sup>          | 600x10 <sup>3</sup>          | 1.2x10 <sup>6</sup>           | 2.4x10 <sup>6</sup>           |  |  |

| 1100 (÷13) | 13x10 <sup>3</sup>          | 26x10 <sup>3</sup>          | 65x10 <sup>3</sup>          | 130x10 <sup>3</sup>          | 260x10 <sup>3</sup>          | 650x10 <sup>3</sup>          | 1.3x10 <sup>6</sup>           | 2.6x10 <sup>6</sup>           |  |  |

| 1101 (÷14) | 14x10 <sup>3</sup>          | 28x10 <sup>3</sup>          | 70x10 <sup>3</sup>          | 140x10 <sup>3</sup>          | 280x10 <sup>3</sup>          | 700x10 <sup>3</sup>          | 1.4x10 <sup>6</sup>           | 2.8x10 <sup>6</sup>           |  |  |

| 1110 (÷15) | 15x10 <sup>3</sup>          | 30x10 <sup>3</sup>          | 75x10 <sup>3</sup>          | 150x10 <sup>3</sup>          | 300x10 <sup>3</sup>          | 750x10 <sup>3</sup>          | 1.5x10 <sup>6</sup>           | 3x10 <sup>6</sup>             |  |  |

| 1111 (÷16) | 16x10 <sup>3</sup>          | 32x10 <sup>3</sup>          | 80x10 <sup>3</sup>          | 160x10 <sup>3</sup>          | 320x10 <sup>3</sup>          | 800x10 <sup>3</sup>          | 1.6x10 <sup>6</sup>           | 3.2x10 <sup>6</sup>           |  |  |

Table 8-11. RTI Frequency Divide Rates for RTDEC=1

### 8.3.2.9 S12XECRG COP Control Register (COPCTL)

This register controls the COP (Computer Operating Properly) watchdog.

Module Base + 0x0008

|                    | 7    | 6     | 5       | 4 | 3 | 2   | 1   | 0   |

|--------------------|------|-------|---------|---|---|-----|-----|-----|

| R                  |      | RSBCK | 0       | 0 | 0 | CR2 | CR1 | CR0 |

| W                  | WCOP | RODUN | WRTMASK |   |   |     |     |     |

| Reset <sup>1</sup> | 0    | 0     | 0       | 0 | 0 | 0   | 0   | 0   |

1. Refer to Device User Guide (Section: S12XECRG) for reset values of WCOP, CR2, CR1 and CR0.

= Unimplemented or Reserved

#### Figure 8-11. S12XECRG COP Control Register (COPCTL)

Read: Anytime

Write:

- 1. RSBCK: anytime in special modes; write to "1" but not to "0" in all other modes

- 2. WCOP, CR2, CR1, CR0:

- Anytime in special modes

- Write once in all other modes

- Writing CR[2:0] to "000" has no effect, but counts for the "write once" condition.

- Writing WCOP to "0" has no effect, but counts for the "write once" condition.

Freescale's Scalable Controller Area Network (S12MSCANV3)

### 11.1.3 Features

The basic features of the MSCAN are as follows:

- Implementation of the CAN protocol Version 2.0A/B

- Standard and extended data frames

- Zero to eight bytes data length

- Programmable bit rate up to  $1 \text{ Mbps}^1$

- Support for remote frames

- Five receive buffers with FIFO storage scheme

- Three transmit buffers with internal prioritization using a "local priority" concept

- Flexible maskable identifier filter supports two full-size (32-bit) extended identifier filters, or four 16-bit filters, or eight 8-bit filters

- Programmable wake-up functionality with integrated low-pass filter

- Programmable loopback mode supports self-test operation

- Programmable listen-only mode for monitoring of CAN bus

- Programmable bus-off recovery functionality

- Separate signalling and interrupt capabilities for all CAN receiver and transmitter error states (warning, error passive, bus-off)

- Programmable MSCAN clock source either bus clock or oscillator clock

- Internal timer for time-stamping of received and transmitted messages

- Three low-power modes: sleep, power down, and MSCAN enable

- Global initialization of configuration registers

### 11.1.4 Modes of Operation

For a description of the specific MSCAN modes and the module operation related to the system operating modes refer to Section 11.4.4, "Modes of Operation".

1. Depending on the actual bit timing and the clock jitter of the PLL.

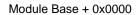

### 14.3.2.3 SCI Alternative Status Register 1 (SCIASR1)

Read: Anytime, if AMAP = 1

Write: Anytime, if AMAP = 1

#### Table 14-6. SCIASR1 Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RXEDGIF | <ul> <li>Receive Input Active Edge Interrupt Flag — RXEDGIF is asserted, if an active edge (falling if RXPOL = 0, rising if RXPOL = 1) on the RXD input occurs. RXEDGIF bit is cleared by writing a "1" to it.</li> <li>0 No active receive on the receive input has occurred</li> <li>1 An active edge on the receive input has occurred</li> </ul>                    |

| 2<br>BERRV   | <ul> <li>Bit Error Value — BERRV reflects the state of the RXD input when the bit error detect circuitry is enabled and a mismatch to the expected value happened. The value is only meaningful, if BERRIF = 1.</li> <li>0 A low input was sampled, when a high was expected</li> <li>1 A high input reassembled, when a low was expected</li> </ul>                    |

| 1<br>BERRIF  | <b>Bit Error Interrupt Flag</b> — BERRIF is asserted, when the bit error detect circuitry is enabled and if the value sampled at the RXD input does not match the transmitted value. If the BERRIE interrupt enable bit is set an interrupt will be generated. The BERRIF bit is cleared by writing a "1" to it.<br>0 No mismatch detected<br>1 A mismatch has occurred |

| 0<br>BKDIF   | <ul> <li>Break Detect Interrupt Flag — BKDIF is asserted, if the break detect circuitry is enabled and a break signal is received. If the BKDIE interrupt enable bit is set an interrupt will be generated. The BKDIF bit is cleared by writing a "1" to it.</li> <li>0 No break signal was received</li> <li>1 A break signal was received</li> </ul>                  |

```

Serial Peripheral Interface (S12SPIV5)

```

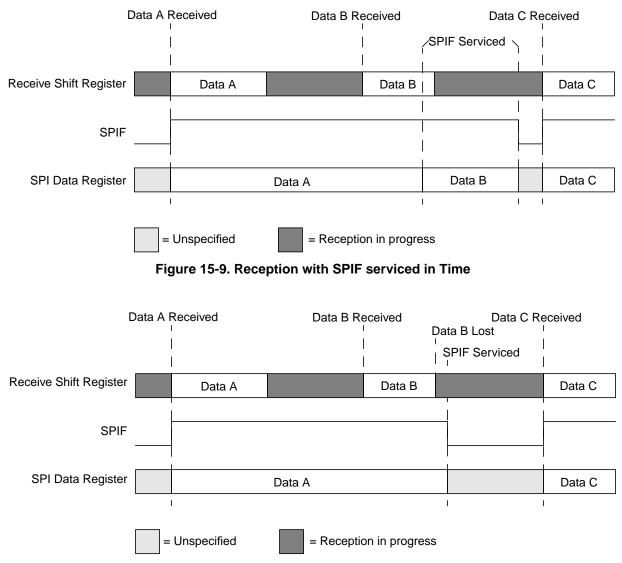

Figure 15-10. Reception with SPIF serviced too late

# 15.4 Functional Description

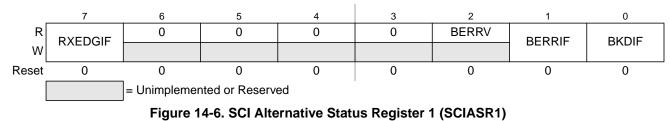

The SPI module allows a duplex, synchronous, serial communication between the MCU and peripheral devices. Software can poll the SPI status flags or SPI operation can be interrupt driven.

The SPI system is enabled by setting the SPI enable (SPE) bit in SPI control register 1. While SPE is set, the four associated SPI port pins are dedicated to the SPI function as:

- Slave select  $(\overline{SS})$

- Serial clock (SCK)

- Master out/slave in (MOSI)

- Master in/slave out (MISO)

NP

Timer Module (TIM16B8CV2)

| Register<br>Name          |        | Bit 7   | 6       | 5       | 4       | 3       | 2       | 1      | Bit 0  |

|---------------------------|--------|---------|---------|---------|---------|---------|---------|--------|--------|

| 0x0006<br>TSCR1           | R<br>W | TEN     | TSWAI   | TSFRZ   | TFFCA   | PRNT    | 0       | 0      | 0      |

| 0x0007<br>TTOV            | R<br>W | TOV7    | TOV6    | TOV5    | TOV4    | TOV3    | TOV2    | TOV1   | TOV0   |

| 0x0008<br>TCTL1           | R<br>W | OM7     | OL7     | OM6     | OL6     | OM5     | OL5     | OM4    | OL4    |

| 0x0009<br>TCTL2           | R<br>W | OM3     | OL3     | OM2     | OL2     | OM1     | OL1     | OM0    | OL0    |

| 0x000A<br>TCTL3           | R<br>W | EDG7B   | EDG7A   | EDG6B   | EDG6A   | EDG5B   | EDG5A   | EDG4B  | EDG4A  |

| 0x000B<br>TCTL4           | R<br>W | EDG3B   | EDG3A   | EDG2B   | EDG2A   | EDG1B   | EDG1A   | EDG0B  | EDG0A  |

| 0x000C<br>TIE             | R<br>W | C7I     | C6I     | C5I     | C4I     | C3I     | C2I     | C1I    | COI    |

| 0x000D<br>TSCR2           | R<br>W | ΤΟΙ     | 0       | 0       | 0       | TCRE    | PR2     | PR1    | PR0    |

| 0x000E<br>TFLG1           | R<br>W | C7F     | C6F     | C5F     | C4F     | C3F     | C2F     | C1F    | C0F    |

| 0x000F<br>TFLG2           | R<br>W | TOF     | 0       | 0       | 0       | 0       | 0       | 0      | 0      |

| 0x0010–0x001F             | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| TCxH–TCxL                 | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x0020<br>PACTL           | R<br>W | 0       | PAEN    | PAMOD   | PEDGE   | CLK1    | CLK0    | PAOVI  | PAI    |

| 0x0021<br>PAFLG           | R<br>W | 0       | 0       | 0       | 0       | 0       | 0       | PAOVF  | PAIF   |

| 0x0022<br>PACNTH          | R<br>W | PACNT15 | PACNT14 | PACNT13 | PACNT12 | PACNT11 | PACNT10 | PACNT9 | PACNT8 |

| 0x0023<br>PACNTL          | R<br>W | PACNT7  | PACNT6  | PACNT5  | PACNT4  | PACNT3  | PACNT2  | PACNT1 | PACNT0 |

| 0x0024–0x002B<br>Reserved | R<br>W |         |         |         |         |         |         |        |        |

= Unimplemented or Reserved

Figure 16-5. TIM16B8CV2 Register Summary (Sheet 2 of 3)

S12XS Family Reference Manual Rev. 1.13

Timer Module (TIM16B8CV2)

# 16.6.1 Channel [7:0] Interrupt (C[7:0]F)

This active high outputs will be asserted by the module to request a timer channel 7 - 0 interrupt to be serviced by the system controller.

### 16.6.2 Pulse Accumulator Input Interrupt (PAOVI)

This active high output will be asserted by the module to request a timer pulse accumulator input interrupt to be serviced by the system controller.

### 16.6.3 Pulse Accumulator Overflow Interrupt (PAOVF)

This active high output will be asserted by the module to request a timer pulse accumulator overflow interrupt to be serviced by the system controller.

### 16.6.4 Timer Overflow Interrupt (TOF)

This active high output will be asserted by the module to request a timer overflow interrupt to be serviced by the system controller.

Voltage Regulator (S12VREGL3V3V1)

3. Shutdown mode

Controlled by VREGEN (see device level specification for connectivity of VREGEN).

This mode is characterized by minimum power consumption. The regulator outputs are in a highimpedance state, only the POR feature is available, LVD, LVR and HTD are disabled. The API internal RC oscillator clock is not available.

This mode must be used to disable the chip internal regulator VREG\_3V3, i.e., to bypass the VREG\_3V3 to use external supplies.

### 17.1.3 Block Diagram

Figure 17-1 shows the function principle of VREG\_3V3 by means of a block diagram. The regulator core REG consists of three parallel subblocks, REG1, REG2 and REG3, providing three independent output voltages.

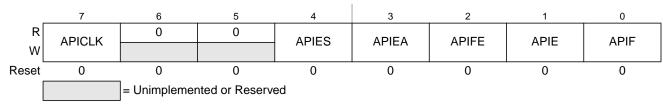

### 17.3.2.3 Autonomous Periodical Interrupt Control Register (VREGAPICL)

The VREGAPICL register allows the configuration of the VREG\_3V3 autonomous periodical interrupt features.

0x02F2

#### Figure 17-3. Autonomous Periodical Interrupt Control Register (VREGAPICL)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7<br>APICLK | <ul> <li>Autonomous Periodical Interrupt Clock Select Bit — Selects the clock source for the API. Writable only if APIFE = 0; APICLK cannot be changed if APIFE is set by the same write operation.</li> <li>0 Autonomous periodical interrupt clock used as source.</li> <li>1 Bus clock used as source.</li> </ul>                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 4<br>APIES  | Autonomous Periodical Interrupt External Select Bit — Selects the waveform at the external pin.If set, at the external pin a clock is visible with 2 times the selected API Period (Table 17-10). If not set, at the external pin will be a high pulse at the end of every selected period with the size of half of the min period (Table 17-10). See device level specification for connectivity.<br>0 At the external periodic high pulses are visible, if APIEA and APIFE is set.<br>1 At the external pin a clock is visible, if APIEA and APIFE is set. |  |  |  |  |  |  |  |

| 3<br>APIEA  | <ul> <li>Autonomous Periodical Interrupt External Access Enable Bit — If set, the waveform selected by bit APIES can be accessed externally. See device level specification for connectivity.</li> <li>Waveform selected by APIES can not be accessed externally.</li> <li>Waveform selected by APIES can be accessed externally, if APIFE is set.</li> </ul>                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 2<br>APIFE  | <ul> <li>Autonomous Periodical Interrupt Feature Enable Bit — Enables the API feature and starts the API timer when set.</li> <li>0 Autonomous periodical interrupt is disabled.</li> <li>1 Autonomous periodical interrupt is enabled and timer starts running.</li> </ul>                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 1<br>APIE   | Autonomous Periodical Interrupt Enable Bit         0 API interrupt request is disabled.         1 API interrupt will be requested whenever APIF is set.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 0<br>APIF   | <ul> <li>Autonomous Periodical Interrupt Flag — APIF is set to 1 when the in the API configured time has elapsed.<br/>This flag can only be cleared by writing a 1 to it. Clearing of the flag has precedence over setting.<br/>Writing a 0 has no effect. If enabled (APIE = 1), APIF causes an interrupt request.</li> <li>0 API timeout has not yet occurred.</li> <li>1 API timeout has occurred.</li> </ul>                                                                                                                                             |  |  |  |  |  |  |  |

<sup>1</sup> Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 20.5.

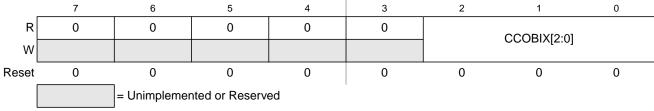

#### 20.3.2.3 Flash CCOB Index Register (FCCOBIX)

The FCCOBIX register is used to index the FCCOB register for Flash memory operations.

Offset Module Base + 0x0002

#### Figure 20-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

#### Table 20-11. FCCOBIX Field Descriptions

| Field              | Description                                                                                                                                                                                                                            |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2–0<br>CCOBIX[1:0] | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See Section 20.3.2.11, "Flash Common Command Object Register (FCCOB)," for more details. |

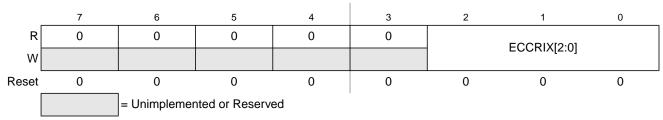

#### 20.3.2.4 Flash ECCR Index Register (FECCRIX)

The FECCRIX register is used to index the FECCR register for ECC fault reporting.

Offset Module Base + 0x0003

#### Figure 20-8. FECCR Index Register (FECCRIX)

ECCRIX bits are readable and writable while remaining bits read 0 and are not writable.

#### Table 20-12. FECCRIX Field Descriptions

| Field              | Description                                                                                                                                                                                                     |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0<br>ECCRIX[2:0] | <b>ECC Error Register Index</b> — The ECCRIX bits are used to select which word of the FECCR register array is being read. See Section 20.3.2.14, "Flash ECC Error Results Register (FECCR)," for more details. |

S12XS Family Reference Manual, Rev. 1.13

#### 64 KByte Flash Module (S12XFTMR64K1V1)

P-Flash phrase containing the D-Flash protection byte during the reset sequence, the DPOPEN bit will be cleared and DPS bits will be set to leave the D-Flash memory fully protected.

Trying to alter data in any protected area in the D-Flash memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. Block erase of the D-Flash memory is not possible if any of the D-Flash sectors are protected.

| Field           | Description                                                                                                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DPOPEN     | <ul> <li>D-Flash Protection Control</li> <li>Enables D-Flash memory protection from program and erase with protected address range defined by DPS bits</li> <li>Disables D-Flash memory protection from program and erase</li> </ul> |

| 4–0<br>DPS[4:0] | <b>D-Flash Protection Size</b> — The DPS[4:0] bits determine the size of the protected area in the D-Flash memory as shown in Table 20-23.                                                                                           |

#### Table 20-22. DFPROT Field Descriptions

| Global Address Range  | Protected Size                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x10_0000 - 0x10_00FF | 256 bytes                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x10_0000 - 0x10_01FF | 512 bytes                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x10_0000 - 0x10_02FF | 768 bytes                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x10_0000 – 0x10_03FF | 1024 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_04FF | 1280 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_05FF | 1536 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_06FF | 1792 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_07FF | 2048 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_08FF | 2304 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_09FF | 2560 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 – 0x10_0AFF | 2816 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 – 0x10_0BFF | 3072 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_0CFF | 3328 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 – 0x10_0DFF | 3584 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_0EFF | 3840 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 – 0x10_0FFF | 4096 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | 0x10_0000 - 0x10_00FF<br>0x10_0000 - 0x10_01FF<br>0x10_0000 - 0x10_02FF<br>0x10_0000 - 0x10_03FF<br>0x10_0000 - 0x10_03FF<br>0x10_0000 - 0x10_05FF<br>0x10_0000 - 0x10_05FF<br>0x10_0000 - 0x10_07FF<br>0x10_0000 - 0x10_08FF<br>0x10_0000 - 0x10_08FF |

#### Table 20-23. D-Flash Protection Address Range

#### 20.3.2.11 Flash Common Command Object Register (FCCOB)

The FCCOB is an array of six words addressed via the CCOBIX index found in the FCCOBIX register. Byte wide reads and writes are allowed to the FCCOB register. 64 KByte Flash Module (S12XFTMR64K1V1)

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |  |  |  |

|-------------|------|-------------------------------------------|--|--|--|

| 011         | HI   | Data 1 [15:8]                             |  |  |  |

|             | LO   | Data 1 [7:0]                              |  |  |  |

| 100         | HI   | Data 2 [15:8]                             |  |  |  |

| 100         | LO   | Data 2 [7:0]                              |  |  |  |

| 101         | HI   | Data 3 [15:8]                             |  |  |  |

| 101         | LO   | Data 3 [7:0]                              |  |  |  |

Table 20-24. FCCOB - NVM Command Mode (Typical Usage)

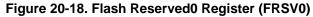

### 20.3.2.12 Flash Reserved0 Register (FRSV0)

This Flash register is reserved for factory testing.

All bits in the FRSV0 register read 0 and are not writable.

### 20.3.2.13 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

All bits in the FRSV1 register read 0 and are not writable.

### 20.3.2.14 Flash ECC Error Results Register (FECCR)

The FECCR registers contain the result of a detected ECC fault for both single bit and double bit faults. The FECCR register provides access to several ECC related fields as defined by the ECCRIX index bits in the FECCRIX register (see Section 20.3.2.4). Once ECC fault information has been stored, no other

```

Detailed Register Address Map

```

#### 0x02C0–0x02EF Analog-to-Digital Converter 12-Bit 16-Channel (ATD0) Map (continued)

|                                       |            |        |        |        |        |        |        | -      |        |        |

|---------------------------------------|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Address                               | Name       | _      | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| 0x02CF                                | ATD0CMPHTL | R<br>W | CMPHT7 | CMPHT6 | CMPHT5 | CMPHT4 | CMPHT3 | CMPHT2 | CMPHT1 | CMPHT0 |

| 0x02D0                                | ATD0DR0H   | R<br>W | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02D1                                | ATD0DR0L   | R<br>W | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02D2                                | ATD0DR1H   | R<br>W | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02D3                                | ATD0DR1L   | R<br>W | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02D4                                | ATD0DR2H   | R<br>W | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02D5                                | ATD0DR2L   | R<br>W | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02D6                                | ATD0DR3H   | R<br>W | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02D7                                | ATD0DR3L   | R<br>W | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02D8                                | ATD0DR4H   | R<br>W | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02D9                                | ATD0DR4L   | R<br>W | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02DA                                | ATD0DR5H   | R<br>W | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02DB                                | ATD0DR5L   | R<br>W | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02DC                                | ATD0DR6H   | R<br>W | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02DD                                | ATD0DR6L   | R<br>W | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02DE                                | ATD0DR7H   | R<br>W | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02DF                                | ATD0DR7L   | R<br>W | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02E0                                | ATD0DR8H   | R<br>W | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02E1                                | ATD0DR8L   | R      | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02E2                                | ATD0DR9H   | W<br>R | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02E3                                | ATD0DR9L   | W<br>R | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| 0x02E4                                | ATD0DR10H  | W<br>R | Bit15  | 14     | 13     | 12     | 11     | 10     | 9      | Bit8   |

| 0x02E5                                | ATD0DR10L  | W<br>R | Bit7   | Bit6   | 0      | 0      | 0      | 0      | 0      | 0      |

| · · · · · · · · · · · · · · · · · · · |            | W      |        |        |        |        |        |        |        |        |