Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 40MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 59                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 8x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs128j1caa |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 2.3.1  | Memory Map                                           | 65    |

|--------|------------------------------------------------------|-------|

| 2.3.2  | Register Descriptions                                |       |

| 2.3.3  | Port A Data Register (PORTA)                         | 75    |

| 2.3.4  | Port B Data Register (PORTB)                         |       |

| 2.3.5  | Port A Data Direction Register (DDRA)                | 76    |

| 2.3.6  | Port B Data Direction Register (DDRB)                | 76    |

| 2.3.7  | PIM Reserved Registers                               |       |

| 2.3.8  | Port E Data Register (PORTE)                         |       |

| 2.3.9  | Port E Data Direction Register (DDRE)                | 78    |

| 2.3.10 | Ports ABEK, BKGD pin Pull-up Control Register (PUCR) | 79    |

| 2.3.11 | Ports ABEK Reduced Drive Register (RDRIV)            | 80    |

| 2.3.12 | ECLK Control Register (ECLKCTL)                      | 81    |

|        | PIM Reserved Register                                |       |

| 2.3.14 | IRQ Control Register (IRQCR)                         | 83    |

| 2.3.15 | PIM Reserved Register PIMTEST                        | 83    |

| 2.3.16 | Port K Data Register (PORTK)                         | 84    |

| 2.3.17 | Port K Data Direction Register (DDRK)                | 84    |

| 2.3.18 | Port T Data Register (PTT)                           | 85    |

| 2.3.19 | Port T Input Register (PTIT)                         | 86    |

| 2.3.20 | Port T Data Direction Register (DDRT)                | 87    |

| 2.3.21 | Port T Reduced Drive Register (RDRT)                 | 87    |

| 2.3.22 | Port T Pull Device Enable Register (PERT)            | 88    |

|        | Port T Polarity Select Register (PPST)               |       |

|        | PIM Reserved Register                                |       |

|        | Port T Routing Register (PTTRR)                      |       |

|        | Port S Data Register (PTS)                           |       |

|        | Port S Input Register (PTIS)                         |       |

|        | Port S Data Direction Register (DDRS)                |       |

|        | Port S Reduced Drive Register (RDRS)                 |       |

|        | Port S Pull Device Enable Register (PERS)            |       |

|        | Port S Polarity Select Register (PPSS)               |       |

|        | Port S Wired-Or Mode Register (WOMS)                 |       |

|        | PIM Reserved Register                                |       |

|        | Port M Data Register (PTM)                           |       |

|        | Port M Input Register (PTIM)                         |       |

|        | Port M Data Direction Register (DDRM)                |       |

|        | Port M Reduced Drive Register (RDRM)                 |       |

|        | Port M Pull Device Enable Register (PERM)            |       |

|        | Port M Polarity Select Register (PPSM)               |       |

|        | Port M Wired-Or Mode Register (WOMM)                 |       |

|        | Module Routing Register (MODRR)                      |       |

|        | Port P Data Register (PTP)                           |       |

|        | Port P Input Register (PTIP)                         |       |

|        | Port P Data Direction Register (DDRP)                |       |

| 2.3.45 | Port P Reduced Drive Register (RDRP)                 | . 106 |

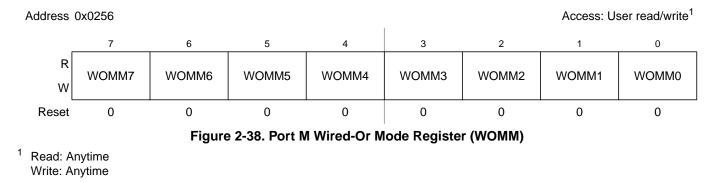

# 2.3.40 Port M Wired-Or Mode Register (WOMM)

#### Table 2-36. WOMM Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>WOMM | <b>Port M wired-or mode</b> —Enable open-drain functionality on output pin<br>This bit configures an output pin as wired-or (open-drain) or push-pull independent of the function used on the pins.<br>In wired-or mode a logic "0" is driven active low while a logic "1" remains undriven. This allows a multipoint<br>connection of several serial modules. The bit has no influence on pins used as input. |

|             | <ol> <li>Output buffer operates as open-drain output.</li> <li>Output buffer operates as push-pull output.</li> </ol>                                                                                                                                                                                                                                                                                          |

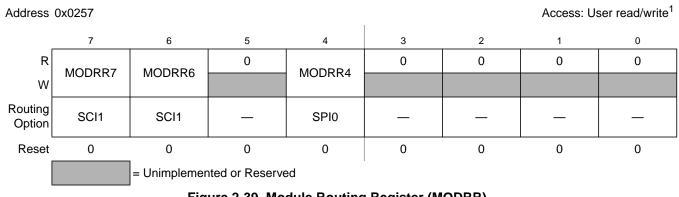

# 2.3.41 Module Routing Register (MODRR)

Figure 2-39. Module Routing Register (MODRR)

<sup>1</sup> Read: Anytime Write: Anytime

This register configures the re-routing of SCI1 and SPI0 on alternative ports.

| MOD | RRx | Related Pins |     |  |  |  |  |

|-----|-----|--------------|-----|--|--|--|--|

| 7   | 6   | TXD          | RXD |  |  |  |  |

#### Table 2-37. SCI1 Routing

Memory Mapping Control (S12XMMCV4)

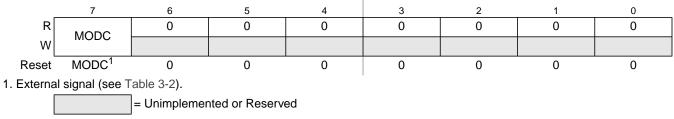

# 3.3.2.1 Mode Register (MODE)

Address: 0x000B PRR

Figure 3-3. Mode Register (MODE)

Read: Anytime. Write: Only if a transition is allowed (see Figure 3-5).

The MODE bits of the MODE register are used to establish the MCU operating mode.

| Field     | Description                                                                                                                                                                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>MODC | <b>Mode Select Bit</b> — This bit controls the current operating mode during <b>RESET</b> high (inactive). The external mode pin MODC determines the operating mode during <b>RESET</b> low (active). The state of the pin is latched into the respective register bit after the <b>RESET</b> signal goes inactive (see Figure 3-3). |

|           | Write restrictions exist to disallow transitions between certain modes. Figure 3-5 illustrates all allowed mode changes. Attempting non authorized transitions will not change the MODE bits, but it will block further writes to these register bits except in special modes.                                                       |

|           | Write accesses to the MODE register are blocked when the device is secured.                                                                                                                                                                                                                                                          |

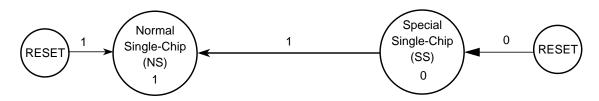

Transition done by external pins (MODC)

Transition done by write access to the MODE register

Figure 3-5. Mode Transition Diagram when MCU is Unsecured

#### Table 6-13. CDCM Encoding

| Description                                                              |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Match2 mapped to comparator C match Match3 mapped to comparator D match. |  |  |  |  |  |  |  |  |

| Match2 mapped to comparator C/D inside range Match3 disabled.            |  |  |  |  |  |  |  |  |

| Match2 mapped to comparator C/D outside range Match3 disabled.           |  |  |  |  |  |  |  |  |

| 1 Reserved <sup>(1)</sup>                                                |  |  |  |  |  |  |  |  |

|                                                                          |  |  |  |  |  |  |  |  |

Currently defaults to Match2 mapped to comparator C : Match3 mapped to comparator D

#### Table 6-14. ABCM Encoding

| Description                                                              |

|--------------------------------------------------------------------------|

| Match0 mapped to comparator A match Match1 mapped to comparator B match. |

| Match 0 mapped to comparator A/B inside range Match1 disabled.           |

| Match 0 mapped to comparator A/B outside range Match1 disabled.          |

| Reserved <sup>(1)</sup>                                                  |

|                                                                          |

Currently defaults to Match0 mapped to comparator A : Match1 mapped to comparator B

#### Debug Trace Buffer Register (DBGTBH:DBGTBL) 6.3.2.5

Address: 0x0024, 0x0025

|                 | 15     | 14     | 13     | 12     | 11     | 10     | 9     | 8     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-----------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W          | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| POR             | Х      | Х      | Х      | Х      | Х      | Х      | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | X     |

| Other<br>Resets | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     |

#### Figure 6-7. Debug Trace Buffer Register (DBGTB)

Read: Only when unlocked AND not secured AND not armed AND with the TSOURCE bit set.

Write: Aligned word writes when disarmed unlock the trace buffer for reading but do not affect trace buffer contents.

### Table 6-15. DBGTB Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>Bit[15:0] | <b>Trace Buffer Data Bits</b> — The Trace Buffer Register is a window through which the 64-bit wide data lines of the Trace Buffer may be read 16 bits at a time. Each valid read of DBGTB increments an internal trace buffer pointer which points to the next address to be read. When the ARM bit is written to 1 the trace buffer is locked to prevent reading. The trace buffer can only be unlocked for reading by writing to DBGTB with an aligned word write when the module is disarmed. The DBGTB register can be read only as an aligned word, any byte reads or misaligned access of these registers will return 0 and will not cause the trace buffer pointer to increment to the next trace buffer address. The same is true for word reads while the debugger is armed. The POR state is undefined Other resets do not affect the trace buffer contents. |

| Field       | Description           PLL Select Bit           Write: Anytime.           Writing a one when LOCK=0 has no effect. This prevents the selection of an unstable PLLCLK as SYSCLK.           PLLSEL bit is cleared when the MCU enters Self Clock Mode, Stop Mode or Wait Mode with PLLWAI bit set.           It is recommended to read back the PLLSEL bit to make sure PLLCLK has really been selected as           SYSCLK, as LOCK status bit could theoretically change at the very moment writing the PLLSEL bit.           0 System clocks are derived from OSCCLK (f <sub>BUS</sub> = f <sub>OSC</sub> / 2).           1 System clocks are derived from PLLCLK (f <sub>BUS</sub> = f <sub>PLL</sub> / 2). |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>PLLSEL |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 6<br>PSTP   | Pseudo Stop Bit         Write: Anytime         This bit controls the functionality of the oscillator during Stop Mode.         0 Oscillator is disabled in Stop Mode.         1 Oscillator continues to run in Stop Mode (Pseudo Stop).         Note: Pseudo Stop Mode allows for faster STOP recovery and reduces the mechanical stress and aging of the resonator in case of frequent STOP conditions at the expense of a slightly increased power consumption.                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 5<br>XCLKS  | <ul> <li>Oscillator Configuration Status Bit — This read-only bit shows the oscillator configuration status.</li> <li>0 Loop controlled Pierce Oscillator is selected.</li> <li>1 External clock / full swing Pierce Oscillator is selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 3<br>PLLWAI | PLL Stops in Wait Mode Bit         Write: Anytime         If PLLWAI is set, the S12XECRG will clear the PLLSEL bit before entering Wait Mode. The PLLON bit remains set during Wait Mode but the IPLL is powered down. Upon exiting Wait Mode, the PLLSEL bit has to be set manually if PLL clock is required.         0       IPLL keeps running in Wait Mode.         1       IPLL stops in Wait Mode.                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 1<br>RTIWAI | <ul> <li>RTI Stops in Wait Mode Bit</li> <li>Write: Anytime</li> <li>0 RTI keeps running in Wait Mode.</li> <li>1 RTI stops and initializes the RTI dividers whenever the part goes into Wait Mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 0<br>COPWAI | <ul> <li>COP Stops in Wait Mode Bit</li> <li>Normal modes: Write once</li> <li>Special modes: Write anytime</li> <li>0 COP keeps running in Wait Mode.</li> <li>1 COP stops and initializes the COP counter whenever the part goes into Wait Mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

### Table 8-6. CLKSEL Field Descriptions

# 8.3.2.7 S12XECRG IPLL Control Register (PLLCTL)

This register controls the IPLL functionality.

Module Base + 0x0006

|        | 7   | 6     | 5   | 4   | 3      | 2   | 1   | 0    |

|--------|-----|-------|-----|-----|--------|-----|-----|------|

| R<br>W | CME | PLLON | FM1 | FM0 | FSTWKP | PRE | PCE | SCME |

| Reset  | 1   | 1     | 0   | 0   | 0      | 0   | 0   | 1    |

### Figure 8-9. S12XECRG IPLL Control Register (PLLCTL)

S12XE Clocks and Reset Generator (S12XECRGV1)

# 8.5 Resets

All reset sources are listed in Table 8-16. Refer to MCU specification for related vector addresses and priorities.

| Reset Source          | Local Enable           |

|-----------------------|------------------------|

| Power on Reset        | None                   |

| Low Voltage Reset     | None                   |

| External Reset        | None                   |

| Illegal Address Reset | None                   |

| Clock Monitor Reset   | PLLCTL (CME=1, SCME=0) |

Analog-to-Digital Converter (ADC12B16CV1)

# 10.1.2 Modes of Operation

## 10.1.2.1 Conversion Modes

There is software programmable selection between performing **single** or **continuous conversion** on a **single channel** or **multiple channels**.

## 10.1.2.2 MCU Operating Modes

### • Stop Mode

### — ICLKSTP=0 (in ATDCTL2 register)

Entering Stop Mode aborts any conversion sequence in progress and if a sequence was aborted restarts it after exiting stop mode. This has the same effect/consequences as starting a conversion sequence with write to ATDCTL5. So after exiting from stop mode with a previously aborted sequence all flags are cleared etc.

### — ICLKSTP=1 (in ATDCTL2 register)

A/D conversion sequence seamless continues in Stop Mode based on the internally generated clock ICLK as ATD clock. For conversions during transition from Run to Stop Mode or vice versa the result is not written to the results register, no CCF flag is set and no compare is done. When converting in Stop Mode (ICLKSTP=1) an ATD Stop Recovery time  $t_{ATDSTPRCV}$  is required to switch back to bus clock based ATDCLK when leaving Stop Mode. Do not access ATD registers during this time.

### • Wait Mode

ADC12B16C behaves same in Run and Wait Mode. For reduced power consumption continuos conversions should be aborted before entering Wait mode.

### • Freeze Mode

In Freeze Mode the ADC12B16C will either continue or finish or stop converting according to the FRZ1 and FRZ0 bits. This is useful for debugging and emulation.

# **10.2 Signal Description**

This section lists all inputs to the ADC12B16C block.

# **10.2.1** Detailed Signal Descriptions

## 10.2.1.1 ANx (x = 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0)

This pin serves as the analog input Channel *x*. It can also be configured as digital port or external trigger for the ATD conversion.

## 10.2.1.2 ETRIG3, ETRIG2, ETRIG1, ETRIG0

These inputs can be configured to serve as an external trigger for the ATD conversion.

Refer to device specification for availability and connection of these inputs!

# 10.2.1.3 V<sub>RH</sub>, V<sub>RL</sub>

$V_{RH}$  is the high reference voltage,  $V_{RL}$  is the low reference voltage for ATD conversion.

## 10.2.1.4 V<sub>DDA</sub>, V<sub>SSA</sub>

These pins are the power supplies for the analog circuitry of the ADC12B16C block.

# **10.3** Memory Map and Register Definition

This section provides a detailed description of all registers accessible in the ADC12B16C.

## 10.3.1 Module Memory Map

Figure 10-3 gives an overview on all ADC12B16C registers.

### NOTE

Register Address = Base Address + Address Offset, where the Base Address is defined at the MCU level and the Address Offset is defined at the module level.

Freescale's Scalable Controller Area Network (S12MSCANV3)

# 11.1.3 Features

The basic features of the MSCAN are as follows:

- Implementation of the CAN protocol Version 2.0A/B

- Standard and extended data frames

- Zero to eight bytes data length

- Programmable bit rate up to  $1 \text{ Mbps}^1$

- Support for remote frames

- Five receive buffers with FIFO storage scheme

- Three transmit buffers with internal prioritization using a "local priority" concept

- Flexible maskable identifier filter supports two full-size (32-bit) extended identifier filters, or four 16-bit filters, or eight 8-bit filters

- Programmable wake-up functionality with integrated low-pass filter

- Programmable loopback mode supports self-test operation

- Programmable listen-only mode for monitoring of CAN bus

- Programmable bus-off recovery functionality

- Separate signalling and interrupt capabilities for all CAN receiver and transmitter error states (warning, error passive, bus-off)

- Programmable MSCAN clock source either bus clock or oscillator clock

- Internal timer for time-stamping of received and transmitted messages

- Three low-power modes: sleep, power down, and MSCAN enable

- Global initialization of configuration registers

# 11.1.4 Modes of Operation

For a description of the specific MSCAN modes and the module operation related to the system operating modes refer to Section 11.4.4, "Modes of Operation".

1. Depending on the actual bit timing and the clock jitter of the PLL.

## 11.4.4.2 Special System Operating Modes

The MSCAN module behaves as described within this specification in all special system operating modes. Write restrictions which exist on specific registers in normal modes are lifted for test purposes in special modes.

### 11.4.4.3 Emulation Modes

In all emulation modes, the MSCAN module behaves just like in normal system operating modes as described within this specification.

### 11.4.4.4 Listen-Only Mode

In an optional CAN bus monitoring mode (listen-only), the CAN node is able to receive valid data frames and valid remote frames, but it sends only "recessive" bits on the CAN bus. In addition, it cannot start a transmission.

If the MAC sub-layer is required to send a "dominant" bit (ACK bit, overload flag, or active error flag), the bit is rerouted internally so that the MAC sub-layer monitors this "dominant" bit, although the CAN bus may remain in recessive state externally.

## 11.4.4.5 MSCAN Initialization Mode

The MSCAN enters initialization mode when it is enabled (CANE=1).

When entering initialization mode during operation, any on-going transmission or reception is immediately aborted and synchronization to the CAN bus is lost, potentially causing CAN protocol violations. To protect the CAN bus system from fatal consequences of violations, the MSCAN immediately drives TXCAN into a recessive state.

### NOTE

The user is responsible for ensuring that the MSCAN is not active when initialization mode is entered. The recommended procedure is to bring the MSCAN into sleep mode (SLPRQ = 1 and SLPAK = 1) before setting the INITRQ bit in the CANCTL0 register. Otherwise, the abort of an on-going message can cause an error condition and can impact other CAN bus devices.

In initialization mode, the MSCAN is stopped. However, interface registers remain accessible. This mode is used to reset the CANCTLO, CANRFLG, CANRIER, CANTFLG, CANTIER, CANTARQ, CANTAAK, and CANTBSEL registers to their default values. In addition, the MSCAN enables the configuration of the CANBTRO, CANBTR1 bit timing registers; CANIDAC; and the CANIDAR, CANIDMR message filters. See Section 11.3.2.1, "MSCAN Control Register 0 (CANCTLO)," for a detailed description of the initialization mode.

# 13.6 Interrupts

The PWM module has only one interrupt which is generated at the time of emergency shutdown, if the corresponding enable bit (PWMIE) is set. This bit is the enable for the interrupt. The interrupt flag PWMIF is set whenever the input level of the PWM7 channel changes while PWM7ENA = 1 or when PWMENA is being asserted while the level at PWM7 is active.

In stop mode or wait mode (with the PSWAI bit set), the emergency shutdown feature will drive the PWM outputs to their shutdown output levels but the PWMIF flag will not be set.

A description of the registers involved and affected due to this interrupt is explained in Section 13.3.2.15, "PWM Shutdown Register (PWMSDN)".

The PWM block only generates the interrupt and does not service it. The interrupt signal name is PWM interrupt signal.

#### Serial Peripheral Interface (S12SPIV5)

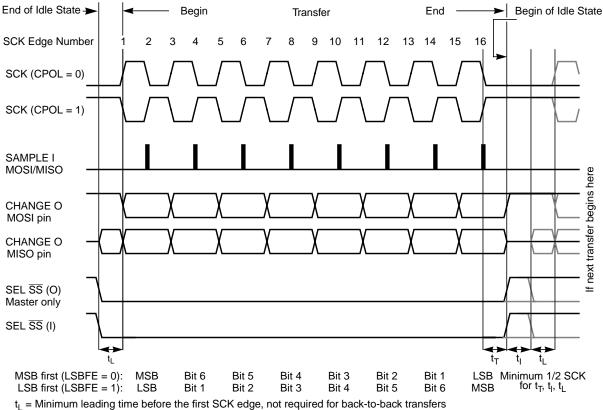

When the third edge occurs, the value previously latched from the serial data input pin is shifted into the LSB or MSB of the SPI shift register, depending on LSBFE bit. After this edge, the next bit of the master data is coupled out of the serial data output pin of the master to the serial input pin on the slave.

This process continues for a total of  $n^1$  edges on the SCK line with data being latched on even numbered edges and shifting taking place on odd numbered edges.

Data reception is double buffered, data is serially shifted into the SPI shift register during the transfer and is transferred to the parallel SPI data register after the last bit is shifted in.

After 2n<sup>1</sup> SCK edges:

- Data that was previously in the SPI data register of the master is now in the data register of the slave, and data that was in the data register of the slave is in the master.

- The SPIF flag bit in SPISR is set indicating that the transfer is complete.

Figure 15-14 shows two clocking variations for CPHA = 1. The diagram may be interpreted as a master or slave timing diagram because the SCK, MISO, and MOSI pins are connected directly between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The  $\overline{SS}$  pin of the master must be either high or reconfigured as a general-purpose output not affecting the SPI.

$t_{T}$  = Minimum trailing time after the last SCK edge

$t_1 =$  Minimum idling time between transfers (minimum  $\overline{SS}$  high time), not required for back-to-back transfers

Figure 15-14. SPI Clock Format 1 (CPHA = 1), with 8-Bit Transfer Width selected (XFRW = 0)

## NOTE

The pulse accumulator counter can operate in event counter mode even when the timer enable bit, TEN, is clear.

# 16.4.6 Gated Time Accumulation Mode

Setting the PAMOD bit configures the pulse accumulator for gated time accumulation operation. An active level on the PACNT input pin enables a divided-by-64 clock to drive the pulse accumulator. The PEDGE bit selects low levels or high levels to enable the divided-by-64 clock.

The trailing edge of the active level at the IOC7 pin sets the PAIF. The PAI bit enables the PAIF flag to generate interrupt requests.

The pulse accumulator counter register reflect the number of pulses from the divided-by-64 clock since the last reset.

### NOTE

The timer prescaler generates the divided-by-64 clock. If the timer is not active, there is no divided-by-64 clock.

# 16.5 Resets

The reset state of each individual bit is listed within Section 16.3, "Memory Map and Register Definition" which details the registers and their bit fields.

# 16.6 Interrupts

This section describes interrupts originated by the TIM16B8CV2 block. Table 16-25 lists the interrupts generated by the TIM16B8CV2 to communicate with the MCU.

| Interrupt | Offset <sup>1</sup> | Vector <sup>1</sup> | Priority <sup>1</sup> | Source                        | Description                                   |

|-----------|---------------------|---------------------|-----------------------|-------------------------------|-----------------------------------------------|

| C[7:0]F   | —                   | —                   | —                     | Timer Channel 7–0             | Active high timer channel interrupts 7–0      |

| PAOVI     | —                   | —                   | —                     | Pulse Accumulator<br>Input    | Active high pulse accumulator input interrupt |

| PAOVF     | —                   | —                   | —                     | Pulse Accumulator<br>Overflow | Pulse accumulator overflow interrupt          |

| TOF       | —                   | _                   | —                     | Timer Overflow                | Timer Overflow interrupt                      |

Table 16-25. TIM16B8CV1 Interrupts

<sup>1</sup> Chip Dependent.

The TIM16B8CV2 uses a total of 11 interrupt vectors. The interrupt vector offsets and interrupt numbers are chip dependent.

#### 128 KByte Flash Module (S12XFTMR128K1V1)

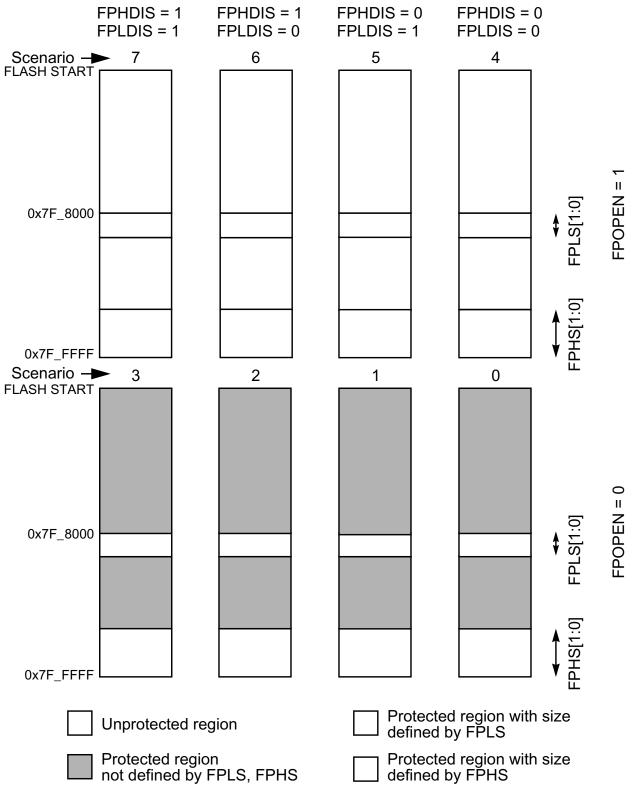

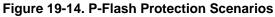

| FPLS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x7F_8000-0x7F_83FF  | 1 Kbyte        |

| 01        | 0x7F_8000-0x7F_87FF  | 2 Kbytes       |

| 10        | 0x7F_8000-0x7F_8FFF  | 4 Kbytes       |

| 11        | 0x7F_8000-0x7F_9FFF  | 8 Kbytes       |

Table 19-20. P-Flash Protection Lower Address Range

All possible P-Flash protection scenarios are shown in Figure 19-14. Although the protection scheme is loaded from the Flash memory at global address 0x7F\_FF0C during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

128 KByte Flash Module (S12XFTMR128K1V1)

CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

The Flash memory may be read as bytes, aligned words, or misaligned words. Read access time is one bus cycle for bytes and aligned words, and two bus cycles for misaligned words. For Flash memory, an erased bit reads 1 and a programmed bit reads 0.

It is not possible to read from a Flash block while any command is executing on that specific Flash block. It is possible to read from a Flash block while a command is executing on a different Flash block.

Both P-Flash and D-Flash memories are implemented with Error Correction Codes (ECC) that can resolve single bit faults and detect double bit faults. For P-Flash memory, the ECC implementation requires that programming be done on an aligned 8 byte basis (a Flash phrase). Since P-Flash memory is always read by phrase, only one single bit fault in the phrase containing the byte or word accessed will be corrected.

# 20.1.1 Glossary

**Command Write Sequence** — An MCU instruction sequence to execute built-in algorithms (including program and erase) on the Flash memory.

**D-Flash Memory** — The D-Flash memory constitutes the nonvolatile memory store for data.

**D-Flash Sector** — The D-Flash sector is the smallest portion of the D-Flash memory that can be erased. The D-Flash sector consists of four 64 byte rows for a total of 256 bytes.

**NVM Command Mode** — An NVM mode using the CPU to setup the FCCOB register to pass parameters required for Flash command execution.

**Phrase** — An aligned group of four 16-bit words within the P-Flash memory. Each phrase includes eight ECC bits for single bit fault correction and double bit fault detection within the phrase.

P-Flash Memory — The P-Flash memory constitutes the main nonvolatile memory store for applications.

**P-Flash Sector** — The P-Flash sector is the smallest portion of the P-Flash memory that can be erased. Each P-Flash sector contains 1024 bytes.

**Program IFR** — Nonvolatile information register located in the P-Flash block that contains the Device ID, Version ID, and the Program Once field. The Program IFR is visible in the global memory map by setting the PGMIFRON bit in the MMCCTL1 register.

# 20.1.2 Features

## 20.1.2.1 P-Flash Features

- 64 Kbytes of P-Flash memory composed of one 64 Kbyte Flash block divided into 64 sectors of 1024 bytes

- Single bit fault correction and double bit fault detection within a 64-bit phrase during read operations

#### 64 KByte Flash Module (S12XFTMR64K1V1)

#### Table 20-4. Program IFR Fields

| Global Address<br>(PGMIFRON) | Size<br>(Bytes) | Field Description                                                       |

|------------------------------|-----------------|-------------------------------------------------------------------------|

| 0x40_0000 - 0x40_0007        | 8               | Device ID                                                               |

| 0x40_0008 - 0x40_00E7        | 224             | Reserved                                                                |

| 0x40_00E8 - 0x40_00E9        | 2               | Version ID                                                              |

| 0x40_00EA - 0x40_00FF        | 22              | Reserved                                                                |

| 0x40_0100 - 0x40_013F        | 64              | Program Once Field<br>Refer to Section 20.4.2.6, "Program Once Command" |

| 0x40_0140 - 0x40_01FF        | 192             | Reserved                                                                |

### Table 20-5. D-Flash and Memory Controller Resource Fields

| Global Address        | Size<br>(Bytes) | Description                                                         |

|-----------------------|-----------------|---------------------------------------------------------------------|

| 0x10_0000 - 0x10_0FFF | 4,096           | D-Flash Memory                                                      |

| 0x10_1000 - 0x11_FFFF | 126,976         | Reserved                                                            |

| 0x12_0000 - 0x12_007F | 128             | D-Flash Nonvolatile Information Register (DFIFRON <sup>1</sup> = 1) |

| 0x12_0080 - 0x12_0FFF | 3,968           | Reserved                                                            |

| 0x12_1000 - 0x12_1FFF | 4,096           | Reserved                                                            |

| 0x12_2000 - 0x12_3CFF | 7,242           | Reserved                                                            |

| 0x12_3D00 - 0x12_3FFF | 768             | Memory Controller Scratch RAM (MGRAMON <sup>1</sup> = 1)            |

| 0x12_4000 - 0x12_E7FF | 43,008          | Reserved                                                            |

| 0x12_E800 - 0x12_FFFF | 6,144           | Reserved                                                            |

| 0x13_0000 - 0x13_FFFF | 65,536          | Reserved                                                            |

<sup>1</sup> MMCCTL1 register bit

#### 64 KByte Flash Module (S12XFTMR64K1V1)

P-Flash phrase containing the D-Flash protection byte during the reset sequence, the DPOPEN bit will be cleared and DPS bits will be set to leave the D-Flash memory fully protected.

Trying to alter data in any protected area in the D-Flash memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. Block erase of the D-Flash memory is not possible if any of the D-Flash sectors are protected.

| Field           | Description                                                                                                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DPOPEN     | <ul> <li>D-Flash Protection Control</li> <li>Enables D-Flash memory protection from program and erase with protected address range defined by DPS bits</li> <li>Disables D-Flash memory protection from program and erase</li> </ul> |

| 4–0<br>DPS[4:0] | <b>D-Flash Protection Size</b> — The DPS[4:0] bits determine the size of the protected area in the D-Flash memory as shown in Table 20-23.                                                                                           |

#### Table 20-22. DFPROT Field Descriptions

| Global Address Range  | Protected Size                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x10_0000 - 0x10_00FF | 256 bytes                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x10_0000 - 0x10_01FF | 512 bytes                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x10_0000 - 0x10_02FF | 768 bytes                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x10_0000 – 0x10_03FF | 1024 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_04FF | 1280 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_05FF | 1536 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_06FF | 1792 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_07FF | 2048 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_08FF | 2304 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_09FF | 2560 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 – 0x10_0AFF | 2816 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 – 0x10_0BFF | 3072 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_0CFF | 3328 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 – 0x10_0DFF | 3584 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 - 0x10_0EFF | 3840 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x10_0000 – 0x10_0FFF | 4096 bytes                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | 0x10_0000 - 0x10_00FF<br>0x10_0000 - 0x10_01FF<br>0x10_0000 - 0x10_02FF<br>0x10_0000 - 0x10_03FF<br>0x10_0000 - 0x10_03FF<br>0x10_0000 - 0x10_05FF<br>0x10_0000 - 0x10_05FF<br>0x10_0000 - 0x10_07FF<br>0x10_0000 - 0x10_08FF<br>0x10_0000 - 0x10_08FF |

#### Table 20-23. D-Flash Protection Address Range

## 20.3.2.11 Flash Common Command Object Register (FCCOB)

The FCCOB is an array of six words addressed via the CCOBIX index found in the FCCOBIX register. Byte wide reads and writes are allowed to the FCCOB register.

| FCMD | Command                         | Function on P-Flash Memory                                                                                                                                                                                                                      |

|------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks      | Verify that all P-Flash (and D-Flash) blocks are erased.                                                                                                                                                                                        |

| 0x02 | Erase Verify Block              | Verify that a P-Flash block is erased.                                                                                                                                                                                                          |

| 0x03 | Erase Verify<br>P-Flash Section | Verify that a given number of words starting at the address provided are erased.                                                                                                                                                                |

| 0x04 | Read Once                       | Read a dedicated 64 byte field in the nonvolatile information register in P-Flash block 0 that was previously programmed using the Program Once command.                                                                                        |

| 0x06 | Program P-Flash                 | Program a phrase in a P-Flash block.                                                                                                                                                                                                            |

| 0x07 | Program Once                    | Program a dedicated 64 byte field in the nonvolatile information register in P-Flash block<br>0 that is allowed to be programmed only once.                                                                                                     |

| 0x08 | Erase All Blocks                | Erase all P-Flash (and D-Flash) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN<br>bits in the FPROT register and the DPOPEN bit in the DFPROT register are set prior to<br>launching the command. |

| 0x09 | Erase Flash Block               | Erase a P-Flash (or D-Flash) block.<br>An erase of the full P-Flash block is only possible when FPLDIS, FPHDIS and FPOPEN<br>bits in the FPROT register are set prior to launching the command.                                                 |

| 0x0A | Erase P-Flash<br>Sector         | Erase all bytes in a P-Flash sector.                                                                                                                                                                                                            |

| 0x0B | Unsecure Flash                  | Supports a method of releasing MCU security by erasing all P-Flash (and D-Flash) blocks and verifying that all P-Flash (and D-Flash) blocks are erased.                                                                                         |

| 0x0C | Verify Backdoor<br>Access Key   | Supports a method of releasing MCU security by verifying a set of security keys.                                                                                                                                                                |

| 0x0D | Set User Margin<br>Level        | Specifies a user margin read level for all P-Flash blocks.                                                                                                                                                                                      |

| 0x0E | Set Field Margin<br>Level       | Specifies a field margin read level for all P-Flash blocks (special modes only).                                                                                                                                                                |

#### Table 20-29. P-Flash Commands

# 20.4.1.5 D-Flash Commands

Table 20-30 summarizes the valid D-Flash commands along with the effects of the commands on the D-Flash block.

| FCMD | Command                    | Function on D-Flash Memory                                                                                                                                                                                                                      |

|------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks | Verify that all D-Flash (and P-Flash) blocks are erased.                                                                                                                                                                                        |

| 0x02 | Erase Verify Block         | Verify that the D-Flash block is erased.                                                                                                                                                                                                        |

| 0x08 | Erase All Blocks           | Erase all D-Flash (and P-Flash) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN<br>bits in the FPROT register and the DPOPEN bit in the DFPROT register are set prior to<br>launching the command. |

| 0x09 | Erase Flash Block          | Erase a D-Flash (or P-Flash) block.<br>An erase of the full D-Flash block is only possible when DPOPEN bit in the DFPROT<br>register is set prior to launching the command.                                                                     |

#### Table 20-30. D-Flash Commands

**Detailed Register Address Map**

### 0x000E–0x000F Reserved Register Space

| Address         | Name          |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------------|---------------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x000E Reserved | R             | 0 | 0     | 0     | 0     | 0     | 0     | 0     | 0     |       |

|                 | Reserved      | W |       |       |       |       |       |       |       |       |

|                 | 000F Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| UXUUUF          |               | W |       |       |       |       |       |       |       |       |

## 0x0010–0x0017 Module Mapping Control (S12XMMC) Map 2 of 2

| Address | Name     |                | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|----------|----------------|--------|-------|---------|---------|-------|-------|-------|-------|--|

| 0x0010  | GPAGE    | R<br>W         | _      | GP6   | GP5     | GP4     | GP3   | GP2   | GP1   | GP0   |  |

| 0x0011  | DIRECT   | R<br>W         | DP15   | DP14  | DP13    | DP12    | DP11  | DP10  | DP9   | DP8   |  |

| 0x0012  | Reserved | R              | 0      | 0     | 0       | 0       | 0     | 0     | 0     | 0     |  |

| 00012   | Reserved | W              |        |       |         |         |       |       |       |       |  |

| 0x0013  | MMCCTI 1 | R              | MGRAMO | 0     | DFIFRON | PGMIFRO | 0     | 0     | 0     | 0     |  |

| 0X0013  |          | W              | Ν      |       |         | N       |       |       |       |       |  |

| 0x0014  | Reserved | R              | 0      | 0     | 0       | 0       | 0     | 0     | 0     | 0     |  |

| 0X0014  | Reserved | KUU14 Keselveu | W      |       |         |         |       |       |       |       |  |

| 0x0015  | PPAGE    | R<br>W         | PIX7   | PIX6  | PIX5    | PIX4    | PIX3  | PIX2  | PIX1  | PIX0  |  |

| 0x0016  | RPAGE    | R<br>W         | RP7    | RP6   | RP5     | RP4     | RP3   | RP2   | RP1   | RP0   |  |

| 0x0017  | EPAGE    | R<br>W         | EP7    | EP6   | EP5     | EP4     | EP3   | EP2   | EP1   | EP0   |  |

### 0x0018–0x001B Miscellaneous Peripheral

| Address | Name     |   | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|----------|---|---------|-------|-------|-------|-------|-------|-------|-------|--|

| 0x0018  | Reserved | R | 0       | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

|         |          | W |         |       |       |       |       |       |       |       |  |

| 0x0019  | Reserved | R | 0       | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

|         |          | W |         |       |       |       |       |       |       |       |  |

| 0x001A  | PARTIDH  | R | PARTIDH |       |       |       |       |       |       |       |  |

|         |          | W |         |       |       |       |       |       |       |       |  |

| 0x001B  | PARTIDL  | R | PARTIDL |       |       |       |       |       |       |       |  |

|         |          | W |         |       |       |       |       |       |       |       |  |

## 0x001C–0x001D Port Integration Module (PIM) Map 3 of 5

| Address | Name     |        | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|--------|-------|--------|-------|-------|-------|-------|-------|-------|

| 0x001C  | ECLKCTL  | R<br>W | NECLK | NCLKX2 | DIV16 | EDIV4 | EDIV3 | EDIV2 | EDIV1 | EDIV0 |

| 0x001D  | Reserved | R      | 0     | 0      | 0     | 0     | 0     | 0     | 0     | 0     |

|         |          | W      |       |        |       |       |       |       |       |       |