Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | HCS12X                                                       |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 40MHz                                                        |

| Connectivity               | CANbus, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 44                                                           |

| Program Memory Size        | 128KB (128K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 8K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                 |

| Data Converters            | A/D 8x12b                                                    |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 64-LQFP                                                      |

| Supplier Device Package    | 64-LQFP (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s12xs128j1cae |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 7.1.7 | Complete Memory Erase (Special Modes) |  |

|-------|---------------------------------------|--|

|-------|---------------------------------------|--|

# Chapter 8 S12XE Clocks and Reset Generator (S12XECRGV1)

| Introduc | ction                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.1.1    | Features                                                                                                                                                |

| 8.1.2    | Modes of Operation                                                                                                                                      |

| 8.1.3    | Block Diagram                                                                                                                                           |

| Signal I | Description                                                                                                                                             |

| 8.2.1    | V <sub>DDPLL</sub> , V <sub>SSPLL</sub>                                                                                                                 |

| 8.2.2    | <b>RESET</b>                                                                                                                                            |

| Memory   | Map and Registers                                                                                                                                       |

| 8.3.1    | Module Memory Map                                                                                                                                       |

| 8.3.2    | Register Descriptions                                                                                                                                   |

| Function | nal Description                                                                                                                                         |

| 8.4.1    | Functional Blocks                                                                                                                                       |

| 8.4.2    | Operation Modes                                                                                                                                         |

| 8.4.3    | Low Power Options                                                                                                                                       |

| Resets   |                                                                                                                                                         |

| 8.5.1    | Description of Reset Operation                                                                                                                          |

| Interrup | ts                                                                                                                                                      |

| 8.6.1    | Description of Interrupt Operation                                                                                                                      |

|          | 8.1.1<br>8.1.2<br>8.1.3<br>Signal I<br>8.2.1<br>8.2.2<br>Memory<br>8.3.1<br>8.3.2<br>Function<br>8.4.1<br>8.4.2<br>8.4.3<br>Resets<br>8.5.1<br>Interrup |

# Chapter 9 Pierce Oscillator (S12XOSCLCPV2)

| 9.1 | Introduc | ction                                                                         | 267 |

|-----|----------|-------------------------------------------------------------------------------|-----|

|     | 9.1.1    | Features                                                                      | 267 |

|     | 9.1.2    | Modes of Operation                                                            | 267 |

|     | 9.1.3    | Block Diagram                                                                 | 268 |

| 9.2 | External | l Signal Description                                                          | 268 |

|     | 9.2.1    | V <sub>DDPLL</sub> and V <sub>SSPLL</sub> — Operating and Ground Voltage Pins | 268 |

|     | 9.2.2    | EXTAL and XTAL — Input and Output Pins                                        | 268 |

| 9.3 | Memory   | y Map and Register Definition                                                 | 270 |

| 9.4 | Function | nal Description                                                               | 270 |

|     | 9.4.1    | Gain Control                                                                  | 270 |

|     | 9.4.2    | Clock Monitor                                                                 | 270 |

|     | 9.4.3    | Wait Mode Operation                                                           | 270 |

|     | 9.4.4    | Stop Mode Operation                                                           | 270 |

|     |          |                                                                               |     |

# Chapter 10

# Analog-to-Digital Converter (ADC12B16CV1)

| 10.1 | Introduction              | 271 |

|------|---------------------------|-----|

|      | 10.1.1 Features           | 271 |

|      | 10.1.2 Modes of Operation | 272 |

| S12XS Family Reference | Manual, | Rev. | 1.13 |

|------------------------|---------|------|------|

|------------------------|---------|------|------|

## 1.2.3.36 PS1 / TXD0 — Port S I/O Pin 1

PS1 is a general-purpose input or output pin. It can be configured as the transmit pin TXD of serial communication interface 0 (SCI0).

## 1.2.3.37 PS0 / RXD0 — Port S I/O Pin 0

PS0 is a general-purpose input or output pin. It can be configured as the receive pin RXD of serial communication interface 0 (SCI0).

# 1.2.3.38 PT[7:6] / IOC[7:6] / PWM[7:6] — Port T I/O Pins 7-6

PT[7:6] are general-purpose input or output pins. They can be configured as timer (TIM) channel 7-6 or pulse width modulator (PWM) outputs 7-6

# 1.2.3.39 PT5 / IOC5 / VREG\_API — Port T I/O Pin 5

PT[5] is a general-purpose input or output pin. It can be configured as timer (TIM) channel 5, pulse width modulator (PWM) output 5 or as the VREG\_API signal output.

## 1.2.3.40 PT4 / IOC4 / PWM4 — Port T I/O Pin 4

PT4 is a general-purpose input or output pin. It can be configured as timer (TIM) channel 4 or pulse width modulator (PWM) output 4.

# 1.2.3.41 PT[3:0] / IOC[3:0] — Port T I/O Pin [3:0]

PT[3:0] are a general-purpose input or output pins. They can be configured as timer (TIM) channels 3-0.

# 1.2.4 Power Supply Pins

S12XS Family power and ground pins are described below.

Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible.

### NOTE

All  $V_{SS}$  pins must be connected together in the application.

### 1.2.4.1 VDDX[2:1], VSSX[2:1] — Power and Ground Pins for I/O Drivers

External power and ground for I/O drivers. Bypass requirements depend on how heavily the MCU pins are loaded. All  $V_{DDX}$  pins are connected together internally. All  $V_{SSX}$  pins are connected together internally.

### 1.2.4.2 VDDR — Power Pin for Internal Voltage Regulator

Power supply input to the internal voltage regulator.

S12XS Family Reference Manual, Rev. 1.13

# 4.4.3 XGATE Requests

If the XGATE module is implemented on the device, the XINT module is also used to process all exception requests to be serviced by the XGATE module. The overall priority level of those exceptions is discussed in the subsections below.

# 4.4.3.1 XGATE Request Prioritization

An interrupt request channel is configured to be handled by the XGATE module, if the RQST bit of the associated configuration register is set to 1 (please refer to Section 4.3.2.4, "Interrupt Request Configuration Data Registers (INT\_CFDATA0-7)"). The priority level configuration (PRIOLVL) for this channel becomes the XGATE priority which will be used to determine the highest priority XGATE request to be serviced next by the XGATE module. Additionally, XGATE interrupts may be raised by the XGATE module by setting one or more of the XGATE channel interrupt flags (by using the SIF instruction). This will result in an CPU interrupt with vector address vector base + (2 \* channel ID number), where the channel ID number corresponds to the highest set channel interrupt flag, if the XGIE and channel RQST bits are set.

The shared interrupt priority for the XGATE interrupt requests is taken from the XGATE interrupt priority configuration register (please refer to Section 4.3.2.2, "XGATE Interrupt Priority Configuration Register (INT\_XGPRIO)"). If more than one XGATE interrupt request channel becomes active at the same time, the channel with the highest vector address wins the prioritization.

# 4.4.4 Priority Decoders

The XINT module contains priority decoders to determine the priority for all interrupt requests pending for the respective target.

There are two priority decoders, one for each interrupt request target, CPU or XGATE. The function of both priority decoders is basically the same with one exception: the priority decoder for the XGATE module does not take the current XGATE thread processing level into account. Instead, XGATE requests are handed to the XGATE module including a 1-bit priority identifier. The XGATE module uses this additional information to decide if the new request can interrupt a currently running thread. The 1-bit priority identifier corresponds to the most significant bit of the priority level configuration of the requesting channel. This means that XGATE requests with priority levels 4, 5, 6 or 7 can interrupt running XGATE threads with priority levels 1, 2 and 3.

A CPU interrupt vector is not supplied until the CPU requests it. Therefore, it is possible that a higher priority interrupt request could override the original exception which caused the CPU to request the vector. In this case, the CPU will receive the highest priority vector and the system will process this exception instead of the original request.

If the interrupt source is unknown (for example, in the case where an interrupt request becomes inactive after the interrupt has been recognized, but prior to the vector request), the vector address supplied to the CPU will default to that of the spurious interrupt vector.

#### S12XE Clocks and Reset Generator (S12XECRGV1)

- System Reset generation from the following possible sources:

- Power on reset

- Low voltage reset

- Illegal address reset

- COP reset

- Loss of clock reset

- External pin reset

- Real-Time Interrupt (RTI)

# 8.1.2 Modes of Operation

This subsection lists and briefly describes all operating modes supported by the S12XECRG.

• Run Mode

All functional parts of the S12XECRG are running during normal Run Mode. If RTI or COP functionality is required the individual bits of the associated rate select registers (COPCTL, RTICTL) have to be set to a non zero value.

• Wait Mode

In this mode the IPLL can be disabled automatically depending on the PLLWAI bit.

• Stop Mode

Depending on the setting of the PSTP bit Stop Mode can be differentiated between Full Stop Mode (PSTP = 0) and Pseudo Stop Mode (PSTP = 1).

— Full Stop Mode

The oscillator is disabled and thus all system and core clocks are stopped. The COP and the RTI remain frozen.

Pseudo Stop Mode

The oscillator continues to run and most of the system and core clocks are stopped. If the respective enable bits are set the COP and RTI will continue to run, else they remain frozen.

Self Clock Mode

Self Clock Mode will be entered if the Clock Monitor Enable Bit (CME) and the Self Clock Mode Enable Bit (SCME) are both asserted and the clock monitor in the oscillator block detects a loss of clock. As soon as Self Clock Mode is entered the S12XECRG starts to perform a clock quality check. Self Clock Mode remains active until the clock quality check indicates that the required quality of the incoming clock signal is met (frequency and amplitude). Self Clock Mode should be used for safety purposes only. It provides reduced functionality to the MCU in case a loss of clock is causing severe system conditions.

# 8.1.3 Block Diagram

Figure 8-1 shows a block diagram of the S12XECRG.

# 11.3 Memory Map and Register Definition

This section provides a detailed description of all registers accessible in the MSCAN.

# 11.3.1 Module Memory Map

Figure 11-3 gives an overview on all registers and their individual bits in the MSCAN memory map. The *register address* results from the addition of *base address* and *address offset*. The *base address* is determined at the MCU level and can be found in the MCU memory map description. The *address offset* is defined at the module level.

The MSCAN occupies 64 bytes in the memory space. The base address of the MSCAN module is determined at the MCU level when the MCU is defined. The register decode map is fixed and begins at the first address of the module address offset.

The detailed register descriptions follow in the order they appear in the register map.

# 12.6 Application Information

To get started quickly with the PIT24B8C module this section provides a small code example how to use the block. Please note that the example provided is only one specific case out of the possible configurations and implementations.

Functionality: Generate an PIT interrupt on channel 0 every 500 PIT clock cycles.

|                                        | ORG            | CODESTART                  | ; place the program into specific<br>; range (to be selected) |

|----------------------------------------|----------------|----------------------------|---------------------------------------------------------------|

|                                        | LDS            | RAMEND                     | ; load stack pointer to top of RAM                            |

|                                        | MOVW           | #CH0_ISR,VEC_PIT_CH0       | ; Change value of channel 0 ISR adr                           |

| • ************************************ | ***** Start PI | T Initialization ********* | ********                                                      |

|                                        | CLR            | PITCFLMT                   | ; disable PIT                                                 |

|                                        | MOVB           | #\$01,PITCE                | ; enable timer channel 0                                      |

|                                        | CLR            | PITMUX                     | ; ch0 connected to micro timer 0                              |

|                                        | MOVB           | #\$63,PITMTLD0             | ; micro time base 0 equals 100 clock cycles                   |

|                                        | MOVW           | #\$0004,PITLD0             | ; time base 0 eq. 5 micro time bases $0 = 5*100 = 500$        |

|                                        | MOVB           | #\$01,PITINTE              | ; enable interupt channel 0                                   |

|                                        | MOVB           | #\$80,PITCFLMT             | ; enable PIT                                                  |

|                                        | CLI            |                            | ; clear Interupt disable Mask bit                             |

| •************************************* | **** Main Pr   | ogram *****************    | ***********                                                   |

| MAIN:                                  | BRA *          |                            | ; loop until interrupt                                        |

| •************************************* | **** Channel   | 0 Interupt Routine ******* | *******                                                       |

| CH0_ISR:                               | LDAA           | PITTF                      | ; 8 bit read of PIT time out flags                            |

| _ `                                    | MOVB           | #\$01,PITTF                | ; clear PIT channel 0 time out flag                           |

|                                        | RTI            |                            | ; return to MAIN                                              |

|                                        |                |                            |                                                               |

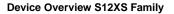

# 13.3.2.7 Reserved Register (PWMTST)

This register is reserved for factory testing of the PWM module and is not available in normal modes.

Module Base + 0x0006

Figure 13-9. Reserved Register (PWMTST)

Read: Always read \$00 in normal modes

Write: Unimplemented in normal modes

NOTE

Writing to this register when in special modes can alter the PWM functionality.

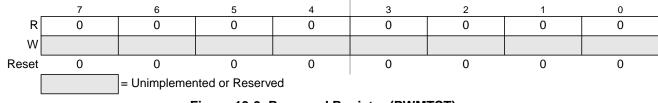

### 13.3.2.8 Reserved Register (PWMPRSC)

This register is reserved for factory testing of the PWM module and is not available in normal modes.

Module Base + 0x0007

Figure 13-10. Reserved Register (PWMPRSC)

Read: Always read \$00 in normal modes

Write: Unimplemented in normal modes

### NOTE

Writing to this register when in special modes can alter the PWM functionality.

### 13.3.2.9 PWM Scale A Register (PWMSCLA)

PWMSCLA is the programmable scale value used in scaling clock A to generate clock SA. Clock SA is generated by taking clock A, dividing it by the value in the PWMSCLA register and dividing that by two.

Clock SA = Clock A / (2 \* PWMSCLA)

S12XS Family Reference Manual, Rev. 1.13

#### Serial Communication Interface (S12SCIV5)

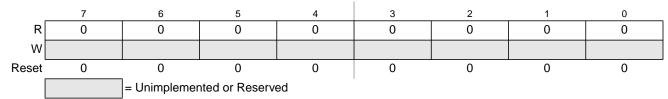

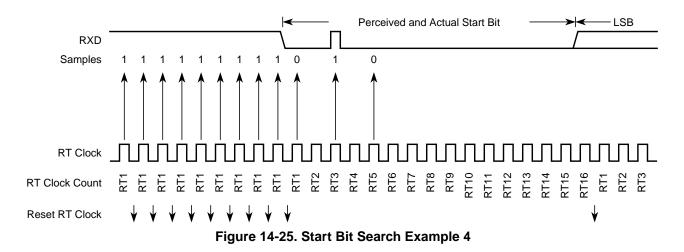

In Figure 14-24, a large burst of noise is perceived as the beginning of a start bit, although the test sample at RT5 is high. The RT5 sample sets the noise flag. Although this is a worst-case misalignment of perceived bit time, the data samples RT8, RT9, and RT10 are within the bit time and data recovery is successful.

Figure 14-25 shows the effect of noise early in the start bit time. Although this noise does not affect proper synchronization with the start bit time, it does set the noise flag.

Timer Module (TIM16B8CV2)

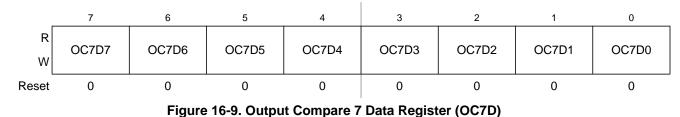

# 16.3.2.4 Output Compare 7 Data Register (OC7D)

Module Base + 0x0003

Read: Anytime

Write: Anytime

### Table 16-5. OC7D Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                          |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OC7D[7:0] | <b>Output Compare 7 Data</b> — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, can cause bits in the output compare 7 data register to transfer to the timer port data register depending on the output compare 7 mask register. |

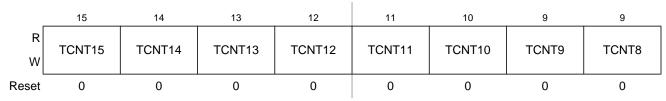

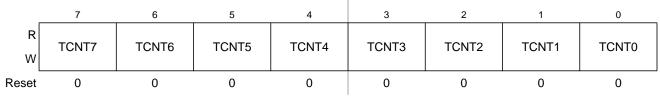

# 16.3.2.5 Timer Count Register (TCNT)

Module Base + 0x0004

Figure 16-10. Timer Count Register High (TCNTH)

Module Base + 0x0005

Figure 16-11. Timer Count Register Low (TCNTL)

The 16-bit main timer is an up counter.

A full access for the counter register should take place in one clock cycle. A separate read/write for high byte and low byte will give a different result than accessing them as a word.

Read: Anytime

S12XS Family Reference Manual, Rev. 1.13

### Read: Anytime

Write: Anytime.

#### Table 16-11. TCTL3/TCTL4 Field Descriptions

| Field | Description                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------|

| 7:0   | Input Capture Edge Control — These eight pairs of control bits configure the input capture edge detector |

| EDGnB | circuits.                                                                                                |

| EDGnA |                                                                                                          |

| EDGnB | EDGnA | Configuration                           |

|-------|-------|-----------------------------------------|

| 0     | 0     | Capture disabled                        |

| 0     | 1     | Capture on rising edges only            |

| 1     | 0     | Capture on falling edges only           |

| 1     | 1     | Capture on any edge (rising or falling) |

#### Table 16-12. Edge Detector Circuit Configuration

### 16.3.2.10 Timer Interrupt Enable Register (TIE)

Module Base + 0x000C

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | C7I | C6I | C5I | C4I | C3I | C2I | C1I | COI |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Figure 16-18. Timer Interrupt Enable Register (TIE)

Read: Anytime

Write: Anytime.

#### Table 16-13. TIE Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>C7I:C0I | <b>Input Capture/Output Compare "x" Interrupt Enable</b> — The bits in TIE correspond bit-for-bit with the bits in the TFLG1 status register. If cleared, the corresponding flag is disabled from causing a hardware interrupt. If set, the corresponding flag is enabled to cause a interrupt. |

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>FPOPEN      | <ul> <li>Flash Protection Operation Enable — The FPOPEN bit determines the protection function for program or erase operations as shown in Table 18-18 for the P-Flash block.</li> <li>When FPOPEN is clear, the FPHDIS and FPLDIS bits define unprotected address ranges as specified by the corresponding FPHS and FPLS bits</li> <li>When FPOPEN is set, the FPHDIS and FPLDIS bits enable protection for the address range specified by the corresponding FPHS and FPLDIS and FPLDIS bits enable protection for the address range specified by the corresponding FPHS and FPLS bits</li> </ul> |  |

| 6<br>RNV[6]      | Reserved Nonvolatile Bit — The RNV bit should remain in the erased state for future enhancements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 5<br>FPHDIS      | Flash Protection Higher Address Range Disable — The FPHDIS bit determines whether there is a<br>protected/unprotected area in a specific region of the P-Flash memory ending with global address 0x7F_FFFF.0 Protection/Unprotection enabled<br>1 Protection/Unprotection disabled                                                                                                                                                                                                                                                                                                                 |  |

| 4–3<br>FPHS[1:0] | Flash Protection Higher Address Size — The FPHS bits determine the size of the protected/unprotected area in P-Flash memory as shown inTable 18-19. The FPHS bits can only be written to while the FPHDIS bit is set.                                                                                                                                                                                                                                                                                                                                                                              |  |

| 2<br>FPLDIS      | <ul> <li>Flash Protection Lower Address Range Disable — The FPLDIS bit determines whether there is a protected/unprotected area in a specific region of the P-Flash memory beginning with global address 0x7F_8000.</li> <li>0 Protection/Unprotection enabled</li> <li>1 Protection/Unprotection disabled</li> </ul>                                                                                                                                                                                                                                                                              |  |

| 1–0<br>FPLS[1:0] | Flash Protection Lower Address Size — The FPLS bits determine the size of the protected/unprotected area in P-Flash memory as shown in Table 18-20. The FPLS bits can only be written to while the FPLDIS bit is set.                                                                                                                                                                                                                                                                                                                                                                              |  |

#### Table 18-18. P-Flash Protection Function

| FPOPEN | FPHDIS | FPLDIS | Function <sup>1</sup>           |

|--------|--------|--------|---------------------------------|

| 1      | 1      | 1      | No P-Flash Protection           |

| 1      | 1      | 0      | Protected Low Range             |

| 1      | 0      | 1      | Protected High Range            |

| 1      | 0      | 0      | Protected High and Low Ranges   |

| 0      | 1      | 1      | Full P-Flash Memory Protected   |

| 0      | 1      | 0      | Unprotected Low Range           |

| 0      | 0      | 1      | Unprotected High Range          |

| 0      | 0      | 0      | Unprotected High and Low Ranges |

<sup>1</sup> For range sizes, refer to Table 18-19 and Table 18-20.

### Table 18-19. P-Flash Protection Higher Address Range

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x7F_F800-0x7F_FFFF  | 2 Kbytes       |

| 01        | 0x7F_F000-0x7F_FFFF  | 4 Kbytes       |

| 10        | 0x7F_E000-0x7F_FFFF  | 8 Kbytes       |

| 11        | 0x7F_C000-0x7F_FFFF  | 16 Kbytes      |

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 18-28)                      |

|          |           | Set if an invalid global address [22:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the global address [22:0] points to a protected area                         |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

#### Table 18-40. Program P-Flash Command Error Handling

### 18.4.2.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash block 0. The Program Once reserved field can be read using the Read Once command as described in Section 18.4.2.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash block 0 cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |                   |  |

|-------------|---------------------------------------------|-------------------|--|

| 000         | 0x07                                        | 0x07 Not Required |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |                   |  |

| 010         | Program Once word 0 value                   |                   |  |

| 011         | Program Once word 1 value                   |                   |  |

| 100         | Program Once word 2 value                   |                   |  |

| 101         | Program Once word 3 value                   |                   |  |

Table 18-41. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash block 0 will return invalid data.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 19-28)                      |

|          |           | Set if an invalid global address [22:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the global address [22:0] points to a protected area                         |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

#### Table 19-40. Program P-Flash Command Error Handling

### 19.4.2.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash block 0. The Program Once reserved field can be read using the Read Once command as described in Section 19.4.2.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash block 0 cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |                   |  |

|-------------|---------------------------------------------|-------------------|--|

| 000         | 0x07                                        | 0x07 Not Required |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |                   |  |

| 010         | Program Once word 0 value                   |                   |  |

| 011         | Program Once word 1 value                   |                   |  |

| 100         | Program Once word 2 value                   |                   |  |

| 101         | Program Once word 3 value                   |                   |  |

Table 19-41. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash block 0 will return invalid data.

#### 128 KByte Flash Module (S12XFTMR128K1V1)

| CCOBIX[2:0] | FCCOB Parameters                                  |                                                   |

|-------------|---------------------------------------------------|---------------------------------------------------|

| 000         | 0x09                                              | Global address [22:16] to<br>identify Flash block |

| 001         | Global address [15:0] in Flash block to be erased |                                                   |

Upon clearing CCIF to launch the Erase Flash Block command, the Memory Controller will erase the selected Flash block and verify that it is erased. The CCIF flag will set after the Erase Flash Block operation has completed.

| Register | Error Bit | Error Condition                                                                                         |

|----------|-----------|---------------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                                             |

|          |           | Set if command not available in current mode (see Table 19-28)                                          |

|          |           | Set if an invalid global address [22:16] is supplied                                                    |

| FSTAT    |           | Set if the supplied P-Flash address is not phrase-aligned or if the D-Flash address is not word-aligned |

|          | FPVIOL    | Set if an area of the selected Flash block is protected                                                 |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                     |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation                     |

Table 19-46. Erase Flash Block Command Error Handling

### 19.4.2.9 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

Table 19-47. Erase P-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                         |                                                                  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| 000         | 0x0A                                                                                                                     | Global address [22:16] to identify<br>P-Flash block to be erased |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 19.1.2.1 for the P-Flash sector size. |                                                                  |  |

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

#### 128 KByte Flash Module (S12XFTMR128K1V1)

erased the MCU will be unsecured. All BDM commands will be enabled and the Flash security byte may be programmed to the unsecure state by the following method:

• Send BDM commands to execute a 'Program P-Flash' command sequence to program the Flash security byte to the unsecured state and reset the MCU.

# 19.5.3 Mode and Security Effects on Flash Command Availability

The availability of Flash module commands depends on the MCU operating mode and security state as shown in Table 19-28.

# 19.6 Initialization

On each system reset the Flash module executes a reset sequence which establishes initial values for the Flash Block Configuration Parameters, the FPROT and DFPROT protection registers, and the FOPT and FSEC registers. The Flash module reverts to built-in default values that leave the module in a fully protected and secured state if errors are encountered during execution of the reset sequence. If a double bit fault is detected during the reset sequence, both MGSTAT bits in the FSTAT register will be set.

CCIF remains clear throughout the reset sequence. The Flash module holds off all CPU access for the initial portion of the reset sequence. While Flash reads are possible when the hold is removed, writes to the FCCOBIX, FCCOBHI, and FCCOBLO registers are ignored to prevent command activity while the Memory Controller remains busy. Completion of the reset sequence is marked by setting CCIF high which enables writes to the FCCOBIX, FCCOBHI, and FCCOBHI, and FCCOBLO registers to launch any available Flash command.

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

64 KByte Flash Module (S12XFTMR64K1V1)

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|------|-------------------------------------------|

| 011         | HI   | Data 1 [15:8]                             |

|             | LO   | Data 1 [7:0]                              |

| 100         | HI   | Data 2 [15:8]                             |

| 100         | LO   | Data 2 [7:0]                              |

| 101         | HI   | Data 3 [15:8]                             |

| 101         | LO   | Data 3 [7:0]                              |

Table 20-24. FCCOB - NVM Command Mode (Typical Usage)

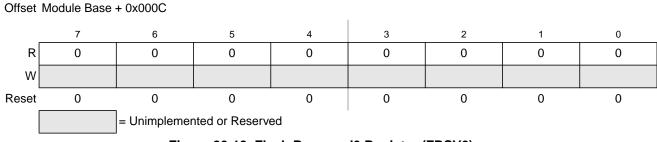

## 20.3.2.12 Flash Reserved0 Register (FRSV0)

This Flash register is reserved for factory testing.

All bits in the FRSV0 register read 0 and are not writable.

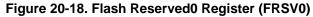

# 20.3.2.13 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

All bits in the FRSV1 register read 0 and are not writable.

# 20.3.2.14 Flash ECC Error Results Register (FECCR)

The FECCR registers contain the result of a detected ECC fault for both single bit and double bit faults. The FECCR register provides access to several ECC related fields as defined by the ECCRIX index bits in the FECCRIX register (see Section 20.3.2.4). Once ECC fault information has been stored, no other

#### 64 KByte Flash Module (S12XFTMR64K1V1)

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |  |  |  |  |  |

|-------------|----------------------------------------------------------|----------------------------------------------|--|--|--|--|--|

| 000         | 0x03                                                     | Global address [22:16] of<br>a P-Flash block |  |  |  |  |  |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |  |  |  |  |  |

| 010         | Number of phrases to be verified                         |                                              |  |  |  |  |  |

Table 20-35. Erase Verify P-Flash Section Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed.

| Register | Error Bit | Error Condition                                                                      |  |  |  |  |  |  |

|----------|-----------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                                          |  |  |  |  |  |  |

|          |           | Set if command not available in current mode (see Table 20-28)                       |  |  |  |  |  |  |

|          | ACCERR    | Set if an invalid global address [22:0] is supplied <sup>1</sup>                     |  |  |  |  |  |  |

| FOTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)         |  |  |  |  |  |  |

| FSTAT    |           | Set if the requested section crosses a 128 Kbyte boundary                            |  |  |  |  |  |  |

|          | FPVIOL    | None                                                                                 |  |  |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read <sup>2</sup>                 |  |  |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read <sup>2</sup> |  |  |  |  |  |  |

Table 20-36. Erase Verify P-Flash Section Command Error Handling

<sup>1</sup> As defined by the memory map for FTMR128K1.

100

<sup>2</sup> As found in the memory map for FTMR128K1.

### 20.4.2.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash block 0. The Read Once field is programmed using the Program Once command described in Section 20.4.2.6. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Pa               | arameters                                |  |  |  |  |  |

|-------------|------------------------|------------------------------------------|--|--|--|--|--|

| 000         | 0x04                   | Not Required                             |  |  |  |  |  |

| 001         | Read Once phrase inc   | Read Once phrase index (0x0000 - 0x0007) |  |  |  |  |  |

| 010         | Read Once word 0 value |                                          |  |  |  |  |  |

| 011         | Read Once              | word 1 value                             |  |  |  |  |  |

Read Once word 2 value

Read Once word 3 value

Table 20-37. Read Once Command FCCOB Requirements

#### **Electrical Characteristics**

### A.3.1.8 Erase P-Flash Block (FCMD=0x09)

Erasing a 256K NVM block takes

$$t_{\text{mass}} \approx 100100 \cdot \frac{1}{f_{\text{NVMOP}}} + 70000 \cdot \frac{1}{f_{\text{NVMBUS}}}$$

Erasing a 128K NVM block takes

$t_{mass} \approx 100100 \cdot \frac{1}{f_{NVMOP}} + 35000 \cdot \frac{1}{f_{NVMBUS}}$

### A.3.1.9 Erase P-Flash Sector (FCMD=0x0A)

The typical time to erase a1024-byte P-Flash sector can be calculated using

$$\mathbf{t}_{era} = \left(20020 \cdot \frac{1}{\mathbf{f}_{\text{NVMOP}}}\right) + \left(700 \cdot \frac{1}{\mathbf{f}_{\text{NVMBUS}}}\right)$$

The maximum time to erase a1024-byte P-Flash sector can be calculated using

$$\mathbf{t}_{era} = \left(20020 \cdot \frac{1}{f_{\mathrm{NVMOP}}}\right) + \left(1100 \cdot \frac{1}{f_{\mathrm{NVMBUS}}}\right)$$

### A.3.1.10 Unsecure Flash (FCMD=0x0B)

The maximum time for unsecuring the flash is given by

$$t_{uns} = \left(100100 \cdot \frac{1}{f_{NVMOP}} + 70000 \cdot \frac{1}{f_{NVMBUS}}\right)$$

### A.3.1.11 Verify Backdoor Access Key (FCMD=0x0C)

The maximum verify backdoor access key time is given by

$$t = 400 \cdot \frac{1}{f_{\text{NVMBUS}}}$$

### A.3.1.12 Set User Margin Level (FCMD=0x0D)

The maximum set user margin level time is given by

$$t= 350 \cdot \frac{1}{f_{\rm NVMBUS}}$$

### A.3.1.13 Set Field Margin Level (FCMD=0x0E)

The maximum set field margin level time is given by

Package Information

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | ON NOT TO SCALE |  |

|---------------------------------------------------------|-----------|--------------|------------------|-----------------|--|

| TITLE: 112LD LQFP                                       |           | DOCUMENT NO  | ): 98ASS23330W   | REV: F          |  |

| 20 X 20 X 1.4                                           |           | CASE NUMBER  | 8: 987–03        | 15 DEC 2006     |  |

| 0.65 PITCH                                              |           | STANDARD: JE | DEC MS-026 BFA   |                 |  |

Figure B-2. 112-pin LQFP (case no. 987) - page 2

S12XS Family Reference Manual, Rev. 1.13

# Appendix E Detailed Register Address Map

# E.1 Detailed Register Map

The following tables show the detailed register map of the S12XS family.

### 0x0000–0x0009 Port Integration Module (PIM) Map 1 of 5

| Address | Name            | _      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0000  | PORTA           | R<br>W | PA7   | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA 0  |

| 0x0001  | PORTB           | R<br>W | PB7   | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   |

| 0x0002  | DDRA            | R<br>W | DDRA7 | DDRA6 | DDRA5 | DDRA4 | DDRA3 | DDRA2 | DDRA1 | DDRA0 |

| 0x0003  | DDRB            | R<br>W | DDRB7 | DDRB6 | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 |

| 0x0004  | Reserved        | R      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0,0001  | 1 cool vou      | W      |       |       |       |       |       |       |       |       |

| 0x0005  | Reserved        | R      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0,0000  | Reserved        | W      |       |       |       |       |       |       |       |       |

| 0.0000  | 0x0006 Reserved | R      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 00000   |                 | W      |       |       |       |       |       |       |       |       |

| 00007   | Reserved        | R      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0007  |                 | w      |       |       |       |       |       |       |       |       |

| 0x0008  | DODTE           | R      |       | DEO   | DEC   |       | DEO   | DEO   | PE1   | PE0   |

|         | PORTE           | w      | PE7   | PE6   | PE5   | PE4   | PE3   | PE2   |       |       |

| 0,0000  | DDDE            | R      |       |       |       |       |       |       | 0     | 0     |

| 0x0009  | DDRE            | W      | DDRE7 | DDRE6 | DDRE5 | DDRE4 | DDRE3 | DDRE2 |       |       |

### 0x000A–0x000B Module Mapping Control (S12XMMC) Map 1 of 2

| Address | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x000A  | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x000A  | Reserveu | W |       |       |       |       |       |       |       |       |

| 0x000B  | MODE     | R | MODC  | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         | MODE     | W | NODC  |       |       |       |       |       |       |       |

### 0x000C–0x000D Port Integration Module (PIM) Map 2 of 5

| Address | Name  |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |      |

|---------|-------|---|-------|-------|-------|-------|-------|-------|-------|-------|--|--|------|

| 0x000C  | PUCR  | R | PUPKE | BKPUE | 0     | PUPEE | 0     | 0     | PUPBE | PUPAE |  |  |      |

| 00000   | FUCK  | W |       | DRIOL | DRIVE | TOLL  |       |       | TOTEL | TOTAL |  |  |      |

| 0x000D  | RDRIV | R | RDPK  | 0     | 0     | RDPE  | 0     | 0     | RDPB  | RDPA  |  |  |      |

| 0x000D  |       |   |       | NDNIV | W     | NUTK  |       |       |       |       |  |  | NULA |