Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 40MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 91                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 112-LQFP                                                                |

| Supplier Device Package    | 112-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs128j1mal |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## NOTE

If there is more than one function associated with a pin, the priority is indicated by the position in the table from top (highest priority) to bottom (lowest priority)

| Port                  | Pin Name                                            | Pin Function<br>& Priority <sup>1</sup> | I/O                                                   | Description                                                                | Pin Function<br>after Reset |

|-----------------------|-----------------------------------------------------|-----------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------|

| -                     | BKGD                                                | MODC <sup>2</sup>                       | I                                                     | MODC input during RESET                                                    | BKGD                        |

|                       |                                                     | BKGD                                    | I/O                                                   | S12X_BDM communication pin                                                 |                             |

| Α                     | PA[7:0]                                             | GPIO                                    | I/O                                                   | General purpose                                                            | GPIO                        |

| В                     | PB[7:0]                                             | GPIO                                    | I/O                                                   | General purpose                                                            | GPIO                        |

| Е                     | PE[7]                                               | XCLKS <sup>2</sup>                      | I                                                     | External clock selection input during RESET                                | GPIO                        |

|                       |                                                     | ECLKX2                                  | 0                                                     | Free-running clock at core clock rate (ECLK x 2)                           |                             |

|                       |                                                     | GPIO                                    | I/O                                                   | General purpose                                                            |                             |

|                       | PE[6:5]                                             | GPIO                                    | I/O                                                   | General purpose                                                            |                             |

|                       | PE[4]                                               | ECLK                                    | 0                                                     | Free-running clock at bus clock rate or programmable down-scaled bus clock |                             |

|                       |                                                     | GPIO                                    | I/O                                                   | General purpose                                                            |                             |

|                       | PE[3:2]                                             | GPIO                                    | I/O                                                   | General purpose                                                            |                             |

|                       | PE[1]                                               | ĪRQ                                     | I Maskable level- or falling edge-sensitive interrupt |                                                                            |                             |

| GPI I General-purpose |                                                     | General-purpose                         |                                                       |                                                                            |                             |

|                       | PE[0] XIRQ I Non-maskable level-sensitive interrupt |                                         | Non-maskable level-sensitive interrupt                |                                                                            |                             |

|                       |                                                     | GPI                                     | I                                                     | General-purpose                                                            |                             |

| к                     | PK[7,5:0]                                           | GPIO                                    | I/O                                                   | General purpose                                                            | GPIO                        |

Table 2-1. Pin Functions and Priorities

#### Table 2-39. PTP Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PTP   | <b>Port P general purpose input/output data</b> —Data Register, PWM input/output, pin interrupt input/output<br>When not used with the alternative function, the associated pin can be used as general purpose I/O. In general<br>purpose output mode the register bit value is driven to the pin.<br>If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered<br>pin input state is read.                        |

|            | <ul> <li>The PWM function takes precedence over the general purpose I/O function if the related channel or the emergency shut-down feature is enabled.</li> <li>Pin interrupts can be generated if enabled in input or output mode.</li> </ul>                                                                                                                                                                                                                                       |

| 6-3<br>PTP | <b>Port P general purpose input/output data</b> —Data Register, PWM output, pin interrupt input/output<br>When not used with the alternative function, the associated pin can be used as general purpose I/O. In general<br>purpose output mode the register bit value is driven to the pin.<br>If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered<br>pin input state is read.                              |

|            | <ul> <li>The PWM function takes precedence over the general purpose I/O function if the related channel is enabled.</li> <li>Pin interrupts can be generated if enabled in input or output mode.</li> </ul>                                                                                                                                                                                                                                                                          |

| 2<br>PTP   | Port P general purpose input/output data—Data Register, PWM output, routed TIM output, routed SCI1 TXD output, pin interrupt input/output<br>When not used with the alternative function, the associated pin can be used as general purpose I/O. In general purpose output mode the register bit value is driven to the pin.<br>If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered pin input state is read. |

|            | <ul> <li>The PWM function takes precedence over the TIM, SCI1 and general purpose I/O function if the related channel is enabled.</li> <li>The TIM function takes precedence over SCI1 and the general purpose I/O function if the related channel is enabled.</li> <li>The SCI1 function takes precedence over the general purpose I/O function if enabled.</li> <li>Pin interrupts can be generated if enabled in input or output mode.</li> </ul>                                 |

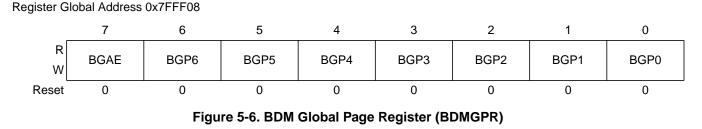

# 5.3.2.4 BDM Global Page Index Register (BDMGPR)

Read: All modes through BDM operation when not secured

Write: All modes through BDM operation when not secured

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>BGAE       | <ul> <li>BDM Global Page Access Enable Bit — BGAE enables global page access for BDM hardware and firmware read/write instructions The BDM hardware commands used to access the BDM registers (READ_BD_ and WRITE_BD_) can not be used for global accesses even if the BGAE bit is set.</li> <li>0 BDM Global Access disabled</li> <li>1 BDM Global Access enabled</li> </ul> |

| 6–0<br>BGP[6:0] | <b>BDM Global Page Index Bits 6–0</b> — These bits define the extended address bits from 22 to 16. For more detailed information regarding the global page window scheme, please refer to the S12X_MMC Block Guide.                                                                                                                                                           |

## 5.3.3 Family ID Assignment

The family ID is a 8-bit value located in the firmware ROM (at global address: 0x7FFF0F). The read-only value is a unique family ID which is 0xC1 for S12X devices.

# 5.4 Functional Description

The BDM receives and executes commands from a host via a single wire serial interface. There are two types of BDM commands: hardware and firmware commands.

Hardware commands are used to read and write target system memory locations and to enter active background debug mode, see Section 5.4.3, "BDM Hardware Commands". Target system memory includes all memory that is accessible by the CPU.

Firmware commands are used to read and write CPU resources and to exit from active background debug mode, see Section 5.4.4, "Standard BDM Firmware Commands". The CPU resources referred to are the accumulator (D), X index register (X), Y index register (Y), stack pointer (SP), and program counter (PC).

Hardware commands can be executed at any time and in any mode excluding a few exceptions as highlighted (see Section 5.4.3, "BDM Hardware Commands") and in secure mode (see Section 5.4.1, "Security"). Firmware commands can only be executed when the system is not secure and is in active background debug mode (BDM).

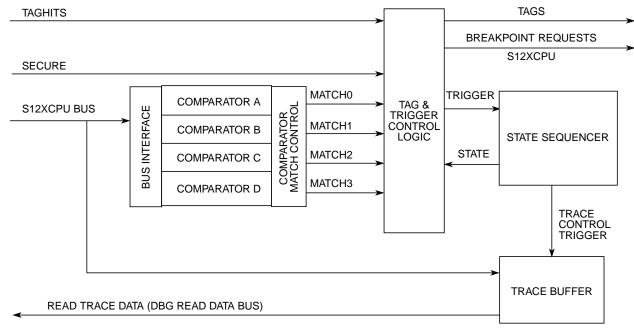

S12X Debug (S12XDBGV3) Module

# 6.1.5 Block Diagram

Figure 6-1. Debug Module Block Diagram

# 6.2 External Signal Description

The S12XDBG sub-module features no external signals.

# 6.3 Memory Map and Registers

## 6.3.1 Module Memory Map

A summary of the registers associated with the S12XDBG sub-block is shown in Table 6-2. Detailed descriptions of the registers and bits are given in the subsections that follow.

| Address | Name   |        | Bit 7   | 6         | 5        | 4   | 3      | 2        | 1    | Bit 0 |

|---------|--------|--------|---------|-----------|----------|-----|--------|----------|------|-------|

| 0x0020  | DBGC1  | R<br>W | ARM     | 0<br>TRIG | reserved | BDM | DBGBRK | reserved | CON  | MRV   |

| 0x0021  | DBGSR  | R<br>W | TBF     | 0         | 0        | 0   | 0      | SSF2     | SSF1 | SSF0  |

| 0x0022  | DBGTCR | R<br>W | eserved | TSOURCE   | TRAI     | NGE | TRCI   | MOD      | TAL  | IGN   |

| 0x0023  | DBGC2  | R<br>W | 0       | 0         | 0        | 0   | CDCM   |          | AB   | СМ    |

Figure 6-2. Quick Reference to S12XDBG Registers

| SC[3:0] | Description                                                                           |

|---------|---------------------------------------------------------------------------------------|

| 0111    | Match1 triggers to State3 Match0 triggers Final State Other matches have no effect    |

| 1000    | Match0 triggers to State2 Match2 triggers to State3 Other matches have no effect      |

| 1001    | Match2 triggers to State3 Match0 triggers Final State Other matches have no effect    |

| 1010    | Match1 triggers to State2 Match3 triggers to State3 Other matches have no effect      |

| 1011    | Match3 triggers to State3 Match1 triggers to Final State Other matches have no effect |

| 1100    | Match3 has no effect All other matches (M0,M1,M2) trigger to State2                   |

| 1101    | Reserved. (No match triggers state sequencer transition)                              |

| 1110    | Reserved. (No match triggers state sequencer transition)                              |

| 1111    | Reserved. (No match triggers state sequencer transition)                              |

| Table 6-20. State | Sequencer l | Next State Selectio | n (continued) |

|-------------------|-------------|---------------------|---------------|

|-------------------|-------------|---------------------|---------------|

The trigger priorities described in Table 6-39 dictate that in the case of simultaneous matches, the match on the lower channel number (0,1,2,3) has priority. The SC[3:0] encoding ensures that a match leading to final state has priority over all other matches.

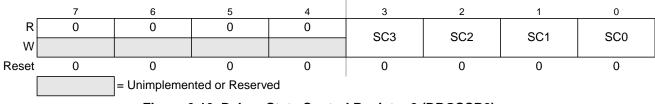

### 6.3.2.7.2 Debug State Control Register 2 (DBGSCR2)

Address: 0x0027

#### Figure 6-10. Debug State Control Register 2 (DBGSCR2)

#### Read: If COMRV[1:0] = 01

Write: If COMRV[1:0] = 01 and S12XDBG is not armed.

This register is visible at 0x0027 only with COMRV[1:0] = 01. The state control register 2 selects the targeted next state whilst in State2. The matches refer to the match channels of the comparator match control logic as depicted in Figure 6-1 and described in Section 6.3.2.8.1. Comparators must be enabled by setting the comparator enable bit in the associated DBGXCTL control register.

#### Table 6-21. DBGSCR2 Field Descriptions

| Field          | Description                                                                             |

|----------------|-----------------------------------------------------------------------------------------|

| 3–0<br>SC[3:0] | These bits select the targeted next state whilst in State2, based upon the match event. |

#### Table 6-22. State2 — Sequencer Next State Selection

| SC[3:0] | Description                                            |  |  |  |  |  |

|---------|--------------------------------------------------------|--|--|--|--|--|

| 0000    | Any match triggers to state1                           |  |  |  |  |  |

| 0001    | Any match triggers to state3                           |  |  |  |  |  |

| 0010    | Any match triggers to Final State                      |  |  |  |  |  |

| 0011    | Match3 triggers to State1 Other matches have no effect |  |  |  |  |  |

| 0100    | Match3 triggers to State3 Other matches have no effect |  |  |  |  |  |

Write: Only in special modes

## 8.3.2.12 S12XECRG COP Timer Arm/Reset Register (ARMCOP)

This register is used to restart the COP time-out period.

Module Base + 0x000B

|       | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| R     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| w     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 8-14. S12XECRG ARMCOP Register Diagram

Read: Always reads \$00

Write: Anytime

When the COP is disabled (CR[2:0] = "000") writing to this register has no effect.

When the COP is enabled by setting CR[2:0] nonzero, the following applies:

Writing any value other than \$55 or \$AA causes a COP reset. To restart the COP time-out period you must write \$55 followed by a write of \$AA. Other instructions may be executed between these writes but the sequence (\$55, \$AA) must be completed prior to COP end of time-out period to avoid a COP reset. Sequences of \$55 writes or sequences of \$AA writes are allowed. When the WCOP bit is set, \$55 and \$AA writes must be done in the last 25% of the selected time-out period; writing any value in the first 75% of the selected period will cause a COP reset.

## 13.3.2.7 Reserved Register (PWMTST)

This register is reserved for factory testing of the PWM module and is not available in normal modes.

Module Base + 0x0006

Figure 13-9. Reserved Register (PWMTST)

Read: Always read \$00 in normal modes

Write: Unimplemented in normal modes

NOTE

Writing to this register when in special modes can alter the PWM functionality.

### 13.3.2.8 Reserved Register (PWMPRSC)

This register is reserved for factory testing of the PWM module and is not available in normal modes.

Module Base + 0x0007

Figure 13-10. Reserved Register (PWMPRSC)

Read: Always read \$00 in normal modes

Write: Unimplemented in normal modes

#### NOTE

Writing to this register when in special modes can alter the PWM functionality.

## 13.3.2.9 PWM Scale A Register (PWMSCLA)

PWMSCLA is the programmable scale value used in scaling clock A to generate clock SA. Clock SA is generated by taking clock A, dividing it by the value in the PWMSCLA register and dividing that by two.

Clock SA = Clock A / (2 \* PWMSCLA)

On the front end of the PWM timer, the clock is enabled to the PWM circuit by the PWMEx bit being high. There is an edge-synchronizing circuit to guarantee that the clock will only be enabled or disabled at an edge. When the channel is disabled (PWMEx = 0), the counter for the channel does not count.

## 13.4.2.2 PWM Polarity

Each channel has a polarity bit to allow starting a waveform cycle with a high or low signal. This is shown on the block diagram as a mux select of either the Q output or the  $\overline{Q}$  output of the PWM output flip flop. When one of the bits in the PWMPOL register is set, the associated PWM channel output is high at the beginning of the waveform, then goes low when the duty count is reached. Conversely, if the polarity bit is zero, the output starts low and then goes high when the duty count is reached.

## 13.4.2.3 PWM Period and Duty

Dedicated period and duty registers exist for each channel and are double buffered so that if they change while the channel is enabled, the change will NOT take effect until one of the following occurs:

- The effective period ends

- The counter is written (counter resets to \$00)

- The channel is disabled

In this way, the output of the PWM will always be either the old waveform or the new waveform, not some variation in between. If the channel is not enabled, then writes to the period and duty registers will go directly to the latches as well as the buffer.

A change in duty or period can be forced into effect "immediately" by writing the new value to the duty and/or period registers and then writing to the counter. This forces the counter to reset and the new duty and/or period values to be latched. In addition, since the counter is readable, it is possible to know where the count is with respect to the duty value and software can be used to make adjustments

### NOTE

When forcing a new period or duty into effect immediately, an irregular PWM cycle can occur.

Depending on the polarity bit, the duty registers will contain the count of either the high time or the low time.

## 13.4.2.4 PWM Timer Counters

Each channel has a dedicated 8-bit up/down counter which runs at the rate of the selected clock source (see Section 13.4.1, "PWM Clock Select" for the available clock sources and rates). The counter compares to two registers, a duty register and a period register as shown in Figure 13-19. When the PWM counter matches the duty register, the output flip-flop changes state, causing the PWM waveform to also change state. A match between the PWM counter and the period register behaves differently depending on what output mode is selected as shown in Figure 13-19 and described in Section 13.4.2.5, "Left Aligned Outputs" and Section 13.4.2.6, "Center Aligned Outputs".

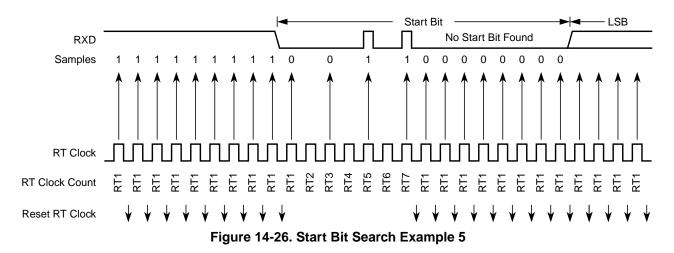

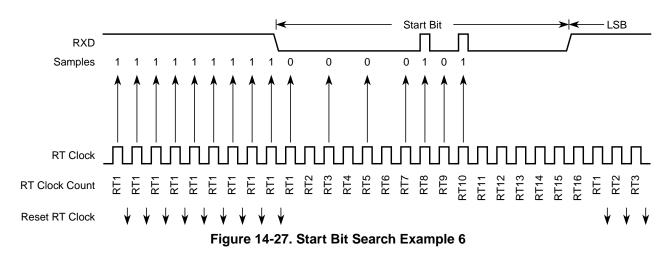

Figure 14-26 shows a burst of noise near the beginning of the start bit that resets the RT clock. The sample after the reset is low but is not preceded by three high samples that would qualify as a falling edge. Depending on the timing of the start bit search and on the data, the frame may be missed entirely or it may set the framing error flag.

In Figure 14-27, a noise burst makes the majority of data samples RT8, RT9, and RT10 high. This sets the noise flag but does not reset the RT clock. In start bits only, the RT8, RT9, and RT10 data samples are ignored.

## 14.4.6.4 Framing Errors

If the data recovery logic does not detect a logic 1 where the stop bit should be in an incoming frame, it sets the framing error flag, FE, in SCI status register 1 (SCISR1). A break character also sets the FE flag because a break character has no stop bit. The FE flag is set at the same time that the RDRF flag is set.

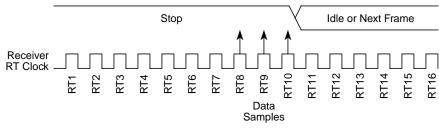

### 14.4.6.5.2 Fast Data Tolerance

Figure 14-29 shows how much a fast received frame can be misaligned. The fast stop bit ends at RT10 instead of RT16 but is still sampled at RT8, RT9, and RT10.

For an 8-bit data character, it takes the receiver 9 bit times x 16 RTr cycles + 10 RTr cycles = 154 RTr cycles to finish data sampling of the stop bit.

With the misaligned character shown in Figure 14-29, the receiver counts 154 RTr cycles at the point when the count of the transmitting device is 10 bit times x 16 RTt cycles = 160 RTt cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is:

$((160 - 154) / 160) \ge 100 = 3.75\%$

For a 9-bit data character, it takes the receiver 10 bit times x 16 RTr cycles + 10 RTr cycles = 170 RTr cycles to finish data sampling of the stop bit.

With the misaligned character shown in Figure 14-29, the receiver counts 170 RTr cycles at the point when the count of the transmitting device is 11 bit times x 16 RTt cycles = 176 RTt cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is:

$((176 - 170) / 176) \ge 100 = 3.40\%$

### 14.4.6.6 Receiver Wakeup

To enable the SCI to ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCI control register 2 (SCICR2) puts the receiver into standby state during which receiver interrupts are disabled. The SCI will still load the receive data into the SCIDRH/L registers, but it will not set the RDRF flag.

The transmitting device can address messages to selected receivers by including addressing information in the initial frame or frames of each message.

The WAKE bit in SCI control register 1 (SCICR1) determines how the SCI is brought out of the standby state to process an incoming message. The WAKE bit enables either idle line wakeup or address mark wakeup.

# Chapter 17 Voltage Regulator (S12VREGL3V3V1)

| Rev. No.<br>(Item No.) | Date<br>(Submitted By) | Sections<br>Affected | Substantial Change(s)                            |

|------------------------|------------------------|----------------------|--------------------------------------------------|

| V01.02                 | 09 Sep 2005            |                      | Updates for API external access and LVR flags.   |

| V01.03                 | 23 Sep 2005            |                      | VAE reset value is 1.                            |

| V01.04                 | 08 Jun 2007            |                      | Added temperature sensor to customer information |

#### Table 17-1. Revision History Table

# 17.1 Introduction

Module VREG\_3V3 is a tri output voltage regulator that provides two separate 1.84V (typical) supplies differing in the amount of current that can be sourced and a 2.82V (typical) supply. The regulator input voltage range is from 3.3V up to 5V (typical).

## 17.1.1 Features

Module VREG\_3V3 includes these distinctive features:

- Three parallel, linear voltage regulators with bandgap reference

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR)

- Low-voltage reset (LVR)

- High Temperature Detect (HTD) with High Temperature Interrupt (HTI)

- Autonomous periodical interrupt (API)

## 17.1.2 Modes of Operation

There are three modes VREG\_3V3 can operate in:

- Full performance mode (FPM) (MCU is not in stop mode) The regulator is active, providing the nominal supply voltages with full current sourcing capability. Features LVD (low-voltage detect), LVR (low-voltage reset), and POR (power-on reset) and HTD (High Temperature Detect) are available. The API is available.

- 2. Reduced power mode (RPM) (MCU is in stop mode)

The purpose is to reduce power consumption of the device. The output voltage may degrade to a lower value than in full performance mode, additionally the current sourcing capability is substantially reduced. Only the POR is available in this mode, LVD, LVR and HTD are disabled. The API is available.

Voltage Regulator (S12VREGL3V3V1)

# 17.3.2.2 Control Register (VREGCTRL)

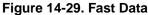

The VREGCTRL register allows the configuration of the VREG\_3V3 low-voltage detect features.

0x02F1

#### Figure 17-2. Control Register (VREGCTRL)

### Table 17-5. VREGCTRL Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>LVDS | <ul> <li>Low-Voltage Detect Status Bit — This read-only status bit reflects the input voltage. Writes have no effect.</li> <li>Input voltage V<sub>DDA</sub> is above level V<sub>LVID</sub> or RPM or shutdown mode.</li> <li>Input voltage V<sub>DDA</sub> is below level V<sub>LVIA</sub> and FPM.</li> </ul>                                                                                |

| 1<br>LVIE | Low-Voltage Interrupt Enable Bit         0 Interrupt request is disabled.         1 Interrupt will be requested whenever LVIF is set.                                                                                                                                                                                                                                                           |

| 0<br>LVIF | <ul> <li>Low-Voltage Interrupt Flag — LVIF is set to 1 when LVDS status bit changes. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (LVIE = 1), LVIF causes an interrupt request.</li> <li>0 No change in LVDS bit.</li> <li>1 LVDS bit has changed.</li> <li>Note: On entering the Reduced Power Mode the LVIF is not cleared by the VREG_3V3.</li> </ul> |

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>CCIF          | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command completion or command violation.</li> <li>0 Flash command in progress</li> <li>1 Flash command has completed</li> </ul>                                                                                                                                           |  |  |  |  |  |

| 5<br>ACCERR        | Flash Access Error Flag — The ACCERR bit indicates an illegal access has occurred to the Flash memory caused by either a violation of the command write sequence (see Section 18.4.1.2) or issuing an illegal Flash command. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR.<br>0 No access error detected<br>1 Access error detected        |  |  |  |  |  |

| 4<br>FPVIOL        | Flash Protection Violation Flag — The FPVIOL bit indicates an attempt was made to program or erase an<br>address in a protected area of P-Flash or D-Flash memory during a command write sequence. The FPVIOL<br>bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL<br>is set, it is not possible to launch a command or start a command write sequence.0No protection violation detected1Protection violation detected |  |  |  |  |  |

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                                                                                                                                                                                                              |  |  |  |  |  |

| 2<br>RSVD          | Reserved Bit — This bit is reserved and always reads 0.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 1–0<br>MGSTAT[1:0] | Memory Controller Command Completion Status Flag — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 18.4.2, "Flash Command Description," and Section 18.6, "Initialization" for details.                                                                                                                                                                                          |  |  |  |  |  |

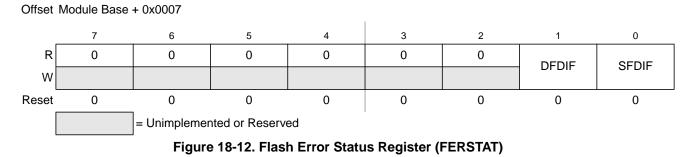

## 18.3.2.8 Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

All flags in the FERSTAT register are readable and only writable to clear the flag.

### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

The Flash memory may be read as bytes, aligned words, or misaligned words. Read access time is one bus cycle for bytes and aligned words, and two bus cycles for misaligned words. For Flash memory, an erased bit reads 1 and a programmed bit reads 0.

It is not possible to read from a Flash block while any command is executing on that specific Flash block. It is possible to read from a Flash block while a command is executing on a different Flash block.

Both P-Flash and D-Flash memories are implemented with Error Correction Codes (ECC) that can resolve single bit faults and detect double bit faults. For P-Flash memory, the ECC implementation requires that programming be done on an aligned 8 byte basis (a Flash phrase). Since P-Flash memory is always read by phrase, only one single bit fault in the phrase containing the byte or word accessed will be corrected.

## 19.1.1 Glossary

**Command Write Sequence** — An MCU instruction sequence to execute built-in algorithms (including program and erase) on the Flash memory.

**D-Flash Memory** — The D-Flash memory constitutes the nonvolatile memory store for data.

**D-Flash Sector** — The D-Flash sector is the smallest portion of the D-Flash memory that can be erased. The D-Flash sector consists of four 64 byte rows for a total of 256 bytes.

**NVM Command Mode** — An NVM mode using the CPU to setup the FCCOB register to pass parameters required for Flash command execution.

**Phrase** — An aligned group of four 16-bit words within the P-Flash memory. Each phrase includes eight ECC bits for single bit fault correction and double bit fault detection within the phrase.

P-Flash Memory — The P-Flash memory constitutes the main nonvolatile memory store for applications.

**P-Flash Sector** — The P-Flash sector is the smallest portion of the P-Flash memory that can be erased. Each P-Flash sector contains 1024 bytes.

**Program IFR** — Nonvolatile information register located in the P-Flash block that contains the Device ID, Version ID, and the Program Once field. The Program IFR is visible in the global memory map by setting the PGMIFRON bit in the MMCCTL1 register.

## 19.1.2 Features

## 19.1.2.1 P-Flash Features

- 128 Kbytes of P-Flash memory composed of one 128 Kbyte Flash block divided into 128 sectors of 1024 bytes

- Single bit fault correction and double bit fault detection within a 64-bit phrase during read operations

128 KByte Flash Module (S12XFTMR128K1V1)

### 19.3.2.9.1 P-Flash Protection Restrictions

The general guideline is that P-Flash protection can only be added and not removed. Table 19-21 specifies all valid transitions between P-Flash protection scenarios. Any attempt to write an invalid scenario to the FPROT register will be ignored. The contents of the FPROT register reflect the active protection scenario. See the FPHS and FPLS bit descriptions for additional restrictions.

| From                   | To Protection Scenario <sup>1</sup> |   |   |   |   |   |   |   |  |

|------------------------|-------------------------------------|---|---|---|---|---|---|---|--|

| Protection<br>Scenario | 0                                   | 1 | 2 | 3 | 4 | 5 | 6 | 7 |  |

| 0                      | Х                                   | Х | Х | Х |   |   |   |   |  |

| 1                      |                                     | Х |   | Х |   |   |   |   |  |

| 2                      |                                     |   | Х | Х |   |   |   |   |  |

| 3                      |                                     |   |   | Х |   |   |   |   |  |

| 4                      |                                     |   |   | Х | Х |   |   |   |  |

| 5                      |                                     |   | Х | Х | Х | Х |   |   |  |

| 6                      |                                     | Х |   | Х | Х |   | Х |   |  |

| 7                      | Х                                   | Х | Х | Х | Х | Х | Х | Х |  |

Table 19-21. P-Flash Protection Scenario Transitions

<sup>1</sup> Allowed transitions marked with X, see Figure 19-14 for a definition of the scenarios.

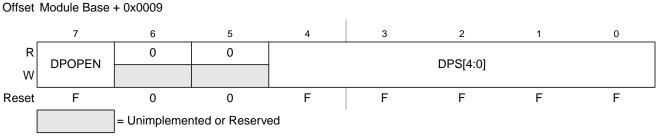

## 19.3.2.10 D-Flash Protection Register (DFPROT)

The DFPROT register defines which D-Flash sectors are protected against program and erase operations.

The (unreserved) bits of the DFPROT register are writable with the restriction that protection can be added but not removed. Writes must increase the DPS value and the DPOEN bit can only be written from 1 (protection disabled) to 0 (protection enabled). If the DPOPEN bit is set, the state of the DPS bits is irrelevant.

During the reset sequence, the DFPROT register is loaded with the contents of the D-Flash protection byte in the Flash configuration field at global address 0x7F\_FF0D located in P-Flash memory (see Table 19-3) as indicated by reset condition F in Figure 19-15. To change the D-Flash protection that will be loaded during the reset sequence, the P-Flash sector containing the D-Flash protection byte must be unprotected, then the D-Flash protection byte must be programmed. If a double bit fault is detected while reading the

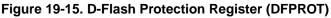

Figure 20-26. Generic Flash Command Write Sequence Flowchart

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 20-28)                      |

|          |           | Set if an invalid phrase index is supplied                                          |

| FSTAT    |           | Set if the requested phrase has already been programmed <sup>1</sup>                |

|          | FPVIOL    | None                                                                                |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

### 20.4.2.7 Erase All Blocks Command

The Erase All Blocks operation will erase the entire P-Flash and D-Flash memory space.

#### Table 20-43. Erase All Blocks Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |  |  |

|-------------|------------------|--------------|--|--|--|

| 000         | 0x08             | Not required |  |  |  |

Upon clearing CCIF to launch the Erase All Blocks command, the Memory Controller will erase the entire Flash memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag will set after the Erase All Blocks operation has completed.

| Register | Error Bit | Error Condition                                                                                  |  |  |  |  |  |

|----------|-----------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                      |  |  |  |  |  |

|          |           | Set if command not available in current mode (see Table 20-28)                                   |  |  |  |  |  |

| FSTAT    | FPVIOL    | Set if any area of the P-Flash or D-Flash memory is protected                                    |  |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation <sup>1</sup>                 |  |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation <sup>1</sup> |  |  |  |  |  |

<sup>1</sup> As found in the memory map for FTMR128K1.

### 20.4.2.8 Erase Flash Block Command

The Erase Flash Block operation will erase all addresses in a P-Flash or D-Flash block.

**Electrical Characteristics**

| Num | С                                                                                 | Rating                                                                            | Symbol          | Min | Тур | Max | Unit |  |  |

|-----|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|--|--|

|     | LQFP 112                                                                          |                                                                                   |                 |     |     |     |      |  |  |

| 1   | D                                                                                 | Thermal resistance LQFP 112, single sided PCB <sup>2</sup>                        | θ <sub>JA</sub> |     |     | 62  | °C/W |  |  |

| 2   | D                                                                                 | Thermal resistance LQFP 112, double sided PCB with 2 internal planes <sup>3</sup> | θ <sub>JA</sub> | _   | _   | 51  | °C/W |  |  |

| 3   | D                                                                                 | Junction to Board LQFP 112                                                        | θ <sub>JB</sub> | _   | _   | 39  | °C/W |  |  |

| 4   | D                                                                                 | Junction to Case LQFP 112 <sup>4</sup>                                            | θ <sub>JC</sub> |     | _   | 16  | °C/W |  |  |

| 5   | D                                                                                 | Junction to Package Top LQFP 112 <sup>5</sup>                                     | Ψ <sub>JT</sub> | _   | _   | 3   | °C/W |  |  |

|     |                                                                                   | QFP 80                                                                            |                 |     |     |     |      |  |  |

| 6   | D                                                                                 | Thermal resistance QFP 80, single sided PCB <sup>2</sup>                          | θ <sub>JA</sub> | _   | _   | 57  | °C/W |  |  |

| 7   | D Thermal resistance QFP 80, double sided PCB with 2 internal planes <sup>3</sup> |                                                                                   | θ <sub>JA</sub> | _   | _   | 45  | °C/W |  |  |

| 8   | D                                                                                 | D Junction to Board QFP 80                                                        |                 |     | _   | 29  | °C/W |  |  |

| 9   | D Junction to Case QFP 80 <sup>4</sup>                                            |                                                                                   | θ <sub>JC</sub> | _   | _   | 20  | °C/W |  |  |

| 10  | D                                                                                 | Junction to Package Top QFP 80 <sup>5</sup>                                       | Ψ <sub>JT</sub> |     | _   | 5   | °C/W |  |  |

|     |                                                                                   | LQFP 64                                                                           |                 |     |     |     | •    |  |  |

| 11  | D                                                                                 | Thermal resistance LQFP 64, single sided PCB <sup>2</sup>                         | θ <sub>JA</sub> | _   | _   | 68  | °C/W |  |  |

| 12  | D                                                                                 | Thermal resistance LQFP 64, double sided PCB with 2 internal planes <sup>3</sup>  | θ <sub>JA</sub> | _   | —   | 50  | °C/W |  |  |

| 13  | D                                                                                 | Junction to Board LQFP 64                                                         | θ <sub>JB</sub> | _   | _   | 32  | °C/W |  |  |

| 14  | D                                                                                 | Junction to Case LQFP 64 <sup>4</sup>                                             | θJC             | _   |     | 15  | °C/W |  |  |

| 15  | D                                                                                 | Junction to Package Top LQFP 64 <sup>5</sup>                                      | Ψ <sub>JT</sub> |     |     | 3   | °C/W |  |  |

| Table A-5. Thermal Package Characteristics | (9S12XS256) <sup>1</sup> |

|--------------------------------------------|--------------------------|

|--------------------------------------------|--------------------------|

1

2

3

The values for thermal resistance are achieved by package simulations Junction to ambient thermal resistance,  $\theta_{JA}$  was simulated to be equivalent to the JEDEC specification JESD51-2 in a horizontal configuration in natural convection. Junction to ambient thermal resistance,  $\theta_{JA}$  was simulated to be equivalent to the JEDEC specification JESD51-7 in a horizontal configuration in natural convection. Junction to case thermal resistance was simulated to be equivalent to the measured values using the cold plate technique with the cold plate temperature used as the "case" temperature. This basic cold plate measurement technique is described by MIL-STD 883D, Method 1012.1. This is the correct thermal metric to use to calculate thermal performance when the package is being used with a best sink 4 being used with a heat sink.

Thermal characterization parameter  $\Psi_{JT}$  is the "resistance" from junction to reference point thermocouple on top center of the case as defined in JESD51-2.  $\Psi_{JT}$  is a useful value to use to estimate junction temperature in a steady state customer 5 enviroment.

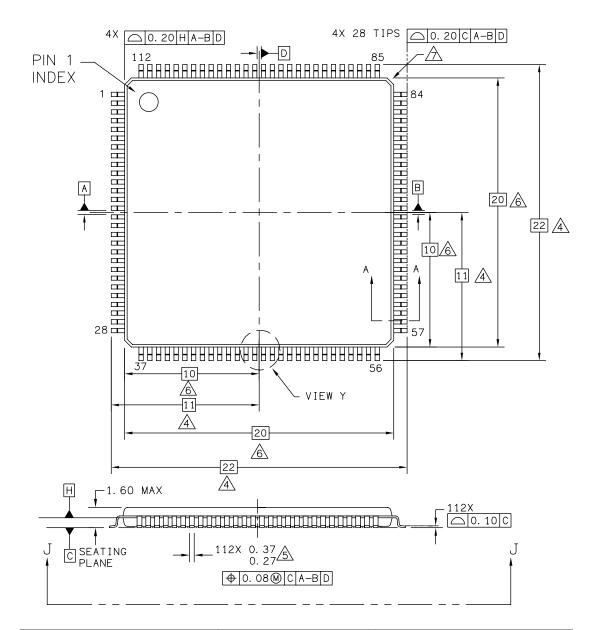

# B.1 112-pin LQFP Mechanical Dimensions

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | HANICAL OUTLINE PRINT VE |                | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------------------|----------------|-------------|

| TITLE: 112LD LQFP                                       |           | DOCUMENT NO              | : 98ASS23330W  | REV: F      |

| 20 X 20 X 1.4                                           |           | CASE NUMBER              | 2: 987–03      | 15 DEC 2006 |

| 0.65 PITCH                                              |           | STANDARD: JE             | DEC MS-026 BFA |             |

Figure B-1. 112-pin LQFP (case no. 987) - page 1

Package Information

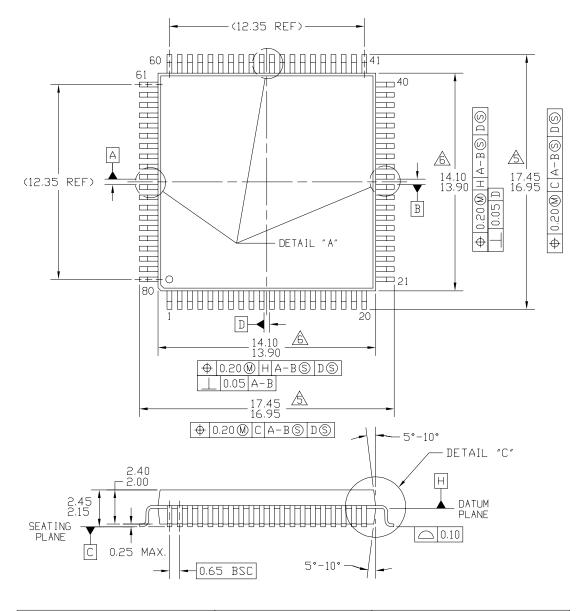

# B.2 80-Pin QFP Mechanical Dimensions

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                     | MECHANICAL OUTLINE |                      | PRINT VERSION NOT TO SCALE |             |

|-----------------------------------------------------------------------------|--------------------|----------------------|----------------------------|-------------|

| TITLE:<br>QUAD FLAT PACKAGE, 80 LEAD,<br>14 X 14 X 2.2 PKG, 0.65 LEAD PITCH |                    | DOCUMENT NE          | ]: 98ASB42846B             | RE∨∶C       |

|                                                                             |                    | CASE NUMBER: 841B-02 |                            | 20 MAY 2005 |

| 14 A 14 A 2.2 FKG, 0.03 L                                                   | ead fiich          | STANDARD: NON-JEDEC  |                            |             |

Figure B-4. 80-pin QFP (case no. 841B) - page 1