Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                   |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, SCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 59                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                             |

| Data Converters            | A/D 8x12b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 80-QFP                                                                   |

| Supplier Device Package    | 80-QFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs128j1vaar |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

To provide the most up-to-date information, the document revision on the World Wide Web is the most current. A printed copy may be an earlier revision. To verify you have the latest information available,

refer to freescale.com.

This document contains information for the complete S12XS Family and thus includes a set of separate flash (FTMR) module sections to cover the whole family. A full list of family members and options is included in the appendices.

This document contains information for all constituent modules, with the exception of the CPU. For CPU information please refer to CPU12XV1 in the CPU12/CPU12X Reference Manual.

### **Revision History**

| Date              | Revision<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November,<br>2010 | 1.11              | Updated Chapter 3 Memory Mapping Control (S12XMMCV4)<br>Updated Chapter 11 Freescale's Scalable Controller Area Network<br>(S12MSCANV3)<br>Updated Chapter 14 Serial Communication Interface (S12SCIV5)<br>Updated footnotes on table 1-2<br>Updated note in Appendix F Ordering Information                                                                                  |

| Jul, 2011         | 1.12              | Corrected API accuracy in feature list<br>Corrected name of pin #27 in 80QFP pinout (PE5->PE4)<br>Updated Chapter 2 Port Integration Module (S12XSPIMV1)<br>Updated Chapter 11 Freescale's Scalable Controller Area Network<br>(S12MSCANV3)                                                                                                                                   |

| Aug, 2012         | 1.13              | Updated Chapter 4 Interrupt (S12XINTV2)<br>Updated Chapter 8 S12XE Clocks and Reset Generator (S12XECRGV1)<br>Updated V <sub>DDF</sub> max. voltage in Appendix A Electrical Characteristics<br>Minor editorial corrections in:<br>Chapter 2 Port Integration Module (S12XSPIMV1)<br>Chapter 5 Background Debug Module (S12XBDMV2)<br>Chapter 6 S12X Debug (S12XDBGV3) Module |

Device Overview S12XS Family

## 1.2.3.8 PE7 / ECLKX2 / XCLKS — Port E I/O Pin 7

PE7 is a general-purpose input or output pin. ECLKX2 is a clock output of twice the internal bus frequency. The  $\overline{\text{XCLKS}}$  is an input signal which controls whether a crystal in combination with the internal loop controlled Pierce oscillator is used or whether full swing Pierce oscillator/external clock circuitry is used (refer to **Section 1.10 Oscillator Configuration**). An internal pull-up is enabled during reset.

## 1.2.3.9 PE[6:5] — Port E I/O Pin 6-5

PE[6:5] are a general-purpose input or output pins.

### 1.2.3.10 PE4 / ECLK — Port E I/O Pin 4

PE4 is a general-purpose input or output pin. It can be configured to output the internal bus clock ECLK. ECLK can be used as a timing reference. The ECLK output has a programmable prescaler.

## 1.2.3.11 PE[3:2] — Port E I/O Pin 3

PE[3:2] are a general-purpose input or output pins.

## 1.2.3.12 PE1 / IRQ — Port E Input Pin 1

PE1 is a general-purpose input pin and the maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from stop or wait mode.

### 1.2.3.13 PE0 / XIRQ — Port E Input Pin 0

PE0 is a general-purpose input pin and the non-maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from stop or wait mode. The XIRQ interrupt is level sensitive and active low. As XIRQ is level sensitive, while this pin is low the MCU will not enter STOP mode.

## 1.2.3.14 PH[7:0] / KWH[7:0] — Port H I/O Pins

PH[7:0] are a general-purpose input or output pins. They can be configured as keypad wakeup inputs.

## 1.2.3.15 PJ[7:6] / KWJ[7:6] — PORT J I/O Pins 7-6

PJ[7:6] are a general-purpose input or output pins. They can be configured as keypad wakeup inputs.

## 1.2.3.16 PJ[1:0] / KWJ[1:0] — PORT J I/O Pins 1-0

PJ[1:0] are a general-purpose input or output pins. They can be configured as keypad wakeup inputs.

### 1.2.3.17 PK[7,5:0] — Port K I/O Pins 7 and 5-0

PK[7,5:0] are a general-purpose input or output pins.

S12XS Family Reference Manual, Rev. 1.13

| Register<br>Name |                             | Bit 7  | 6      | 5     | 4      | 3     | 2     | 1     | Bit 0 |  |

|------------------|-----------------------------|--------|--------|-------|--------|-------|-------|-------|-------|--|

| 0x0256<br>WOMM   | R<br>W                      | WOMM7  | WOMM6  | WOMM5 | WOMM4  | WOMM3 | WOMM2 | WOMM1 | WOMM0 |  |

| 0x0257<br>MODRR  | R<br>W                      | MODRR7 | MODRR6 | 0     | MODRR4 | 0     | 0     | 0     | 0     |  |

| 0x0258<br>PTP    | R<br>W                      | PTP7   | PTP6   | PTP5  | PTP4   | PTP3  | PTP2  | PTP1  | PTP0  |  |

| 0x0259<br>PTIP   | R<br>W                      | PTIP7  | PTIP6  | PTIP5 | PTIP4  | PTIP3 | PTIP2 | PTIP1 | PTIP0 |  |

| 0x025A<br>DDRP   | R<br>W                      | DDRP7  | DDRP6  | DDRP5 | DDRP4  | DDRP3 | DDRP2 | DDRP1 | DDRP0 |  |

| 0x025B<br>RDRP   | R<br>W                      | RDRP7  | RDRP6  | RDRP5 | RDRP4  | RDRP3 | RDRP2 | RDRP1 | RDRP0 |  |

| 0x025C<br>PERP   | R<br>W                      | PERP7  | PERP6  | PERP5 | PERP4  | PERP3 | PERP2 | PERP1 | PERP0 |  |

| 0x025D<br>PPSP   | R<br>W                      | PPSP7  | PPSP6  | PPSP5 | PPSP4  | PPSP3 | PPSP2 | PPSP1 | PPSP0 |  |

| 0x025E<br>PIEP   | R<br>W                      | PIEP7  | PIEP6  | PIEP5 | PIEP4  | PIEP3 | PIEP2 | PIEP1 | PIEP0 |  |

| 0x025F<br>PIFP   | R<br>W                      | PIFP7  | PIFP6  | PIFP5 | PIFP4  | PIFP3 | PIFP2 | PIFP1 | PIFP0 |  |

| 0x0260<br>PTH    | R<br>W                      | PTH7   | PTH6   | PTH5  | PTH4   | PTH3  | PTH2  | PTH1  | PTH0  |  |

| 0x0261<br>PTIH   | R<br>W                      | PTIH7  | PTIH6  | PTIH5 | PTIH4  | PTIH3 | PTIH2 | PTIH1 | PTIH0 |  |

| 0x0262<br>DDRH   | R<br>W                      | DDRH7  | DDRH6  | DDRH5 | DDRH4  | DDRH3 | DDRH2 | DDRH1 | DDRH0 |  |

| 0x0263<br>RDRH   | R<br>W                      | RDRH7  | RDRH6  | RDRH5 | RDRH4  | RDRH3 | RDRH2 | RDRH1 | RDRH0 |  |

| 0x0264<br>PERH   | R<br>W                      | PERH7  | PERH6  | PERH5 | PERH4  | PERH3 | PERH2 | PERH1 | PERH0 |  |

|                  | = Unimplemented or Reserved |        |        |       |        |       |       |       |       |  |

Port Integration Module (S12XSPIMV1)

<sup>1</sup> Read: Always reads 0x00 Write: Unimplemented

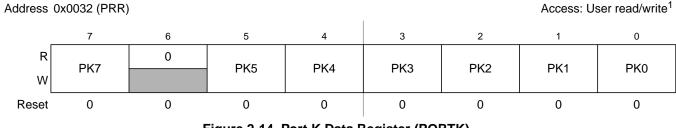

# 2.3.16 Port K Data Register (PORTK)

Figure 2-14. Port K Data Register (PORTK)

Read: Anytime, the data source depends on the data direction value Write: Anytime

#### Table 2-14. PORTK Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7,5-0<br>PK | <b>Port K general purpose input/output data</b> —Data Register<br>The associated pin can be used as general purpose I/O. In general purpose output mode the register bit value is<br>driven to the pin.<br>If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered<br>pin input state is read. |

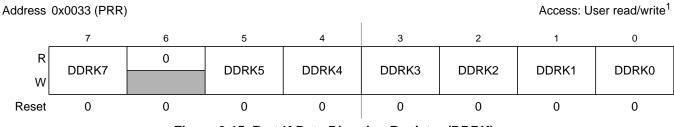

# 2.3.17 Port K Data Direction Register (DDRK)

Figure 2-15. Port K Data Direction Register (DDRK)

Read: Anytime, the data source depends on the data direction value Write: Anytime

Read: Anytime

Write: Anytime

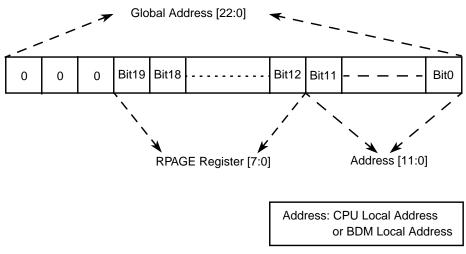

These eight index bits are used to page 4KB blocks into the RAM page window located in the local (CPU or BDM) memory map from address 0x1000 to address 0x1FFF (see Figure 3-14). This supports accessing up to 1022KB of RAM (in the Global map) within the 64KB Local map. The RAM page index register is effectively used to construct paged RAM addresses in the Local map format.

Figure 3-14. RPAGE Address Mapping

#### NOTE

Because RAM page 0 has the same global address as the register space, it is possible to write to registers through the RAM space when RPAGE = 0x00.

#### Table 3-8. RPAGE Field Descriptions

| Field | Description                                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>RAM Page Index Bits 7–0</b> — These page index bits are used to select which of the 256 RAM array pages is to be accessed in the RAM Page Window. |

The reset value of 0xFD ensures that there is a linear RAM space available between addresses 0x1000 and 0x3FFF out of reset.

The fixed 4K page from 0x2000–0x2FFF of RAM is equivalent to page 254 (page number 0xFE).

The fixed 4K page from 0x3000–0x3FFF of RAM is equivalent to page 255 (page number 0xFF).

#### NOTE

The page 0xFD (reset value) contains unimplemented area in the range not occupied by RAM if RAMSIZE is less than 12KB (Refer to Section 3.4.2.3, "Implemented Memory Map).

In single-chip modes accesses by the CPU (except for firmware commands) to any of the unimplemented areas (see Figure 3-19) will result in an illegal access reset (system reset) in case of no MPU error. BDM accesses to the unimplemented areas are allowed but the data will be undefined.No misaligned word access from the BDM module will occur; these accesses are blocked in the BDM module (Refer to BDM Block Guide).

Misaligned word access to the last location of RAM is performed but the data will be undefined.

Misaligned word access to the last location of any global page (64KB) by any global instruction, is performed by accessing the last byte of the page and the first byte of the same page, considering the above mentioned misaligned access cases.

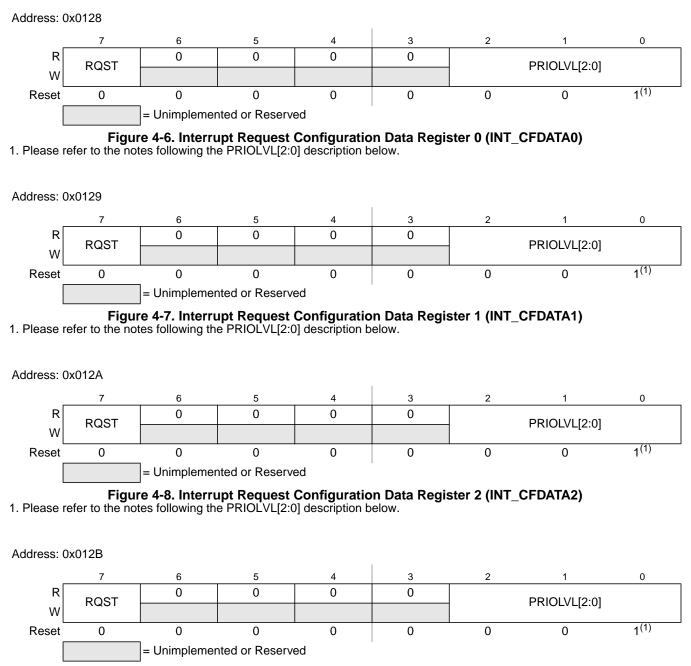

Figure 4-9. Interrupt Request Configuration Data Register 3 (INT\_CFDATA3) 1. Please refer to the notes following the PRIOLVL[2:0] description below.

| fosc | REFDIV[5:0] | f <sub>REF</sub> | REFFRQ[1:0] | SYNDIV[5:0] | f <sub>VCO</sub> | VCOFRQ[1:0] | POSTDIV[4:0] | f <sub>PLL</sub> | f <sub>BUS</sub> |

|------|-------------|------------------|-------------|-------------|------------------|-------------|--------------|------------------|------------------|

| 4MHz | \$01        | 2MHz             | 01          | \$18        | 100MHz           | 11          | \$00         | 100MHz           | 50 MHz           |

| 8MHz | \$03        | 2MHz             | 01          | \$18        | 100MHz           | 11          | \$00         | 100MHz           | 50 MHz           |

| 4MHz | \$00        | 4MHz             | 01          | \$09        | 80MHz            | 01          | \$00         | 80MHz            | 40MHz            |

| 8MHz | \$00        | 8MHz             | 10          | \$04        | 80MHz            | 01          | \$00         | 80MHz            | 40MHz            |

| 4MHz | \$00        | 4MHz             | 01          | \$03        | 32MHz            | 00          | \$01         | 16MHz            | 8MHz             |

| 4MHz | \$01        | 2MHz             | 01          | \$18        | 100MHz           | 11          | \$01         | 50MHz            | 25MHz            |

| <b>Table 8-14</b> | . Examples of IPLL | Divider Settings <sup>(1)</sup> |

|-------------------|--------------------|---------------------------------|

|-------------------|--------------------|---------------------------------|

f<sub>PLL</sub> and f<sub>BUS</sub> values in this table may exceed maximum allowed frequencies for some devices. Refer to device information for maximum values.

#### 8.4.1.1.1 **IPLL** Operation

The oscillator output clock signal (OSCCLK) is fed through the reference programmable divider and is divided in a range of 1 to 64 (REFDIV+1) to output the REFCLK. The VCO output clock, (VCOCLK) is fed back through the programmable loop divider and is divided in a range of 2 to 128 in increments of [2 x (SYNDIV +1)] to output the FBCLK. The VCOCLK is fed to the final programmable divider and is divided in a range of 1,2,4,6,8,... to 62 (2\*POSTDIV) to output the PLLCLK. See Figure 8-15.

The phase detector then compares the FBCLK, with the REFCLK. Correction pulses are generated based on the phase difference between the two signals. The loop filter then slightly alters the DC voltage on the internal filter capacitor, based on the width and direction of the correction pulse.

The user must select the range of the REFCLK frequency and the range of the VCOCLK frequency to ensure that the correct IPLL loop bandwidth is set.

The lock detector compares the frequencies of the FBCLK, and the REFCLK. Therefore, the speed of the lock detector is directly proportional to the reference clock frequency. The circuit determines the lock condition based on this comparison.

If IPLL LOCK interrupt requests are enabled, the software can wait for an interrupt request and then check the LOCK bit. If interrupt requests are disabled, software can poll the LOCK bit continuously (during IPLL start-up, usually) or at periodic intervals. In either case, only when the LOCK bit is set, the PLLCLK can be selected as the source for the system and core clocks. If the IPLL is selected as the source for the system and core clocks and the LOCK bit is clear, the IPLL has suffered a severe noise hit and the software must take appropriate action, depending on the application.

- The LOCK bit is a read-only indicator of the locked state of the IPLL.

- The LOCK bit is set when the VCO frequency is within a certain tolerance,  $\Delta_{Lock}$ , and is cleared when the VCO frequency is out of a certain tolerance,  $\Delta_{unl}$ .

- Interrupt requests can occur if enabled (LOCKIE = 1) when the lock condition changes, toggling the LOCK bit.

Pierce Oscillator (S12XOSCLCPV2)

# 9.3 Memory Map and Register Definition

The CRG contains the registers and associated bits for controlling and monitoring the oscillator module.

# 9.4 Functional Description

The XOSC module has control circuitry to maintain the crystal oscillator circuit voltage level to an optimal level which is determined by the amount of hysteresis being used and the maximum oscillation range.

The oscillator block has two external pins, EXTAL and XTAL. The oscillator input pin, EXTAL, is intended to be connected to either a crystal or an external clock source. The XTAL pin is an output signal that provides crystal circuit feedback.

A buffered EXTAL signal becomes the internal clock. To improve noise immunity, the oscillator is powered by the VDDPLL and VSSPLL power supply pins.

## 9.4.1 Gain Control

In LCP mode a closed loop control system will be utilized whereby the amplifier is modulated to keep the output waveform sinusoidal and to limit the oscillation amplitude. The output peak to peak voltage will be kept above twice the maximum hysteresis level of the input buffer. Electrical specification details are provided in the Electrical Characteristics appendix.

## 9.4.2 Clock Monitor

The clock monitor circuit is based on an internal RC time delay so that it can operate without any MCU clocks. If no OSCCLK edges are detected within this RC time delay, the clock monitor indicates failure which asserts self-clock mode or generates a system reset depending on the state of SCME bit. If the clock monitor is disabled or the presence of clocks is detected no failure is indicated. The clock monitor function is enabled/disabled by the CME control bit, described in the CRG block description chapter.

## 9.4.3 Wait Mode Operation

During wait mode, XOSC is not impacted.

## 9.4.4 Stop Mode Operation

XOSC is placed in a static state when the part is in stop mode except when pseudo-stop mode is enabled. During pseudo-stop mode, XOSC is not impacted.

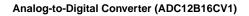

## 10.3.2.9 ATD Status Register 2 (ATDSTAT2)

This read-only register contains the Conversion Complete Flags CCF[15:0].

#### Read: Anytime

Write: Anytime, no effect

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>CCF[15:0] | <b>Conversion Complete Flag</b> <i>n</i> ( <i>n</i> = 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) — A conversion complete flag is set at the end of each conversion in a sequence. The flags are associated with the conversion position in a sequence (and also the result register number). Therefore in non-fifo mode, CCF[8] is set when the ninth conversion in a sequence is complete and the result is available in result register ATDDR8; CCF[9] is set when the tenth conversion in a sequence is complete and the result is available in ATDDR9, and so forth.                                                                                                                                                                              |

|                   | If automatic compare of conversion results is enabled (CMPE[ <i>n</i> ]=1 in ATDCMPE), the conversion complete flag<br>is only set if comparison with ATDDR <i>n</i> is true and if ACMPIE=1 a compare interrupt will be requested. In this<br>case, as the ATDDR <i>n</i> result register is used to hold the compare value, the result will not be stored there at the<br>end of the conversion but is lost.<br>A flag CCF[ <i>n</i> ] is cleared when one of the following occurs:<br>A) Write to ATDCTL5 (a new conversion sequence is started)<br>B) If AFFC=0, write "1" to CCF[ <i>n</i> ]<br>C) If AFFC=1 and CMPE[ <i>n</i> ]=0, read of result register ATDDR <i>n</i><br>D) If AFFC=1 and CMPE[ <i>n</i> ]=1, write to result register ATDDR <i>n</i> |

|                   | <ul> <li>In case of a concurrent set and clear on CCF[<i>n</i>]: The clearing by method A) will overwrite the set. The clearing by methods B) or C) or D) will be overwritten by the set.</li> <li>0 Conversion number <i>n</i> not completed or successfully compared</li> <li>1 If (CMPE[<i>n</i>]=0): Conversion number <i>n</i> has completed. Result is ready in ATDDR<i>n</i>.</li> <li>If (CMPE[<i>n</i>]=1): Compare for conversion result number <i>n</i> with compare value in ATDDR<i>n</i>, using compare operator CMPGT[<i>n</i>] is true. (No result available in ATDDR<i>n</i>)</li> </ul>                                                                                                                                                        |

# 11.4 Functional Description

## 11.4.1 General

This section provides a complete functional description of the MSCAN.

## 11.4.2 Message Storage

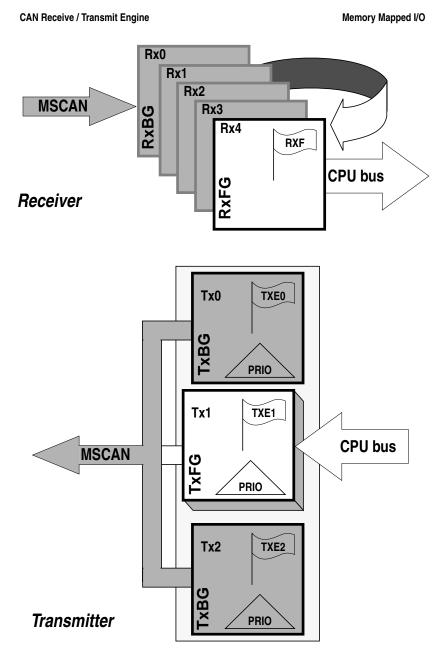

Figure 11-39. User Model for Message Buffer Organization

S12XS Family Reference Manual Rev. 1.13

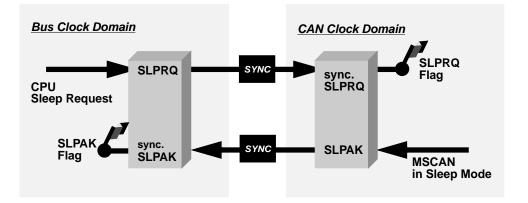

## 11.4.5.5 MSCAN Sleep Mode

The CPU can request the MSCAN to enter this low power mode by asserting the SLPRQ bit in the CANCTL0 register. The time when the MSCAN enters sleep mode depends on a fixed synchronization delay and its current activity:

- If there are one or more message buffers scheduled for transmission (TXEx = 0), the MSCAN will continue to transmit until all transmit message buffers are empty (TXEx = 1, transmitted successfully or aborted) and then goes into sleep mode.

- If the MSCAN is receiving, it continues to receive and goes into sleep mode as soon as the CAN bus next becomes idle.

- If the MSCAN is neither transmitting nor receiving, it immediately goes into sleep mode.

Figure 11-46. Sleep Request / Acknowledge Cycle

#### NOTE

The application software must avoid setting up a transmission (by clearing one or more TXEx flag(s)) and immediately request sleep mode (by setting SLPRQ). Whether the MSCAN starts transmitting or goes into sleep mode directly depends on the exact sequence of operations.

If sleep mode is active, the SLPRQ and SLPAK bits are set (Figure 11-46). The application software must use SLPAK as a handshake indication for the request (SLPRQ) to go into sleep mode.

When in sleep mode (SLPRQ = 1 and SLPAK = 1), the MSCAN stops its internal clocks. However, clocks that allow register accesses from the CPU side continue to run.

If the MSCAN is in bus-off state, it stops counting the 128 occurrences of 11 consecutive recessive bits due to the stopped clocks. TXCAN remains in a recessive state. If RXF = 1, the message can be read and RXF can be cleared. Shifting a new message into the foreground buffer of the receiver FIFO (RxFG) does not take place while in sleep mode.

It is possible to access the transmit buffers and to clear the associated TXE flags. No message abort takes place while in sleep mode.

S12XS Family Reference Manual, Rev. 1.13

#### Pulse-Width Modulator (S12PWM8B8CV1)

Either left aligned or center aligned output mode can be used in concatenated mode and is controlled by the low order CAEx bit. The high order CAEx bit has no effect.

Table 13-11 is used to summarize which channels are used to set the various control bits when in 16-bit mode.

| CONxx | PWMEx | PPOLx | PCLKx | CAEx | PWMx<br>Output |

|-------|-------|-------|-------|------|----------------|

| CON67 | PWME7 | PPOL7 | PCLK7 | CAE7 | PWM7           |

| CON45 | PWME5 | PPOL5 | PCLK5 | CAE5 | PWM5           |

| CON23 | PWME3 | PPOL3 | PCLK3 | CAE3 | PWM3           |

| CON01 | PWME1 | PPOL1 | PCLK1 | CAE1 | PWM1           |

Table 13-11. 16-bit Concatenation Mode Summary

#### 13.4.2.8 PWM Boundary Cases

Table 13-12 summarizes the boundary conditions for the PWM regardless of the output mode (left aligned or center aligned) and 8-bit (normal) or 16-bit (concatenation).

| PWMDTYx                     | PWMPERx                                    | PPOLx | PWMx Output |  |

|-----------------------------|--------------------------------------------|-------|-------------|--|

| \$00<br>(indicates no duty) | >\$00                                      | 1     | Always low  |  |

| \$00<br>(indicates no duty) | >\$00                                      | 0     | Always high |  |

| XX                          | \$00 <sup>1</sup><br>(indicates no period) | 1     | Always high |  |

| XX                          | \$00 <sup>1</sup><br>(indicates no period) | 0     | Always low  |  |

| >= PWMPERx                  | XX                                         | 1     | Always high |  |

| >= PWMPERx                  | XX                                         | 0     | Always low  |  |

Table 13-12. PWM Boundary Cases

$\frac{1}{1}$  Counter = \$00 and does not count.

## 13.5 Resets

The reset state of each individual bit is listed within the Section 13.3.2, "Register Descriptions" which details the registers and their bit-fields. All special functions or modes which are initialized during or just following reset are described within this section.

- The 8-bit up/down counter is configured as an up counter out of reset.

- All the channels are disabled and all the counters do not count.

NP

Timer Module (TIM16B8CV2)

| Register<br>Name          |        | Bit 7   | 6       | 5       | 4       | 3       | 2       | 1      | Bit 0  |

|---------------------------|--------|---------|---------|---------|---------|---------|---------|--------|--------|

| 0x0006<br>TSCR1           | R<br>W | TEN     | TSWAI   | TSFRZ   | TFFCA   | PRNT    | 0       | 0      | 0      |

| 0x0007<br>TTOV            | R<br>W | TOV7    | TOV6    | TOV5    | TOV4    | TOV3    | TOV2    | TOV1   | TOV0   |

| 0x0008<br>TCTL1           | R<br>W | OM7     | OL7     | OM6     | OL6     | OM5     | OL5     | OM4    | OL4    |

| 0x0009<br>TCTL2           | R<br>W | OM3     | OL3     | OM2     | OL2     | OM1     | OL1     | OM0    | OL0    |

| 0x000A<br>TCTL3           | R<br>W | EDG7B   | EDG7A   | EDG6B   | EDG6A   | EDG5B   | EDG5A   | EDG4B  | EDG4A  |

| 0x000B<br>TCTL4           | R<br>W | EDG3B   | EDG3A   | EDG2B   | EDG2A   | EDG1B   | EDG1A   | EDG0B  | EDG0A  |

| 0x000C<br>TIE             | R<br>W | C7I     | C6I     | C5I     | C4I     | C3I     | C2I     | C1I    | COI    |

| 0x000D<br>TSCR2           | R<br>W | ΤΟΙ     | 0       | 0       | 0       | TCRE    | PR2     | PR1    | PR0    |

| 0x000E<br>TFLG1           | R<br>W | C7F     | C6F     | C5F     | C4F     | C3F     | C2F     | C1F    | C0F    |

| 0x000F<br>TFLG2           | R<br>W | TOF     | 0       | 0       | 0       | 0       | 0       | 0      | 0      |

| 0x0010–0x001F             | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| TCxH–TCxL                 | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x0020<br>PACTL           | R<br>W | 0       | PAEN    | PAMOD   | PEDGE   | CLK1    | CLK0    | PAOVI  | PAI    |

| 0x0021<br>PAFLG           | R<br>W | 0       | 0       | 0       | 0       | 0       | 0       | PAOVF  | PAIF   |

| 0x0022<br>PACNTH          | R<br>W | PACNT15 | PACNT14 | PACNT13 | PACNT12 | PACNT11 | PACNT10 | PACNT9 | PACNT8 |

| 0x0023<br>PACNTL          | R<br>W | PACNT7  | PACNT6  | PACNT5  | PACNT4  | PACNT3  | PACNT2  | PACNT1 | PACNT0 |

| 0x0024–0x002B<br>Reserved | R<br>W |         |         |         |         |         |         |        |        |

= Unimplemented or Reserved

Figure 16-5. TIM16B8CV2 Register Summary (Sheet 2 of 3)

S12XS Family Reference Manual Rev. 1.13

#### 256 KByte Flash Module (S12XFTMR256K1V1)

| CCOBIX[2:0] | FCCOB Parameters                 |

|-------------|----------------------------------|

| 101         | Word 3 program value, if desired |

Upon clearing CCIF to launch the Program D-Flash command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program D-Flash command launch determines how many words will be programmed in the D-Flash block. The CCIF flag is set when the operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] < 010 at command launch                                          |  |  |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |  |  |

|          |           | Set if command not available in current mode (see Table 18-28)                      |  |  |

|          |           | Set if an invalid global address [22:0] is supplied                                 |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |

| -        |           | Set if the requested group of words breaches the end of the D-Flash block           |  |  |

|          | FPVIOL    | Set if the selected area of the D-Flash memory is protected                         |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTATO   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

#### Table 18-62. Program D-Flash Command Error Handling

### 18.4.2.16 Erase D-Flash Sector Command

The Erase D-Flash Sector operation will erase all addresses in a sector of the D-Flash block.

Table 18-63. Erase D-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                |                                                     |  |

|-------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| 000         | 0x12                                                                                                            | Global address [22:16] to identify<br>D-Flash block |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 18.1.2.2 for D-Flash sector size. |                                                     |  |

Upon clearing CCIF to launch the Erase D-Flash Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase D-Flash Sector operation has completed.

#### 128 KByte Flash Module (S12XFTMR128K1V1)

| С | COBIX[2:0] | FCCOB Parameters                 |

|---|------------|----------------------------------|

|   | 101        | Word 3 program value, if desired |

Upon clearing CCIF to launch the Program D-Flash command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program D-Flash command launch determines how many words will be programmed in the D-Flash block. The CCIF flag is set when the operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] < 010 at command launch                                          |  |  |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |  |  |

|          |           | Set if command not available in current mode (see Table 19-28)                      |  |  |

|          |           | Set if an invalid global address [22:0] is supplied                                 |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |

| -        |           | Set if the requested group of words breaches the end of the D-Flash block           |  |  |

|          | FPVIOL    | Set if the selected area of the D-Flash memory is protected                         |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTATO   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

#### Table 19-62. Program D-Flash Command Error Handling

### 19.4.2.16 Erase D-Flash Sector Command

The Erase D-Flash Sector operation will erase all addresses in a sector of the D-Flash block.

Table 19-63. Erase D-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                |                                                     |  |

|-------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| 000         | 0x12                                                                                                            | Global address [22:16] to identify<br>D-Flash block |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 19.1.2.2 for D-Flash sector size. |                                                     |  |

Upon clearing CCIF to launch the Erase D-Flash Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase D-Flash Sector operation has completed.

# Appendix A Electrical Characteristics

# A.1 General

#### NOTE

The electrical characteristics given in this section should be used as a guide only. Values cannot be guaranteed by Freescale and are subject to change without notice. Data are currently based on characterization data of 9S12XS128 material only unless marked differently.

This supplement contains the most accurate electrical information for the S12XS family microcontroller available at the time of publication.

This introduction is intended to give an overview on several common topics like power supply, current injection etc.

## A.1.1 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate.

#### NOTE

This classification is shown in the column labeled "C" in the parameter tables where appropriate.

- P: Those parameters are guaranteed during production testing on each individual device.

- C: Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.

- T: Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category.

- D: Those parameters are derived mainly from simulations.

## A.1.2 Power Supply

The S12XS family utilizes several pins to supply power to the I/O ports, A/D converter, oscillator, and PLL as well as the digital core.

The VDDA, VSSA pin pairs supply the A/D converter and parts of the internal voltage regulator.

S12XS Family Reference Manual, Rev. 1.13

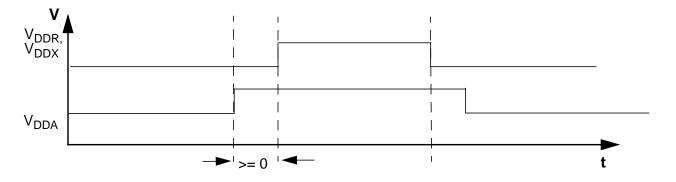

Figure A-3. S12XS family Power Sequencing

During power sequencing  $V_{DDA}$  can be powered up before  $V_{DDR}$ ,  $V_{DDX}$ .  $V_{DDR}$  and  $V_{DDX}$  must be powered up together adhering to the operating conditions differential.  $V_{RH}$  power up must follow  $V_{DDA}$  to avoid current injection.

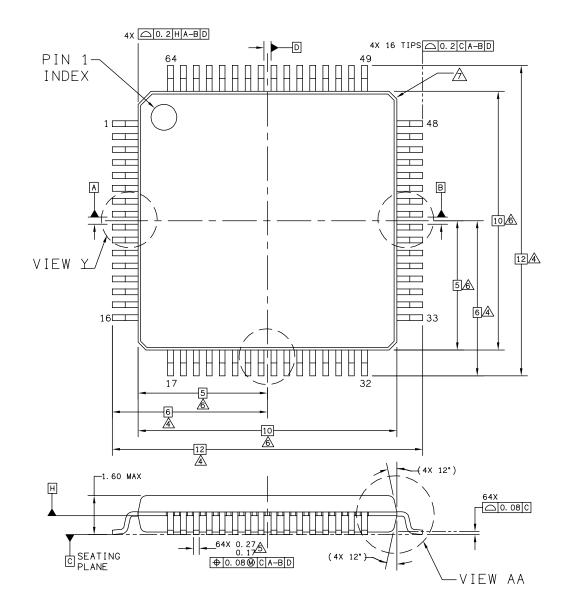

# B.3 64-Pin LQFP Mechanical Dimensions

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                       |  |              | PRINT VERSION NO | DT TO SCALE |

|-------------------------------------------------------------------------------|--|--------------|------------------|-------------|

| <sup>title:</sup> 64LD LQFP,<br>10 X 10 X 1.4 PKG,<br>0.5 PITCH, CASE OUTLINE |  | DOCUMENT NO  | : 98ASS23234W    | REV: E      |

|                                                                               |  | CASE NUMBER  | 2: 840F-02       | 11 AUG 2006 |

|                                                                               |  | STANDARD: JE | DEC MS-026 BCD   |             |

S12XS Family Reference Manual, Rev. 1.13

#### How to Reach Us:

Home Page: www.freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 1-800-521-6274 or 480-768-2130

#### Europe, Middle East, and Africa:

+44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French)

#### Japan:

Freescale Semiconductor Japan Ltd. Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-0047, Japan 0120-191014 or +81-3-3440-3569

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong 852-26668334

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. Java and all other Java-based marks are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries.

© Freescale Semiconductor, Inc. 2007. All rights reserved. MC9S12XS256RMV1

Rev. 1.13 08/2012