### NXP USA Inc. - S9S12XS128J1VAER Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                   |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, SCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 59                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                             |

| Data Converters            | A/D 8x12b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs128j1vaer |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Device Overview S12XS Family**

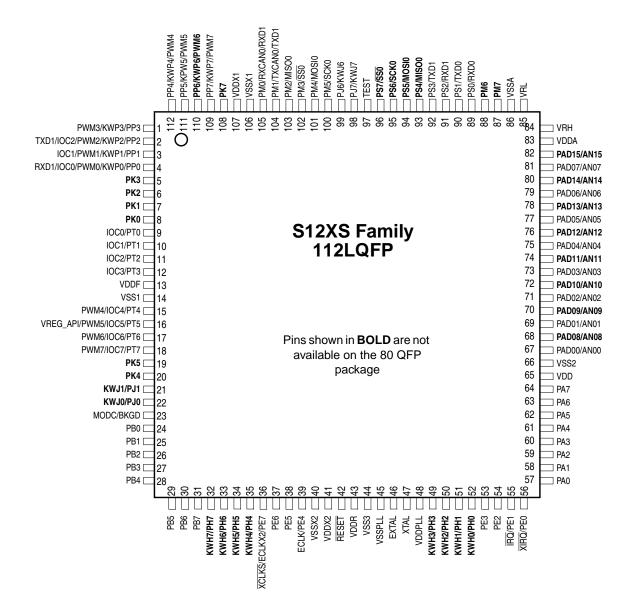

Figure 1-3. S12XS Family Pin Assignments 112-pin LQFP Package

S12XS Family Reference Manual, Rev. 1.13

**Device Overview S12XS Family**

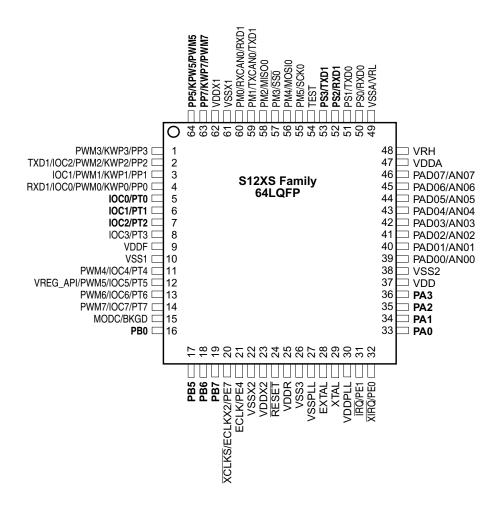

Figure 1-5. S12XS Family Pin Assignments 64-pin LQFP Package

| Vector Address <sup>1</sup>                    | Interrupt Source                           | CCR<br>Mask | Local Enable               | STOP<br>Wake up | WAIT<br>Wake up |

|------------------------------------------------|--------------------------------------------|-------------|----------------------------|-----------------|-----------------|

| Vector base + \$BA                             | FLASH Fault Detect                         | I bit       | FCNFG2 (SFDIE, DFDIE)      | No              | No              |

| Vector base + \$B8                             | FLASH                                      | l bit       | FCNFG (CCIE)               | No              | Yes             |

| Vector base + \$B6                             | CAN0 wake-up                               | I bit       | CAN0RIER (WUPIE)           | Yes             | Yes             |

| Vector base + \$B4                             | CAN0 errors                                | l bit       | CANORIER (CSCIE,<br>OVRIE) | No              | Yes             |

| Vector base + \$B2                             | CAN0 receive                               | I bit       | CANORIER (RXFIE)           | No              | Yes             |

| Vector base + \$B0                             | CAN0 transmit                              | l bit       | CAN0TIER (TXEIE[2:0])      | No              | Yes             |

| Vector base + \$AE<br>to<br>Vector base + \$90 |                                            | Rese        | rved                       |                 |                 |

| Vector base + \$8E                             | Port P Interrupt                           | l bit       | PIEP (PIEP7-PIEP0)         | Yes             | Yes             |

| Vector base+ \$8C                              | PWM emergency shutdown                     | l bit       | PWMSDN (PWMIE)             | No              | Yes             |

| Vector base + \$8A<br>to<br>Vector base + \$82 | Reserved                                   |             |                            |                 |                 |

| Vector base + \$80                             | Low-voltage interrupt (LVI)                | I bit       | VREGCTRL (LVIE)            | No              | Yes             |

| Vector base + \$7E                             | \$7E Autonomous periodical interrupt (API) |             | VREGAPICTRL (APIE)         | Yes             | Yes             |

| Vector base + \$7C                             | High Temperature Interrupt (HTI)           | I bit       | VREGHTCL (HTIE)            | No              | Yes             |

| Vector base + \$7A                             | Periodic interrupt timer channel 0         | I bit       | PITINTE (PINTE0)           | No              | Yes             |

| Vector base + \$78                             | Periodic interrupt timer channel 1         | l bit       | PITINTE (PINTE1)           | No              | Yes             |

| Vector base + \$76                             | Periodic interrupt timer channel 2         | I bit       | PITINTE (PINTE2)           | No              | Yes             |

| Vector base + \$74                             | Periodic interrupt timer channel 3         | l bit       | PITINTE (PINTE3)           | No              | Yes             |

| Vector base + \$72<br>to<br>Vector base + \$40 | Reserved                                   |             |                            |                 |                 |

| Vector base + \$3E                             | ATD0 Compare Interrupt                     | l bit       | ATD0CTL2 (ACMPIE)          | Yes             | Yes             |

| Vector base + \$3C<br>to<br>Vector base + \$14 |                                            | Rese        | rved                       |                 |                 |

| Vector base + \$12                             | System Call Interrupt (SYS)                | -           | None                       | _               |                 |

| Vector base + \$10                             | Spurious interrupt                         | _           | None                       | —               | —               |

### Table 1-10. Interrupt Vector Locations (Sheet 2 of 2)

1 16 bits vector address based

# 1.6.3 Effects of Reset

When a reset occurs, MCU registers and control bits are initialized. Refer to the respective block sections for register reset states.

On each reset, the Flash module executes a reset sequence to load Flash configuration registers.

S12XS Family Reference Manual, Rev. 1.13

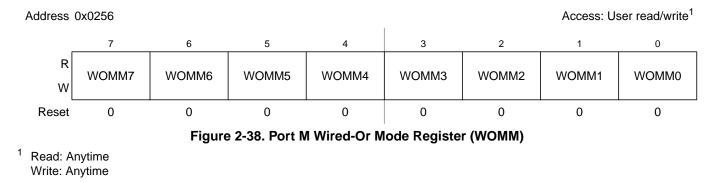

# 2.3.40 Port M Wired-Or Mode Register (WOMM)

### Table 2-36. WOMM Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>WOMM | <b>Port M wired-or mode</b> —Enable open-drain functionality on output pin<br>This bit configures an output pin as wired-or (open-drain) or push-pull independent of the function used on the pins.<br>In wired-or mode a logic "0" is driven active low while a logic "1" remains undriven. This allows a multipoint<br>connection of several serial modules. The bit has no influence on pins used as input. |

|             | <ol> <li>Output buffer operates as open-drain output.</li> <li>Output buffer operates as push-pull output.</li> </ol>                                                                                                                                                                                                                                                                                          |

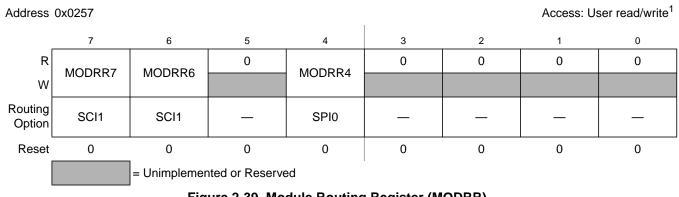

# 2.3.41 Module Routing Register (MODRR)

Figure 2-39. Module Routing Register (MODRR)

<sup>1</sup> Read: Anytime Write: Anytime

This register configures the re-routing of SCI1 and SPI0 on alternative ports.

| MOD | RRx | Related Pins |     |  |  |

|-----|-----|--------------|-----|--|--|

| 7   | 6   | TXD          | RXD |  |  |

### Table 2-37. SCI1 Routing

Port Integration Module (S12XSPIMV1)

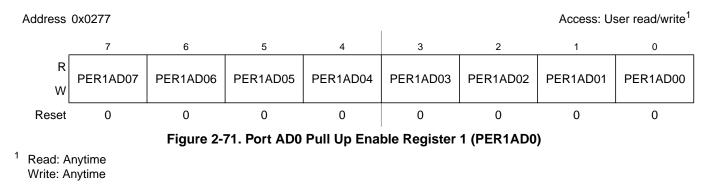

# 2.3.73 Port AD0 Pull Up Enable Register 1 (PER1AD0)

### Table 2-70. PER1AD0 Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port AD0 pull device enable—Enable pull-up device on input pin</li> <li>This bit controls whether a pull device on the associated port input pin is active. If a pin is used as output this bit has no effect. The polarity is selected by the related polarity select register bit.</li> <li>1 Pull device enabled</li> <li>0 Pull device disabled</li> </ul> |

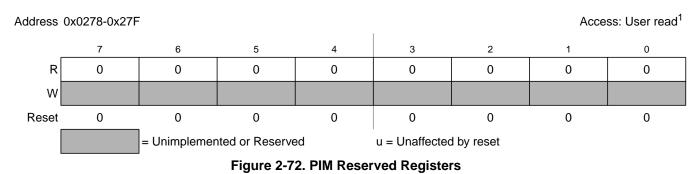

# 2.3.74 PIM Reserved Registers

<sup>1</sup> Read: Always reads 0x00 Write: Unimplemented

# 2.4 Functional Description

# 2.4.1 General

Each pin except PE0, PE1, and BKGD can act as general purpose I/O. In addition each pin can act as an output or input of a peripheral module.

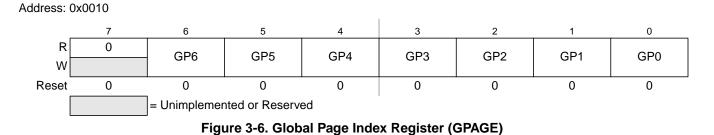

# 3.3.2.2 Global Page Index Register (GPAGE)

### Read: Anytime

### Write: Anytime

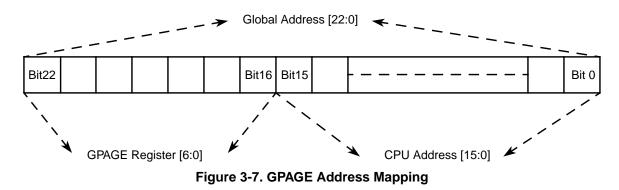

The global page index register is used to construct a 23 bit address in the global map format. It is only used when the CPU is executing a global instruction (GLDAA, GLDAB, GLDD, GLDS, GLDX, GLDY,GSTAA, GSTAB, GSTD, GSTS, GSTX, GSTY) (see CPU Block Guide). The generated global address is the result of concatenation of the CPU local address [15:0] with the GPAGE register [22:16] (see Figure 3-7).

#### Table 3-4. GPAGE Field Descriptions

| Field          | Description                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| 6–0<br>GP[6:0] | <b>Global Page Index Bits 6–0</b> — These page index bits are used to select which of the 128 64KB pages is to be accessed. |

#### Example 3-1. This example demonstrates usage of the GPAGE register

| LDX #0x5<br>MOVB #0x1<br>GLDAA X | 14, GPAGE ; Initiali | GE offset to the val<br>ize GPAGE register w<br>cu A from the global | ith the value of 0x14 |

|----------------------------------|----------------------|----------------------------------------------------------------------|-----------------------|

|----------------------------------|----------------------|----------------------------------------------------------------------|-----------------------|

S12X Debug (S12XDBGV3) Module

## NOTE

Using this configuration, a byte access of ADDR[n] can cause a comparator match if the databus low byte by chance contains the same value as ADDR[n+1] because the databus comparator does not feature access size comparison and uses the mask as a "don't care" function. Thus masked bits do not prevent a match.

Comparators A and C feature an NDB control bit to determine if a match occurs when the data bus differs to comparator register contents or when the data bus is equivalent to the comparator register contents.

# 6.4.2.2 Exact Address Comparator Match (Comparators B and D)

Comparators B and D feature SZ and SZE control bits. If SZE is clear, then the comparator address match qualification functions the same as for comparators A and C.

If the SZE bit is set the access size (word or byte) is compared with the SZ bit value such that only the specified type of access causes a match. Thus if configured for a byte access of a particular address, a word access covering the same address does not lead to match.

| Comparator             | Address | SZE | SZ8 | Condition For Valid Match                                                                        |

|------------------------|---------|-----|-----|--------------------------------------------------------------------------------------------------|

| Comparators<br>A and C | ADDR[n] |     |     | Word and byte accesses of ADDR[n] <sup>(1)</sup><br>MOVB #\$BYTE ADDR[n]<br>MOVW #\$WORD ADDR[n] |

| Comparators<br>B and D | ADDR[n] | 0   | Х   | Word and byte accesses of ADDR[n] <sup>1</sup><br>MOVB #\$BYTE ADDR[n]<br>MOVW #\$WORD ADDR[n]   |

| Comparators<br>B and D | ADDR[n] | 1   | 0   | Word accesses of ADDR[n] <sup>1</sup><br>MOVW #\$WORD ADDR[n]                                    |

| Comparators<br>B and D | ADDR[n] | 1   | 1   | Byte accesses of ADDR[n]<br>MOVB #\$BYTE ADDR[n]                                                 |

Table 6-37. Comparator Access Size Considerations

1. A word access of ADDR[n-1] also accesses ADDR[n] but does not generate a match.

The comparator address register must contain the exact address used in the code.

# 6.4.2.3 Data Bus Comparison NDB Dependency

Comparators A and C each feature an NDB control bit, which allows data bus comparators to be configured to either trigger on equivalence or trigger on difference. This allows monitoring of a difference in the contents of an address location from an expected value.

When matching on an equivalence (NDB=0), each individual data bus bit position can be masked out by clearing the corresponding mask bit (DBGxDHM/DBGxDLM), so that it is ignored in the comparison. A match occurs when all data bus bits with corresponding mask bits set are equivalent. If all mask register bits are clear, then a match is based on the address bus only, the data bus is ignored.

When matching on a difference, mask bits can be cleared to ignore bit positions. A match occurs when any data bus bit with corresponding mask bit set is different. Clearing all mask bits, causes all bits to be ignored and prevents a match because no difference can be detected. In this case address bus equivalence does not cause a match.

| Field                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1<br>SLPRQ <sup>(4)</sup>      | Sleep Mode Request — This bit requests the MSCAN to enter sleep mode, which is an internal power saving mode (see Section 11.4.5.5, "MSCAN Sleep Mode"). The sleep mode request is serviced when the CAN bus is idle, i.e., the module is not receiving a message and all transmit buffers are empty. The module indicates entry to sleep mode by setting SLPAK = 1 (see Section 11.3.2.2, "MSCAN Control Register 1 (CANCTL1)"). SLPRQ cannot be set while the WUPIF flag is set (see Section 11.3.2.5, "MSCAN Receiver Flag Register (CANRFLG)"). Sleep mode will be active until SLPRQ is cleared by the CPU or, depending on the setting of WUPE, the MSCAN detects activity on the CAN bus and clears SLPRQ itself. 0 Running — The MSCAN functions normally 1 Sleep mode request — The MSCAN enters sleep mode when CAN bus idle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 0<br>INITRQ <sup>(5),(6)</sup> | Initialization Mode Request — When this bit is set by the CPU, the MSCAN skips to initialization mode (see<br>Section 11.4.4.5, "MSCAN Initialization Mode"). Any ongoing transmission or reception is aborted and<br>synchronization to the CAN bus is lost. The module indicates entry to initialization mode by setting INITAK = 1<br>(Section 11.3.2.2, "MSCAN Control Register 1 (CANCTL1)").<br>The following registers enter their hard reset state and restore their default values: CANCTL0 <sup>(7)</sup> , CANRFLG <sup>(8)</sup> ,<br>CANRIER <sup>(9)</sup> , CANTFLG, CANTIER, CANTARQ, CANTAAK, and CANTBSEL.<br>The registers CANCTL1, CANBTR0, CANBTR1, CANIDAC, CANIDAR0-7, and CANIDMR0-7 can only be<br>written by the CPU when the MSCAN is in initialization mode (INITRQ = 1 and INITAK = 1). The values of the<br>error counters are not affected by initialization mode.<br>When this bit is cleared by the CPU, the MSCAN restarts and then tries to synchronize to the CAN bus. If the<br>MSCAN is not in bus-off state, it synchronizes after 11 consecutive recessive bits on the CAN bus; if the MSCAN<br>is in bus-off state, it continues to wait for 128 occurrences of 11 consecutive recessive bits.<br>Writing to other bits in CANCTL0, CANRFLG, CANRIER, CANTFLG, or CANTIER must be done only after<br>initialization mode is exited, which is INITRQ = 0 and INITAK = 0.<br>0 Normal operation<br>1 MSCAN in initialization mode<br>sch CAN 2.0A/B specification for a detailed definition of transmitter and receiver states. |  |  |  |  |

In order to protect from accidentally violating the CAN protocol, TXCAN is immediately forced to a recessive state when the CPU enters wait (CSWAI = 1) or stop mode (see Section 11.4.5.2, "Operation in Wait Mode" and Section 11.4.5.3, "Operation in Stop Mode").

- 3. The CPU has to make sure that the WUPE register and the WUPIE wake-up interrupt enable register (see Section 11.3.2.6, "MSCAN Receiver Interrupt Enable Register (CANRIER)) is enabled, if the recovery mechanism from stop or wait is required.

- 4. The CPU cannot clear SLPRQ before the MSCAN has entered sleep mode (SLPRQ = 1 and SLPAK = 1).

- 5. The CPU cannot clear INITRQ before the MSCAN has entered initialization mode (INITRQ = 1 and INITAK = 1).

- 6. In order to protect from accidentally violating the CAN protocol, TXCAN is immediately forced to a recessive state when the initialization mode is requested by the CPU. Thus, the recommended procedure is to bring the MSCAN into sleep mode (SLPRQ = 1 and SLPAK = 1) before requesting initialization mode.

- 7. Not including WUPE, INITRQ, and SLPRQ.

- 8. TSTAT1 and TSTAT0 are not affected by initialization mode.

- 9. RSTAT1 and RSTAT0 are not affected by initialization mode.

# 11.3.2.2 MSCAN Control Register 1 (CANCTL1)

The CANCTL1 register provides various control bits and handshake status information of the MSCAN module as described below.

| Offset<br>Address | Register                                                  | Access |

|-------------------|-----------------------------------------------------------|--------|

| 0x00X0            | Identifier Register 0                                     | R/W    |

| 0x00X1            | Identifier Register 1                                     | R/W    |

| 0x00X2            | Identifier Register 2                                     | R/W    |

| 0x00X3            | Identifier Register 3                                     | R/W    |

| 0x00X4            | Data Segment Register 0                                   | R/W    |

| 0x00X5            | Data Segment Register 1                                   | R/W    |

| 0x00X6            | Data Segment Register 2                                   | R/W    |

| 0x00X7            | Data Segment Register 3                                   | R/W    |

| 0x00X8            | Data Segment Register 4                                   | R/W    |

| 0x00X9            | Data Segment Register 5                                   | R/W    |

| 0x00XA            | Data Segment Register 6                                   | R/W    |

| 0x00XB            | Data Segment Register 7                                   | R/W    |

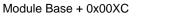

| 0x00XC            | Data Length Register                                      | R/W    |

| 0x00XD            | Transmit Buffer Priority Register <sup>(1)</sup>          | R/W    |

| 0x00XE            | Time Stamp Register (High Byte)                           | R      |

| 0x00XF            | Time Stamp Register (Low Byte)<br>ble for receive buffers | R      |

| Table 11-26 | Message | Buffer | Organization |

|-------------|---------|--------|--------------|

|-------------|---------|--------|--------------|

Not applicable for receive buffers

Figure 11-24 shows the common 13-byte data structure of receive and transmit buffers for extended identifiers. The mapping of standard identifiers into the IDR registers is shown in Figure 11-25.

All bits of the receive and transmit buffers are 'x' out of reset because of RAM-based implementation<sup>1</sup>. All reserved or unused bits of the receive and transmit buffers always read 'x'.

1. Exception: The transmit buffer priority registers are 0 out of reset.

Freescale's Scalable Controller Area Network (S12MSCANV3)

# 11.3.3.3 Data Length Register (DLR)

This register keeps the data length field of the CAN frame.

| Table 11-34. DLK Keyislei Field Descriptions | Table 11-34. | <b>DLR Register Field Descriptions</b> |  |

|----------------------------------------------|--------------|----------------------------------------|--|

|----------------------------------------------|--------------|----------------------------------------|--|

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-0<br>DLC[3:0] | <b>Data Length Code Bits</b> — The data length code contains the number of bytes (data byte count) of the respective message. During the transmission of a remote frame, the data length code is transmitted as programmed while the number of transmitted data bytes is always 0. The data byte count ranges from 0 to 8 for a data frame. Table 11-35 shows the effect of setting the DLC bits. |

### Table 11-35. Data Length Codes

|      | Data Byte |      |      |       |

|------|-----------|------|------|-------|

| DLC3 | DLC2      | DLC1 | DLC0 | Count |

| 0    | 0         | 0    | 0    | 0     |

| 0    | 0         | 0    | 1    | 1     |

| 0    | 0         | 1    | 0    | 2     |

| 0    | 0         | 1    | 1    | 3     |

| 0    | 1         | 0    | 0    | 4     |

| 0    | 1         | 0    | 1    | 5     |

| 0    | 1         | 1    | 0    | 6     |

| 0    | 1         | 1    | 1    | 7     |

| 1    | 0         | 0    | 0    | 8     |

# 11.3.3.4 Transmit Buffer Priority Register (TBPR)

This register defines the local priority of the associated message buffer. The local priority is used for the internal prioritization process of the MSCAN and is defined to be highest for the smallest binary number. The MSCAN implements the following internal prioritization mechanisms:

• All transmission buffers with a cleared TXEx flag participate in the prioritization immediately before the SOF (start of frame) is sent.

# Chapter 13 Pulse-Width Modulator (S12PWM8B8CV1)

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                                                               |

|-------------------|------------------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| 01.17             |                  | 08-01-2004        |        | Added clarification of PWMIF operation in STOP and WAIT mode.<br>Added notes on minimum pulse width of emergency shutdown<br>signal. |

# 13.1 Introduction

The PWM definition is based on the HC12 PWM definitions. It contains the basic features from the HC11 with some of the enhancements incorporated on the HC12: center aligned output mode and four available clock sources. The PWM module has eight channels with independent control of left and center aligned outputs on each channel.

Each of the eight channels has a programmable period and duty cycle as well as a dedicated counter. A flexible clock select scheme allows a total of four different clock sources to be used with the counters. Each of the modulators can create independent continuous waveforms with software-selectable duty rates from 0% to 100%. The PWM outputs can be programmed as left aligned outputs or center aligned outputs.

# 13.1.1 Features

The PWM block includes these distinctive features:

- Eight independent PWM channels with programmable period and duty cycle

- Dedicated counter for each PWM channel

- Programmable PWM enable/disable for each channel

- Software selection of PWM duty pulse polarity for each channel

- Period and duty cycle are double buffered. Change takes effect when the end of the effective period is reached (PWM counter reaches zero) or when the channel is disabled.

- Programmable center or left aligned outputs on individual channels

- Eight 8-bit channel or four 16-bit channel PWM resolution

- Four clock sources (A, B, SA, and SB) provide for a wide range of frequencies

- Programmable clock select logic

- Emergency shutdown

#### Pulse-Width Modulator (S12PWM8B8CV1)

| Register<br>Name  |        | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

|-------------------|--------|-------|------------|----------------|--------|---|--------|---------|---------|

| 0x0019<br>PWMPER5 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x001A<br>PWMPER6 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x001B<br>PWMPER7 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x001C<br>PWMDTY0 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x001D<br>PWMDTY1 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x001E<br>PWMDTY2 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x001F<br>PWMDTY3 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x0010<br>PWMDTY4 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x0021<br>PWMDTY5 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x0022<br>PWMDTY6 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x0023<br>PWMDTY7 | R<br>W | Bit 7 | 6          | 5              | 4      | 3 | 2      | 1       | Bit 0   |

| 0x0024<br>PWMSDN  | R<br>W | PWMIF | PWMIE      | 0<br>PWMRSTRT  | PWMLVL | 0 | PWM7IN | PWM7INL | PWM7ENA |

|                   |        |       | = Unimplem | ented or Reser | ved    |   |        |         |         |

Figure 13-2. PWM Register Summary (Sheet 3 of 3)

1 Intended for factory test purposes only.

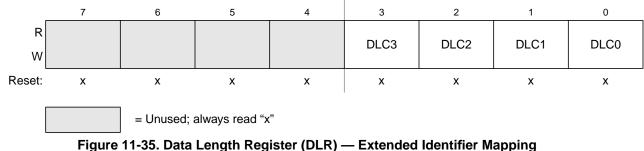

# 13.3.2.1 PWM Enable Register (PWME)

Each PWM channel has an enable bit (PWMEx) to start its waveform output. When any of the PWMEx bits are set (PWMEx = 1), the associated PWM output is enabled immediately. However, the actual PWM waveform is not available on the associated PWM output until its clock source begins its next cycle due to the synchronization of PWMEx and the clock source.

### NOTE

The first PWM cycle after enabling the channel can be irregular.

An exception to this is when channels are concatenated. Once concatenated mode is enabled (CONxx bits set in PWMCTL register), enabling/disabling the corresponding 16-bit PWM channel is controlled by the low order PWMEx bit. In this case, the high order bytes PWMEx bits have no effect and their corresponding PWM output lines are disabled.

While in run mode, if all eight PWM channels are disabled (PWME7-0 = 0), the prescaler counter shuts off for power savings.

Module Base + 0x0000

Figure 13-3. PWM Enable Register (PWME)

Read: Anytime

### Write: Anytime

| Field      | Description                                                                                                                                                                                                                                                                                                                        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PWME7 | Pulse Width Channel 7 Enable         0       Pulse width channel 7 is disabled.         1       Pulse width channel 7 is enabled. The pulse modulated signal becomes available at PWM output bit 7 when its clock source begins its next cycle.                                                                                    |

| 6<br>PWME6 | <ul> <li>Pulse Width Channel 6 Enable</li> <li>0 Pulse width channel 6 is disabled.</li> <li>1 Pulse width channel 6 is enabled. The pulse modulated signal becomes available at PWM output bit6 when<br/>its clock source begins its next cycle. If CON67=1, then bit has no effect and PWM output line 6 is disabled.</li> </ul> |

| 5<br>PWME5 | Pulse Width Channel 5 Enable         0       Pulse width channel 5 is disabled.         1       Pulse width channel 5 is enabled. The pulse modulated signal becomes available at PWM output bit 5 when its clock source begins its next cycle.                                                                                    |

| 4<br>PWME4 | Pulse Width Channel 4 Enable         0       Pulse width channel 4 is disabled.         1       Pulse width channel 4 is enabled. The pulse modulated signal becomes available at PWM, output bit 4 when its clock source begins its next cycle. If CON45 = 1, then bit has no effect and PWM output bit4 is disabled.             |

| 3<br>PWME3 | <ul> <li>Pulse Width Channel 3 Enable</li> <li>0 Pulse width channel 3 is disabled.</li> <li>1 Pulse width channel 3 is enabled. The pulse modulated signal becomes available at PWM, output bit 3 when its clock source begins its next cycle.</li> </ul>                                                                         |

| 2<br>PWME2 | <ul> <li>Pulse Width Channel 2 Enable</li> <li>Pulse width channel 2 is disabled.</li> <li>Pulse width channel 2 is enabled. The pulse modulated signal becomes available at PWM, output bit 2 when its clock source begins its next cycle. If CON23 = 1, then bit has no effect and PWM output bit2 is disabled.</li> </ul>       |

| Table 15-2. SPICR1 | Field Descriptions (continued) |

|--------------------|--------------------------------|

|--------------------|--------------------------------|

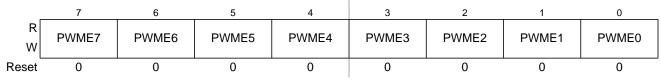

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>SSOE  | <b>Slave Select Output Enable</b> — The $\overline{SS}$ output feature is enabled only in master mode, if MODFEN is set, by asserting the SSOE as shown in Table 15-3. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.                                                                                                                                                              |

| 0<br>LSBFE | <ul> <li>LSB-First Enable — This bit does not affect the position of the MSB and LSB in the data register. Reads and writes of the data register always have the MSB in the highest bit position. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Data is transferred most significant bit first.</li> <li>1 Data is transferred least significant bit first.</li> </ul> |

### Table 15-3. SS Input / Output Selection

| MODFEN | SSOE | Master Mode Slave Mode             |          |  |

|--------|------|------------------------------------|----------|--|

| 0      | 0    | SS not used by SPI                 | SS input |  |

| 0      | 1    | SS not used by SPI                 | SS input |  |

| 1      | 0    | SS input with MODF feature SS inpu |          |  |

| 1      | 1    | SS is slave select output          | SS input |  |

# 15.3.2.2 SPI Control Register 2 (SPICR2)

Module Base +0x0001

Figure 15-4. SPI Control Register 2 (SPICR2)

### Read: Anytime

Write: Anytime; writes to the reserved bits have no effect

### Read: Anytime

Write: Anytime.

### Table 16-11. TCTL3/TCTL4 Field Descriptions

| Field | Description                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------|

| 7:0   | Input Capture Edge Control — These eight pairs of control bits configure the input capture edge detector |

| EDGnB | circuits.                                                                                                |

| EDGnA |                                                                                                          |

| EDGnB | EDGnA | Configuration                           |

|-------|-------|-----------------------------------------|

| 0     | 0     | Capture disabled                        |

| 0     | 1     | Capture on rising edges only            |

| 1     | 0     | Capture on falling edges only           |

| 1     | 1     | Capture on any edge (rising or falling) |

### Table 16-12. Edge Detector Circuit Configuration

## 16.3.2.10 Timer Interrupt Enable Register (TIE)

Module Base + 0x000C

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | C7I | C6I | C5I | C4I | C3I | C2I | C1I | COI |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Figure 16-18. Timer Interrupt Enable Register (TIE)

Read: Anytime

Write: Anytime.

### Table 16-13. TIE Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>C7I:C0 | Input Capture/Output Compare "x" Interrupt Enable — The bits in TIE correspond bit-for-bit with the bits in the TFLG1 status register. If cleared, the corresponding flag is disabled from causing a hardware interrupt. If set, the corresponding flag is enabled to cause a interrupt. |

| ECCRIX[2:0] | FECCR Register Content               |                                    |                           |  |  |  |  |

|-------------|--------------------------------------|------------------------------------|---------------------------|--|--|--|--|

|             | Bits [15:8]                          | Bit[7]                             | Bits[6:0]                 |  |  |  |  |

| 000         | Parity bits read from<br>Flash block | 0                                  | Global address<br>[22:16] |  |  |  |  |

| 001         | Global address [15:0]                |                                    |                           |  |  |  |  |

| 010         |                                      | Data 0 [15:0]                      |                           |  |  |  |  |

| 011         | Da                                   | Data 1 [15:0] (P-Flash only)       |                           |  |  |  |  |

| 100         | Da                                   | Data 2 [15:0] (P-Flash only)       |                           |  |  |  |  |

| 101         | Da                                   | Data 3 [15:0] (P-Flash only)       |                           |  |  |  |  |

| 110         | Not used, returns 0x0000 when read   |                                    |                           |  |  |  |  |

| 111         | Not use                              | Not used, returns 0x0000 when read |                           |  |  |  |  |

### Table 18-25. FECCR Index Settings

### Table 18-26. FECCR Index=000 Bit Descriptions

| Field               | Description                                                                                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8<br>PAR[7:0]    | <b>ECC Parity Bits</b> — Contains the 8 parity bits from the 72 bit wide P-Flash data word or the 6 parity bits, allocated to PAR[5:0], from the 22 bit wide D-Flash word with PAR[7:6]=00. |

| 6–0<br>GADDR[22:16] | <b>Global Address</b> — The GADDR[22:16] field contains the upper seven bits of the global address having caused the error.                                                                 |

The P-Flash word addressed by ECCRIX = 001 contains the lower 16 bits of the global address. The following four words addressed by ECCRIX = 010 to 101 contain the 64-bit wide data phrase. The four data words and the parity byte are the uncorrected data read from the P-Flash block.

The D-Flash word addressed by ECCRIX = 001 contains the lower 16 bits of the global address. The uncorrected 16-bit data word is addressed by ECCRIX = 010.

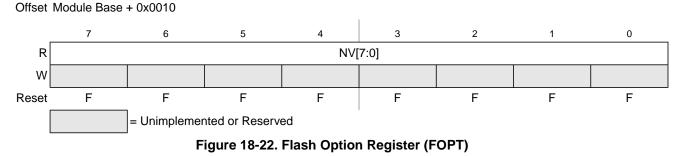

# 18.3.2.15 Flash Option Register (FOPT)

The FOPT register is the Flash option register.

All bits in the FOPT register are readable but are not writable.

S12XS Family Reference Manual, Rev. 1.13

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FPOPEN      | <ul> <li>Flash Protection Operation Enable — The FPOPEN bit determines the protection function for program or erase operations as shown in Table 20-18 for the P-Flash block.</li> <li>When FPOPEN is clear, the FPHDIS and FPLDIS bits define unprotected address ranges as specified by the corresponding FPHS and FPLS bits</li> <li>When FPOPEN is set, the FPHDIS and FPLDIS bits enable protection for the address range specified by the corresponding FPHS and FPLDIS bits bits enable protection for the address range specified by the corresponding FPHS and FPLDIS bits</li> </ul> |

| 6<br>RNV[6]      | <b>Reserved Nonvolatile Bit</b> — The RNV bit should remain in the erased state for future enhancements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5<br>FPHDIS      | Flash Protection Higher Address Range Disable — The FPHDIS bit determines whether there is a<br>protected/unprotected area in a specific region of the P-Flash memory ending with global address 0x7F_FFFF.0 Protection/Unprotection enabled<br>1 Protection/Unprotection disabled                                                                                                                                                                                                                                                                                                             |

| 4–3<br>FPHS[1:0] | Flash Protection Higher Address Size — The FPHS bits determine the size of the protected/unprotected area in P-Flash memory as shown inTable 20-19. The FPHS bits can only be written to while the FPHDIS bit is set.                                                                                                                                                                                                                                                                                                                                                                          |

| 2<br>FPLDIS      | Flash Protection Lower Address Range Disable — The FPLDIS bit determines whether there is a protected/unprotected area in a specific region of the P-Flash memory beginning with global address 0x7F_8000.         0       Protection/Unprotection enabled         1       Protection/Unprotection disabled                                                                                                                                                                                                                                                                                    |

| 1–0<br>FPLS[1:0] | Flash Protection Lower Address Size — The FPLS bits determine the size of the protected/unprotected area in P-Flash memory as shown in Table 20-20. The FPLS bits can only be written to while the FPLDIS bit is set.                                                                                                                                                                                                                                                                                                                                                                          |

### Table 20-17. FPROT Field Descriptions

#### Table 20-18. P-Flash Protection Function

| FPOPEN | FPHDIS | FPLDIS | Function <sup>1</sup>           |  |  |  |

|--------|--------|--------|---------------------------------|--|--|--|

| 1      | 1      | 1      | No P-Flash Protection           |  |  |  |

| 1      | 1      | 0      | Protected Low Range             |  |  |  |

| 1      | 0      | 1      | Protected High Range            |  |  |  |

| 1      | 0      | 0      | Protected High and Low Ranges   |  |  |  |

| 0      | 1      | 1      | Full P-Flash Memory Protected   |  |  |  |

| 0      | 1      | 0      | Unprotected Low Range           |  |  |  |

| 0      | 0      | 1      | Unprotected High Range          |  |  |  |

| 0      | 0      | 0      | Unprotected High and Low Ranges |  |  |  |

<sup>1</sup> For range sizes, refer to Table 20-19 and Table 20-20.

### Table 20-19. P-Flash Protection Higher Address Range

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x7F_F800-0x7F_FFFF  | 2 Kbytes       |

| 01        | 0x7F_F000-0x7F_FFFF  | 4 Kbytes       |

| 10        | 0x7F_E000-0x7F_FFFF  | 8 Kbytes       |

| 11        | 0x7F_C000-0x7F_FFFF  | 16 Kbytes      |

S12XS Family Reference Manual, Rev. 1.13

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 101 at command launch                                         |

|          | ACCERR    | Set if command not available in current mode (see Table 20-28)                      |

|          | ACCERK    | Set if an invalid global address [22:0] is supplied <sup>1</sup>                    |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the global address [22:0] points to a protected area                         |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

#### Table 20-40. Program P-Flash Command Error Handling

<sup>1</sup> As defined by the memory map for FTMR128K1.

# 20.4.2.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash block 0. The Program Once reserved field can be read using the Read Once command as described in Section 20.4.2.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash block 0 cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |                |  |  |  |  |  |

|-------------|---------------------------------------------|----------------|--|--|--|--|--|

| 000         | 0x07                                        | Not Required   |  |  |  |  |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |                |  |  |  |  |  |

| 010         | Program Once word 0 value                   |                |  |  |  |  |  |

| 011         | Program Once word 1 value                   |                |  |  |  |  |  |

| 100         | Program Once word 2 value                   |                |  |  |  |  |  |

| 101         | Program Once                                | e word 3 value |  |  |  |  |  |

Table 20-41. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash block 0 will return invalid data.

# Appendix C PCB Layout Guidelines

# C.1 General

The PCB must be carefully laid out to ensure proper operation of the voltage regulator as well as of the MCU itself. The following rules must be observed:

- Every supply pair must be decoupled by a ceramic capacitor connected as near as possible to the corresponding pins .

- Central point of the ground star should be the VSS3 pin.

- Use low ohmic low inductance connections between VSS1, VSS2 and VSS3.

- VSSPLL must be directly connected to VSS3.

- Keep traces of VSSPLL, EXTAL, and XTAL as short as possible and occupied board area for C7, C8, and Q1 as small as possible.

- Do not place other signals or supplies underneath area occupied by C7, C8, and Q1 and the connection area to the MCU.

- Central power input should be fed in at the VDDA/VSSA pins.

Example layouts are illustrated on the following pages.

| Component | Purpose                             | Туре                      | Value    |  |

|-----------|-------------------------------------|---------------------------|----------|--|

| C1        | V <sub>DDF</sub> filter capacitor   | Ceramic X7R               | 220 nF   |  |

| C2        | N/A                                 | _                         | —        |  |

| C3        | V <sub>DDX2</sub> filter capacitor  | X7R/tantalum              | >=100 nF |  |

| C4        | V <sub>DDPLL</sub> filter capacitor | Ceramic X7R               | 220 nF   |  |

| C5        | OSC load capacitor                  | From crystal manufacturer |          |  |

| C6        | OSC load capacitor                  |                           |          |  |

| C7        | V <sub>DDR</sub> filter capacitor   | X7R/tantalum              | >=100 nF |  |

| C8        | N/A                                 | _                         | —        |  |

| C9        | V <sub>DD</sub> filter capacitor    | Ceramic X7R               | 220 nF   |  |

| C10       | V <sub>DDA1</sub> filter capacitor  | Ceramic X7R               | >=100 nF |  |

| C11       | V <sub>DDX1</sub> filter capacitor  | X7R/tantalum              | >=100 nF |  |

| Q1        | Quartz                              |                           |          |  |

### Table C-1. Recommended Decoupling Capacitor Choice

| Address | Name     |             | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   |

|---------|----------|-------------|--------|--------|--------|--------|--------|--------|---------|---------|

| 0x0104  | FCNFG    | R<br>W      | CCIE   | 0      | 0      | IGNSF  | 0      | 0      | FDFD    | FSFD    |

| 0x0105  | FERCNFG  | R<br>W      | 0      | 0      | 0      | 0      | 0      | 0      | DFDIE   | SFDIE   |

| 0x0106  | FSTAT    | R<br>W      | CCIE   | 0      | ACCERR | FPVIOL | MGBUSY | RSVD   | MGSTAT1 | MGSTAT0 |

| 0x0107  | FERSTAT  | R<br>W      | 0      | 0      | 0      | 0      | 0      | 0      | DFDIF   | SFDIF   |

| 0x0108  | FPROT    | R<br>W      | FPOPEN | RNV6   | FPHDIS | FPHS1  | FPHS0  | FPLDIS | FPLS1   | FPLS0   |

| 0x0109  | DFPROT   | R<br>W      | DPOPEN | 0      | 0      | DPS4   | DPS3   | DPS2   | DPS1    | DPS0    |

| 0x010A  | FCCOBHI  | R<br>W      | CCOB15 | CCOB14 | CCOB13 | CCOB12 | CCOB11 | CCOB10 | CCOB9   | CCOB8   |

| 0x010B  | FCCOBLO  | R<br>W      | CCOB7  | CCOB6  | CCOB5  | CCOB4  | ССОВЗ  | CCOB2  | CCOB1   | CCOB0   |

| 0x010C  | Reserved | R<br>W      | 0      | 0      | 0      | 0      | 0      | 0      | 0       | 0       |

| 0x010D  | Reserved | R<br>W      | 0      | 0      | 0      | 0      | 0      | 0      | 0       | 0       |

| 0x010E  | FECCRHI  | R           | ECCR15 | ECCR14 | ECCR13 | ECCR12 | ECCR11 | ECCR10 | ECCR9   | ECCR8   |

| 0x010F  | FECCRLO  | W<br>R      | ECCR7  | ECCR6  | ECCR5  | ECCR4  | ECCR3  | ECCR2  | ECCR1   | ECCR0   |

| 0x0110  | FOPT     | W<br>R      | NV7    | NV6    | NV5    | NV4    | NV3    | NV2    | NV1     | NV0     |

| 0x0111  | Reserved | W<br>R      | 0      | 0      | 0      | 0      | 0      | 0      | 0       | 0       |

| 0x0112  | Reserved | W<br>R      | 0      | 0      | 0      | 0      | 0      | 0      | 0       | 0       |

| 0x0113  | Reserved | W<br>R<br>W | 0      | 0      | 0      | 0      | 0      | 0      | 0       | 0       |

### 0x0100–0x0113 NVM Control Register (FTMR) Map (continued)

# 0x0114–0x011F Reserved Register Space

| Address | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0114- | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x011F  | Reserved | W |       |       |       |       |       |       |       |       |