Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 40MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 91                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 112-LQFP                                                                |

| Supplier Device Package    | 112-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs256j0cal |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Appendix A Electrical Characteristics

| A.1 | General  |                                               | 657 |

|-----|----------|-----------------------------------------------|-----|

|     |          | Parameter Classification                      |     |

|     | A.1.2    | Power Supply                                  | 657 |

|     | A.1.3    | Pins                                          |     |

|     | A.1.4    | Current Injection                             |     |

|     | A.1.5    | Absolute Maximum Ratings                      | 659 |

|     | A.1.6    | ESD Protection and Latch-up Immunity.         | 660 |

|     | A.1.7    | Operating Conditions                          |     |

|     | A.1.8    | Power Dissipation and Thermal Characteristics | 662 |

|     |          | I/O Characteristics                           |     |

|     | A.1.10   | ) Supply Currents                             | 669 |

| A.2 |          | haracteristics                                |     |

|     | A.2.1    | ATD Operating Characteristics.                | 673 |

|     | A.2.2    | Factors Influencing Accuracy                  | 673 |

|     | A.2.3    | ATD Accuracy                                  | 675 |

| A.3 | NVM, F   | Flash                                         | 679 |

|     | A.3.1    | Timing Parameters                             | 679 |

|     | A.3.2    | NVM Reliability Parameters.                   | 683 |

| A.4 | Voltage  | Regulator                                     | 685 |

| A.5 |          | Loads                                         |     |

|     | A.5.1    | Resistive Loads                               | 686 |

|     | A.5.2    | Capacitive Loads                              | 686 |

|     | A.5.3    | Chip Power-up and Voltage Drops               | 686 |

| A.6 | Reset, C | Dscillator and PLL                            | 688 |

|     | A.6.1    | Startup                                       | 688 |

|     | A.6.2    | Oscillator                                    | 690 |

|     | A.6.3    | Phase Locked Loop                             | 691 |

| A.7 | MSCAN    | Ν                                             | 693 |

| A.8 | SPI Tin  | ning                                          | 694 |

|     | A.8.1    | Master Mode                                   | 694 |

|     | A.8.2    | Slave Mode                                    | 696 |

# Appendix B Package Information

| <b>B</b> .1 | 112-pin LQFP Mechanical Dimensions | . 699 |

|-------------|------------------------------------|-------|

|             | 80-Pin QFP Mechanical Dimensions   |       |

| B.3         | 64-Pin LQFP Mechanical Dimensions  | . 705 |

# Appendix C PCB Layout Guidelines

| C.1 | General                                   | 708 |

|-----|-------------------------------------------|-----|

|     | C.1.1 112-Pin LQFP Recommended PCB Layout | 709 |

Port Integration Module (S12XSPIMV1)

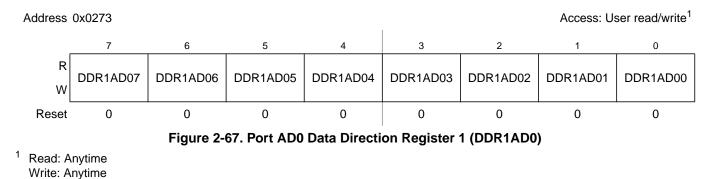

# 2.3.69 Port AD0 Data Direction Register 1 (DDR1AD0)

#### Table 2-66. DDR1AD0 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7-0<br>DDR1AD0 | Port AD0 data direction—<br>This bit determines whether the associated pin is an input or output.<br>To use the digital input function the ATD Digital Input Enable Register (ATD0DIEN) has to be set to logic level "1".<br>1 Associated pin configured as output<br>0 Associated pin configured as input |  |

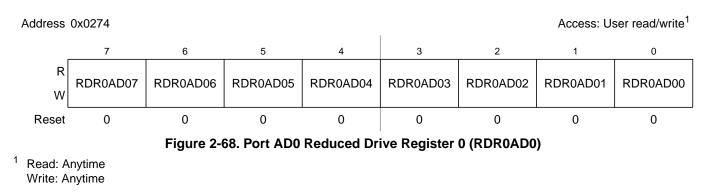

# 2.3.70 Port AD0 Reduced Drive Register 0 (RDR0AD0)

#### Table 2-67. RDR0AD0 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                              |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7-0<br>RDR0AD0 | <b>Port AD0 reduced drive</b> —Select reduced drive for output pin<br>This bit configures the drive strength of the associated output pin as either full or reduced. If a pin is used as input<br>this bit has no effect. The reduced drive function is independent of which function is being used on a particular pin. |  |

|                | 1 Reduced drive selected (approx. 1/5 of the full drive strength)<br>0 Full drive strength enabled                                                                                                                                                                                                                       |  |

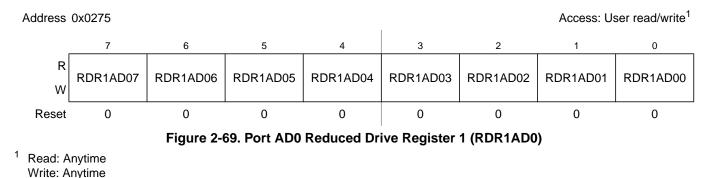

# 2.3.71 Port AD0 Reduced Drive Register 1 (RDR1AD0)

#### Table 2-68. RDR1AD0 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                              |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7-0<br>RDR1AD0 | <b>Port AD0 reduced drive</b> —Select reduced drive for output pin<br>This bit configures the drive strength of the associated output pin as either full or reduced. If a pin is used as input<br>this bit has no effect. The reduced drive function is independent of which function is being used on a particular pin. |  |

|                | 1 Reduced drive selected (approx. 1/5 of the full drive strength)<br>0 Full drive strength enabled                                                                                                                                                                                                                       |  |

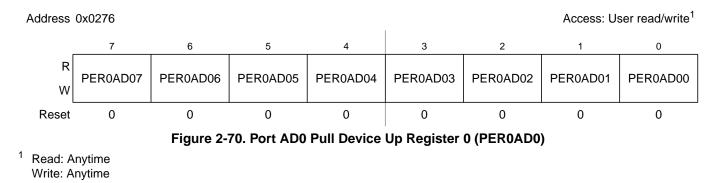

# 2.3.72 Port AD0 Pull Up Enable Register 0 (PER0AD0)

#### Table 2-69. PER0AD0 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                          |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7-0<br>PER0AD0 | Port AD0 pull device enable—Enable pull-up device on input pin<br>This bit controls whether a pull device on the associated port input pin is active. If a pin is used as output this bit has<br>no effect. The polarity is selected by the related polarity select register bit.<br>1 Pull device enabled<br>0 Pull device disabled |  |

Memory Mapping Control (S12XMMCV4)

# 3.3.2.1 Mode Register (MODE)

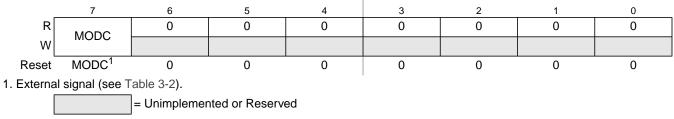

Address: 0x000B PRR

Figure 3-3. Mode Register (MODE)

Read: Anytime. Write: Only if a transition is allowed (see Figure 3-5).

The MODE bits of the MODE register are used to establish the MCU operating mode.

| Field     | Description                                                                                                                                                                                                                                                                                                                          |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>MODC | <b>Mode Select Bit</b> — This bit controls the current operating mode during <b>RESET</b> high (inactive). The external node pin MODC determines the operating mode during <b>RESET</b> low (active). The state of the pin is latched into the respective register bit after the <b>RESET</b> signal goes inactive (see Figure 3-3). |  |

|           | Write restrictions exist to disallow transitions between certain modes. Figure 3-5 illustrates all allowed mode changes. Attempting non authorized transitions will not change the MODE bits, but it will block further writes to these register bits except in special modes.                                                       |  |

|           | Write accesses to the MODE register are blocked when the device is secured.                                                                                                                                                                                                                                                          |  |

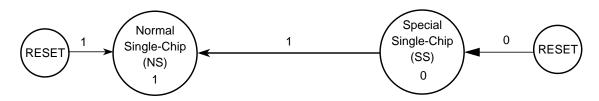

Transition done by external pins (MODC)

Transition done by write access to the MODE register

Figure 3-5. Mode Transition Diagram when MCU is Unsecured

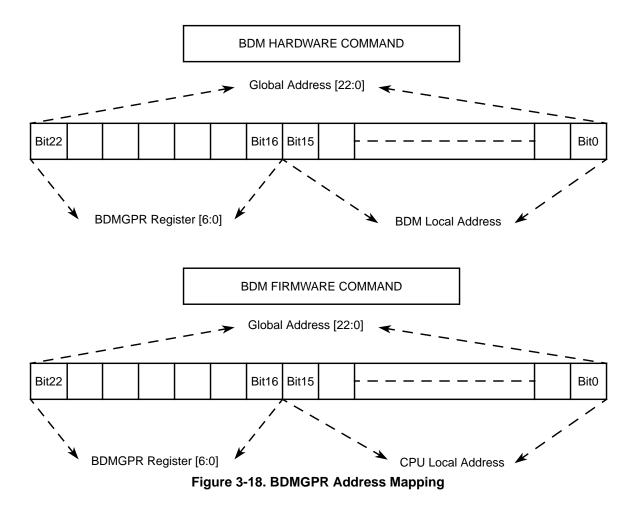

### Expansion of the BDM Local Address Map

PPAGE, RPAGE, and EPAGE registers are also used for the expansion of the BDM local address to the global address. These registers can be read and written by the BDM.

The BDM expansion scheme is the same as the CPU expansion scheme.

## 3.4.2.2 Global Addresses Based on the Global Page

### **CPU Global Addresses Based on the Global Page**

The seven global page index bits allow access to the full 8MB address map that can be accessed with 23 address bits. This provides an alternative way to access all of the various pages of FLASH, RAM and Data FLASH.

The GPAGE Register is used only when the CPU is executing a global instruction (see Section 3.3.2.2, "Global Page Index Register (GPAGE)). The generated global address is the result of concatenation of the CPU local address [15:0] with the GPAGE register [22:16] (see Figure 3-7).

#### **BDM Global Addresses Based on the Global Page**

The seven BDMGPR Global Page index bits allow access to the full 8MB address map that can be accessed with 23 address bits. This provides an alternative way to access all of the various pages of FLASH, RAM and Data FLASH.

The BDM global page index register (BDMGPR) is used only in the case the CPU is executing a firmware command which uses a global instruction (like GLDD, GSTD) or by a BDM hardware command (like WRITE\_W, WRITE\_BYTE, READ\_W, READ\_BYTE). See the BDM Block Guide for further details.

The generated global address is a result of concatenation of the BDM local address with the BDMGPR register [22:16] in the case of a hardware command or concatenation of the CPU local address and the BDMGPR register [22:16] in the case of a firmware command (see Figure 3-18).

Memory Mapping Control (S12XMMCV4)

## 3.4.2.3 Implemented Memory Map

The global memory spaces reserved for the internal resources (RAM, Data FLASH, and FLASH) are not determined by the MMC module. Size of the individual internal resources are however fixed in the design of the device cannot be changed by the user. Please refer to the SoC Guide for further details. Figure 3-19 and Table 3-10 show the memory spaces occupied by the on-chip resources. Please note that the memory spaces have fixed top addresses.

| Internal Resource | \$Address                                          |

|-------------------|----------------------------------------------------|

| RAM               | RAM_LOW = 0x10_0000 minus RAMSIZE <sup>1</sup>     |

| Data FLASH        | DF_HIGH = 0x10_0000 plus DFLASHSIZE <sup>2</sup>   |

| FLASH             | FLASH_LOW = 0x80_0000 minus FLASHSIZE <sup>3</sup> |

1 RAMSIZE is the hexadecimal value of RAM SIZE in Bytes

2 DFLASHSIZE is the hexadecimal value of DFLASH SIZE in Bytes

3 FLASHSIZE is the hexadecimal value of FLASH SIZE in Bytes

## 4.5.3.2 XGATE Wake Up from Stop or Wait Mode

Interrupt request channels which are configured to be handled by the XGATE module are capable of waking up the XGATE module. Interrupt request channels handled by the XGATE module do not affect the state of the CPU.

S12X Debug (S12XDBGV3) Module

| SUB_1            | BRN                               | *                           | ; JMP Destination address TRACE BUFFER ENTRY 1<br>; RTI Destination address TRACE BUFFER ENTRY 3 |

|------------------|-----------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------|

|                  | NOP                               |                             | i                                                                                                |

| ADDR1            | DBNE                              | A,PART5                     | ; Source address TRACE BUFFER ENTRY 4                                                            |

|                  |                                   |                             |                                                                                                  |

| IRQ_ISR          | LDAB                              | #\$F0                       | ; IRQ Vector \$FFF2 = TRACE BUFFER ENTRY 2                                                       |

|                  | STAB                              | VAR_C1                      |                                                                                                  |

|                  | RTI                               |                             | ;                                                                                                |

|                  | Th                                | ne execution flow taking in | to account the IRQ is as follows                                                                 |

|                  |                                   |                             |                                                                                                  |

|                  | I DV                              |                             |                                                                                                  |

|                  | LDX                               | #SUB_1                      |                                                                                                  |

| MARK1            | JMP                               | 0,X                         | ;                                                                                                |

| MARK1<br>IRQ_ISR |                                   |                             | ;<br>;                                                                                           |

|                  | JMP                               | 0,X                         |                                                                                                  |

|                  | JMP<br>LDAB                       | 0,X<br>#\$F0                |                                                                                                  |

|                  | JMP<br>LDAB<br>STAB               | 0,X<br>#\$F0                | ;                                                                                                |

| IRQ_ISR          | JMP<br>LDAB<br>STAB<br>RTI        | 0,X<br>#\$F0<br>VAR_C1      | ;                                                                                                |

| IRQ_ISR          | JMP<br>LDAB<br>STAB<br>RTI<br>BRN | 0,X<br>#\$F0<br>VAR_C1      | ;                                                                                                |

### 6.4.5.2.2 Loop1 Mode

Loop1 Mode, similarly to Normal Mode also stores only COF address information to the trace buffer, it however allows the filtering out of redundant information.

The intent of Loop1 Mode is to prevent the Trace Buffer from being filled entirely with duplicate information from a looping construct such as delays using the DBNE instruction or polling loops using BRSET/BRCLR instructions. Immediately after address information is placed in the Trace Buffer, the S12XDBG module writes this value into a background register. This prevents consecutive duplicate address entries in the Trace Buffer resulting from repeated branches.

Loop1 Mode only inhibits consecutive duplicate source address entries that would typically be stored in most tight looping constructs. It does not inhibit repeated entries of destination addresses or vector addresses, since repeated entries of these would most likely indicate a bug in the user's code that the S12XDBG module is designed to help find.

### 6.4.5.2.3 Detail Mode

In Detail Mode, address and data for all memory and register accesses is stored in the trace buffer. This mode also features information byte entries to the trace buffer, for each address byte entry. The information byte indicates the size of access (word or byte) and the type of access (read or write).

When tracing CPU12X activity in Detail Mode, all cycles are traced except those when the CPU12X is either in a free or opcode fetch cycle, the address range can be limited to a range specified by the TRANGE bits in DBGTCR. This function uses comparators C and D to define an address range inside which CPU12X activity should be traced (see Table 6-40). Thus the traced CPU12X activity can be restricted to particular register range accesses.

### 6.4.5.2.4 Pure PC Mode

In Pure PC Mode, tracing from the CPU the PC addresses of all executed opcodes, including illegal opcodes, are stored.

## 11.4.4.2 Special System Operating Modes

The MSCAN module behaves as described within this specification in all special system operating modes. Write restrictions which exist on specific registers in normal modes are lifted for test purposes in special modes.

## 11.4.4.3 Emulation Modes

In all emulation modes, the MSCAN module behaves just like in normal system operating modes as described within this specification.

## 11.4.4.4 Listen-Only Mode

In an optional CAN bus monitoring mode (listen-only), the CAN node is able to receive valid data frames and valid remote frames, but it sends only "recessive" bits on the CAN bus. In addition, it cannot start a transmission.

If the MAC sub-layer is required to send a "dominant" bit (ACK bit, overload flag, or active error flag), the bit is rerouted internally so that the MAC sub-layer monitors this "dominant" bit, although the CAN bus may remain in recessive state externally.

## 11.4.4.5 MSCAN Initialization Mode

The MSCAN enters initialization mode when it is enabled (CANE=1).

When entering initialization mode during operation, any on-going transmission or reception is immediately aborted and synchronization to the CAN bus is lost, potentially causing CAN protocol violations. To protect the CAN bus system from fatal consequences of violations, the MSCAN immediately drives TXCAN into a recessive state.

### NOTE

The user is responsible for ensuring that the MSCAN is not active when initialization mode is entered. The recommended procedure is to bring the MSCAN into sleep mode (SLPRQ = 1 and SLPAK = 1) before setting the INITRQ bit in the CANCTL0 register. Otherwise, the abort of an on-going message can cause an error condition and can impact other CAN bus devices.

In initialization mode, the MSCAN is stopped. However, interface registers remain accessible. This mode is used to reset the CANCTLO, CANRFLG, CANRIER, CANTFLG, CANTIER, CANTARQ, CANTAAK, and CANTBSEL registers to their default values. In addition, the MSCAN enables the configuration of the CANBTRO, CANBTR1 bit timing registers; CANIDAC; and the CANIDAR, CANIDMR message filters. See Section 11.3.2.1, "MSCAN Control Register 0 (CANCTLO)," for a detailed description of the initialization mode.

Periodic Interrupt Timer (S12PIT24B4CV1)

#### Serial Communication Interface (S12SCIV5)

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 14-18 summarizes the results of the data bit samples.

| RT8, RT9, and RT10 Samples | Data Bit Determination | Noise Flag |

|----------------------------|------------------------|------------|

| 000                        | 0                      | 0          |

| 001                        | 0                      | 1          |

| 010                        | 0                      | 1          |

| 011                        | 1                      | 1          |

| 100                        | 0                      | 1          |

| 101                        | 1                      | 1          |

| 110                        | 1                      | 1          |

| 111                        | 1                      | 0          |

Table 14-18. Data Bit Recovery

### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are logic 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit (logic 0).

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 14-19 summarizes the results of the stop bit samples.

| RT8, RT9, and RT10 Samples | Framing Error Flag | Noise Flag |

|----------------------------|--------------------|------------|

| 000                        | 1                  | 0          |

| 001                        | 1                  | 1          |

| 010                        | 1                  | 1          |

| 011                        | 0                  | 1          |

| 100                        | 1                  | 1          |

| 101                        | 0                  | 1          |

| 110                        | 0                  | 1          |

| 111                        | 0                  | 0          |

Table 14-19. Stop Bit Recovery

## Read: Anytime but will always return 0x0000 (1 state is transient)

## Write: Anytime

| Table 16-3. | <b>CFORC</b> Field | d Descriptions |

|-------------|--------------------|----------------|

|             |                    |                |

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>FOC[7:0] | <ul> <li>Force Output Compare Action for Channel 7:0 — A write to this register with the corresponding data bit(s) set causes the action which is programmed for output compare "x" to occur immediately. The action taken is the same as if a successful comparison had just taken place with the TCx register except the interrupt flag does not get set.</li> <li>Note: A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. If forced output compare on any channel occurs at the same time as the successful output compare then forced output compare action will take precedence and interrupt flag won't get set.</li> </ul> |

# 16.3.2.3 Output Compare 7 Mask Register (OC7M)

Module Base + 0x0002

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | OC7M7 | OC7M6 | OC7M5 | OC7M4 | OC7M3 | OC7M2 | OC7M1 | OC7M0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 16-8. Output Compare 7 Mask Register (OC7M)

Read: Anytime

Write: Anytime

### Table 16-4. OC7M Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OC7M[7:0] | <ul> <li>Output Compare 7 Mask — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. For each OC7M bit that is set, the output compare action reflects the corresponding OC7D bit.</li> <li>0 The corresponding OC7Dx bit in the output compare 7 data register will not be transferred to the timer port on a channel 7 event, even if the corresponding pin is setup for output compare.</li> <li>1 The corresponding OC7Dx bit in the output compare 7 data register will be transferred to the timer port on a channel 7 event.</li> <li>Note: The corresponding channel must also be setup for output compare (IOSx = 1 and OCPDx = 0) for data to be transferred from the output compare 7 data register to the timer port.</li> </ul> |

Timer Module (TIM16B8CV2)

| PAMOD | PEDGE | Pin Action                                   |

|-------|-------|----------------------------------------------|

| 0     | 0     | Falling edge                                 |

| 0     | 1     | Rising edge                                  |

| 1     | 0     | Div. by 64 clock enabled with pin high level |

| 1     | 1     | Div. by 64 clock enabled with pin low level  |

#### Table 16-19. Pin Action

### NOTE

If the timer is not active (TEN = 0 in TSCR), there is no divide-by-64 because the  $\div$ 64 clock is generated by the timer prescaler.

#### Table 16-20. Timer Clock Selection

| CLK1 | CLK0 | CLK0 Timer Clock                                 |  |

|------|------|--------------------------------------------------|--|

| 0    | 0    | Use timer prescaler clock as timer counter clock |  |

| 0    | 1    | Use PACLK as input to timer counter clock        |  |

| 1    | 0    | Use PACLK/256 as timer counter clock frequency   |  |

| 1    | 1    | Use PACLK/65536 as timer counter clock frequency |  |

For the description of PACLK please refer Figure 16-30.

If the pulse accumulator is disabled (PAEN = 0), the prescaler clock from the timer is always used as an input clock to the timer counter. The change from one selected clock to the other happens immediately after these bits are written.

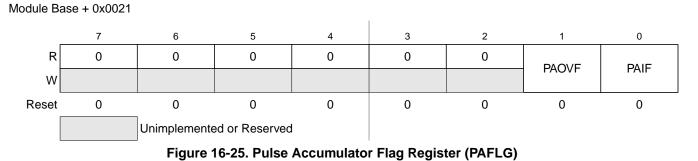

## 16.3.2.16 Pulse Accumulator Flag Register (PAFLG)

### Read: Anytime

Write: Anytime

When the TFFCA bit in the TSCR register is set, any access to the PACNT register will clear all the flags in the PAFLG register. Timer module or Pulse Accumulator must stay enabled (TEN=1 or PAEN=1) while clearing these bits.

corresponding deassertion levels, signal LVR deasserts. The LVR function is available only in Full Performance Mode.

# 17.4.6 HTD - High Temperature Detect

Subblock HTD is responsible for generating the high temperature interrupt (HTI). HTD monitors the die temperature  $T_{DIE}$  and continuously updates the status flag HTDS. Interrupt flag HTIF is set whenever status flag HTDS changes its value.

The HTD is available in FPM and is inactive in Reduced Power Mode and Shutdown Mode.

The HT Trimming bits HTTR[3:0] can be set so that the temperature offset is zero, if accurate temperature measurement is desired.

See Table 23-16 for the trimming effect of APITR.

# 17.4.7 Regulator Control (CTRL)

This part contains the register block of VREG\_3V3 and further digital functionality needed to control the operating modes. CTRL also represents the interface to the digital core logic.

# 17.4.8 Autonomous Periodical Interrupt (API)

Subblock API can generate periodical interrupts independent of the clock source of the MCU. To enable the timer, the bit APIFE needs to be set.

The API timer is either clocked by a trimmable internal RC oscillator or the bus clock. Timer operation will freeze when MCU clock source is selected and bus clock is turned off. See CRG specification for details. The clock source can be selected with bit APICLK. APICLK can only be written when APIFE is not set.

The APIR[15:0] bits determine the interrupt period. APIR[15:0] can only be written when APIFE is cleared. As soon as APIFE is set, the timer starts running for the period selected by APIR[15:0] bits. When the configured time has elapsed, the flag APIF is set. An interrupt, indicated by flag APIF = 1, is triggered if interrupt enable bit APIE = 1. The timer is started automatically again after it has set APIF.

The procedure to change APICLK or APIR[15:0] is first to clear APIFE, then write to APICLK or APIR[15:0], and afterwards set APIFE.

The API Trimming bits APITR[5:0] must be set so the minimum period equals 0.2 ms if stable frequency is desired.

See Table 17-8 for the trimming effect of APITR.

### NOTE

The first period after enabling the counter by APIFE might be reduced by API start up delay  $t_{sdel}$ . The API internal RC oscillator clock is not available if VREG\_3V3 is in Shutdown Mode.

#### 256 KByte Flash Module (S12XFTMR256K1V1)

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the field margin level for the targeted block and then set the CCIF flag. Valid margin level settings for the Set Field Margin Level command are defined in Table 18-57.

| CCOB<br>(CCOBIX=001) | Level Description                 |

|----------------------|-----------------------------------|

| 0x0000               | Return to Normal Level            |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

| Register | Error Bit | Error Condition                                                |  |  |

|----------|-----------|----------------------------------------------------------------|--|--|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                    |  |  |

|          |           | Set if command not available in current mode (see Table 18-28) |  |  |

|          |           | Set if an invalid global address [22:16] is supplied           |  |  |

|          |           | Set if an invalid margin level setting is supplied             |  |  |

|          | FPVIOL    | None                                                           |  |  |

|          | MGSTAT1   | None                                                           |  |  |

|          | MGSTAT0   | None                                                           |  |  |

### CAUTION

Field margin levels must only be used during verify of the initial factory programming.

### NOTE

Field margin levels can be used to check that Flash memory contents have adequate margin for data retention at the normal level setting. If unexpected results are encountered when checking Flash memory contents at field margin levels, the Flash memory contents should be erased and reprogrammed.

## 18.4.2.14 Erase Verify D-Flash Section Command

The Erase Verify D-Flash Section command will verify that a section of code in the D-Flash is erased. The Erase Verify D-Flash Section command defines the starting point of the data to be verified and the number of words.

64 KByte Flash Module (S12XFTMR64K1V1)

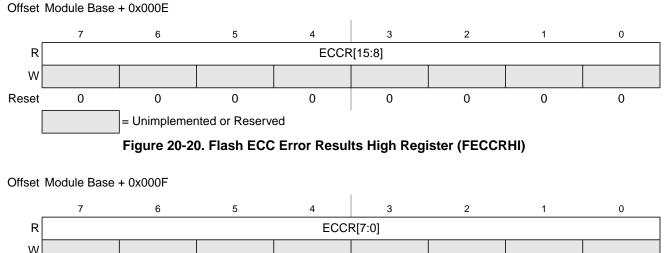

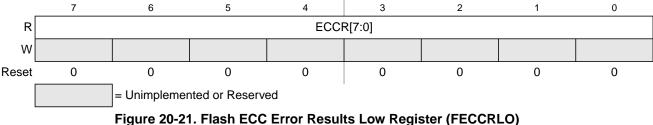

fault information will be recorded until the specific ECC fault flag has been cleared. In the event of simultaneous ECC faults the priority for fault recording is double bit fault over single bit fault.

All FECCR bits are readable but not writable.

Table 20-25. FECCR Index Settings

| ECCRIX[2:0] | FECCR Register Content               |        |                           |  |

|-------------|--------------------------------------|--------|---------------------------|--|

|             | Bits [15:8]                          | Bit[7] | Bits[6:0]                 |  |

| 000         | Parity bits read from<br>Flash block | 0      | Global address<br>[22:16] |  |

| 001         | Global address [15:0]                |        |                           |  |

| 010         | Data 0 [15:0]                        |        |                           |  |

| 011         | Data 1 [15:0] (P-Flash only)         |        |                           |  |

| 100         | Data 2 [15:0] (P-Flash only)         |        |                           |  |

| 101         | Data 3 [15:0] (P-Flash only)         |        |                           |  |

| 110         | Not used, returns 0x0000 when read   |        |                           |  |

| 111         | Not used, returns 0x0000 when read   |        |                           |  |

### Table 20-26. FECCR Index=000 Bit Descriptions

| Field               | Description                                                                                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | <b>ECC Parity Bits</b> — Contains the 8 parity bits from the 72 bit wide P-Flash data word or the 6 parity bits, allocated to PAR[5:0], from the 22 bit wide D-Flash word with PAR[7:6]=00. |

| 6–0<br>GADDR[22:16] | <b>Global Address</b> — The GADDR[22:16] field contains the upper seven bits of the global address having caused the error.                                                                 |

| CCOBIX[2:0] | FCCOB Parameters     |                                                       |  |

|-------------|----------------------|-------------------------------------------------------|--|

| 000         | 0x0D                 | Global address [22:16] to identify the<br>Flash block |  |

| 001         | Margin level setting |                                                       |  |

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

Valid margin level settings for the Set User Margin Level command are defined in Table 20-54.

#### Table 20-54. Valid Set User Margin Level Settings

| CCOB<br>(CCOBIX=001) | Level Description                |  |  |  |

|----------------------|----------------------------------|--|--|--|

| 0x0000               | Return to Normal Level           |  |  |  |

| 0x0001               | User Margin-1 Level <sup>1</sup> |  |  |  |

| 0x0002               | User Margin-0 Level <sup>2</sup> |  |  |  |

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### Table 20-55. Set User Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                   |  |  |

|----------|-----------|-------------------------------------------------------------------|--|--|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                       |  |  |

|          |           | Set if command not available in current mode (see Table 20-28)    |  |  |

|          |           | Set if an invalid global address [22:16] is supplied <sup>1</sup> |  |  |

|          |           | Set if an invalid margin level setting is supplied                |  |  |

|          | FPVIOL    | None                                                              |  |  |

|          | MGSTAT1   | None                                                              |  |  |

|          | MGSTAT0   | None                                                              |  |  |

<sup>1</sup> As defined by the memory map for FTMR128K1.

### NOTE

User margin levels can be used to check that Flash memory contents have adequate margin for normal level read operations. If unexpected results are encountered when checking Flash memory contents at user margin levels, a potential loss of information has been detected.

Electrical Characteristics

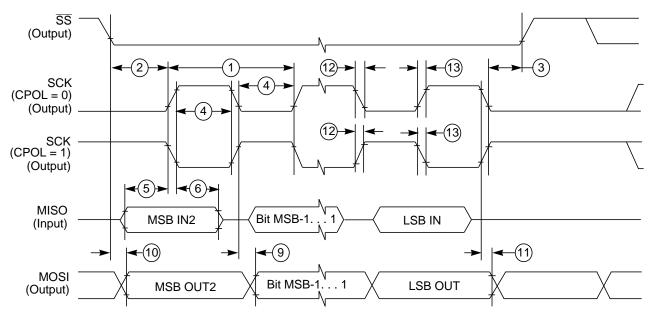

# A.8 SPI Timing

This section provides electrical parametrics and ratings for the SPI. In Table A-26 the measurement conditions are listed.

| Description                                                      | Value                        | Unit |

|------------------------------------------------------------------|------------------------------|------|

| Drive mode                                                       | Full drive mode              | _    |

| Load capacitance C <sub>LOAD</sub> <sup>1</sup> , on all outputs | 50                           | pF   |

| Thresholds for delay measurement points                          | (20% / 80%) V <sub>DDX</sub> | V    |

Table A-26. Measurement Conditions

Timing specified for equal load on all SPI output pins. Avoid asymmetric load.

## A.8.1 Master Mode

In Figure A-6 the timing diagram for master mode with transmission format CPHA = 0 is depicted.

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, bit 2... MSB.

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

- A DIMENSIONS TO BE DETERMINED AT SEATING PLANE C.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 mm AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm.

- THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0. 25 mm PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

- A EXACT SHAPE OF EACH CORNER IS OPTIONAL.

- A THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 mm AND 0.25 mm FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                       |  | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|-------------------------------------------------------------------------------|--|--------------|------------------|-------------|

| <sup>TITLE:</sup> 64LD LQFP,<br>10 X 10 X 1.4 PKG,<br>0.5 PITCH, CASE OUTLINE |  | DOCUMENT NO  | ): 98ASS23234W   | REV: E      |

|                                                                               |  | CASE NUMBER  | R: 840F-02       | 11 AUG 2006 |

|                                                                               |  | STANDARD: JE | DEC MS-026 BCD   |             |

#### Figure B-8. 64-pin LQFP (case no. 840F) - page 3