Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 40MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 59                                                                      |

| Program Memory Size        | 256КВ (256К х 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 8x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs256j0maa |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

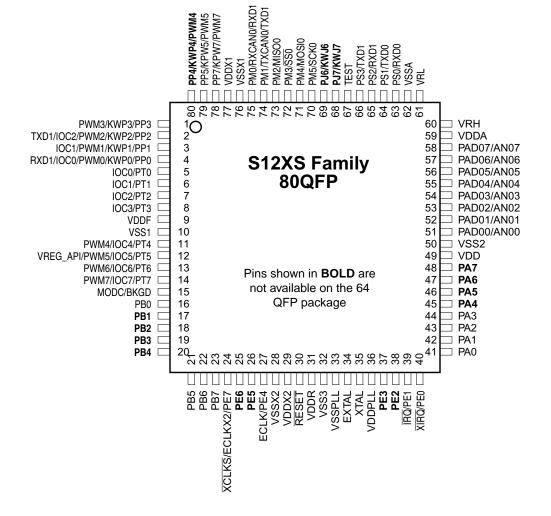

Figure 1-4. S12XS Family Pin Assignments 80-pin QFP Package

34

# Table 1-6 provides a pin out summary listing the availability and functionality of individual pins for each package option.

| Pack        | age Ter   | minal      |      |              | Function     |              |              | Power            | Internal Pull<br>Resistor |                | Description                                               |  |

|-------------|-----------|------------|------|--------------|--------------|--------------|--------------|------------------|---------------------------|----------------|-----------------------------------------------------------|--|

| LQFP<br>112 | QFP<br>80 | LQFP<br>64 | Pin  | 2nd<br>Func. | 3rd<br>Func. | 4th<br>Func. | 5th<br>Func. | Supply           | CTRL                      | Reset<br>State | Description                                               |  |

| 1           | 1         | 1          | PP3  | KWP3         | PWM3         |              |              | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       | Port P I/O, interrupt,<br>PWM channel                     |  |

| 2           | 2         | 2          | PP2  | KWP2         | PWM2         | IOC2         | TXD1         | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       | Port P I/O, interrupt,<br>PWM/TIM channel, TXD<br>of SCI1 |  |

| 3           | 3         | 3          | PP1  | KWP1         | PWM1         | IOC1         | _            | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       | Port P I/O, interrupt,<br>PWM/TIM channel                 |  |

| 4           | 4         | 4          | PP0  | KWP0         | PWM0         | IOC0         | RXD1         | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       | Port P I/O, interrupt,<br>PWM/TIM channel,<br>RXD of SCI1 |  |

| 5           | -         | -          | PK3  | _            | —            | —            | _            | V <sub>DDX</sub> | PUCR                      | Up             | Port K I/O                                                |  |

| 6           | -         | -          | PK2  | _            | —            | —            | _            | V <sub>DDX</sub> | PUCR                      | Up             | Port K I/O                                                |  |

| 7           | -         | -          | PK1  | _            | —            | —            | _            | V <sub>DDX</sub> | PUCR                      | Up             | Port K I/O                                                |  |

| 8           | -         | -          | PK0  | _            | —            | —            | _            | V <sub>DDX</sub> | PUCR                      | Up             | Port K I/O                                                |  |

| 9           | 5         | 5          | PT0  | IOC0         | —            | —            | _            | V <sub>DDX</sub> | PERT/PPST                 | Disabled       | Port T I/O, TIM channel                                   |  |

| 10          | 6         | 6          | PT1  | IOC1         | —            | —            | —            | V <sub>DDX</sub> | PERT/PPST                 | Disabled       | Port T I/O, TIM channel                                   |  |

| 11          | 7         | 7          | PT2  | IOC2         | —            | _            | _            | V <sub>DDX</sub> | PERT/PPST                 | Disabled       | Port T I/O, TIM channel                                   |  |

| 12          | 8         | 8          | PT3  | IOC3         | _            |              |              | V <sub>DDX</sub> | PERT/PPST                 | Disabled       | Port T I/O, TIM channel                                   |  |

| 13          | 9         | 9          | VDDF |              | _            |              | _            | _                | —                         | _              | —                                                         |  |

| 14          | 10        | 10         | VSS1 | —            | —            | _            | _            | _                | —                         | _              | —                                                         |  |

| 15          | 11        | 11         | PT4  | IOC4         | PWM4         | _            | —            | V <sub>DDX</sub> | PERT/PPST                 | Disabled       | Port T I/O, PWM/TIM channel                               |  |

#### Table 1-6. Pin-Out Summary<sup>1</sup>

**Device Overview S12XS Family**

**Device Overview S12XS Family**

### 1.2.4.3 VDD, VSS2, VSS3 — Core Power Pins

The voltage supply of nominally 1.8 V is derived from the internal voltage regulator. The return current path is through the VSS2 and VSS3 pins. No static external loading of these pins is permitted.

### 1.2.4.4 VDDF, VSS1 — NVM Power Pins

The voltage supply of nominally 2.8 V is derived from the internal voltage regulator. The return current path is through the VSS1 pin. No static external loading of these pins is permitted.

### 1.2.4.5 VDDA, VSSA — Power Supply Pins for ATD and Voltage Regulator

These are the power supply and ground input pins for the analog-to-digital converters and the voltage regulator.

### 1.2.4.6 VRH, VRL — ATD Reference Voltage Input Pins

$V_{RH}$  and  $V_{RL}$  are the reference voltage input pins for the analog-to-digital converter.

### 1.2.4.7 VDDPLL, VSSPLL — Power Supply Pins for PLL

These pins provide operating voltage and ground for the oscillator and the phased-locked loop. The voltage supply of nominally 1.8 V is derived from the internal voltage regulator. This allows the supply voltage to the oscillator and PLL to be bypassed independently. This voltage is generated by the internal voltage regulator. No static external loading of these pins is permitted.

| Mnemonic            | Nominal<br>Voltage | Description                                                                                                                                                    |  |  |  |

|---------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VDDR                | 5.0 V              | External power supply to internal voltage regulator                                                                                                            |  |  |  |

| VDDX[2:1]           | 5.0 V              | External power and ground, supply to pin                                                                                                                       |  |  |  |

| VSSX[2:1]           | 0 V                | drivers                                                                                                                                                        |  |  |  |

| VDDA                | 5.0 V              | Operating voltage and ground for the                                                                                                                           |  |  |  |

| VSSA                | 0 V                | analog-to-digital converters and the<br>reference for the internal voltage regulator,<br>allows the supply voltage to the A/D to be<br>bypassed independently. |  |  |  |

| VRL                 | 0 V                | Reference voltages for the analog-to-digital                                                                                                                   |  |  |  |

| VRH                 | 5.0 V              | converter.                                                                                                                                                     |  |  |  |

| VDD                 | 1.8 V              | Internal power and ground generated by                                                                                                                         |  |  |  |

| VSS1, VSS2,<br>VSS3 | 0 V                | internal regulator for the internal core.                                                                                                                      |  |  |  |

| VDDF                | 2.8 V              | Internal power and ground generated by internal regulator for the internal NVM.                                                                                |  |  |  |

Table 1-7. Power and Ground Connection Summary

# 4.5 Initialization/Application Information

### 4.5.1 Initialization

After system reset, software should:

- Initialize the interrupt vector base register if the interrupt vector table is not located at the default location (0xFF10–0xFFF9).

- Initialize the interrupt processing level configuration data registers (INT\_CFADDR, INT\_CFDATA0-7) for all interrupt vector requests with the desired priority levels and the request target (CPU or XGATE module). It might be a good idea to disable unused interrupt requests.

- If the XGATE module is used, setup the XGATE interrupt priority register (INT\_XGPRIO) and configure the XGATE module (please refer the XGATE Block Guide for details).

- Enable I maskable interrupts by clearing the I bit in the CCR.

- Enable the X maskable interrupt by clearing the X bit in the CCR (if required).

### 4.5.2 Interrupt Nesting

The interrupt request priority level scheme makes it possible to implement priority based interrupt request nesting for the I bit maskable interrupt requests handled by the CPU.

• I bit maskable interrupt requests can be interrupted by an interrupt request with a higher priority, so that there can be up to seven nested I bit maskable interrupt requests at a time (refer to Figure 4-14 for an example using up to three nested interrupt requests).

I bit maskable interrupt requests cannot be interrupted by other I bit maskable interrupt requests per default. In order to make an interrupt service routine (ISR) interruptible, the ISR must explicitly clear the I bit in the CCR (CLI). After clearing the I bit, I bit maskable interrupt requests with higher priority can interrupt the current ISR.

An ISR of an interruptible I bit maskable interrupt request could basically look like this:

- Service interrupt, e.g., clear interrupt flags, copy data, etc.

- Clear I bit in the CCR by executing the instruction CLI (thus allowing interrupt requests with higher priority)

- Process data

- Return from interrupt by executing the instruction RTI

# NP

#### Background Debug Module (S12XBDMV2)

- Hardware handshake protocol to increase the performance of the serial communication

- Active out of reset in special single chip mode

- Nine hardware commands using free cycles, if available, for minimal CPU intervention

- Hardware commands not requiring active BDM

- 14 firmware commands execute from the standard BDM firmware lookup table

- Software control of BDM operation during wait mode

- Software selectable clocks

- Global page access functionality

- Enabled but not active out of reset in emulation modes (if modes available)

- CLKSW bit set out of reset in emulation modes (if modes available).

- When secured, hardware commands are allowed to access the register space in special single chip mode, if the non-volatile memory erase test fail.

- Family ID readable from firmware ROM at global address 0x7FFF0F (value for HCS12X devices is 0xC1)

- BDM hardware commands are operational until system stop mode is entered (all bus masters are in stop mode)

# 5.1.2 Modes of Operation

BDM is available in all operating modes but must be enabled before firmware commands are executed. Some systems may have a control bit that allows suspending thefunction during background debug mode.

## 5.1.2.1 Regular Run Modes

All of these operations refer to the part in run mode and not being secured. The BDM does not provide controls to conserve power during run mode.

- Normal modes General operation of the BDM is available and operates the same in all normal modes.

- Special single chip mode

In special single chip mode, background operation is enabled and active out of reset. This allows programming a system with blank memory.

• Emulation modes (if modes available)

In emulation mode, background operation is enabled but not active out of reset. This allows debugging and programming a system in this mode more easily.

## 5.1.2.2 Secure Mode Operation

If the device is in secure mode, the operation of the BDM is reduced to a small subset of its regular run mode operation. Secure operation prevents BDM and CPU accesses to non-volatile memory (Flash and/or EEPROM) other than allowing erasure. For more information please see Section 5.4.1, "Security".

# Chapter 8 S12XE Clocks and Reset Generator (S12XECRGV1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected           | Description of Changes                                                                                                                           |  |  |  |

|--------------------|------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V01.00             | 26 Oct. 2005     |                                | Initial release                                                                                                                                  |  |  |  |

| V01.01             | 02 Nov 2006      | 8.4.1.1/8-254                  | Table "Examples of IPLL Divider settings": corrected \$32 to \$31                                                                                |  |  |  |

| V01.02             | 4 Mar. 2008      | 8.4.1.4/8-257<br>8.4.3.3/8-261 | Corrected details                                                                                                                                |  |  |  |

| V01.03             | 1 Sep. 2008      | Table 8-14                     | added 100MHz example for PLL                                                                                                                     |  |  |  |

| V01.04             | 20 Nov. 2008     | 8.3.2.4/8-243                  | S12XECRG Flags Register: corrected address to Module Base + 0x0003                                                                               |  |  |  |

| V01.05             | 19. Sep 2009     | 8.5.1/8-263                    | Modified Note below Table 8-17./8-263                                                                                                            |  |  |  |

| V01.06             | 18. Sep 2012     | Table 8-14<br>8.5.1            | Added footnote concerning maximum clock frequencies to table<br>Removed redundant examples from table<br>Replaced reference to MMC documentation |  |  |  |

Table 8-1. Revision History

# 8.1 Introduction

This specification describes the function of the Clocks and Reset Generator (S12XECRG).

### 8.1.1 Features

The main features of this block are:

- Phase Locked Loop (IPLL) frequency multiplier with internal filter

- Reference divider

- Post divider

- Configurable internal filter (no external pin)

- Optional frequency modulation for defined jitter and reduced emission

- Automatic frequency lock detector

- Interrupt request on entry or exit from locked condition

- Self Clock Mode in absence of reference clock

- System Clock Generator

- Clock Quality Check

- User selectable fast wake-up from Stop in Self-Clock Mode for power saving and immediate program execution

- Clock switch for either Oscillator or PLL based system clocks

- Computer Operating Properly (COP) watchdog timer with time-out clear window.

S12XE Clocks and Reset Generator (S12XECRGV1)

# 8.6.1 Description of Interrupt Operation

### 8.6.1.1 Real Time Interrupt

The S12XECRG generates a real time interrupt when the selected interrupt time period elapses. RTI interrupts are locally disabled by setting the RTIE bit to zero. The real time interrupt flag (RTIF) is set to 1 when a timeout occurs, and is cleared to 0 by writing a 1 to the RTIF bit.

The RTI continues to run during Pseudo Stop Mode if the PRE bit is set to 1. This feature can be used for periodic wakeup from Pseudo Stop if the RTI interrupt is enabled.

### 8.6.1.2 IPLL Lock Interrupt

The S12XECRG generates a IPLL Lock interrupt when the LOCK condition of the IPLL has changed, either from a locked state to an unlocked state or vice versa. Lock interrupts are locally disabled by setting the LOCKIE bit to zero. The IPLL Lock interrupt flag (LOCKIF) is set to1 when the LOCK condition has changed, and is cleared to 0 by writing a 1 to the LOCKIF bit.

### 8.6.1.3 Self Clock Mode Interrupt

The S12XECRG generates a Self Clock Mode interrupt when the SCM condition of the system has changed, either entered or exited Self Clock Mode. SCM conditions are caused by a failing clock quality check after power on reset (POR) or low voltage reset (LVR) or recovery from Full Stop Mode (PSTP = 0) or Clock Monitor failure. For details on the clock quality check refer to Section 8.4.1.4, "Clock Quality Checker". If the clock monitor is enabled (CME = 1) a loss of external clock will also cause a SCM condition (SCME = 1).

SCM interrupts are locally disabled by setting the SCMIE bit to zero. The SCM interrupt flag (SCMIF) is set to1 when the SCM condition has changed, and is cleared to 0 by writing a 1 to the SCMIF bit.

| Table 10-7. | ATDCTL2 F | ield Descrip | ptions (co | ontinued) |

|-------------|-----------|--------------|------------|-----------|

|-------------|-----------|--------------|------------|-----------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>ETRIGLE | <b>External Trigger Level/Edge Control</b> — This bit controls the sensitivity of the external trigger signal. See Table 10-8 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3<br>ETRIGP  | External Trigger Polarity — This bit controls the polarity of the external trigger signal. See Table 10-8 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2<br>ETRIGE  | <ul> <li>External Trigger Mode Enable — This bit enables the external trigger on one of the AD channels or one of the ETRIG3-0 inputs as described in Table 10-6. If external trigger source is one of the AD channels, the digital input buffer of this channel is enabled. The external trigger allows to synchronize the start of conversion with external events. External trigger will not work while converting in stop mode.</li> <li>0 Disable external trigger</li> <li>1 Enable external trigger</li> </ul>                                                           |

| 1<br>ASCIE   | <ul> <li>ATD Sequence Complete Interrupt Enable</li> <li>0 ATD Sequence Complete interrupt requests are disabled.</li> <li>1 ATD Sequence Complete interrupt will be requested whenever SCF=1 is set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                |

| 0<br>ACMPIE  | <ul> <li>ATD Compare Interrupt Enable — If automatic compare is enabled for conversion <i>n</i> (CMPE[<i>n</i>]=1 in ATDCMPE register) this bit enables the compare interrupt. If the CCF[<i>n</i>] flag is set (showing a successful compare for conversion <i>n</i>), the compare interrupt is triggered.</li> <li>0 ATD Compare interrupt requests are disabled.</li> <li>1 For the conversions in a sequence for which automatic compare is enabled (CMPE[<i>n</i>]=1), ATD Compare Interrupt will be requested whenever any of the respective CCF flags is set.</li> </ul> |

Table 10-8. External Trigger Configurations

| ETRIGLE | ETRIGP | External Trigger Sensitivity |

|---------|--------|------------------------------|

| 0       | 0      | Falling edge                 |

| 0       | 1      | Rising edge                  |

| 1       | 0      | Low level                    |

| 1       | 1      | High level                   |

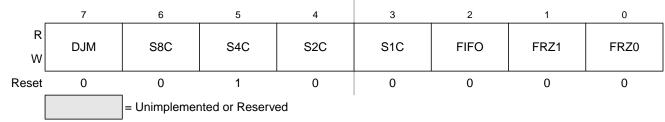

# 10.3.2.4 ATD Control Register 3 (ATDCTL3)

Writes to this register will abort current conversion sequence.

Module Base + 0x0003

Read: Anytime

Write: Anytime

#### Freescale's Scalable Controller Area Network (S12MSCANV3)

1. Read: Anytime

Write: Anytime when out of initialization mode; exceptions are read-only RXACT and SYNCH, RXFRM (which is set by the module only), and INITRQ (which is also writable in initialization mode)

#### NOTE

The CANCTL0 register, except WUPE, INITRQ, and SLPRQ, is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable again as soon as the initialization mode is exited (INITRQ = 0 and INITAK = 0).

#### Table 11-3. CANCTL0 Register Field Descriptions

| Field                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RXFRM                | <ul> <li>Received Frame Flag — This bit is read and clear only. It is set when a receiver has received a valid message correctly, independently of the filter configuration. After it is set, it remains set until cleared by software or reset. Clearing is done by writing a 1. Writing a 0 is ignored. This bit is not valid in loopback mode.</li> <li>0 No valid message was received since last clearing this flag</li> <li>1 A valid message was received since last clearing of this flag</li> </ul>                                                                                                                                                     |

| 6<br>RXACT                | <ul> <li>Receiver Active Status — This read-only flag indicates the MSCAN is receiving a message<sup>(1)</sup>. The flag is controlled by the receiver front end. This bit is not valid in loopback mode.</li> <li>0 MSCAN is transmitting or idle</li> <li>1 MSCAN is receiving a message (including when arbitration is lost)</li> </ul>                                                                                                                                                                                                                                                                                                                       |

| 5<br>CSWAI <sup>(2)</sup> | <ul> <li>CAN Stops in Wait Mode — Enabling this bit allows for lower power consumption in wait mode by disabling all the clocks at the CPU bus interface to the MSCAN module.</li> <li>0 The module is not affected during wait mode</li> <li>1 The module ceases to be clocked during wait mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |

| 4<br>SYNCH                | <ul> <li>Synchronized Status — This read-only flag indicates whether the MSCAN is synchronized to the CAN bus and able to participate in the communication process. It is set and cleared by the MSCAN.</li> <li>0 MSCAN is not synchronized to the CAN bus</li> <li>1 MSCAN is synchronized to the CAN bus</li> </ul>                                                                                                                                                                                                                                                                                                                                           |

| 3<br>TIME                 | <b>Timer Enable</b> — This bit activates an internal 16-bit wide free running timer which is clocked by the bit clock rate.<br>If the timer is enabled, a 16-bit time stamp will be assigned to each transmitted/received message within the active TX/RX buffer. Right after the EOF of a valid message on the CAN bus, the time stamp is written to the highest bytes (0x000E, 0x000F) in the appropriate buffer (see Section 11.3.3, "Programmer's Model of Message Storage"). The internal timer is reset (all bits set to 0) when disabled. This bit is held low in initialization mode.<br>0 Disable internal MSCAN timer<br>1 Enable internal MSCAN timer |

| 2<br>WUPE <sup>(3)</sup>  | <ul> <li>Wake-Up Enable — This configuration bit allows the MSCAN to restart from sleep mode or from power down mode (entered from sleep) when traffic on CAN is detected (see Section 11.4.5.5, "MSCAN Sleep Mode"). This bit must be configured before sleep mode entry for the selected function to take effect.</li> <li>0 Wake-up disabled — The MSCAN ignores traffic on CAN</li> <li>1 Wake-up enabled — The MSCAN is able to restart</li> </ul>                                                                                                                                                                                                          |

Freescale's Scalable Controller Area Network (S12MSCANV3)

| BRP5 | BRP4 | BRP3 | BRP2 | BRP1 | BRP0 | Prescaler value (P) |

|------|------|------|------|------|------|---------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 1                   |

| 0    | 0    | 0    | 0    | 0    | 1    | 2                   |

| 0    | 0    | 0    | 0    | 1    | 0    | 3                   |

| 0    | 0    | 0    | 0    | 1    | 1    | 4                   |

| :    | :    | :    | :    | :    | :    | :                   |

| 1    | 1    | 1    | 1    | 1    | 1    | 64                  |

#### Table 11-7. Baud Rate Prescaler

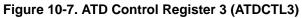

## 11.3.2.4 MSCAN Bus Timing Register 1 (CANBTR1)

The CANBTR1 register configures various CAN bus timing parameters of the MSCAN module.

Module Base + 0x0003

Access: User read/write<sup>(1)</sup>

#### 1. Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 11-8. CANBTR1 Register Field Descriptions

Figure 11-7. MSCAN Bus Timing Register 1 (CANBTR1)

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Sampling — This bit determines the number of CAN bus samples taken per bit time.</li> <li>0 One sample per bit.</li> <li>1 Three samples per bit<sup>(1)</sup>.</li> <li>If SAMP = 0, the resulting bit value is equal to the value of the single bit positioned at the sample point. If SAMP = 1, the resulting bit value is determined by using majority rule on the three total samples. For higher bit rates, it is recommended that only one sample is taken per bit time (SAMP = 0).</li> </ul> |

| <b>Time Segment 2</b> — Time segments within the bit time fix the number of clock cycles per bit time and the location of the sample point (see Figure 11-44). Time segment 2 (TSEG2) values are programmable as shown in Table 11-9.                                                                                                                                                                                                                                                                          |

| <b>Time Segment 1</b> — Time segments within the bit time fix the number of clock cycles per bit time and the location of the sample point (see Figure 11-44). Time segment 1 (TSEG1) values are programmable as shown in Table 11-10.                                                                                                                                                                                                                                                                         |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

1. In this case, PHASE\_SEG1 must be at least 2 time quanta (Tq).

Freescale's Scalable Controller Area Network (S12MSCANV3)

#### Pulse-Width Modulator (S12PWM8B8CV1)

with the PWM and their relative offset from the base address. The register detail description follows the order they appear in the register map.

Reserved bits within a register will always read as 0 and the write will be unimplemented. Unimplemented functions are indicated by shading the bit.

#### NOTE

Register Address = Base Address + Address Offset, where the Base Address is defined at the MCU level and the Address Offset is defined at the module level.

### 13.3.2 Register Descriptions

This section describes in detail all the registers and register bits in the PWM module.

| Register<br>Name     |        | Bit 7                       | 6      | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |

|----------------------|--------|-----------------------------|--------|-------|-------|-------|-------|-------|-------|--|

| 0x0000<br>PWME       | R<br>W | PWME7                       | PWME6  | PWME5 | PWME4 | PWME3 | PWME2 | PWME1 | PWME0 |  |

| 0x0001<br>PWMPOL     | R<br>W | PPOL7                       | PPOL6  | PPOL5 | PPOL4 | PPOL3 | PPOL2 | PPOL1 | PPOL0 |  |

| 0x0002<br>PWMCLK     | R<br>W | PCLK7                       | PCLKL6 | PCLK5 | PCLK4 | PCLK3 | PCLK2 | PCLK1 | PCLK0 |  |

| 0x0003<br>PWMPRCLK   | R<br>W | 0                           | PCKB2  | PCKB1 | PCKB0 | 0     | PCKA2 | PCKA1 | PCKA0 |  |

| 0x0004<br>PWMCAE     | R<br>W | CAE7                        | CAE6   | CAE5  | CAE4  | CAE3  | CAE2  | CAE1  | CAE0  |  |

| 0x0005<br>PWMCTL     | R<br>W | CON67                       | CON45  | CON23 | CON01 | PSWAI | PFRZ  | 0     | 0     |  |

| 0x0006               | R      | 0                           | 0      | 0     | 0     | 0     | 0     | 0     | 0     |  |

| PWMTST <sup>1</sup>  | W      |                             |        |       |       |       |       |       |       |  |

| 0x0007               | R      | 0                           | 0      | 0     | 0     | 0     | 0     | 0     | 0     |  |

| PWMPRSC <sup>1</sup> | w      |                             |        |       |       |       |       |       |       |  |

| 0x0008<br>PWMSCLA    | R<br>W | Bit 7                       | 6      | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |

| 0x0009<br>PWMSCLB    | R<br>W | Bit 7                       | 6      | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |

|                      |        | = Unimplemented or Reserved |        |       |       |       |       |       |       |  |

Figure 13-2. PWM Register Summary (Sheet 1 of 3)

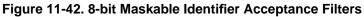

### 14.3.2.8 SCI Status Register 2 (SCISR2)

Read: Anytime

Write: Anytime

#### Table 14-12. SCISR2 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>AMAP  | Alternative Map — This bit controls which registers sharing the same address space are accessible. In the reset condition the SCI behaves as previous versions. Setting AMAP=1 allows the access to another set of control and status registers and hides the baud rate and SCI control Register 1.<br>0 The registers labelled SCIBDH (0x0000),SCIBDL (0x0001), SCICR1 (0x0002) are accessible<br>1 The registers labelled SCIASR1 (0x0000),SCIACR1 (0x0001), SCIACR2 (0x00002) are accessible                                                                              |

| 4<br>TXPOL | <ul> <li>Transmit Polarity — This bit control the polarity of the transmitted data. In NRZ format, a one is represented by a mark and a zero is represented by a space for normal polarity, and the opposite for inverted polarity. In IrDA format, a zero is represented by short high pulse in the middle of a bit time remaining idle low for a one for normal polarity, and a zero is represented by short low pulse in the middle of a bit time remaining idle high for a one for inverted polarity.</li> <li>0 Normal polarity</li> <li>1 Inverted polarity</li> </ul> |

| 3<br>RXPOL | <ul> <li>Receive Polarity — This bit control the polarity of the received data. In NRZ format, a one is represented by a mark and a zero is represented by a space for normal polarity, and the opposite for inverted polarity. In IrDA format, a zero is represented by short high pulse in the middle of a bit time remaining idle low for a one for normal polarity, and a zero is represented by short low pulse in the middle of a bit time remaining idle high for a one for inverted polarity.</li> <li>0 Normal polarity</li> <li>1 Inverted polarity</li> </ul>     |

| 2<br>BRK13 | Break Transmit Character Length — This bit determines whether the transmit break character is 10 or 11 bitrespectively 13 or 14 bits long. The detection of a framing error is not affected by this bit.0 Break character is 10 or 11 bit long1 Break character is 13 or 14 bit long                                                                                                                                                                                                                                                                                         |

| 1<br>TXDIR | <ul> <li>Transmitter Pin Data Direction in Single-Wire Mode — This bit determines whether the TXD pin is going to be used as an input or output, in the single-wire mode of operation. This bit is only relevant in the single-wire mode of operation.</li> <li>0 TXD pin to be used as an input in single-wire mode</li> <li>1 TXD pin to be used as an output in single-wire mode</li> </ul>                                                                                                                                                                               |

| 0<br>RAF   | <ul> <li>Receiver Active Flag — RAF is set when the receiver detects a logic 0 during the RT1 time period of the start bit search. RAF is cleared when the receiver detects an idle character.</li> <li>0 No reception in progress</li> <li>1 Reception in progress</li> </ul>                                                                                                                                                                                                                                                                                               |

P-Flash phrase containing the D-Flash protection byte during the reset sequence, the DPOPEN bit will be cleared and DPS bits will be set to leave the D-Flash memory fully protected.

Trying to alter data in any protected area in the D-Flash memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. Block erase of the D-Flash memory is not possible if any of the D-Flash sectors are protected.

| Field           | Description                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DPOPEN     | <ul> <li>D-Flash Protection Control</li> <li>0 Enables D-Flash memory protection from program and erase with protected address range defined by DPS bits</li> <li>1 Disables D-Flash memory protection from program and erase</li> </ul> |

| 4–0<br>DPS[4:0] | <b>D-Flash Protection Size</b> — The DPS[4:0] bits determine the size of the protected area in the D-Flash memory as shown in Table 18-23.                                                                                               |

#### Table 18-22. DFPROT Field Descriptions

| DPS[4:0] | Global Address Range  | Protected Size |  |  |  |  |  |  |

|----------|-----------------------|----------------|--|--|--|--|--|--|

| 0_000    | 0x10_0000 - 0x10_00FF | 256 bytes      |  |  |  |  |  |  |

| 0_0001   | 0x10_0000 - 0x10_01FF | 512 bytes      |  |  |  |  |  |  |

| 0_0010   | 0x10_0000 - 0x10_02FF | 768 bytes      |  |  |  |  |  |  |

| 0_0011   | 0x10_0000 - 0x10_03FF | 1024 bytes     |  |  |  |  |  |  |

| 0_0100   | 0x10_0000 - 0x10_04FF | 1280 bytes     |  |  |  |  |  |  |

| 0_0101   | 0x10_0000 - 0x10_05FF | 1536 bytes     |  |  |  |  |  |  |

| 0_0110   | 0x10_0000 - 0x10_06FF | 1792 bytes     |  |  |  |  |  |  |

| 0_0111   | 0x10_0000 – 0x10_07FF | 2048 bytes     |  |  |  |  |  |  |

| 0_1000   | 0x10_0000 - 0x10_08FF | 2304 bytes     |  |  |  |  |  |  |

| 0_1001   | 0x10_0000 - 0x10_09FF | 2560 bytes     |  |  |  |  |  |  |

| 0_1010   | 0x10_0000 - 0x10_0AFF | 2816 bytes     |  |  |  |  |  |  |

| 0_1011   | 0x10_0000 - 0x10_0BFF | 3072 bytes     |  |  |  |  |  |  |

| 0_1100   | 0x10_0000 - 0x10_0CFF | 3328 bytes     |  |  |  |  |  |  |

| 0_1101   | 0x10_0000 - 0x10_0DFF | 3584 bytes     |  |  |  |  |  |  |

| 0_1110   | 0x10_0000 - 0x10_0EFF | 3840 bytes     |  |  |  |  |  |  |

| 0_1111   | 0x10_0000 - 0x10_0FFF | 4096 bytes     |  |  |  |  |  |  |

| 1_0000   | 0x10_0000 - 0x10_10FF | 4352 bytes     |  |  |  |  |  |  |

| 1_0001   | 0x10_0000 - 0x10_11FF | 4608 bytes     |  |  |  |  |  |  |

| 1_0010   | 0x10_0000 - 0x10_12FF | 4864 bytes     |  |  |  |  |  |  |

| 1_0011   | 0x10_0000 - 0x10_13FF | 5120 bytes     |  |  |  |  |  |  |

| 1_0100   | 0x10_0000 - 0x10_14FF | 5376 bytes     |  |  |  |  |  |  |

| 1_0101   | 0x10_0000 - 0x10_15FF | 5632 bytes     |  |  |  |  |  |  |

#### Table 18-23. D-Flash Protection Address Range

P-Flash phrase containing the D-Flash protection byte during the reset sequence, the DPOPEN bit will be cleared and DPS bits will be set to leave the D-Flash memory fully protected.

Trying to alter data in any protected area in the D-Flash memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. Block erase of the D-Flash memory is not possible if any of the D-Flash sectors are protected.

| Field           | Description                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DPOPEN     | <ul> <li>D-Flash Protection Control</li> <li>0 Enables D-Flash memory protection from program and erase with protected address range defined by DPS bits</li> <li>1 Disables D-Flash memory protection from program and erase</li> </ul> |

| 4–0<br>DPS[4:0] | <b>D-Flash Protection Size</b> — The DPS[4:0] bits determine the size of the protected area in the D-Flash memory as shown in Table 19-23.                                                                                               |

#### Table 19-22. DFPROT Field Descriptions

| <b>.</b>              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Global Address Range  | Protected Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 0x10_0000 - 0x10_00FF | 256 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 0x10_0000 - 0x10_01FF | 512 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 0x10_0000 - 0x10_02FF | 768 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 0x10_0000 – 0x10_03FF | 1024 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_04FF | 1280 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 – 0x10_05FF | 1536 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 – 0x10_06FF | 1792 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 – 0x10_07FF | 2048 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_08FF | 2304 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 – 0x10_09FF | 2560 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_0AFF | 2816 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_0BFF | 3072 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_0CFF | 3328 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_0DFF | 3584 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_0EFF | 3840 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_0FFF | 4096 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_10FF | 4352 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_11FF | 4608 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_12FF | 4864 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_13FF | 5120 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_14FF | 5376 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 0x10_0000 - 0x10_15FF | 5632 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                       | 0x10_0000 - 0x10_00FF           0x10_0000 - 0x10_01FF           0x10_0000 - 0x10_02FF           0x10_0000 - 0x10_03FF           0x10_0000 - 0x10_03FF           0x10_0000 - 0x10_04FF           0x10_0000 - 0x10_05FF           0x10_0000 - 0x10_06FF           0x10_0000 - 0x10_07FF           0x10_0000 - 0x10_17FF           0x10_0000 - 0x10_13FF           0x10_0000 - 0x10_13FF           0x10_0000 - 0x10_14FF |  |  |  |  |  |  |

#### Table 19-23. D-Flash Protection Address Range

phrase index values for the Read Once command range from 0x0000 to 0x0007. During execution of the Read Once command, any attempt to read addresses within P-Flash block will return invalid data.

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                             |

|          | ACCERR    | Set if command not available in current mode (see Table 19-28)          |

| FSTAT    |           | Set if an invalid phrase index is supplied                              |

| FSTAI    | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

Table 19-38. Read Once Command Error Handling

### 19.4.2.5 Program P-Flash Command

The Program P-Flash operation will program a previously erased phrase in the P-Flash memory using an embedded algorithm.

#### CAUTION

A P-Flash phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash phrase is not allowed.

| CCOBIX[2:0] | FCCOB Parameters                                                       |  |  |  |  |

|-------------|------------------------------------------------------------------------|--|--|--|--|

| 000         | 0x06 Global address [22:16] to<br>identify P-Flash block               |  |  |  |  |

| 001         | Global address [15:0] of phrase location to be programmed <sup>1</sup> |  |  |  |  |

| 010         | Word 0 program value                                                   |  |  |  |  |

| 011         | Word 1 program value                                                   |  |  |  |  |

| 100         | Word 2 program value                                                   |  |  |  |  |

| 101         | Word 3 program value                                                   |  |  |  |  |

Table 19-39. Program P-Flash Command FCCOB Requirements

<sup>1</sup> Global address [2:0] must be 000

Upon clearing CCIF to launch the Program P-Flash command, the Memory Controller will program the data words to the supplied global address and will then proceed to verify the data words read back as expected. The CCIF flag will set after the Program P-Flash operation has completed.

keys stored in the Flash memory via the Memory Controller. If the keys presented in the Verify Backdoor Access Key command match the backdoor keys stored in the Flash memory, the SEC bits in the FSEC register (see Table 19-10) will be changed to unsecure the MCU. Key values of 0x0000 and 0xFFFF are not permitted as backdoor keys. While the Verify Backdoor Access Key command is active, P-Flash block 0 will not be available for read access and will return invalid data.

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 19.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 19.4.2.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired.

In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses  $0x7F_F00-0x7F_FF07$  in the Flash configuration field.

The security as defined in the Flash security byte (0x7F\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x7F\_FF00-0x7F\_FF07 are unaffected by the Verify Backdoor Access Key command sequence. After the next reset of the MCU, the security state of the Flash module is determined by the Flash security byte (0x7F\_FF0F). The Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

# 19.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

The MCU can be unsecured in special single chip mode by erasing the P-Flash and D-Flash memory by one of the following methods:

- Reset the MCU into special single chip mode, delay while the erase test is performed by the BDM, send BDM commands to disable protection in the P-Flash and D-Flash memory, and execute the Erase All Blocks command write sequence to erase the P-Flash and D-Flash memory.

- Reset the MCU into special expanded wide mode, disable protection in the P-Flash and D-Flash memory and run code from external memory to execute the Erase All Blocks command write sequence to erase the P-Flash and D-Flash memory.

After the CCIF flag sets to indicate that the Erase All Blocks operation has completed, reset the MCU into special single chip mode. The BDM will execute the Erase Verify All Blocks command write sequence to verify that the P-Flash and D-Flash memory is erased. If the P-Flash and D-Flash memory are verified as

### 64 KByte Flash Module (S12XFTMR64K1V1)

### CAUTION