#### NXP USA Inc. - S9S12XS256J0MAER Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                   |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, SCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 44                                                                       |

| Program Memory Size        | 256КВ (256К х 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 12K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                             |

| Data Converters            | A/D 8x12b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs256j0maer |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 17.2.3 VDD, VSS — Regulator Output1 (Core Logic) Pins                             |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | 17.2.4 VDDF — Regulator Output2 (NVM Logic) Pins                                  |     |

|      | 17.2.5 VDDPLL, VSSPLL — Regulator Output3 (PLL) Pins                              |     |

|      | 17.2.6 VDDX — Power Input Pin                                                     |     |

|      | 17.2.7 V <sub>REGEN</sub> — Optional Regulator Enable Pin                         |     |

|      | 17.2.8 V <sub>REG API</sub> — Optional Autonomous Periodical Interrupt Output Pin |     |

| 17.3 | Memory Map and Register Definition                                                |     |

|      | 17.3.1 Module Memory Map                                                          |     |

|      | 17.3.2 Register Descriptions                                                      |     |

| 17.4 | Functional Description                                                            | 502 |

|      | 17.4.1 General                                                                    | 502 |

|      | 17.4.2 Regulator Core (REG)                                                       | 502 |

|      | 17.4.3 Low-Voltage Detect (LVD)                                                   | 502 |

|      | 17.4.4 Power-On Reset (POR)                                                       | 502 |

|      | 17.4.5 Low-Voltage Reset (LVR)                                                    | 502 |

|      | 17.4.6 HTD - High Temperature Detect                                              | 503 |

|      | 17.4.7 Regulator Control (CTRL)                                                   | 503 |

|      | 17.4.8 Autonomous Periodical Interrupt (API)                                      | 503 |

|      | 17.4.9 Resets                                                                     | 504 |

|      | 17.4.10Description of Reset Operation                                             | 504 |

|      | 17.4.11Interrupts                                                                 | 504 |

|      |                                                                                   |     |

## Chapter 18 256 KByte Flash Module (S12XFTMR256K1V1)

| 18.1 | ntroduction                                                     |   |

|------|-----------------------------------------------------------------|---|

|      | 18.1.1 Glossary                                                 | 8 |

|      | 18.1.2 Features                                                 | 8 |

|      | 18.1.3 Block Diagram                                            | 9 |

| 18.2 | External Signal Description                                     | 0 |

| 18.3 | Aemory Map and Registers                                        | 0 |

|      | 18.3.1 Module Memory Map                                        | 1 |

|      | 18.3.2 Register Descriptions                                    | 4 |

| 18.4 | Functional Description                                          | 5 |

|      | 18.4.1 Flash Command Operations                                 | 5 |

|      | 18.4.2 Flash Command Description                                | 0 |

|      | 18.4.3 Interrupts                                               | 3 |

|      | 18.4.4 Wait Mode                                                | 4 |

|      | 18.4.5 Stop Mode                                                | 4 |

| 18.5 | lecurity                                                        | 4 |

|      | 18.5.1 Unsecuring the MCU using Backdoor Key Access             | 4 |

|      | 18.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM | 5 |

|      | 18.5.3 Mode and Security Effects on Flash Command Availability  | 6 |

| 18.6 | nitialization                                                   | 6 |

## **1.2 Signal Description**

This section describes signals that connect off-chip. It includes a pinout diagram, a table of signal properties, and detailed discussion of signals. It is built from the signal description sections of the individual IP blocks on the device.

## 1.2.1 Device Pinout

The XS family of devices offers pin-compatible packaged devices to assist with system development and accommodate expansion of the application.

The S12XS family devices are offered in the following package options:

- 112-pin LQFP

- 80-pin QFP

- 64-pin LQFP

## **1.7 ATD0 Configuration**

## 1.7.1 External Trigger Input Connection

The ATD module includes four external trigger inputs ETRIG0, ETRIG1, ETRIG2, and ETRIG3. The external trigger allows the user to synchronize ATD conversion to external trigger events. Table 1-13 shows the connection of the external trigger inputs.

| External Trigger<br>Input | Connectivity                                |

|---------------------------|---------------------------------------------|

| ETRIG0                    | Pulse width modulator channel 1             |

| ETRIG1                    | Pulse width modulator channel 3             |

| ETRIG2                    | Periodic interrupt timer hardware trigger 0 |

| ETRIG3                    | Periodic interrupt timer hardware trigger 1 |

Table 1-13. ATD0 External Trigger Sources

Consult the ATD section for information about the analog-to-digital converter module. References to freeze mode are equivalent to active BDM mode.

## 1.7.2 ATD0 Channel[17] Connection

Further to the 16 externally available channels, ATD0 features an extra channel[17] that is connected to the internal temperature sensor at device level. To access this channel ATD0 must use the channel encoding SC:CD:CC:CB:CA = 1:0:0:0:1 in ATDCTL5. For more temperature sensor information, please refer to 1.8.1 Temperature Sensor Configuration.

## 1.8 VREG Configuration

The device must be configured with the internal voltage regulator enabled. Operation in conjunction with an external voltage regulator is not supported.

The API trimming register APITR is loaded from the Flash IFR option field at global address 0x40\_00F0 bits[5:0] during the reset sequence. Currently factory programming of this IFR range is not supported.

Read access to reserved VREG register space returns "0". Write accesses have no effect. This device does not support access abort of reserved VREG register space.

## **1.8.1** Temperature Sensor Configuration

The VREG high temperature trimming register bits VREGHTTR[3:0] are loaded from the internal Flash during the reset sequence. To use the high temperature interrupt within the specified limits ( $T_{HTIA}$  and  $T_{HTID}$ ) these bits must be loaded with 0x8. Currently factory programming is not supported.

The device temperature can be monitored on ATD0 channel[17]. The internal bandgap reference voltage can also be mapped to ATD0 analog input channel[17]. The voltage regulator VSEL bit when set, maps the bandgap and, when clear, maps the temperature sensor to ATD0 channel[17].

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>RDPB | <ul> <li>Port B reduced drive—Select reduced drive for output port</li> <li>This bit configures the drive strength of all associated port output pins as either full or reduced. If a pin is used as input this bit has no effect. The reduced drive function is independent of which function is being used on a particular pin.</li> <li>1 Reduced drive selected (approx. 1/5 of the full drive strength)</li> </ul> |

| 0<br>RDPA | <ul> <li>0 Full drive strength enabled</li> <li>Port A reduced drive—Select reduced drive for output port</li> <li>This bit configures the drive strength of all associated port output pins as either full or reduced. If a pin is used as input this bit has no effect. The reduced drive function is independent of which function is being used on a particular pin.</li> </ul>                                     |

|           | 1 Reduced drive selected (approx. 1/5 of the full drive strength)<br>0 Full drive strength enabled                                                                                                                                                                                                                                                                                                                      |

## 2.3.12 ECLK Control Register (ECLKCTL)

Address 0x001C (PRR)

Access: User read/write<sup>1</sup>

| _                      | 7                      | 6      | 5     | 4     | 3     | 2     | 1     | 0     |

|------------------------|------------------------|--------|-------|-------|-------|-------|-------|-------|

| R<br>W                 | NECLK                  | NCLKX2 | DIV16 | EDIV4 | EDIV3 | EDIV2 | EDIV1 | EDIV0 |

| Reset:                 | Mode<br>Depen-<br>dent | 1      | 0     | 0     | 0     | 0     | 0     | 0     |

| Special<br>single-chip | 0                      | 1      | 0     | 0     | 0     | 0     | 0     | 0     |

| Normal<br>single-chip  | 1                      | 1      | 0     | 0     | 0     | 0     | 0     | 0     |

= Unimplemented or Reserved

#### Figure 2-10. ECLK Control Register (ECLKCTL)

<sup>1</sup> Read: Anytime Write: Anytime

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>PTT   | <b>Port T general purpose input/output data</b> —Data Register, TIM output, routed PWM output, VREG_API output<br>When not used with the alternative function, the associated pin can be used as general purpose I/O. In general<br>purpose output mode the register bit value is driven to the pin.<br>If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered<br>pin input state is read. |

|            | <ul> <li>The TIM output function takes precedence over the routed PWM, VREG_API function and the general purpose I/O function if the related channel is enabled.</li> <li>The routed PWM function takes precedence over VREG_API and the general purpose I/O function if the related channel is enabled.</li> <li>The VREG_API takes precedence over the general purpose I/O function if enabled.</li> </ul>                                                    |

| 3-0<br>PTT | Port T general purpose input/output data—Data Register, TIM output<br>When not used with the alternative function, the associated pin can be used as general purpose I/O. In general<br>purpose output mode the register bit value is driven to the pin.<br>If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered<br>pin input state is read.                                             |

|            | • The TIM output function takes precedence over the general purpose I/O function if the related channel is enabled.                                                                                                                                                                                                                                                                                                                                             |

#### Table 2-16. PTT Register Field Descriptions (continued)

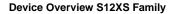

## 2.3.19 Port T Input Register (PTIT)

#### Figure 2-17. Port T Input Register (PTIT)

<sup>1</sup> Read: Anytime

Write:Never, writes to this register have no effect

#### Table 2-17. PTIT Register Field Descriptions

| Field | Description                                                                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0   | Port T input data—                                                                                                                                  |

| PTIT  | A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

#### unimplemented bus, thus preventing proper operation.

The DBGC1\_COMRV bits determine which comparator control, address, data and datamask registers are visible in the 8-byte window from 0x0028 to 0x002F as shown in Section Table 6-26.

#### Table 6-26. Comparator Address Register Visibility

| COMRV | Visible Comparator                                                |

|-------|-------------------------------------------------------------------|

| 00    | DBGACTL, DBGAAH ,DBGAAM, DBGAAL, DBGADH, DBGADL, DBGADHM, DBGADLM |

| 01    | DBGBCTL, DBGBAH, DBGBAM, DBGBAL                                   |

| 10    | DBGCCTL, DBGCAH, DBGCAM, DBGCAL, DBGCDH, DBGCDL, DBGCDHM, DBGCDLM |

| 11    | DBGDCTL, DBGDAH, DBGDAM, DBGDAL                                   |

#### Table 6-27. DBGXCTL Field Descriptions

| Field                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SZE<br>(Comparators<br>B and D) | <ul> <li>Size Comparator Enable Bit — The SZE bit controls whether access size comparison is enabled for the associated comparator. This bit is ignored if the TAG bit in the same register is set.</li> <li>0 Word/Byte access size is not used in comparison</li> <li>1 Word/Byte access size is used in comparison</li> </ul>                                                                                                                                                                                                                                                                                                      |

| 6<br>NDB<br>(Comparators<br>A and C  | <ul> <li>Not Data Bus — The NDB bit controls whether the match occurs when the data bus matches the comparator register value or when the data bus differs from the register value. Furthermore data bus bits can be individually masked using the comparator data mask registers. This bit is only available for comparators A and C. This bit is ignored if the TAG bit in the same register is set. This bit position has an SZ functionality for comparators B and D.</li> <li>0 Match on data bus equivalence to comparator register contents</li> <li>1 Match on data bus difference to comparator register contents</li> </ul> |

| 6<br>SZ<br>(Comparators<br>B and D)  | Size Comparator Value Bit — The SZ bit selects either word or byte access size in comparison for the associated comparator. This bit is ignored if the SZE bit is cleared or if the TAG bit in the same register is set. This bit position has NDB functionality for comparators A and C<br>0 Word access size will be compared<br>1 Byte access size will be compared                                                                                                                                                                                                                                                                |

| 5<br>TAG                             | <ul> <li>Tag Select — This bit controls whether the comparator match will cause a trigger or tag the opcode at the matched address. Tagged opcodes trigger only if they reach the execution stage of the instruction queue.</li> <li>0 Trigger immediately on match</li> <li>1 On match, tag the opcode. If the opcode is about to be executed a trigger is generated</li> </ul>                                                                                                                                                                                                                                                      |

| 4<br>BRK                             | <ul> <li>Break — This bit controls whether a channel match terminates a debug session immediately, independent of state sequencer state. To generate an immediate breakpoint the module breakpoints must be enabled using DBGBRK.</li> <li>0 The debug session termination is dependent upon the state sequencer and trigger conditions.</li> <li>1 A match on this channel terminates the debug session immediately; breakpoints if active are generated, tracing, if active, is terminated and the module disarmed.</li> </ul>                                                                                                      |

| 3<br>RW                              | <ul> <li>Read/Write Comparator Value Bit — The RW bit controls whether read or write is used in compare for the associated comparator. The RW bit is not used if RWE = 0.</li> <li>0 Write cycle will be matched</li> <li>1 Read cycle will be matched</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |

| 2<br>RWE                             | <ul> <li>Read/Write Enable Bit — The RWE bit controls whether read or write comparison is enabled for the associated comparator. This bit is not used for tagged operations.</li> <li>0 Read/Write is not used in comparison</li> <li>1 Read/Write is used in comparison</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |

| Field    | Description                                                                                                                                                                                                                                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>CRW | <ul> <li>Read Write Indicator — This bit indicates if the corresponding stored address corresponds to a read or write access. This bit only contains valid information when tracing CPU12X activity in Detail Mode.</li> <li>0 Write Access</li> <li>1 Read Access</li> </ul> |

## 6.4.5.4 Reading Data from Trace Buffer

The data stored in the Trace Buffer can be read using either the background debug module (BDM) module or the CPU12X provided the S12XDBG module is not armed, is configured for tracing and the system not secured. When the ARM bit is written to 1 the trace buffer is locked to prevent reading. The trace buffer can only be unlocked for reading by an aligned word write to DBGTB when the module is disarmed.

The Trace Buffer can only be read through the DBGTB register using aligned word reads, any byte or misaligned reads return 0 and do not cause the trace buffer pointer to increment to the next trace buffer address. The Trace Buffer data is read out first-in first-out. By reading CNT in DBGCNT the number of valid 64-bit lines can be determined. DBGCNT will not decrement as data is read.

Whilst reading an internal pointer is used to determine the next line to be read. After a tracing session, the pointer points to the oldest data entry, thus if no overflow has occurred, the pointer points to line0, otherwise it points to the line with the oldest entry. The pointer is initialized by each aligned write to DBGTBH to point to the oldest data again. This enables an interrupted trace buffer read sequence to be easily restarted from the oldest data entry.

The least significant word of each 64-bit wide array line is read out first. This corresponds to the bytes 1 and 0 of Table 6-40. The bytes containing invalid information (shaded in Table 6-40) are also read out.

Reading the Trace Buffer while the S12XDBG module is armed will return invalid data and no shifting of the RAM pointer will occur.

## 6.4.5.5 Trace Buffer Reset State

The Trace Buffer contents are not initialized by a system reset. Thus should a system reset occur, the trace session information from immediately before the reset occurred can be read out. The DBGCNT bits are not cleared by a system reset. Thus should a reset occur, the number of valid lines in the trace buffer is indicated by DBGCNT. The internal pointer to the current trace buffer address is initialized by unlocking the trace buffer thus points to the oldest valid data even if a reset occurred during the tracing session. Generally debugging occurrences of system resets is best handled using mid or end trigger alignment since the reset may occur before the trace trigger, which in the begin trigger alignment case means no information would be stored in the trace buffer.

#### NOTE

An external pin RESET that occurs simultaneous to a trace buffer entry can, in very seldom cases, lead to either that entry being corrupted or the first entry of the session being corrupted. In such cases the other contents of the trace buffer still contain valid tracing information. The case occurs when the reset assertion coincides with the trace buffer entry clock edge.

## NOTE

The CANTBSEL register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK=1). This register is writable when not in initialization mode (INITRQ = 0 and INITAK = 0).

#### Table 11-17. CANTBSEL Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2-0<br>TX[2:0] | <ul> <li>Transmit Buffer Select — The lowest numbered bit places the respective transmit buffer in the CANTXFG register space (e.g., TX1 = 1 and TX0 = 1 selects transmit buffer TX0; TX1 = 1 and TX0 = 0 selects transmit buffer TX1). Read and write accesses to the selected transmit buffer will be blocked, if the corresponding TXEx bit is cleared and the buffer is scheduled for transmission (see Section 11.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)").</li> <li>0 The associated message buffer is deselected</li> <li>1 The associated message buffer is selected, if lowest numbered bit</li> </ul> |  |  |  |

The following gives a short programming example of the usage of the CANTBSEL register:

To get the next available transmit buffer, application software must read the CANTFLG register and write this value back into the CANTBSEL register. In this example Tx buffers TX1 and TX2 are available. The value read from CANTFLG is therefore 0b0000\_0110. When writing this value back to CANTBSEL, the Tx buffer TX1 is selected in the CANTXFG because the lowest numbered bit set to 1 is at bit position 1. Reading back this value out of CANTBSEL results in 0b0000\_0010, because only the lowest numbered bit position set to 1 is presented. This mechanism eases the application software's selection of the next available Tx buffer.

- LDAA CANTFLG; value read is 0b0000\_0110

- STAA CANTBSEL; value written is 0b0000\_0110

- LDAA CANTBSEL; value read is 0b0000\_0010

If all transmit message buffers are deselected, no accesses are allowed to the CANTXFG registers.

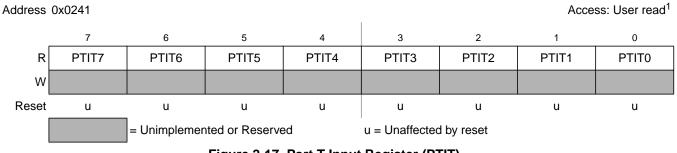

## 11.3.2.12 MSCAN Identifier Acceptance Control Register (CANIDAC)

The CANIDAC register is used for identifier acceptance control as described below.

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1), except bits IDHITx, which are read-only

### 11.4.7.3 Receive Interrupt

A message is successfully received and shifted into the foreground buffer (RxFG) of the receiver FIFO. This interrupt is generated immediately after receiving the EOF symbol. The RXF flag is set. If there are multiple messages in the receiver FIFO, the RXF flag is set as soon as the next message is shifted to the foreground buffer.

### 11.4.7.4 Wake-Up Interrupt

A wake-up interrupt is generated if activity on the CAN bus occurs during MSCAN sleep or power-down mode.

#### NOTE

This interrupt can only occur if the MSCAN was in sleep mode (SLPRQ = 1 and SLPAK = 1) before entering power down mode, the wake-up option is enabled (WUPE = 1), and the wake-up interrupt is enabled (WUPIE = 1).

#### 11.4.7.5 Error Interrupt

An error interrupt is generated if an overrun of the receiver FIFO, error, warning, or bus-off condition occurrs. MSCAN Receiver Flag Register (CANRFLG) indicates one of the following conditions:

- **Overrun** An overrun condition of the receiver FIFO as described in Section 11.4.2.3, "Receive Structures," occurred.

- CAN Status Change The actual value of the transmit and receive error counters control the CAN bus state of the MSCAN. As soon as the error counters skip into a critical range (Tx/Rx-warning, Tx/Rx-error, bus-off) the MSCAN flags an error condition. The status change, which caused the error condition, is indicated by the TSTAT and RSTAT flags (see Section 11.3.2.5, "MSCAN Receiver Flag Register (CANRFLG)" and Section 11.3.2.6, "MSCAN Receiver Interrupt Enable Register (CANRIER)").

#### 11.4.7.6 Interrupt Acknowledge

Interrupts are directly associated with one or more status flags in either the MSCAN Receiver Flag Register (CANRFLG) or the MSCAN Transmitter Flag Register (CANTFLG). Interrupts are pending as long as one of the corresponding flags is set. The flags in CANRFLG and CANTFLG must be reset within the interrupt handler to handshake the interrupt. The flags are reset by writing a 1 to the corresponding bit position. A flag cannot be cleared if the respective condition prevails.

#### NOTE

It must be guaranteed that the CPU clears only the bit causing the current interrupt. For this reason, bit manipulation instructions (BSET) must not be used to clear interrupt flags. These instructions may cause accidental clearing of interrupt flags which are set after entering the current interrupt service routine.

| Table 15-4 | . SPICR2 Field | Descriptions |

|------------|----------------|--------------|

|------------|----------------|--------------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>XFRW    | <b>Transfer Width</b> — This bit is used for selecting the data transfer width. If 8-bit transfer width is selected, SPIDRL becomes the dedicated data register and SPIDRH is unused. If 16-bit transfer width is selected, SPIDRH and SPIDRL form a 16-bit data register. Please refer to Section 15.3.2.4, "SPI Status Register (SPISR) for information about transmit/receive data handling and the interrupt flag clearing mechanism. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state. 0 8-bit Transfer Width (n = 8) <sup>1</sup> 1 16-bit Transfer Width (n = 16) <sup>1</sup> |

| 4<br>MODFEN  | <ul> <li>Mode Fault Enable Bit — This bit allows the MODF failure to be detected. If the SPI is in master mode and MODFEN is cleared, then the SS port pin is not used by the SPI. In slave mode, the SS is available only as an input regardless of the value of MODFEN. For an overview on the impact of the MODFEN bit on the SS port pin configuration, refer to Table 15-3. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>O SS port pin is not used by the SPI.</li> <li>1 SS port pin with MODF feature.</li> </ul>                                                |

| 3<br>BIDIROE | <ul> <li>Output Enable in the Bidirectional Mode of Operation — This bit controls the MOSI and MISO output buffer of the SPI, when in bidirectional mode of operation (SPC0 is set). In master mode, this bit controls the output buffer of the MOSI port, in slave mode it controls the output buffer of the MISO port. In master mode, with SPC0 set, a change of this bit will abort a transmission in progress and force the SPI into idle state.</li> <li>Output buffer disabled.</li> <li>Output buffer enabled.</li> </ul>                                                                                                                        |

| 1<br>SPISWAI | <ul> <li>SPI Stop in Wait Mode Bit — This bit is used for power conservation while in wait mode.</li> <li>SPI clock operates normally in wait mode.</li> <li>Stop SPI clock generation when in wait mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0<br>SPC0    | <b>Serial Pin Control Bit 0</b> — This bit enables bidirectional pin configurations as shown in Table 15-5. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### Table 15-5. Bidirectional Pin Configurations

| Pin Mode                 | SPC0 | BIDIROE | MISO                 | MOSI                 |  |  |  |

|--------------------------|------|---------|----------------------|----------------------|--|--|--|

| Master Mode of Operation |      |         |                      |                      |  |  |  |

| Normal                   | 0    | Х       | Master In            | Master Out           |  |  |  |

| Bidirectional            | 1    | 0       | MISO not used by SPI | Master In            |  |  |  |

|                          |      | 1       |                      | Master I/O           |  |  |  |

| Slave Mode of Operation  |      |         |                      |                      |  |  |  |

| Normal                   | 0    | Х       | Slave Out            | Slave In             |  |  |  |

| Bidirectional            | 1    | 0       | Slave In             | MOSI not used by SPI |  |  |  |

|                          |      | 1       | Slave I/O            | ]                    |  |  |  |

In Shutdown Mode an external supply driving VDD/VSS can replace the voltage regulator.

## 17.2.4 VDDF — Regulator Output2 (NVM Logic) Pins

Signals VDDF/VSS are the secondary outputs of VREG\_3V3 that provide the power supply for the NVM logic. These signals are connected to device pins to allow external decoupling capacitors (220 nF, X7R ceramic).

In Shutdown Mode an external supply driving VDDF/VSS can replace the voltage regulator.

## 17.2.5 VDDPLL, VSSPLL — Regulator Output3 (PLL) Pins

Signals VDDPLL/VSSPLL are the secondary outputs of VREG\_3V3 that provide the power supply for the PLL and oscillator. These signals are connected to device pins to allow external decoupling capacitors (100 nF...220 nF, X7R ceramic).

In Shutdown Mode, an external supply driving VDDPLL/VSSPLL can replace the voltage regulator.

## 17.2.6 VDDX — Power Input Pin

Signals VDDX/VSS are monitored by VREG\_3V3 with the LVR feature.

## 17.2.7 VREGEN — Optional Regulator Enable Pin

This optional signal is used to shutdown VREG\_3V3. In that case, VDD/VSS and VDDPLL/VSSPLL must be provided externally. Shutdown mode is entered with VREGEN being low. If VREGEN is high, the VREG\_3V3 is either in Full Performance Mode or in Reduced Power Mode.

For the connectivity of VREGEN, see device specification.

#### NOTE

Switching from FPM or RPM to shutdown of VREG\_3V3 and vice versa is not supported while MCU is powered.

## 17.2.8 VREG\_API — Optional Autonomous Periodical Interrupt Output Pin

This pin provides the signal selected via APIEA if system is set accordingly. See 17.3.2.3, "Autonomous Periodical Interrupt Control Register (VREGAPICL) and 17.4.8, "Autonomous Periodical Interrupt (API) for details.

For the connectivity of VREG\_API, see device specification.

## 17.3 Memory Map and Register Definition

This section provides a detailed description of all registers accessible in VREG\_3V3.

If enabled in the system, the VREG\_3V3 will abort all read and write accesses to reserved registers within it's memory slice. See device level specification for details.

## 17.4.11.1 Low-Voltage Interrupt (LVI)

In FPM, VREG\_3V3 monitors the input voltage  $V_{DDA}$ . Whenever  $V_{DDA}$  drops below level  $V_{LVIA}$ , the status bit LVDS is set to 1. On the other hand, LVDS is reset to 0 when  $V_{DDA}$  rises above level  $V_{LVID}$ . An interrupt, indicated by flag LVIF = 1, is triggered by any change of the status bit LVDS if interrupt enable bit LVIE = 1.

#### NOTE

On entering the Reduced Power Mode, the LVIF is not cleared by the VREG\_3V3.

### 17.4.11.2 HTI - High Temperature Interrupt

In FPM VREG monitors the die temperature  $T_{DIE}$ . Whenever  $T_{DIE}$  exceeds level  $T_{HTIA}$  the status bit HTDS is set to 1. Vice versa, HTDS is reset to 0 when  $T_{DIE}$  get below level  $T_{HTID}$ . An interrupt, indicated by flag HTIF=1, is triggered by any change of the status bit HTDS if interrupt enable bit HTIE=1.

#### NOTE

On entering the Reduced Power Mode the HTIF is not cleared by the VREG.

## 17.4.11.3 Autonomous Periodical Interrupt (API)

As soon as the configured timeout period of the API has elapsed, the APIF bit is set. An interrupt, indicated by flag APIF = 1, is triggered if interrupt enable bit APIE = 1.

CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

The Flash memory may be read as bytes, aligned words, or misaligned words. Read access time is one bus cycle for bytes and aligned words, and two bus cycles for misaligned words. For Flash memory, an erased bit reads 1 and a programmed bit reads 0.

It is not possible to read from a Flash block while any command is executing on that specific Flash block. It is possible to read from a Flash block while a command is executing on a different Flash block.

Both P-Flash and D-Flash memories are implemented with Error Correction Codes (ECC) that can resolve single bit faults and detect double bit faults. For P-Flash memory, the ECC implementation requires that programming be done on an aligned 8 byte basis (a Flash phrase). Since P-Flash memory is always read by phrase, only one single bit fault in the phrase containing the byte or word accessed will be corrected.

## 18.1.1 Glossary

**Command Write Sequence** — An MCU instruction sequence to execute built-in algorithms (including program and erase) on the Flash memory.

**D-Flash Memory** — The D-Flash memory constitutes the nonvolatile memory store for data.

**D-Flash Sector** — The D-Flash sector is the smallest portion of the D-Flash memory that can be erased. The D-Flash sector consists of four 64 byte rows for a total of 256 bytes.

**NVM Command Mode** — An NVM mode using the CPU to setup the FCCOB register to pass parameters required for Flash command execution.

**Phrase** — An aligned group of four 16-bit words within the P-Flash memory. Each phrase includes eight ECC bits for single bit fault correction and double bit fault detection within the phrase.

P-Flash Memory — The P-Flash memory constitutes the main nonvolatile memory store for applications.

**P-Flash Sector** — The P-Flash sector is the smallest portion of the P-Flash memory that can be erased. Each P-Flash sector contains 1024 bytes.

**Program IFR** — Nonvolatile information register located in the P-Flash block that contains the Device ID, Version ID, and the Program Once field. The Program IFR is visible in the global memory map by setting the PGMIFRON bit in the MMCCTL1 register.

## 18.1.2 Features

## 18.1.2.1 P-Flash Features

- 256 Kbytes of P-Flash memory composed of one 256 Kbyte Flash block divided into 256 sectors of 1024 bytes

- Single bit fault correction and double bit fault detection within a 64-bit phrase during read operations

## 18.3.1 Module Memory Map

The S12X architecture places the P-Flash memory between global addresses 0x7C\_0000 and 0x7F\_FFFF as shown in Table 18-2. The P-Flash memory map is shown in Figure 18-2.

| Global Address        | Size<br>(Bytes) | Description                                                               |

|-----------------------|-----------------|---------------------------------------------------------------------------|

| 0x7C_0000 - 0x7F_FFFF | 256 K           | P-Flash Block 0<br>Contains Flash Configuration Field<br>(see Table 18-3) |

Table 18-2. P-Flash Memory Addressing

The FPROT register, described in Section 18.3.2.9, can be set to protect regions in the Flash memory from accidental program or erase. Three separate memory regions, one growing upward from global address 0x7F\_8000 in the Flash memory (called the lower region), one growing downward from global address 0x7F\_FFFF in the Flash memory (called the higher region), and the remaining addresses in the Flash memory, can be activated for protection. The Flash memory addresses covered by these protectable regions are shown in the P-Flash memory map. The higher address region is mainly targeted to hold the boot loader code since it covers the vector space. Default protection settings as well as security information that allows the MCU to restrict access to the Flash module are stored in the Flash configuration field as described in Table 18-3.

| Global Address                       | Size<br>(Bytes) | Description                                                                                                                                                        |

|--------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x7F_FF00 – 0x7F_FF07                | 8               | Backdoor Comparison Key<br>Refer to Section 18.4.2.11, "Verify Backdoor Access Key Command," and<br>Section 18.5.1, "Unsecuring the MCU using Backdoor Key Access" |

| 0x7F_FF08 - 0x7F_FF0B <sup>2</sup> 4 |                 | Reserved                                                                                                                                                           |

| 0x7F_FF0C <sup>2</sup>               | 1               | P-Flash Protection byte.<br>Refer to Section 18.3.2.9, "P-Flash Protection Register (FPROT)"                                                                       |

| 0x7F_FF0D <sup>2</sup>               | 1               | D-Flash Protection byte.<br>Refer to Section 18.3.2.10, "D-Flash Protection Register (DFPROT)"                                                                     |

| 0x7F_FF0E <sup>2</sup>               | 1               | Flash Nonvolatile byte<br>Refer to Section 18.3.2.15, "Flash Option Register (FOPT)"                                                                               |

| 0x7F_FF0F <sup>2</sup>               | 1               | Flash Security byte<br>Refer to Section 18.3.2.2, "Flash Security Register (FSEC)"                                                                                 |

| Table 18-3. Fla | ash Configura | tion Field <sup>1</sup> |

|-----------------|---------------|-------------------------|

|-----------------|---------------|-------------------------|

<sup>1</sup> Older versions may have swapped protection byte addresses

<sup>2</sup> 0x7FF08 - 0x7F\_FF0F form a Flash phrase and must be programmed in a single command write sequence. Each byte in the 0x7F\_FF08 - 0x7F\_FF0B reserved field should be programmed to 0xFF.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 19-28)                      |

|          |           | Set if an invalid global address [22:16] is supplied                                |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 19-48. Erase P-Flash Sector Command Error Handling

### 19.4.2.10 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and D-Flash memory space and, if the erase is successful, will release security.

Table 19-49. Unsecure Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |

|-------------|------------------|--------------|--|

| 000         | 0x0B             | Not required |  |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and D-Flash memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security state. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag is set after the Unsecure Flash operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                         |  |  |

|          |           | Set if command not available in current mode (see Table 19-28)                      |  |  |

| FSTAT    | FPVIOL    | Set if any area of the P-Flash or D-Flash memory is protected                       |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

Table 19-50. Unsecure Flash Command Error Handling

#### 19.4.2.11 Verify Backdoor Access Key Command

The Verify Backdoor Access Key command will only execute if it is enabled by the KEYEN bits in the FSEC register (see Table 19-9). The Verify Backdoor Access Key command releases security if user-supplied keys match those stored in the Flash security bytes of the Flash configuration field (see

64 KByte Flash Module (S12XFTMR64K1V1)

| OSCCLK Frequency<br>(MHz) |                  | FDIV[6:0] |                  | OSCCLK Frequency<br>(MHz) |           |

|---------------------------|------------------|-----------|------------------|---------------------------|-----------|

| MIN <sup>1</sup>          | MAX <sup>2</sup> |           | MIN <sup>1</sup> | MAX <sup>2</sup>          | FDIV[6:0] |

| 1.60                      | 2.10             | 0x01      | 33.60            | 34.65                     | 0x20      |

| 2.40                      | 3.15             | 0x02      | 34.65            | 35.70                     | 0x21      |

| 3.20                      | 4.20             | 0x03      | 35.70            | 36.75                     | 0x22      |

| 4.20                      | 5.25             | 0x04      | 36.75            | 37.80                     | 0x23      |

| 5.25                      | 6.30             | 0x05      | 37.80            | 38.85                     | 0x24      |

| 6.30                      | 7.35             | 0x06      | 38.85            | 39.90                     | 0x25      |

| 7.35                      | 8.40             | 0x07      | 39.90            | 40.95                     | 0x26      |

| 8.40                      | 9.45             | 0x08      | 40.95            | 42.00                     | 0x27      |

| 9.45                      | 10.50            | 0x09      | 42.00            | 43.05                     | 0x28      |

| 10.50                     | 11.55            | 0x0A      | 43.05            | 44.10                     | 0x29      |

| 11.55                     | 12.60            | 0x0B      | 44.10            | 45.15                     | 0x2A      |

| 12.60                     | 13.65            | 0x0C      | 45.15            | 46.20                     | 0x2B      |

| 13.65                     | 14.70            | 0x0D      | 46.20            | 47.25                     | 0x2C      |

| 14.70                     | 15.75            | 0x0E      | 47.25            | 48.30                     | 0x2D      |

| 15.75                     | 16.80            | 0x0F      | 48.30            | 49.35                     | 0x2E      |

| 16.80                     | 17.85            | 0x10      | 49.35            | 50.40                     | 0x2F      |

| 17.85                     | 18.90            | 0x11      |                  |                           |           |

| 18.90                     | 19.95            | 0x12      |                  |                           |           |

| 19.95                     | 21.00            | 0x13      |                  |                           |           |

| 21.00                     | 22.05            | 0x14      |                  |                           |           |

| 22.05                     | 23.10            | 0x15      |                  |                           |           |

| 23.10                     | 24.15            | 0x16      |                  |                           |           |

| 24.15                     | 25.20            | 0x17      |                  |                           |           |

| 25.20                     | 26.25            | 0x18      |                  |                           |           |

| 26.25                     | 27.30            | 0x19      |                  |                           |           |

| 27.30                     | 28.35            | 0x1A      |                  |                           |           |

| 28.35                     | 29.40            | 0x1B      |                  |                           |           |

| 29.40                     | 30.45            | 0x1C      |                  |                           |           |

| 30.45                     | 31.50            | 0x1D      |                  |                           |           |

| 31.50                     | 32.55            | 0x1E      |                  |                           |           |

| 32.55                     | 33.60            | 0x1F      |                  |                           |           |

#### Table 20-7. FDIV vs OSCCLK Frequency

<sup>1</sup> FDIV shown generates an FCLK frequency of >0.8 MHz

<sup>2</sup> FDIV shown generates an FCLK frequency of 1.05 MHz

## 64 KByte Flash Module (S12XFTMR64K1V1)

#### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

| CCOBIX[2:0] | FCCOB Parameters                               |                                                      |  |  |  |  |  |

|-------------|------------------------------------------------|------------------------------------------------------|--|--|--|--|--|

| 000         | 0x11                                           | Global address [22:16] to identify the D-Flash block |  |  |  |  |  |

| 001         | Global address [15:0] of word to be programmed |                                                      |  |  |  |  |  |

| 010         | Word 0 program value                           |                                                      |  |  |  |  |  |

| 011         | Word 1 program value, if desired               |                                                      |  |  |  |  |  |

| 100         | Word 2 program value, if desired               |                                                      |  |  |  |  |  |

| 101         | Word 3 program value, if desired               |                                                      |  |  |  |  |  |

#### Table 20-61. Program D-Flash Command FCCOB Requirements

Upon clearing CCIF to launch the Program D-Flash command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program D-Flash command launch determines how many words will be programmed in the D-Flash block. The CCIF flag is set when the operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|--|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                          |  |  |  |  |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 20-28)                      |  |  |  |  |

|          | ACCERK    | Set if an invalid global address [22:0] is supplied                                 |  |  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |  |  |

|          |           | Set if the requested group of words breaches the end of the D-Flash block           |  |  |  |  |

|          | FPVIOL    | Set if the selected area of the D-Flash memory is protected                         |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |  |

#### Table 20-62. Program D-Flash Command Error Handling

#### 20.4.2.16 Erase D-Flash Sector Command

The Erase D-Flash Sector operation will erase all addresses in a sector of the D-Flash block.

#### Table 20-63. Erase D-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |                                                     |  |  |  |  |

|-------------|------------------|-----------------------------------------------------|--|--|--|--|

| 000         | 0x12             | Global address [22:16] to identify<br>D-Flash block |  |  |  |  |

Package Information

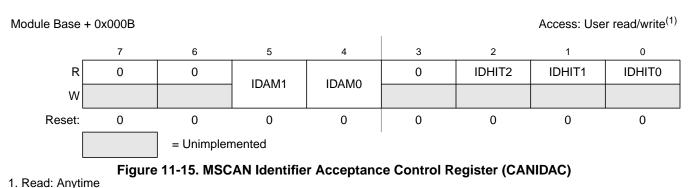

## B.2 80-Pin QFP Mechanical Dimensions

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | Mechanical outline |                                 | PRINT VERSION NOT TO SCALE |  |  |

|---------------------------------------------------------|--------------------|---------------------------------|----------------------------|--|--|

| TITLE:                                                  |                    | DOCUMENT NO: 98ASB42846B REV: C |                            |  |  |

| QUAD FLAT PACKAGE, 8<br>14 X 14 X 2.2 PKG, 0.65 L       | ,                  | CASE NUMBER                     | 20 MAY 2005                |  |  |

| 14 A 14 A 2.2 FKG, 0.03 L                               | ead fiich          | STANDARD: NON-JEDEC             |                            |  |  |

Figure B-4. 80-pin QFP (case no. 841B) - page 1

**PCB Layout Guidelines**

## C.1.3 64-Pin LQFP Recommended PCB Layout

# TBD

Figure C-3. 64-Pin LQFP Recommended PCB Layout (Loop Controlled Pierce Oscillator)

### 0x0300–0x0327 Pulse Width Modulator 8-Bit 8-Channel (PWM) Map

| Address | Name                |        | Bit 7      | Bit 6  | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0      |

|---------|---------------------|--------|------------|--------|--------|-------|--------|--------|--------|------------|

| 0x0300  | PWME                | R<br>W | PWME7      | PWME6  | PWME5  | PWME4 | PWME3  | PWME2  | PWME1  | PWME0      |

| 0x0301  | PWMPOL              | R<br>W | PPOL7      | PPOL6  | PPOL5  | PPOL4 | PPOL3  | PPOL2  | PPOL1  | PPOL0      |

| 0x0302  | PWMCLK              | R<br>W | PCLK7      | PCLK6  | PCLK5  | PCLK4 | PCLK3  | PCLK2  | PCLK1  | PCLK0      |

| 0x0303  | PWMPRCLK            | R<br>W | 0          | PCKB2  | PCKB1  | PCKB0 | 0      | PCKA2  | PCKA1  | PCKA0      |

| 0x0304  | PWMCAE              | R<br>W | CAE7       | CAE6   | CAE5   | CAE4  | CAE3   | CAE2   | CAE1   | CAE0       |

| 0x0305  | PWMCTL              | R<br>W | CON67      | CON45  | CON23  | CON01 | PSWAI  | PFRZ   | 0      | 0          |

| 0x0306  | PWMTST<br>Test Only | R<br>W | 0          | 0      | 0      | 0     | 0      | 0      | 0      | 0          |

| 0x0307  | PWMPRSC             | R<br>W | 0          | 0      | 0      | 0     | 0      | 0      | 0      | 0          |

| 0x0308  | PWMSCLA             | R<br>W | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

| 0x0309  | PWMSCLB             | R<br>W | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

| 0x030A  | PWMSCNTA            | R<br>W | 0          | 0      | 0      | 0     | 0      | 0      | 0      | 0          |

| 0x030B  | PWMSCNTB            | R<br>W | 0          | 0      | 0      | 0     | 0      | 0      | 0      | 0          |

| 0x030C  | PWMCNT0             | R      | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

|         |                     | W      | 0          | 0      | 0      | 0     | 0      | 0      | 0      | 0          |

| 0x030D  | PWMCNT1             | R<br>W | Bit 7<br>0 | 6<br>0 | 5<br>0 | 4     | 3<br>0 | 2<br>0 | 1<br>0 | Bit 0<br>0 |

|         |                     | R      | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

| 0x030E  | PWMCNT2             | W      | 0          | 0      | 0      | 0     | 0      | 0      | 0      | 0          |

| 0.0005  |                     | R      | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

| 0x030F  | PWMCNT3             | W      | 0          | 0      | 0      | 0     | 0      | 0      | 0      | 0          |

| 0x0310  | PWMCNT4             | R      | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

| 0.0310  |                     | W      | 0          | 0      | 0      | 0     | 0      | 0      | 0      | 0          |

| 0x0311  | PWMCNT5             | R      | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

|         |                     | W      | 0          | 0      | 0      | 0     | 0      | 0      | 0      | 0          |

| 0x0312  | PWMCNT6             | R      | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

| 0x0313  | PWMCNT7             | W      |            | 0      | 0      | 0     | 0      | 0      | 0      | 0<br>Dit 0 |

|         |                     | R<br>W | Bit 7<br>0 | 6<br>0 | 5<br>0 | 4     | 0      | 2      | 1<br>0 | Bit 0<br>0 |

| 0x0314  | PWMPER0             | R<br>W | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

| 0x0315  | PWMPER1             | R<br>W | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |

| 0x0316  | PWMPER2             | R<br>W | Bit 7      | 6      | 5      | 4     | 3      | 2      | 1      | Bit 0      |