Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                   |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, SCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 91                                                                       |

| Program Memory Size        | 256КВ (256К х 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 12K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                             |

| Data Converters            | A/D 16x12b                                                               |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 112-LQFP                                                                 |

| Supplier Device Package    | 112-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs256j0malr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 1-6. Pin-Out Summary<sup>1</sup> (continued)

| Packa       | Package Terminal |            |                  |              | Function     |              |              | Power            | Internal Pull<br>Resistor |                | Description                         |

|-------------|------------------|------------|------------------|--------------|--------------|--------------|--------------|------------------|---------------------------|----------------|-------------------------------------|

| LQFP<br>112 | QFP<br>80        | LQFP<br>64 | Pin              | 2nd<br>Func. | 3rd<br>Func. | 4th<br>Func. | 5th<br>Func. | Supply           | CTRL                      | Reset<br>State | Description                         |

| 72          | -                | -          | PAD10            | AN10         |              |              |              | V <sub>DDA</sub> | PER0AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 73          | 54               | 42         | PAD03            | AN03         | _            | _            |              | V <sub>DDA</sub> | PER1AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 74          | -                | -          | PAD11            | AN11         | _            | _            |              | V <sub>DDA</sub> | PER0AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 75          | 55               | 43         | PAD04            | AN04         | _            |              |              | V <sub>DDA</sub> | PER1AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 76          | -                | -          | PAD12            | AN12         | _            |              |              | V <sub>DDA</sub> | PER0AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 77          | 56               | 44         | PAD05            | AN05         | _            |              |              | V <sub>DDA</sub> | PER1AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 78          | -                | -          | PAD13            | AN13         |              |              |              | V <sub>DDA</sub> | PER0AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 79          | 57               | 45         | PAD06            | AN06         | _            |              |              | V <sub>DDA</sub> | PER1AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 80          | -                | -          | PAD14            | AN14         | _            | _            |              | V <sub>DDA</sub> | PER0AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 81          | 58               | 46         | PAD07            | AN07         | _            |              |              | V <sub>DDA</sub> | PER1AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 82          | -                | -          | PAD15            | AN15         | _            |              |              | V <sub>DDA</sub> | PER0AD                    | Disabled       | Port AD I/O,<br>analog input of ATD |

| 83          | 59               | 47         | VDDA             |              |              |              | _            | —                | _                         | _              | _                                   |

| 84          | 60               | 48         | VRH              |              |              |              | _            | —                | _                         | —              | —                                   |

| 85          | 61               | 49         | VRL <sup>3</sup> | _            | _            | _            | _            | —                | _                         | —              | —                                   |

| 86          | 62               | 49         | VSSA             | _            |              | _            |              | _                | _                         | _              | _                                   |

S12XS Family Reference Manual, Rev. 1.13

#### Background Debug Module (S12XBDMV2)

16-bit misaligned reads and writes are generally not allowed. If attempted by BDM hardware command, the BDM will ignore the least significant bit of the address and will assume an even address from the remaining bits.

For devices with external bus:

The following cycle count information is only valid when the external wait function is not used (see wait bit of EBI sub-block). During an external wait the BDM can not steal a cycle. Hence be careful with the external wait function if the BDM serial interface is much faster than the bus, because of the BDM soft-reset after time-out (see Section 5.4.11, "Serial Communication Time Out").

For hardware data read commands, the external host must wait at least 150 bus clock cycles after sending the address before attempting to obtain the read data. This is to be certain that valid data is available in the BDM shift register, ready to be shifted out. For hardware write commands, the external host must wait 150 bus clock cycles after sending the data to be written before attempting to send a new command. This is to avoid disturbing the BDM shift register before the write has been completed. The 150 bus clock cycle delay in both cases includes the maximum 128 cycle delay that can be incurred as the BDM waits for a free cycle before stealing a cycle.

For firmware read commands, the external host should wait at least 48 bus clock cycles after sending the command opcode and before attempting to obtain the read data. This includes the potential of extra cycles when the access is external and stretched (+1 to maximum +7 cycles) or to registers of the PRU (port replacement unit) in emulation modes (if modes available). The 48 cycle wait allows enough time for the requested data to be made available in the BDM shift register, ready to be shifted out.

### NOTE

This timing has increased from previous BDM modules due to the new capability in which the BDM serial interface can potentially run faster than the bus. On previous BDM modules this extra time could be hidden within the serial time.

For firmware write commands, the external host must wait 36 bus clock cycles after sending the data to be written before attempting to send a new command. This is to avoid disturbing the BDM shift register before the write has been completed.

The external host should wait at least for 76 bus clock cycles after a TRACE1 or GO command before starting any new serial command. This is to allow the CPU to exit gracefully from the standard BDM firmware lookup table and resume execution of the user code. Disturbing the BDM shift register prematurely may adversely affect the exit from the standard BDM firmware lookup table.

### NOTE

If the bus rate of the target processor is unknown or could be changing or the external wait function is used, it is recommended that the ACK (acknowledge function) is used to indicate when an operation is complete. When using ACK, the delay times are automated.

Figure 5-7 represents the BDM command structure. The command blocks illustrate a series of eight bit times starting with a falling edge. The bar across the top of the blocks indicates that the BKGD line idles in the high state. The time for an 8-bit command is  $8 \times 16$  target clock cycles.<sup>1</sup>

#### Background Debug Module (S12XBDMV2)

Differently from the normal bit transfer (where the host initiates the transmission), the serial interface ACK handshake pulse is initiated by the target MCU by issuing a negative edge in the BKGD pin. The hardware handshake protocol in Figure 5-11 specifies the timing when the BKGD pin is being driven, so the host should follow this timing constraint in order to avoid the risk of an electrical conflict in the BKGD pin.

### NOTE

The only place the BKGD pin can have an electrical conflict is when one side is driving low and the other side is issuing a speedup pulse (high). Other "highs" are pulled rather than driven. However, at low rates the time of the speedup pulse can become lengthy and so the potential conflict time becomes longer as well.

The ACK handshake protocol does not support nested ACK pulses. If a BDM command is not acknowledge by an ACK pulse, the host needs to abort the pending command first in order to be able to issue a new BDM command. When the CPU enters wait or stop while the host issues a hardware command (e.g., WRITE\_BYTE), the target discards the incoming command due to the wait or stop being detected. Therefore, the command is not acknowledged by the target, which means that the ACK pulse will not be issued in this case. After a certain time the host (not aware of stop or wait) should decide to abort any possible pending ACK pulse in order to be sure a new command can be issued. Therefore, the protocol provides a mechanism in which a command, and its corresponding ACK, can be aborted.

### NOTE

The ACK pulse does not provide a time out. This means for the GO\_UNTIL command that it can not be distinguished if a stop or wait has been executed (command discarded and ACK not issued) or if the "UNTIL" condition (BDM active) is just not reached yet. Hence in any case where the ACK pulse of a command is not issued the possible pending command should be aborted before issuing a new command. See the handshake abort procedure described in Section 5.4.8, "Hardware Handshake Abort Procedure".

## 5.4.8 Hardware Handshake Abort Procedure

The abort procedure is based on the SYNC command. In order to abort a command, which had not issued the corresponding ACK pulse, the host controller should generate a low pulse in the BKGD pin by driving it low for at least 128 serial clock cycles and then driving it high for one serial clock cycle, providing a speedup pulse. By detecting this long low pulse in the BKGD pin, the target executes the SYNC protocol, see Section 5.4.9, "SYNC — Request Timed Reference Pulse", and assumes that the pending command and therefore the related ACK pulse, are being aborted. Therefore, after the SYNC protocol has been completed the host is free to issue new BDM commands. For Firmware READ or WRITE commands it can not be guaranteed that the pending command is aborted when issuing a SYNC before the corresponding ACK pulse. There is a short latency time from the time the READ or WRITE access begins until it is finished and the corresponding ACK pulse is issued. The latency time depends on the firmware READ or WRITE command that is issued and if the serial interface is running on a different clock rate than the bus. When the SYNC command starts during this latency time the READ or WRITE command will not be aborted, but the corresponding ACK pulse will be aborted. A pending GO, TRACE1 or

## 8.3.2 Register Descriptions

This section describes in address order all the S12XECRG registers and their individual bits.

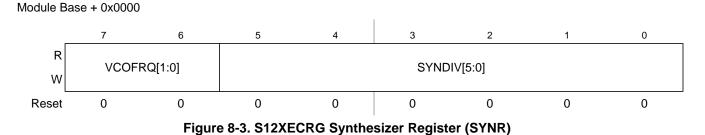

### 8.3.2.1 S12XECRG Synthesizer Register (SYNR)

The SYNR register controls the multiplication factor of the IPLL and selects the VCO frequency range.

Read: Anytime

Write: Anytime except if PLLSEL = 1

#### NOTE

Write to this register initializes the lock detector bit.

$$f_{VCO} = 2 \times f_{OSC} \times \frac{(SYNDIV + 1)}{(REFDIV + 1)}$$

$$f_{PLL} = \frac{f_{VCO}}{2 \times POSTDIV}$$

$$f_{BUS} = \frac{f_{PLL}}{2}$$

#### NOTE

$f_{VCO}$  must be within the specified VCO frequency lock range. F.<sub>BUS</sub> (Bus Clock) must not exceed the specified maximum. If POSTDIV = \$00 then  $f_{PLL}$  is same as  $f_{VCO}$  (divide by one).

The VCOFRQ[1:0] bit are used to configure the VCO gain for optimal stability and lock time. For correct IPLL operation the VCOFRQ[1:0] bits have to be selected according to the actual target VCOCLK frequency as shown in Table 8-2. Setting the VCOFRQ[1:0] bits wrong can result in a non functional IPLL (no locking and/or insufficient stability).

| VCOCLK Frequency Ranges            | VCOFRQ[1:0] |

|------------------------------------|-------------|

| 32MHz <= f <sub>VCO</sub> <= 48MHz | 00          |

| 48MHz < f <sub>VCO</sub> <= 80MHz  | 01          |

| Reserved                           | 10          |

| 80MHz < f <sub>VCO</sub> <= 120MHz | 11          |

Table 8-2. VCO Clock Frequency Selection

| Field       | Description                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTIF   | <ul> <li>Real Time Interrupt Flag — RTIF is set to 1 at the end of the RTI period. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (RTIE=1), RTIF causes an interrupt request.</li> <li>0 RTI time-out has not yet occurred.</li> <li>1 RTI time-out has occurred.</li> </ul>                            |

| 6<br>PORF   | <ul> <li>Power on Reset Flag — PORF is set to 1 when a power on reset occurs. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 Power on reset has not occurred.</li> <li>1 Power on reset has occurred.</li> </ul>                                                                                        |

| 5<br>LVRF   | <ul> <li>Low Voltage Reset Flag — LVRF is set to 1 when a low voltage reset occurs. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 Low voltage reset has not occurred.</li> <li>1 Low voltage reset has occurred.</li> </ul>                                                                            |

| 4<br>LOCKIF | <ul> <li>IPLL Lock Interrupt Flag — LOCKIF is set to 1 when LOCK status bit changes. This flag can only be cleared by writing a 1. Writing a 0 has no effect.If enabled (LOCKIE=1), LOCKIF causes an interrupt request.</li> <li>0 No change in LOCK bit.</li> <li>1 LOCK bit has changed.</li> </ul>                                        |

| 3<br>LOCK   | <ul> <li>Lock Status Bit — LOCK reflects the current state of IPLL lock condition. This bit is cleared in Self Clock Mode.</li> <li>Writes have no effect.</li> <li>VCOCLK is not within the desired tolerance of the target frequency.</li> <li>VCOCLK is within the desired tolerance of the target frequency.</li> </ul>                  |

| 2<br>ILAF   | Illegal Address Reset Flag — ILAF is set to 1 when an illegal address reset occurs. Refer to S12XMMC BlockGuide for details. This flag can only be cleared by writing a 1. Writing a 0 has no effect.0 Illegal address reset has not occurred.1 Illegal address reset has occurred.                                                          |

| 1<br>SCMIF  | <ul> <li>Self Clock Mode Interrupt Flag — SCMIF is set to 1 when SCM status bit changes. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (SCMIE=1), SCMIF causes an interrupt request.</li> <li>0 No change in SCM bit.</li> <li>1 SCM bit has changed.</li> </ul>                                       |

| 0<br>SCM    | <ul> <li>Self Clock Mode Status Bit — SCM reflects the current clocking mode. Writes have no effect.</li> <li>MCU is operating normally with OSCCLK available.</li> <li>MCU is operating in Self Clock Mode with OSCCLK in an unknown state. All clocks are derived from PLLCLK running at its minimum frequency f<sub>SCM</sub>.</li> </ul> |

#### Table 8-4. CRGFLG Field Descriptions

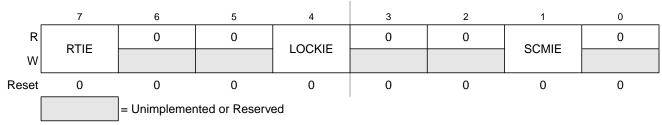

## 8.3.2.5 S12XECRG Interrupt Enable Register (CRGINT)

This register enables S12XECRG interrupt requests.

Module Base + 0x0004

### Figure 8-7. S12XECRG Interrupt Enable Register (CRGINT)

S12XS Family Reference Manual, Rev. 1.13

## Chapter 12 Periodic Interrupt Timer (S12PIT24B4CV1)

Table 12-1. Revision History

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                       |

|-------------------|------------------|-------------------|--------|----------------------------------------------|

| 01.00             | 28-Apr-05        | 28-Apr-05         |        | Initial Release                              |

| 01.01             | 05-Jul-05        | 05-Jul-05         |        | Added application section, removed table 1-1 |

## 12.1 Introduction

The period interrupt timer (PIT) is an array of 24-bit timers that can be used to trigger peripheral modules or raise periodic interrupts. Refer to Figure 12-1 for a simplified block diagram.

## 12.1.1 Glossary

| Acronyms and Abbreviations |                                                                                                                  |  |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIT                        | Periodic Interrupt Timer                                                                                         |  |  |  |  |

| ISR                        | Interrupt Service Routine                                                                                        |  |  |  |  |

| CCR                        | Condition Code Register                                                                                          |  |  |  |  |

| SoC                        | System on Chip                                                                                                   |  |  |  |  |

| micro time bases           | clock periods of the 16-bit timer modulus down-counters, which are generated by the 8-bit modulus down-counters. |  |  |  |  |

## 12.1.2 Features

The PIT includes these features:

- Four timers implemented as modulus down-counters with independent time-out periods.

- Time-out periods selectable between 1 and  $2^{24}$  bus clock cycles. Time-out equals m\*n bus clock cycles with 1 <= m <= 256 and 1 <= n <= 65536.

- Timers that can be enabled individually.

- Four time-out interrupts.

- Four time-out trigger output signals available to trigger peripheral modules.

- Start of timer channels can be aligned to each other.

## 12.1.3 Modes of Operation

Refer to the SoC guide for a detailed explanation of the chip modes.

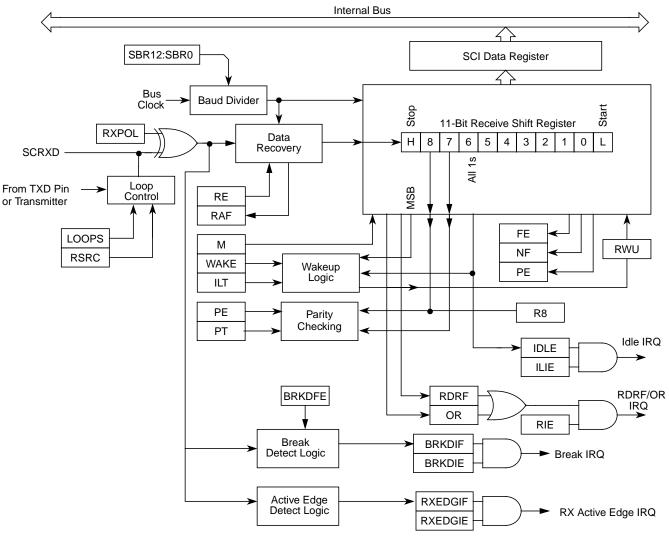

## 14.4.6 Receiver

Figure 14-20. SCI Receiver Block Diagram

## 14.4.6.1 Receiver Character Length

The SCI receiver can accommodate either 8-bit or 9-bit data characters. The state of the M bit in SCI control register 1 (SCICR1) determines the length of data characters. When receiving 9-bit data, bit R8 in SCI data register high (SCIDRH) is the ninth bit (bit 8).

## 14.4.6.2 Character Reception

During an SCI reception, the receive shift register shifts a frame in from the RXD pin. The SCI data register is the read-only buffer between the internal data bus and the receive shift register.

After a complete frame shifts into the receive shift register, the data portion of the frame transfers to the SCI data register. The receive data register full flag, RDRF, in SCI status register 1 (SCISR1) becomes set,

Serial Peripheral Interface (S12SPIV5)

## 15.3.2.5 SPI Data Register (SPIDR = SPIDRH:SPIDRL)

Module Base +0x0004

|       | 7                                           | 6   | 5   | 4   | 3   | 2   | 1  | 0  |  |  |

|-------|---------------------------------------------|-----|-----|-----|-----|-----|----|----|--|--|

| R     | R15                                         | R14 | R13 | R12 | R11 | R10 | R9 | R8 |  |  |

| w     | T15                                         | T14 | T13 | T12 | T11 | T10 | Т9 | Т8 |  |  |

| Reset | 0                                           | 0   | 0   | 0   | 0   | 0   | 0  | 0  |  |  |

|       | Figure 15.7 SPI Data Bagistar High (SPIDPH) |     |     |     |     |     |    |    |  |  |

Figure 15-7. SPI Data Register High (SPIDRH)

Module Base +0x0005

|       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|----|----|

| R     | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| W     | T7 | T6 | T5 | T4 | Т3 | T2 | T1 | T0 |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Figure 15-8. SPI Data Register Low (SPIDRL)

Read: Anytime; read data only valid when SPIF is set

Write: Anytime

The SPI data register is both the input and output register for SPI data. A write to this register allows data to be queued and transmitted. For an SPI configured as a master, queued data is transmitted immediately after the previous transmission has completed. The SPI transmitter empty flag SPTEF in the SPISR register indicates when the SPI data register is ready to accept new data.

Received data in the SPIDR is valid when SPIF is set.

If SPIF is cleared and data has been received, the received data is transferred from the receive shift register to the SPIDR and SPIF is set.

If SPIF is set and not serviced, and a second data value has been received, the second received data is kept as valid data in the receive shift register until the start of another transmission. The data in the SPIDR does not change.

If SPIF is set and valid data is in the receive shift register, and SPIF is serviced before the start of a third transmission, the data in the receive shift register is transferred into the SPIDR and SPIF remains set (see Figure 15-9).

If SPIF is set and valid data is in the receive shift register, and SPIF is serviced after the start of a third transmission, the data in the receive shift register has become invalid and is not transferred into the SPIDR (see Figure 15-10).

## 16.3.2.15 16-Bit Pulse Accumulator Control Register (PACTL)

Module Base + 0x0020

|       | 7                         | 6    | 5     | 4     | 3      | 2      | 1                | 0   |

|-------|---------------------------|------|-------|-------|--------|--------|------------------|-----|

| R     | 0                         |      | DAMOD | DEDOE | 01.144 | 01.140 | <b>DA O</b> ) // | DAL |

| W     |                           | PAEN | PAMOD | PEDGE | CLK1   | CLK0   | PAOVI            | PAI |

| Reset | 0                         | 0    | 0     | 0     | 0      | 0      | 0                | 0   |

|       | Unimplemented or Reserved |      |       |       |        |        |                  |     |

#### Figure 16-24. 16-Bit Pulse Accumulator Control Register (PACTL)

When PAEN is set, the PACT is enabled. The PACT shares the input pin with IOC7.

Read: Any time

Write: Any time

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>PAEN       | <ul> <li>Pulse Accumulator System Enable — PAEN is independent from TEN. With timer disabled, the pulse accumulator can function unless pulse accumulator is disabled.</li> <li>0 16-Bit Pulse Accumulator system disabled.</li> <li>1 Pulse Accumulator system enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5<br>PAMOD      | <ul> <li>Pulse Accumulator Mode — This bit is active only when the Pulse Accumulator is enabled (PAEN = 1). See Table 16-19.</li> <li>0 Event counter mode.</li> <li>1 Gated time accumulation mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4<br>PEDGE      | <ul> <li>Pulse Accumulator Edge Control — This bit is active only when the Pulse Accumulator is enabled (PAEN = 1). For PAMOD bit = 0 (event counter mode). See Table 16-19.</li> <li>0 Falling edges on IOC7 pin cause the count to be incremented.</li> <li>1 Rising edges on IOC7 pin cause the count to be incremented.</li> <li>For PAMOD bit = 1 (gated time accumulation mode).</li> <li>0 IOC7 input pin high enables M (bus clock) divided by 64 clock to Pulse Accumulator and the trailing falling edge on IOC7 sets the PAIF flag.</li> <li>1 IOC7 input pin low enables M (bus clock) divided by 64 clock to Pulse Accumulator and the trailing rising edge on IOC7 sets the PAIF flag.</li> </ul> |

| 3:2<br>CLK[1:0] | Clock Select Bits — Refer to Table 16-20.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1<br>PAOVI      | Pulse Accumulator Overflow Interrupt Enable         0 Interrupt inhibited.         1 Interrupt requested if PAOVF is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0<br>PAI        | Pulse Accumulator Input Interrupt Enable         0 Interrupt inhibited.         1 Interrupt requested if PAIF is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### Table 16-18. PACTL Field Descriptions

### Table 16-23. PTPSR Field Descriptions

| Field            | Description                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTPS[7:0] | <b>Precision Timer Prescaler Select Bits</b> — These eight bits specify the division rate of the main Timer prescaler. These are effective only when the PRNT bit of TSCR1 is set to 1. Table 16-24 shows some selection examples in this case. |

|                  | The newly selected prescale factor will not take effect until the next synchronized edge where all prescale counter stages equal zero.                                                                                                          |

The Prescaler can be calculated as follows depending on logical value of the PTPS[7:0] and PRNT bit:

PRNT = 1 : Prescaler = PTPS[7:0] + 1

|       | -     |       |       |       |       |       |       |                    |

|-------|-------|-------|-------|-------|-------|-------|-------|--------------------|

| PTPS7 | PTPS6 | PTPS5 | PTPS4 | PTPS3 | PTPS2 | PTPS1 | PTPS0 | Prescale<br>Factor |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 2                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 3                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 4                  |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 5                  |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     | 6                  |

| 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     | 7                  |

| 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 8                  |

| 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 16                 |

| 0     | 0     | 0     | 1     | 1     | 1     | 1     | 1     | 32                 |

| 0     | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 64                 |

| 0     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 128                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 256                |

Table 16-24. Precision Timer Prescaler Selection Examples when PRNT = 1

## 16.4 Functional Description

This section provides a complete functional description of the timer TIM16B8CV2 block. Please refer to the detailed timer block diagram in Figure 16-30 as necessary.

Voltage Regulator (S12VREGL3V3V1)

# 17.2 External Signal Description

Due to the nature of VREG\_3V3 being a voltage regulator providing the chip internal power supply voltages, most signals are power supply signals connected to pads.

Table 17-2 shows all signals of VREG\_3V3 associated with pins.

| Name                   | Function                                         | Reset State | Pull Up |

|------------------------|--------------------------------------------------|-------------|---------|

| VDDR                   | Power input (positive supply)                    | —           | —       |

| VDDA                   | Quiet input (positive supply)                    | —           | —       |

| VSSA                   | Quiet input (ground)                             | —           | —       |

| VDDX                   | Power input (positive supply)                    | —           | —       |

| VDD                    | Primary output (positive supply)                 | —           | —       |

| VSS                    | Primary output (ground)                          | —           | —       |

| VDDF                   | Secondary output (positive supply)               | —           | —       |

| VDDPLL                 | Tertiary output (positive supply)                | —           | —       |

| VSSPLL                 | Tertiary output (ground)                         | —           | —       |

| VREGEN (optional)      | Optional Regulator Enable                        | —           | —       |

| VREG_API<br>(optional) | VREG Autonomous Periodical —<br>Interrupt output |             | —       |

Table 17-2. Signal Properties

### NOTE

Check device level specification for connectivity of the signals.

## 17.2.1 VDDR — Regulator Power Input Pins

Signal VDDR is the power input of VREG\_3V3. All currents sourced into the regulator loads flow through this pin. A chip external decoupling capacitor (100 nF...220 nF, X7R ceramic) between VDDR and VSSR (if VSSR is not available VSS) can smooth ripple on VDDR.

For entering Shutdown Mode, pin VDDR should also be tied to ground on devices without VREGEN pin.

## 17.2.2 VDDA, VSSA — Regulator Reference Supply Pins

Signals VDDA/VSSA, which are supposed to be relatively quiet, are used to supply the analog parts of the regulator. Internal precision reference circuits are supplied from these signals. A chip external decoupling capacitor (100 nF...220 nF, X7R ceramic) between VDDA and VSSA can further improve the quality of this supply.

## 17.2.3 VDD, VSS — Regulator Output1 (Core Logic) Pins

Signals VDD/VSS are the primary outputs of VREG\_3V3 that provide the power supply for the core logic. These signals are connected to device pins to allow external decoupling capacitors (220 nF, X7R ceramic).

#### 256 KByte Flash Module (S12XFTMR256K1V1)

| Table 18-61. Program D-Flash Comm | nand FCCOB Requirements |

|-----------------------------------|-------------------------|

|-----------------------------------|-------------------------|

| CCOBIX[2:0] | FCCOB Parameters                 |  |

|-------------|----------------------------------|--|

| 101         | Word 3 program value, if desired |  |

Upon clearing CCIF to launch the Program D-Flash command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program D-Flash command launch determines how many words will be programmed in the D-Flash block. The CCIF flag is set when the operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                          |  |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |  |

|          | ACCERR    | Set if command not available in current mode (see Table 18-28)                      |  |

|          | ACCERK    | Set if an invalid global address [22:0] is supplied                                 |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |

|          |           | Set if the requested group of words breaches the end of the D-Flash block           |  |

|          | FPVIOL    | Set if the selected area of the D-Flash memory is protected                         |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |

|          | MGSTATO   | Set if any non-correctable errors have been encountered during the verify operation |  |

### Table 18-62. Program D-Flash Command Error Handling

### 18.4.2.16 Erase D-Flash Sector Command

The Erase D-Flash Sector operation will erase all addresses in a sector of the D-Flash block.

Table 18-63. Erase D-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                |                                                     |  |

|-------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| 000         | 0x12                                                                                                            | Global address [22:16] to identify<br>D-Flash block |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 18.1.2.2 for D-Flash sector size. |                                                     |  |

Upon clearing CCIF to launch the Erase D-Flash Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase D-Flash Sector operation has completed.

#### 128 KByte Flash Module (S12XFTMR128K1V1)

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the field margin level for the targeted block and then set the CCIF flag. Valid margin level settings for the Set Field Margin Level command are defined in Table 19-57.

| CCOB<br>(CCOBIX=001) | Level Description                 |  |

|----------------------|-----------------------------------|--|

| 0x0000               | Return to Normal Level            |  |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |  |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |  |

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

| Table 19-58. Set Field Margin Level Command Error H | Handling |

|-----------------------------------------------------|----------|

|-----------------------------------------------------|----------|

| Register | Error Bit | Error Condition                                                |  |

|----------|-----------|----------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                    |  |

|          |           | Set if command not available in current mode (see Table 19-28) |  |

| FSTAT    |           | Set if an invalid global address [22:16] is supplied           |  |

|          |           | Set if an invalid margin level setting is supplied             |  |

|          | FPVIOL    | None                                                           |  |

|          | MGSTAT1   | None                                                           |  |

|          | MGSTAT0   | None                                                           |  |

### CAUTION

Field margin levels must only be used during verify of the initial factory programming.

### NOTE

Field margin levels can be used to check that Flash memory contents have adequate margin for data retention at the normal level setting. If unexpected results are encountered when checking Flash memory contents at field margin levels, the Flash memory contents should be erased and reprogrammed.

### 19.4.2.14 Erase Verify D-Flash Section Command

The Erase Verify D-Flash Section command will verify that a section of code in the D-Flash is erased. The Erase Verify D-Flash Section command defines the starting point of the data to be verified and the number of words.

128 KByte Flash Module (S12XFTMR128K1V1)

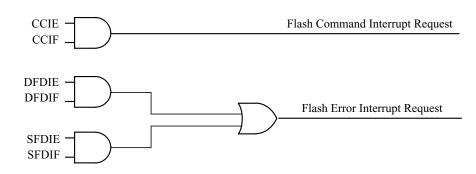

Figure 19-27. Flash Module Interrupts Implementation

## 19.4.4 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 19.4.3, "Interrupts").

## 19.4.5 Stop Mode

If a Flash command is active (CCIF = 0) when the MCU requests stop mode, the current Flash operation will be completed before the CPU is allowed to enter stop mode.

## 19.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 19-10). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x7F\_FF0F.

The security state out of reset can be permanently changed by programming the security byte of the Flash configuration field. This assumes that you are starting from a mode where the necessary P-Flash erase and program commands are available and that the upper region of the P-Flash is unprotected. If the Flash security byte is successfully programmed, its new value will take affect after the next MCU reset.

The following subsections describe these security-related subjects:

- Unsecuring the MCU using Backdoor Key Access

- Unsecuring the MCU in Special Single Chip Mode using BDM

- Mode and Security Effects on Flash Command Availability

## 19.5.1 Unsecuring the MCU using Backdoor Key Access

The MCU may be unsecured by using the backdoor key access feature which requires knowledge of the contents of the backdoor keys (four 16-bit words programmed at addresses 0x7F\_FF00–0x7F\_FF07). If the KEYEN[1:0] bits are in the enabled state (see Section 19.3.2.2), the Verify Backdoor Access Key command (see Section 19.4.2.11) allows the user to present four prospective keys for comparison to the

## Chapter 20 64 KByte Flash Module (S12XFTMR64K1V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected                                                                                                      | Description of Changes                                                                                                                                              |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V01.04             | 03 Jan 2008      |                                                                                                                           | - Cosmetic changes                                                                                                                                                  |

| V01.05             | 19 Dec 2008      | 20.1/20-607<br>20.4.2.4/20-642<br>20.4.2.6/20-644<br>20.4.2.11/20-64<br>8<br>20.4.2.11/20-64<br>8<br>20.4.2.11/20-64<br>8 | Program Once, and Verify Backdoor Access Key commands from Flash block containing associated fields<br>- Relate Key 0 to associated Backdoor Comparison Key address |

| V01.06             | 25 Sep 2009      | 20.3.2/20-615<br>20.3.2.1/20-617<br>20.4.1.2/20-636<br>20.6/20-656                                                        | ······································                                                                                                                              |

### Table 20-1. Revision History

## 20.1 Introduction

The FTMR64K1 module implements the following:

- 64 Kbytes of P-Flash (Program Flash) memory

- 4 Kbytes of D-Flash (Data Flash) memory

The Flash memory is ideal for single-supply applications allowing for field reprogramming without requiring external high voltage sources for program or erase operations. The Flash module includes a memory controller that executes commands to modify Flash memory contents. The user interface to the memory controller consists of the indexed Flash Common Command Object (FCCOB) register which is written to with the command, global address, data, and any required command parameters. The memory controller must complete the execution of a command before the FCCOB register can be written to with a new command.

| Register | Error Bit | Error Condition                                                                     |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|

|          |           | Set if CCOBIX[2:0] != 101 at command launch                                         |  |

|          | ACCERR    | Set if command not available in current mode (see Table 20-28)                      |  |

|          | ACCERK    | Set if an invalid global address [22:0] is supplied <sup>1</sup>                    |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |

|          | FPVIOL    | Set if the global address [22:0] points to a protected area                         |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |

#### Table 20-40. Program P-Flash Command Error Handling

<sup>1</sup> As defined by the memory map for FTMR128K1.

## 20.4.2.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash block 0. The Program Once reserved field can be read using the Read Once command as described in Section 20.4.2.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash block 0 cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |  |  |

|-------------|---------------------------------------------|--|--|

| 000         | 0x07 Not Required                           |  |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |  |  |

| 010         | Program Once word 0 value                   |  |  |

| 011         | Program Once word 1 value                   |  |  |

| 100         | Program Once word 2 value                   |  |  |

| 101         | Program Once word 3 value                   |  |  |

Table 20-41. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash block 0 will return invalid data.

## 64 KByte Flash Module (S12XFTMR64K1V1)

### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

| CCOBIX[2:0] | FCCOB Parameters                               |                                                      |  |  |  |  |  |  |

|-------------|------------------------------------------------|------------------------------------------------------|--|--|--|--|--|--|

| 000         | 0x11                                           | Global address [22:16] to identify the D-Flash block |  |  |  |  |  |  |

| 001         | Global address [15:0] of word to be programmed |                                                      |  |  |  |  |  |  |

| 010         | Word 0 program value                           |                                                      |  |  |  |  |  |  |

| 011         | Word 1 program value, if desired               |                                                      |  |  |  |  |  |  |

| 100         | Word 2 program value, if desired               |                                                      |  |  |  |  |  |  |

| 101         | Word 3 program value, if desired               |                                                      |  |  |  |  |  |  |

### Table 20-61. Program D-Flash Command FCCOB Requirements

Upon clearing CCIF to launch the Program D-Flash command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program D-Flash command launch determines how many words will be programmed in the D-Flash block. The CCIF flag is set when the operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                          |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |

|          | ACCERR    | Set if command not available in current mode (see Table 20-28)                      |

|          | ACCERK    | Set if an invalid global address [22:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          |           | Set if the requested group of words breaches the end of the D-Flash block           |

|          | FPVIOL    | Set if the selected area of the D-Flash memory is protected                         |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

#### Table 20-62. Program D-Flash Command Error Handling

### 20.4.2.16 Erase D-Flash Sector Command

The Erase D-Flash Sector operation will erase all addresses in a sector of the D-Flash block.

### Table 20-63. Erase D-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |                                                     |  |  |  |  |  |

|-------------|------------------|-----------------------------------------------------|--|--|--|--|--|

| 000         | 0x12             | Global address [22:16] to identify<br>D-Flash block |  |  |  |  |  |

**Electrical Characteristics**

| Voltage difference V <sub>DDR</sub> to V <sub>DDX</sub>                                                                 | $\Delta_{VDDR}$                  | -0.1     | 0                   | 0.1        | V   |  |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------|---------------------|------------|-----|--|

| Voltage difference $V_{SSX}$ to $V_{SSA}$                                                                               | $\Delta_{VSSX}$                  |          | refer to Table A-14 |            |     |  |

| Voltage difference $V_{SS1}$ , $V_{SS2}$ , $V_{SS3}$ , $V_{SSPLL}$ to $V_{SSX}$                                         | $\Delta_{VSS}$                   | -0.1     | 0                   | 0.1        | V   |  |

| Digital logic supply voltage <sup>1</sup>                                                                               | V <sub>DD</sub>                  | 1.72     | 1.8                 | 1.98       | V   |  |

| PLL supply voltage                                                                                                      | V <sub>DDPLL</sub>               | 1.72     | 1.8                 | 1.98       | V   |  |

| Oscillator <sup>2</sup> (Loop Controlled Pierce)<br>(Full Swing Pierce)                                                 | f <sub>osc</sub>                 | 4<br>2   |                     | 16<br>40   | MHz |  |

| Bus frequency <sup>3</sup>                                                                                              | f <sub>bus</sub>                 | 0.5      | _                   | 40         | MHz |  |

| Temperature Option <b>C</b><br>Operating junction temperature range<br>Operating ambient temperature range <sup>4</sup> | T <sub>J</sub><br>T <sub>A</sub> | 40<br>40 | <br>27              | 110<br>85  | °C  |  |

| Temperature Option <b>V</b><br>Operating junction temperature range<br>Operating ambient temperature range <sup>4</sup> | T <sub>J</sub><br>T <sub>A</sub> | 40<br>40 | <br>27              | 130<br>105 | °C  |  |

| Temperature Option <b>M</b><br>Operating junction temperature range<br>Operating ambient temperature range <sup>4</sup> | T <sub>J</sub><br>T <sub>A</sub> | 40<br>40 | <br>27              | 150<br>125 | °C  |  |

#### **Table A-4. Operating Conditions**

The device contains an internal voltage regulator to generate the logic and PLL supply out of the I/O supply. 1

This refers to the oscillator base frequency. Typical crystal & resonator tolerances are supported. Please refer to Table A-24 for maximum bus frequency limits with frequency modulation enabled 2

3

Please refer to Section A.1.8, "Power Dissipation and Thermal Characteristics" for more details about the relation between ambient temperature  $T_A$  and device junction temperature  $T_J$ . 4

### NOTE

Using the internal voltage regulator, operation is guaranteed in a power down until a low voltage reset assertion.

#### A.1.8 **Power Dissipation and Thermal Characteristics**

Power dissipation and thermal characteristics are closely related. The user must assure that the maximum operating junction temperature is not exceeded. The average chip-junction temperature  $(T_1)$  in °C can be obtained from:

$$\mathsf{T}_{\mathsf{J}} = \mathsf{T}_{\mathsf{A}} + (\mathsf{P}_{\mathsf{D}} \bullet \Theta_{\mathsf{J}} \mathsf{A})$$

$T_{I}$  = Junction Temperature, [°C]

$T_{\Lambda}$  = Ambient Temperature, [°C]

P<sub>D</sub> = Total Chip Power Dissipation, [W]

$\Theta_{I\Delta}$  = Package Thermal Resistance, [°C/W]

S12XS Family Reference Manual, Rev. 1.13

## C.1.1 112-Pin LQFP Recommended PCB Layout

Figure C-1. 112-Pin LQFP Recommended PCB Layout (Loop Controlled Pierce Oscillator)

S12XS Family Reference Manual, Rev. 1.13

**Detailed Register Address Map**

### Detailed MSCAN Foreground Receive and Transmit Buffer Layout (continued)

| Address | Name      |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0xXX1F  | CANxTTSRL | R | TSR7  | TSR6  | TSR5  | TSR4  | TSR3  | TSR2  | TSR1  | TSR0  |

|         |           | W |       |       |       |       |       |       |       |       |

### 0x0180–0x023F Reserved Register Space

| Address           | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0180-<br>0x023F | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                   |          | W |       |       |       |       |       |       |       |       |

### 0x0240–0x027F Port Integration Module (PIM) Map 5 of 5

| Address | Name     |        | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|---------|----------|--------|--------|--------|--------|--------|-------|--------|--------|--------|

| 0x0240  | PTT      | R<br>W | PTT7   | PTT6   | PTT5   | PTT4   | PTT3  | PTT2   | PTT1   | PTT0   |

| 0x0241  | PTIT     | R      | PTIT7  | PTIT6  | PTIT5  | PTIT4  | PTIT3 | PTIT2  | PTIT1  | PTIT0  |

| 0702-11 |          | W      |        |        |        |        |       |        |        |        |

| 0x0242  | DDRT     | R<br>W | DDRT7  | DDRT6  | DDRT5  | DDRT4  | DDRT3 | DDRT2  | DDRT1  | DDRT0  |

| 0x0243  | RDRT     | R<br>W | RDRT7  | RDRT6  | RDRT5  | RDRT4  | RDRT3 | RDRT2  | RDRT1  | RDRT0  |

| 0x0244  | PERT     | R<br>W | PERT7  | PERT6  | PERT5  | PERT4  | PERT3 | PERT2  | PERT1  | PERT0  |

| 0x0245  | PPST     | R<br>W | PPST7  | PPST6  | PPST5  | PPST4  | PPST3 | PPST2  | PPST1  | PPST0  |

| 0x0246  | Reserved | R      | 0      | 0      | 0      | 0      | 0     | 0      | 0      | 0      |

| 0/0240  | 10001700 | W      |        |        |        |        |       |        |        |        |

| 0x0247  | PTTRR    | R<br>W | PTTRR7 | PTTRR6 | PTTRR5 | PTTRR4 | 0     | PTTRR2 | PTTRR1 | PTTRR0 |