Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |  |  |

|----------------------------|-------------------------------------------------------------------------|--|--|

| Product Status             | Active                                                                  |  |  |

| Core Processor             | HCS12X                                                                  |  |  |

| Core Size                  | 16-Bit                                                                  |  |  |

| Speed                      | 40MHz                                                                   |  |  |

| Connectivity               | CANbus, SCI, SPI                                                        |  |  |

| Peripherals                | LVD, POR, PWM, WDT                                                      |  |  |

| Number of I/O              | 59                                                                      |  |  |

| Program Memory Size        | 256KB (256K x 8)                                                        |  |  |

| Program Memory Type        | FLASH                                                                   |  |  |

| EEPROM Size                | -                                                                       |  |  |

| RAM Size                   | 12К х 8                                                                 |  |  |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |  |  |

| Data Converters A/D 8x12b  |                                                                         |  |  |

| Oscillator Type            | External                                                                |  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |  |  |

| Mounting Type              | Surface Mount                                                           |  |  |

| Package / Case             | 80-QFP                                                                  |  |  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs256j0vaa |  |  |

|                            |                                                                         |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 12.1.2 Features             | . 349 |

|------|-----------------------------|-------|

|      | 12.1.3 Modes of Operation   | . 349 |

|      | 12.1.4 Block Diagram        | . 350 |

| 12.2 | External Signal Description | . 350 |

| 12.3 | Register Definition         | . 351 |

| 12.4 | Functional Description      |       |

|      | 12.4.1 Timer                | . 360 |

|      | 12.4.2 Interrupt Interface  |       |

|      | 12.4.3 Hardware Trigger     | . 362 |

| 12.5 | Initialization              | . 362 |

|      | 12.5.1 Startup              | . 362 |

|      | 12.5.2 Shutdown             | . 362 |

|      | 12.5.3 Flag Clearing        | . 362 |

| 12.6 | Application Information     | . 363 |

# Chapter 13 Pulse-Width Modulator (S12PWM8B8CV1)

| 13.1 | Introduction                       | 55             |

|------|------------------------------------|----------------|

|      | 13.1.1 Features                    | 55             |

|      | 13.1.2 Modes of Operation          | 56             |

|      | 13.1.3 Block Diagram               | 56             |

| 13.2 | External Signal Description        | 56             |

|      | 13.2.1 PWM7 — PWM Channel 7 36     | 57             |

|      | 13.2.2 PWM6 — PWM Channel 6 36     | 57             |

|      | 13.2.3 PWM5 — PWM Channel 5 36     | 57             |

|      | 13.2.4 PWM4 — PWM Channel 4 36     | 57             |

|      | 13.2.5 PWM3 — PWM Channel 3 36     | 57             |

|      | 13.2.6 PWM3 — PWM Channel 2 36     | 57             |

|      | 13.2.7 PWM3 — PWM Channel 1 36     | 57             |

|      | 13.2.8 PWM3 — PWM Channel 0 36     | 57             |

| 13.3 | Memory Map and Register Definition | 57             |

|      | 13.3.1 Module Memory Map           | 57             |

|      | 13.3.2 Register Descriptions       | 58             |

| 13.4 | Functional Description             | 33             |

|      | 13.4.1 PWM Clock Select            | 33             |

|      | 13.4.2 PWM Channel Timers          | 36             |

| 13.5 | Resets                             | <del>)</del> 4 |

| 13.6 | Interrupts                         | <del>)</del> 5 |

# Chapter 14

# Serial Communication Interface (S12SCIV5)

| 14.1 Introduction | on      | 397 |

|-------------------|---------|-----|

| 14.1.1 Gl         | lossary | 397 |

| 14.1.2 Fe         | eatures | 398 |

**Device Overview S12XS Family**

## **1.2.3 Detailed Signal Descriptions**

#### NOTE

The pin list of the largest package version of each S12XS Family derivative gives the complete of interface signals that also exist on smaller package options, although some of them are not bonded out. For devices assembled in smaller packages all non-bonded out pins should be configured as outputs after reset in order to avoid current drawn from floating inputs. Refer to Table 1-6 for affected pins.

## 1.2.3.1 EXTAL, XTAL — Oscillator Pins

EXTAL and XTAL are the crystal driver and external clock pins. On reset all the device clocks are derived from the EXTAL input frequency. XTAL is the oscillator output.

## 1.2.3.2 RESET — External Reset Pin

The  $\overline{\text{RESET}}$  pin is an active low bidirectional control signal. It acts as an input to initialize the MCU to a known start-up state. As an output it is driven low to indicate when any internal MCU reset source triggers. The  $\overline{\text{RESET}}$  pin has an internal pull-up device.

## 1.2.3.3 TEST — Test Pin

This input only pin is reserved for factory test. This pin has a pull-down device.

#### NOTE

The TEST pin must be tied to  $V_{SS}$  in all applications.

## 1.2.3.4 BKGD / MODC — Background Debug and Mode Pin

The BKGD/MODC pin is used as a pseudo-open-drain pin for the background debug communication. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODC bit at the rising edge of RESET. The BKGD pin has an internal pull-up device.

## 1.2.3.5 PAD[15:0] / AN[15:0] — Port AD Input Pins of ATD0

PAD[15:0] are general-purpose input or output pins and analog inputs AN[15:0] of the analog-to-digital converter ATD0.

## 1.2.3.6 PA[7:0] — Port A I/O Pins

PA[7:0] are general-purpose input or output pins.

## 1.2.3.7 PB[7:0] — Port B I/O Pins

PB[7:0] are general-purpose input or output pins.

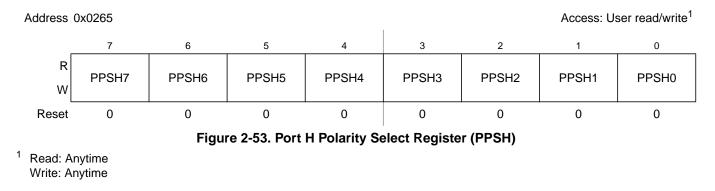

# 2.3.55 Port H Polarity Select Register (PPSH)

#### Table 2-52. PPSH Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PPSH | <ul> <li>Port H pull device select—Configure pull device and pin interrupt edge polarity on input pin<br/>This bit selects a pull-up or a pull-down device if enabled on the associated port input pin.<br/>This bit also selects the polarity of the active pin interrupt edge.</li> <li>1 A pull-down device selected; rising edge selected</li> <li>0 A pull-up device selected; falling edge selected</li> </ul> |

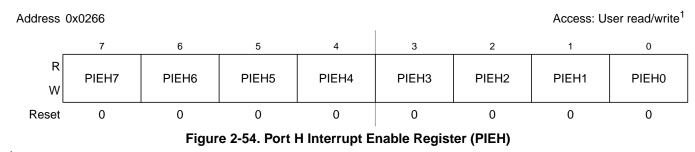

## 2.3.56 Port H Interrupt Enable Register (PIEH)

<sup>1</sup> Read: Anytime Write: Anytime

Table 2-53. PIEH Register Field Descriptions

| Field       | Description                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PIEH | Port H interrupt enable—<br>This bit enables or disables on the edge sensitive pin interrupt on the associated pin. |

|             | 1 Interrupt enabled<br>0 Interrupt disabled (interrupt flag masked)                                                 |

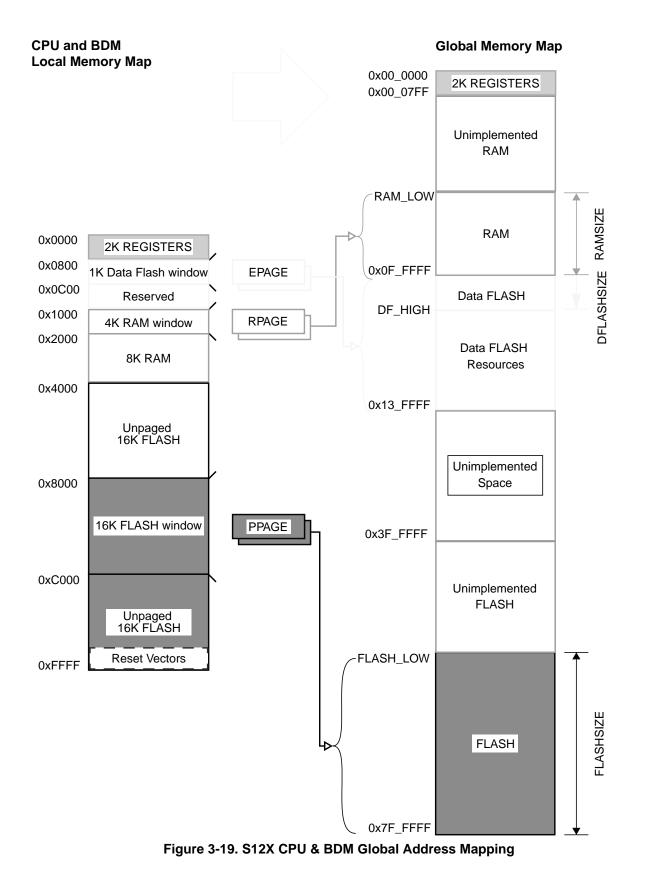

Memory Mapping Control (S12XMMCV4)

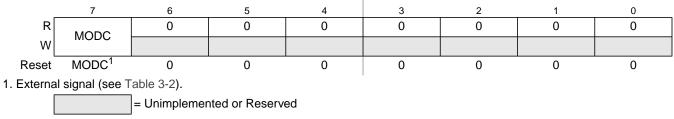

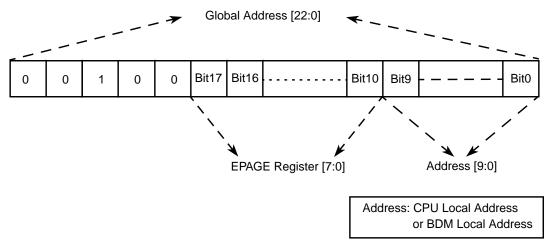

# 3.3.2.1 Mode Register (MODE)

Address: 0x000B PRR

Figure 3-3. Mode Register (MODE)

Read: Anytime. Write: Only if a transition is allowed (see Figure 3-5).

The MODE bits of the MODE register are used to establish the MCU operating mode.

| Field     | Description                                                                                                                                                                                                                                                                                       |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>MODC | <b>Mode Select Bit</b> — This bit controls the current operating mode during RESET high (inactive). The ex mode pin MODC determines the operating mode during RESET low (active). The state of the pin is latc the respective register bit after the RESET signal goes inactive (see Figure 3-3). |  |  |

|           | Write restrictions exist to disallow transitions between certain modes. Figure 3-5 illustrates all allowed mode changes. Attempting non authorized transitions will not change the MODE bits, but it will block further writes to these register bits except in special modes.                    |  |  |

|           | Write accesses to the MODE register are blocked when the device is secured.                                                                                                                                                                                                                       |  |  |

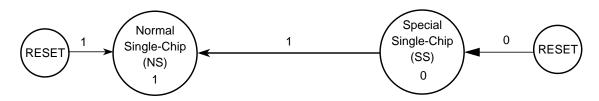

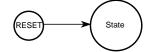

Transition done by external pins (MODC)

Transition done by write access to the MODE register

Figure 3-5. Mode Transition Diagram when MCU is Unsecured

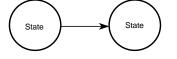

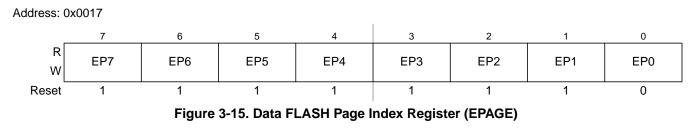

### 3.3.2.7 Data FLASH Page Index Register (EPAGE)

Read: Anytime

Write: Anytime

These eight index bits are used to page 1KB blocks into the Data FLASH page window located in the local (CPU or BDM) memory map from address 0x0800 to address 0x0BFF (see Figure 3-16). This supports accessing up to 256KB of Data FLASH (in the Global map) within the 64KB Local map. The Data FLASH page index register is effectively used to construct paged Data FLASH addresses in the Local map format.

Figure 3-16. EPAGE Address Mapping

| Table 3-9 | . EPAGE Field | d Descriptions |

|-----------|---------------|----------------|

|-----------|---------------|----------------|

| Field | Description                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data FLASH Page Index Bits 7–0</b> — These page index bits are used to select which of the 256 Data FLASH array pages is to be accessed in the Data FLASH Page Window. |

Memory Mapping Control (S12XMMCV4)

S12XS Family Reference Manual, Rev. 1.13

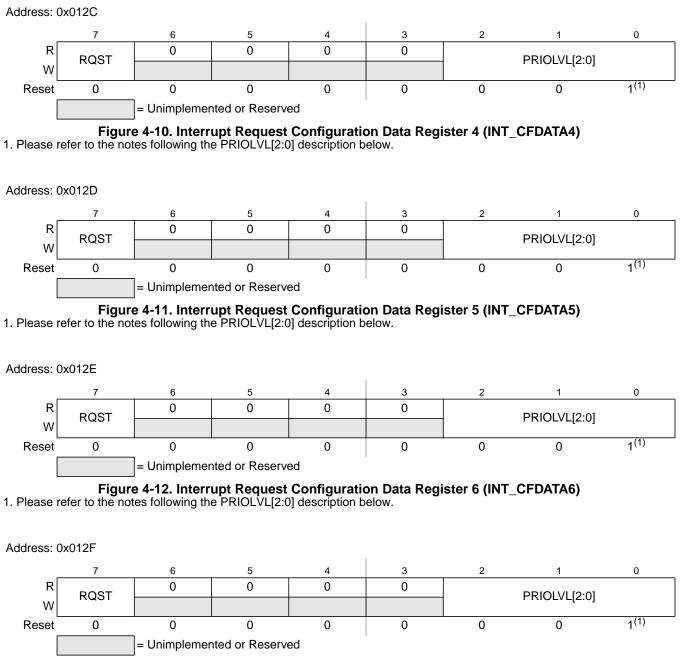

# Chapter 4 Interrupt (S12XINTV2)

| Revision<br>Number | Revision Date | Sections<br>Affected           | Description of Changes                                                                                                                               |  |

|--------------------|---------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V02.00             | 01 Jul 2005   | 4.1.2/4-152                    | Initial V2 release, added new features:<br>- XGATE threads can be interrupted.<br>- SYS instruction vector.<br>- Access violation interrupt vectors. |  |

| V02.04             | 11 Jan 2007   | 4.3.2.2/4-157<br>4.3.2.4/4-158 | - Added Notes for devices without XGATE module.                                                                                                      |  |

| V02.05             | 20 Mar 2007   | 4.4.6/4-164                    | - Fixed priority definition for software exceptions.                                                                                                 |  |

| V02.07             | 13 Dec 2011   | 4.5.3.1/4-166                  | - Re-worded for difference of Wake-up feature between STOP and WAIT modes.                                                                           |  |

#### Table 4-1. Revision History

# 4.1 Introduction

The XINT module decodes the priority of all system exception requests and provides the applicable vector for processing the exception to either the CPU or the XGATE module. The XINT module supports:

- I bit and X bit maskable interrupt requests

- One non-maskable unimplemented op-code trap

- One non-maskable software interrupt (SWI) or background debug mode request

- One non-maskable system call interrupt (SYS)

- Three non-maskable access violation interrupts

- One spurious interrupt vector request

- Three system reset vector requests

Each of the I bit maskable interrupt requests can be assigned to one of seven priority levels supporting a flexible priority scheme. For interrupt requests that are configured to be handled by the CPU, the priority scheme can be used to implement nested interrupt capability where interrupts from a lower level are automatically blocked if a higher level interrupt is being processed. Interrupt requests configured to be handled by the XGATE module can be nested one level deep.

#### NOTE

The HPRIO register and functionality of the original S12 interrupt module is no longer supported. It is superseded by the 7-level interrupt request priority scheme.

#### Interrupt (S12XINTV2)

Figure 4-13. Interrupt Request Configuration Data Register 7 (INT\_CFDATA7) 1. Please refer to the notes following the PRIOLVL[2:0] description below.

Read: Anytime

Write: Anytime

| Table 5 | -7. Fi | rmware | Commands |

|---------|--------|--------|----------|

|---------|--------|--------|----------|

| Command <sup>1</sup>                                                                | Opcode<br>(hex) | Data            | Description                                                                                                                                                      |

|-------------------------------------------------------------------------------------|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ_NEXT <sup>2</sup>                                                              | 62              | 16-bit data out | Increment X index register by 2 (X = X + 2), then read word X points to.                                                                                         |

| READ_PC                                                                             | 63              | 16-bit data out | Read program counter.                                                                                                                                            |

| READ_D                                                                              | 64              | 16-bit data out | Read D accumulator.                                                                                                                                              |

| READ_X                                                                              | 65              | 16-bit data out | Read X index register.                                                                                                                                           |

| READ_Y                                                                              | 66              | 16-bit data out | Read Y index register.                                                                                                                                           |

| READ_SP                                                                             | 67              | 16-bit data out | Read stack pointer.                                                                                                                                              |

| WRITE_NEXT <f-hel<br>vetica&gt;<st-superscri<br>pt&gt;</st-superscri<br></f-hel<br> | 42              | 16-bit data in  | Increment X index register by 2 (X = X + 2), then write word to location pointed to by X.                                                                        |

| WRITE_PC                                                                            | 43              | 16-bit data in  | Write program counter.                                                                                                                                           |

| WRITE_D                                                                             | 44              | 16-bit data in  | Write D accumulator.                                                                                                                                             |

| WRITE_X                                                                             | 45              | 16-bit data in  | Write X index register.                                                                                                                                          |

| WRITE_Y                                                                             | 46              | 16-bit data in  | Write Y index register.                                                                                                                                          |

| WRITE_SP                                                                            | 47              | 16-bit data in  | Write stack pointer.                                                                                                                                             |

| GO                                                                                  | 08              | none            | Go to user program. If enabled, ACK will occur when leaving active background mode.                                                                              |

| GO_UNTIL <sup>3</sup>                                                               | 0C              | none            | Go to user program. If enabled, ACK will occur upon returning to active background mode.                                                                         |

| TRACE1                                                                              | 10              | none            | Execute one user instruction then return to active BDM. If enabled, ACK will occur upon returning to active background mode.                                     |

| TAGGO -> GO                                                                         | 18              | none            | (Previous enable tagging and go to user program.)<br>This command will be deprecated and should not be used anymore.<br>Opcode will be executed as a GO command. |

<sup>1</sup> If enabled, ACK will occur when data is ready for transmission for all BDM READ commands and will occur after the write is complete for all BDM WRITE commands.

<sup>2</sup> When the firmware command READ\_NEXT or WRITE\_NEXT is used to access the BDM address space the BDM resources are accessed rather than user code. Writing BDM firmware is not possible.

<sup>3</sup> System stop disables the ACK function and ignored commands will not have an ACK-pulse (e.g., CPU in stop or wait mode). The GO\_UNTIL command will not get an Acknowledge if CPU executes the wait or stop instruction before the "UNTIL" condition (BDM active again) is reached (see Section 5.4.7, "Serial Interface Hardware Handshake Protocol" last Note).

# 5.4.5 BDM Command Structure

Hardware and firmware BDM commands start with an 8-bit opcode followed by a 16-bit address and/or a 16-bit data word depending on the command. All the read commands return 16 bits of data despite the byte or word implication in the command name.

8-bit reads return 16-bits of data, of which, only one byte will contain valid data. If reading an even address, the valid data will appear in the MSB. If reading an odd address, the valid data will appear in the LSB.

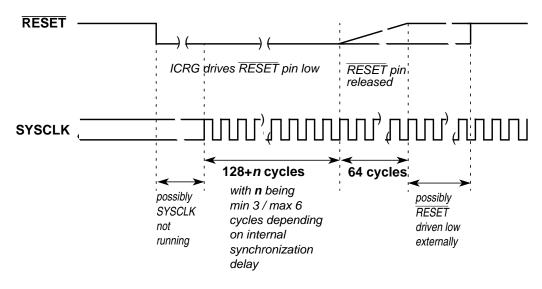

S12XE Clocks and Reset Generator (S12XECRGV1)

|            |                             |                             |                             | RTR                          | [6:4] =                      |                              |                               |                               |

|------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------------------------------|-------------------------------|-------------------------------|

| RTR[3:0]   | 000<br>(1x10 <sup>3</sup> ) | 001<br>(2x10 <sup>3</sup> ) | 010<br>(5x10 <sup>3</sup> ) | 011<br>(10x10 <sup>3</sup> ) | 100<br>(20x10 <sup>3</sup> ) | 101<br>(50x10 <sup>3</sup> ) | 110<br>(100x10 <sup>3</sup> ) | 111<br>(200x10 <sup>3</sup> ) |

| 0110 (÷7)  | 7x10 <sup>3</sup>           | 14x10 <sup>3</sup>          | 35x10 <sup>3</sup>          | 70x10 <sup>3</sup>           | 140x10 <sup>3</sup>          | 350x10 <sup>3</sup>          | 700x10 <sup>3</sup>           | 1.4x10 <sup>6</sup>           |

| 0111 (÷8)  | 8x10 <sup>3</sup>           | 16x10 <sup>3</sup>          | 40x10 <sup>3</sup>          | 80x10 <sup>3</sup>           | 160x10 <sup>3</sup>          | 400x10 <sup>3</sup>          | 800x10 <sup>3</sup>           | 1.6x10 <sup>6</sup>           |

| 1000 (÷9)  | 9x10 <sup>3</sup>           | 18x10 <sup>3</sup>          | 45x10 <sup>3</sup>          | 90x10 <sup>3</sup>           | 180x10 <sup>3</sup>          | 450x10 <sup>3</sup>          | 900x10 <sup>3</sup>           | 1.8x10 <sup>6</sup>           |

| 1001 (÷10) | 10 x10 <sup>3</sup>         | 20x10 <sup>3</sup>          | 50x10 <sup>3</sup>          | 100x10 <sup>3</sup>          | 200x10 <sup>3</sup>          | 500x10 <sup>3</sup>          | 1x10 <sup>6</sup>             | 2x10 <sup>6</sup>             |

| 1010 (÷11) | 11 x10 <sup>3</sup>         | 22x10 <sup>3</sup>          | 55x10 <sup>3</sup>          | 110x10 <sup>3</sup>          | 220x10 <sup>3</sup>          | 550x10 <sup>3</sup>          | 1.1x10 <sup>6</sup>           | 2.2x10 <sup>6</sup>           |

| 1011 (÷12) | 12x10 <sup>3</sup>          | 24x10 <sup>3</sup>          | 60x10 <sup>3</sup>          | 120x10 <sup>3</sup>          | 240x10 <sup>3</sup>          | 600x10 <sup>3</sup>          | 1.2x10 <sup>6</sup>           | 2.4x10 <sup>6</sup>           |

| 1100 (÷13) | 13x10 <sup>3</sup>          | 26x10 <sup>3</sup>          | 65x10 <sup>3</sup>          | 130x10 <sup>3</sup>          | 260x10 <sup>3</sup>          | 650x10 <sup>3</sup>          | 1.3x10 <sup>6</sup>           | 2.6x10 <sup>6</sup>           |

| 1101 (÷14) | 14x10 <sup>3</sup>          | 28x10 <sup>3</sup>          | 70x10 <sup>3</sup>          | 140x10 <sup>3</sup>          | 280x10 <sup>3</sup>          | 700x10 <sup>3</sup>          | 1.4x10 <sup>6</sup>           | 2.8x10 <sup>6</sup>           |

| 1110 (÷15) | 15x10 <sup>3</sup>          | 30x10 <sup>3</sup>          | 75x10 <sup>3</sup>          | 150x10 <sup>3</sup>          | 300x10 <sup>3</sup>          | 750x10 <sup>3</sup>          | 1.5x10 <sup>6</sup>           | 3x10 <sup>6</sup>             |

| 1111 (÷16) | 16x10 <sup>3</sup>          | 32x10 <sup>3</sup>          | 80x10 <sup>3</sup>          | 160x10 <sup>3</sup>          | 320x10 <sup>3</sup>          | 800x10 <sup>3</sup>          | 1.6x10 <sup>6</sup>           | 3.2x10 <sup>6</sup>           |

Table 8-11. RTI Frequency Divide Rates for RTDEC=1

## 8.3.2.9 S12XECRG COP Control Register (COPCTL)

This register controls the COP (Computer Operating Properly) watchdog.

Module Base + 0x0008

|                    | 7    | 6     | 5       | 4 | 3 | 2   | 1   | 0   |

|--------------------|------|-------|---------|---|---|-----|-----|-----|

| R                  |      | RSBCK | 0       | 0 | 0 | 002 |     | CDO |

| W                  | WCOP | RSBUN | WRTMASK |   |   | CR2 | CR1 | CR0 |

| Reset <sup>1</sup> | 0    | 0     | 0       | 0 | 0 | 0   | 0   | 0   |

1. Refer to Device User Guide (Section: S12XECRG) for reset values of WCOP, CR2, CR1 and CR0.

= Unimplemented or Reserved

#### Figure 8-11. S12XECRG COP Control Register (COPCTL)

Read: Anytime

Write:

- 1. RSBCK: anytime in special modes; write to "1" but not to "0" in all other modes

- 2. WCOP, CR2, CR1, CR0:

- Anytime in special modes

- Write once in all other modes

- Writing CR[2:0] to "000" has no effect, but counts for the "write once" condition.

- Writing WCOP to "0" has no effect, but counts for the "write once" condition.

#### S12XE Clocks and Reset Generator (S12XECRGV1)

The internal reset of the MCU remains asserted while the reset generator completes the 192 SYSCLK long reset sequence. In case the  $\overline{\text{RESET}}$  pin is externally driven low for more than these 192 SYSCLK cycles (External Reset), the internal reset remains asserted longer.

#### 8.5.1.1 Clock Monitor Reset

The S12XECRG generates a Clock Monitor Reset in case all of the following conditions are true:

- Clock monitor is enabled (CME = 1)

- Loss of clock is detected

- Self-Clock Mode is disabled (SCME = 0).

The reset event asynchronously forces the configuration registers to their default settings. In detail the CME and the SCME are reset to logical '1' (which changes the state of the SCME bit. As a consequence the S12XECRG immediately enters Self Clock Mode and starts its internal reset sequence. In parallel the clock quality check starts. As soon as clock quality check indicates a valid Oscillator Clock the S12XECRG switches to OSCCLK and leaves Self Clock Mode. Since the clock quality checker is running in parallel to the reset generator, the S12XECRG may leave Self Clock Mode while still completing the internal reset sequence.

## 8.5.1.2 Computer Operating Properly Watchdog (COP) Reset

When COP is enabled, the S12XECRG expects sequential write of \$55 and \$AA (in this order) to the ARMCOP register during the selected time-out period. Once this is done, the COP time-out period restarts. If the program fails to do this the S12XECRG will generate a reset.

#### 8.5.1.3 Power On Reset, Low Voltage Reset

The on-chip voltage regulator detects when  $V_{DD}$  to the MCU has reached a certain level and asserts power on reset or low voltage reset or both. As soon as a power on reset or low voltage reset is triggered the

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>SLPAK  | <ul> <li>Sleep Mode Acknowledge — This flag indicates whether the MSCAN module has entered sleep mode (see Section 11.4.5.5, "MSCAN Sleep Mode"). It is used as a handshake flag for the SLPRQ sleep mode request. Sleep mode is active when SLPRQ = 1 and SLPAK = 1. Depending on the setting of WUPE, the MSCAN will clear the flag if it detects activity on the CAN bus while in sleep mode.</li> <li>0 Running — The MSCAN operates normally</li> <li>1 Sleep mode active — The MSCAN has entered sleep mode</li> </ul>                                                                      |

| 0<br>INITAK | Initialization Mode Acknowledge — This flag indicates whether the MSCAN module is in initialization mode (see Section 11.4.4.5, "MSCAN Initialization Mode"). It is used as a handshake flag for the INITRQ initialization mode request. Initialization mode is active when INITRQ = 1 and INITAK = 1. The registers CANCTL1, CANBTR0, CANBTR1, CANIDAC, CANIDAR0–CANIDAR7, and CANIDMR0–CANIDMR7 can be written only by the CPU when the MSCAN is in initialization mode.<br>0 Running — The MSCAN operates normally<br>1 Initialization mode active — The MSCAN has entered initialization mode |

#### Table 11-4. CANCTL1 Register Field Descriptions (continued)

### 11.3.2.3 MSCAN Bus Timing Register 0 (CANBTR0)

The CANBTR0 register configures various CAN bus timing parameters of the MSCAN module.

Module Base + 0x0002

Access: User read/write<sup>(1)</sup>

| _      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

| R<br>W | SJW1 | SJW0 | BRP5 | BRP4 | BRP3 | BRP2 | BRP1 | BRP0 |

| Reset: | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

1. Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 11-5. CANBTR0 Register Field Descriptions

Figure 11-6. MSCAN Bus Timing Register 0 (CANBTR0)

| Field           | Description                                                                                                                                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6<br>SJW[1:0] | Synchronization Jump Width — The synchronization jump width defines the maximum number of time quanta (Tq) clock cycles a bit can be shortened or lengthened to achieve resynchronization to data transitions on the CAN bus (see Table 11-6). |

| 5-0<br>BRP[5:0] | Baud Rate Prescaler — These bits determine the time quanta (Tq) clock which is used to build up the bit timing (see Table 11-7).                                                                                                               |

| Table 11-6. Synchronization Jump Width |

|----------------------------------------|

|----------------------------------------|

| SJW1 | SJW0 | Synchronization Jump Width |

|------|------|----------------------------|

| 0    | 0    | 1 Tq clock cycle           |

| 0    | 1    | 2 Tq clock cycles          |

| 1    | 0    | 3 Tq clock cycles          |

| 1    | 1    | 4 Tq clock cycles          |

#### Freescale's Scalable Controller Area Network (S12MSCANV3)

The MSCAN facilitates a sophisticated message storage system which addresses the requirements of a broad range of network applications.

### 11.4.2.1 Message Transmit Background

Modern application layer software is built upon two fundamental assumptions:

- Any CAN node is able to send out a stream of scheduled messages without releasing the CAN bus between the two messages. Such nodes arbitrate for the CAN bus immediately after sending the previous message and only release the CAN bus in case of lost arbitration.

- The internal message queue within any CAN node is organized such that the highest priority message is sent out first, if more than one message is ready to be sent.

The behavior described in the bullets above cannot be achieved with a single transmit buffer. That buffer must be reloaded immediately after the previous message is sent. This loading process lasts a finite amount of time and must be completed within the inter-frame sequence (IFS) to be able to send an uninterrupted stream of messages. Even if this is feasible for limited CAN bus speeds, it requires that the CPU reacts with short latencies to the transmit interrupt.

A double buffer scheme de-couples the reloading of the transmit buffer from the actual message sending and, therefore, reduces the reactiveness requirements of the CPU. Problems can arise if the sending of a message is finished while the CPU re-loads the second buffer. No buffer would then be ready for transmission, and the CAN bus would be released.

At least three transmit buffers are required to meet the first of the above requirements under all circumstances. The MSCAN has three transmit buffers.

The second requirement calls for some sort of internal prioritization which the MSCAN implements with the "local priority" concept described in Section 11.4.2.2, "Transmit Structures."

#### 11.4.2.2 Transmit Structures

The MSCAN triple transmit buffer scheme optimizes real-time performance by allowing multiple messages to be set up in advance. The three buffers are arranged as shown in Figure 11-39.

All three buffers have a 13-byte data structure similar to the outline of the receive buffers (see Section 11.3.3, "Programmer's Model of Message Storage"). An additional Transmit Buffer Priority Register (TBPR) contains an 8-bit local priority field (PRIO) (see Section 11.3.3.4, "Transmit Buffer Priority Register (TBPR)"). The remaining two bytes are used for time stamping of a message, if required (see Section 11.3.3.5, "Time Stamp Register (TSRH–TSRL)").

To transmit a message, the CPU must identify an available transmit buffer, which is indicated by a set transmitter buffer empty (TXEx) flag (see Section 11.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)"). If a transmit buffer is available, the CPU must set a pointer to this buffer by writing to the CANTBSEL register (see Section 11.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). This makes the respective buffer accessible within the CANTXFG address space (see Section 11.3.3, "Programmer's Model of Message Storage"). The algorithmic feature associated with the CANTBSEL register simplifies the transmit buffer selection. In addition, this scheme makes the handler

| Syntax         | Description                                                                                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNC_SEG       | System expects transitions to occur on the CAN bus during this period.                                                                                                   |

| Transmit Point | A node in transmit mode transfers a new value to the CAN bus at this point.                                                                                              |

| Sample Point   | A node in receive mode samples the CAN bus at this point. If the<br>three samples per bit option is selected, then this point marks the<br>position of the third sample. |

#### Table 11-36. Time Segment Syntax

The synchronization jump width (see the Bosch CAN 2.0A/B specification for details) can be programmed in a range of 1 to 4 time quanta by setting the SJW parameter.

The SYNC\_SEG, TSEG1, TSEG2, and SJW parameters are set by programming the MSCAN bus timing registers (CANBTR0, CANBTR1) (see Section 11.3.2.3, "MSCAN Bus Timing Register 0 (CANBTR0)" and Section 11.3.2.4, "MSCAN Bus Timing Register 1 (CANBTR1)").

Table 11-37 gives an overview of the Bosch CAN 2.0A/B specification compliant segment settings and the related parameter values.

#### NOTE

It is the user's responsibility to ensure the bit time settings are in compliance with the CAN standard.

| Time Segment 1 | TSEG1 | Time Segment 2 | TSEG2 | Synchronization<br>Jump Width | SJW |

|----------------|-------|----------------|-------|-------------------------------|-----|

| 5 10           | 4 9   | 2              | 1     | 1 2                           | 0 1 |

| 4 11           | 3 10  | 3              | 2     | 13                            | 0 2 |

| 5 12           | 4 11  | 4              | 3     | 14                            | 03  |

| 6 13           | 5 12  | 5              | 4     | 14                            | 0 3 |

| 7 14           | 6 13  | 6              | 5     | 14                            | 03  |

| 8 15           | 7 14  | 7              | 6     | 14                            | 03  |

| 9 16           | 8 15  | 8              | 7     | 14                            | 03  |

Table 11-37. Bosch CAN 2.0A/B Compliant Bit Time Segment Settings

# 11.4.4 Modes of Operation

## 11.4.4.1 Normal System Operating Modes

The MSCAN module behaves as described within this specification in all normal system operating modes. Write restrictions exist for some registers.

# Chapter 15 Serial Peripheral Interface (S12SPIV5)

Table 15-1. Revision History

| Revision<br>Number | Revision Date | Sections<br>Affected | Description of Changes                 |

|--------------------|---------------|----------------------|----------------------------------------|

| V05.00             | 24 Mar 2005   | 15.3.2/15-439        | - Added 16-bit transfer width feature. |

# 15.1 Introduction

The SPI module allows a duplex, synchronous, serial communication between the MCU and peripheral devices. Software can poll the SPI status flags or the SPI operation can be interrupt driven.

## 15.1.1 Glossary of Terms

| SPI                            | Serial Peripheral Interface      |  |

|--------------------------------|----------------------------------|--|

| SS                             | Slave Select                     |  |

| SCK                            | Serial Clock                     |  |

| MOSI                           | Master Output, Slave Input       |  |

| MISO                           | Master Input, Slave Output       |  |

| MOMI                           | MOMI Master Output, Master Input |  |

| SISO Slave Input, Slave Output |                                  |  |

## 15.1.2 Features

The SPI includes these distinctive features:

- Master mode and slave mode

- Selectable 8 or 16-bit transfer width

- Bidirectional mode

- Slave select output

- Mode fault error flag with CPU interrupt capability

- Double-buffered data register

- Serial clock with programmable polarity and phase

- Control of SPI operation during wait mode

## 15.1.3 Modes of Operation

The SPI functions in three modes: run, wait, and stop.

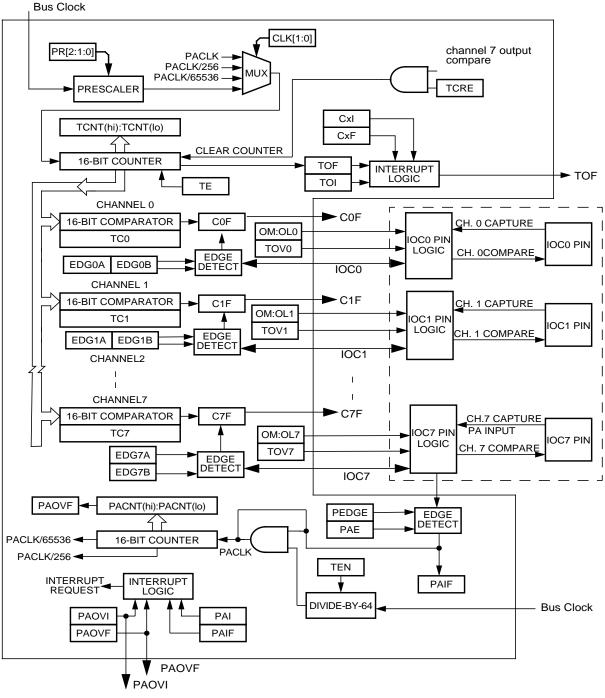

#### Timer Module (TIM16B8CV2)

Figure 16-30. Detailed Timer Block Diagram

## 16.4.1 Prescaler

The prescaler divides the bus clock by 1,2,4,8,16,32,64 or 128. The prescaler select bits, PR[2:0], select the prescaler divisor. PR[2:0] are in timer system control register 2 (TSCR2).

Voltage Regulator (S12VREGL3V3V1)

# 17.2 External Signal Description

Due to the nature of VREG\_3V3 being a voltage regulator providing the chip internal power supply voltages, most signals are power supply signals connected to pads.

Table 17-2 shows all signals of VREG\_3V3 associated with pins.

| Name                   | Function                                       | Reset State | Pull Up |

|------------------------|------------------------------------------------|-------------|---------|

| VDDR                   | Power input (positive supply)                  | —           | —       |

| VDDA                   | Quiet input (positive supply)                  | —           | —       |

| VSSA                   | Quiet input (ground)                           | —           | —       |

| VDDX                   | Power input (positive supply)                  | —           | —       |

| VDD                    | Primary output (positive supply)               | —           | _       |

| VSS                    | Primary output (ground)                        | —           | —       |

| VDDF                   | Secondary output (positive supply)             | —           | —       |

| VDDPLL                 | Tertiary output (positive supply)              | —           | —       |

| VSSPLL                 | Tertiary output (ground)                       | —           | _       |

| VREGEN (optional)      | Optional Regulator Enable                      | —           | —       |

| VREG_API<br>(optional) | VREG Autonomous Periodical<br>Interrupt output |             | —       |

Table 17-2. Signal Properties

#### NOTE

Check device level specification for connectivity of the signals.

# 17.2.1 VDDR — Regulator Power Input Pins

Signal VDDR is the power input of VREG\_3V3. All currents sourced into the regulator loads flow through this pin. A chip external decoupling capacitor (100 nF...220 nF, X7R ceramic) between VDDR and VSSR (if VSSR is not available VSS) can smooth ripple on VDDR.

For entering Shutdown Mode, pin VDDR should also be tied to ground on devices without VREGEN pin.

# 17.2.2 VDDA, VSSA — Regulator Reference Supply Pins

Signals VDDA/VSSA, which are supposed to be relatively quiet, are used to supply the analog parts of the regulator. Internal precision reference circuits are supplied from these signals. A chip external decoupling capacitor (100 nF...220 nF, X7R ceramic) between VDDA and VSSA can further improve the quality of this supply.

# 17.2.3 VDD, VSS — Regulator Output1 (Core Logic) Pins

Signals VDD/VSS are the primary outputs of VREG\_3V3 that provide the power supply for the core logic. These signals are connected to device pins to allow external decoupling capacitors (220 nF, X7R ceramic).

128 KByte Flash Module (S12XFTMR128K1V1)

<sup>1</sup> Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 19.5.

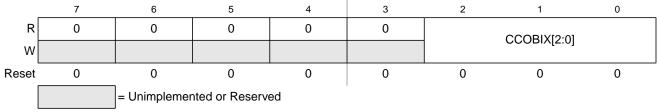

## 19.3.2.3 Flash CCOB Index Register (FCCOBIX)

The FCCOBIX register is used to index the FCCOB register for Flash memory operations.

Offset Module Base + 0x0002

#### Figure 19-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

#### Table 19-11. FCCOBIX Field Descriptions

| Field              | Description                                                                                                                                                                                                                            |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2–0<br>CCOBIX[1:0] | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See Section 19.3.2.11, "Flash Common Command Object Register (FCCOB)," for more details. |

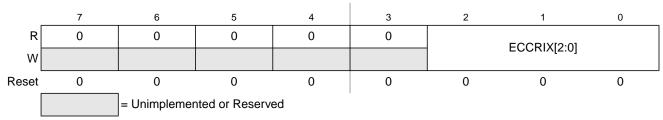

## 19.3.2.4 Flash ECCR Index Register (FECCRIX)

The FECCRIX register is used to index the FECCR register for ECC fault reporting.

Offset Module Base + 0x0003

#### Figure 19-8. FECCR Index Register (FECCRIX)

ECCRIX bits are readable and writable while remaining bits read 0 and are not writable.

#### Table 19-12. FECCRIX Field Descriptions

| Field | Description                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>ECC Error Register Index</b> — The ECCRIX bits are used to select which word of the FECCR register array is being read. See Section 19.3.2.14, "Flash ECC Error Results Register (FECCR)," for more details. |

64 KByte Flash Module (S12XFTMR64K1V1)

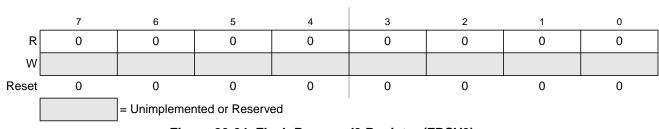

### 20.3.2.17 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

Offset Module Base + 0x0012

Figure 20-24. Flash Reserved3 Register (FRSV3)

All bits in the FRSV3 register read 0 and are not writable.

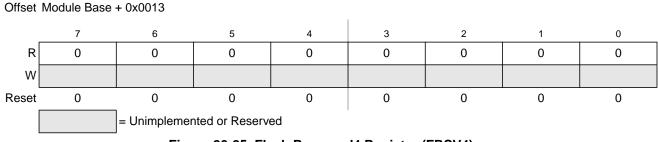

#### 20.3.2.18 Flash Reserved4 Register (FRSV4)

This Flash register is reserved for factory testing.

Figure 20-25. Flash Reserved4 Register (FRSV4)

All bits in the FRSV4 register read 0 and are not writable.

# 20.4 Functional Description

#### 20.4.1 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

- How to write the FCLKDIV register that is used to generate a time base (FCLK) derived from OSCCLK for Flash program and erase command operations

- The command write sequence used to set Flash command parameters and launch execution

- Valid Flash commands available for execution

#### **Detailed Register Address Map**

| Address | Name         |        | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|---------|--------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| 0x0356  | PITCNT3 (hi) | R<br>W | PCNT15 | PCNT14 | PCNT13 | PCNT12 | PCNT11 | PCNT10 | PCNT9 | PCNT8 |

| 0x0357  | PITCNT3 (lo) | R<br>W | PCNT7  | PCNT6  | PCNT5  | PCNT4  | PCNT3  | PCNT2  | PCNT1 | PCNT0 |

| 0x0358– | Reserved     | R      | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| 0x0367  | Reserved     | W      |        |        |        |        |        |        |       |       |

#### 0x0368–0x077F Reserved

| Address | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0368  | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         |          | W |       |       |       |       |       |       |       |       |