Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| -                          |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Details                    |                                                                         |

| Product Status             | Active                                                                  |

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 40MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 44                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 8x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12xs256j0vae |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 7.1.7 C      | omplete Memory Erase (Special Modes)                             | 236 |

|------|--------------|------------------------------------------------------------------|-----|

|      |              | Chapter 8                                                        |     |

|      |              | S12XE Clocks and Reset Generator (S12XECRGV1)                    |     |

| 8.1  |              | on                                                               |     |

|      |              | eatures                                                          |     |

|      |              | Iodes of Operation                                               |     |

|      |              | lock Diagram                                                     |     |

| 8.2  |              | scription                                                        |     |

|      |              | DDPLL, V <sub>SSPLL</sub>                                        |     |

|      |              | ESET                                                             |     |

| 8.3  | •            | Iap and Registers                                                |     |

|      |              | Iodule Memory Map                                                |     |

|      |              | egister Descriptions                                             |     |

| 8.4  |              | Description                                                      |     |

|      |              | unctional Blocks                                                 |     |

|      |              | peration Modes                                                   |     |

|      |              | ow Power Options                                                 |     |

| 8.5  |              |                                                                  |     |

| 0 -  |              | escription of Reset Operation                                    |     |

| 8.6  | _            |                                                                  |     |

|      | 8.6.1 D      | escription of Interrupt Operation                                | 266 |

|      |              | Chapter 9                                                        |     |

|      |              | Pierce Oscillator (S12XOSCLCPV2)                                 |     |

| 9.1  | Introduction | on                                                               | 267 |

|      |              | eatures                                                          |     |

|      |              | Iodes of Operation                                               |     |

|      |              | lock Diagram                                                     |     |

| 9.2  |              | ignal Description                                                |     |

|      | 9.2.1 V      | DDPLL and V <sub>SSPLL</sub> — Operating and Ground Voltage Pins | 268 |

|      |              | XTAL and XTAL — Input and Output Pins                            |     |

| 9.3  |              | Iap and Register Definition                                      |     |

| 9.4  | •            | Description                                                      |     |

|      |              | ain Control                                                      |     |

|      |              | lock Monitor                                                     |     |

|      | 9.4.3 W      | Vait Mode Operation                                              | 270 |

|      |              | top Mode Operation                                               |     |

|      |              | Chapter 10                                                       |     |

|      |              | Analog-to-Digital Converter (ADC12B16CV1)                        |     |

| 10.1 | Introduction | on                                                               | 271 |

|      |              | eatures                                                          |     |

|      |              | Iodes of Operation                                               |     |

|      |              | - r                                                              |     |

|      |              |                                                                  |     |

S12XS Family Reference Manual, Rev. 1.13

Freescale Semiconductor

# 1.1.4 Device Memory Map

Table 1-1 shows the device register memory map.

Table 1-1. Device Register Memory Map

| Address       | Module                                               | Size<br>(Bytes) |

|---------------|------------------------------------------------------|-----------------|

| 0x0000-0x0009 | PIM (port integration module)                        | 10              |

| 0x000A-0x000B | MMC (memory map control)                             | 2               |

| 0x000C-0x000D | PIM (port integration module)                        | 2               |

| 0x000E-0x000F | Reserved                                             | 2               |

| 0x0010-0x0017 | MMC (memory map control)                             | 8               |

| 0x0018-0x0019 | Reserved                                             | 2               |

| 0x001A-0x001B | Device ID register                                   | 2               |

| 0x001C-0x001F | PIM (port integration module)                        | 4               |

| 0x0020-0x002F | DBG (debug module)                                   | 16              |

| 0x0030-0x0031 | Reserved                                             | 2               |

| 0x0032-0x0033 | PIM (port integration module)                        | 2               |

| 0x0034-0x003F | ECRG (clock and reset generator)                     | 12              |

| 0x0040-0x006F | TIM (timer module)                                   | 48              |

| 0x0070-0x00C7 | Reserved                                             | 88              |

| 0x00C8-0x00CF | SCI0 (serial communications interface)               | 8               |

| 0x00D0-0x00D7 | SCI1 (serial communications interface)               | 8               |

| 0x00D8-0x00DF | SPI0 (serial peripheral interface)                   | 8               |

| 0x00E0-0x00FF | Reserved                                             | 32              |

| 0x0100-0x0113 | FTMR control registers                               | 20              |

| 0x0114-0x011F | Reserved                                             | 12              |

| 0x0120-0x012F | INT (interrupt module)                               | 16              |

| 0x0130-0x013F | Reserved                                             | 16              |

| 0x0140-0x017F | CAN0                                                 | 64              |

| 0x0180-0x023F | Reserved                                             | 192             |

| 0x0240-0x027F | PIM (port integration module)                        | 64              |

| 0x0280-0x02BF | Reserved                                             | 64              |

| 0x02C0-0x02EF | ATD0 (analog-to-digital converter 12 bit 16-channel) | 48              |

| 0x02F0-0x02F7 | Voltage regulator                                    | 8               |

| 0x02F8-0x02FF | Reserved                                             | 8               |

| 0x0300-0x0327 | PWM (pulse-width modulator 8 channels)               | 40              |

| 0x0328-0x033F | Reserved                                             | 24              |

| 0x0340-0x0367 | PIT (periodic interrupt timer)                       | 40              |

S12XS Family Reference Manual, Rev. 1.13

|           | Mode                       |                   |                                                            |  |  |  |

|-----------|----------------------------|-------------------|------------------------------------------------------------|--|--|--|

| Pulse     | STOR                       | STOP <sup>1</sup> |                                                            |  |  |  |

|           |                            | Unit              |                                                            |  |  |  |

| Ignored   | t <sub>pulse</sub> ≤ 3     | bus clocks        | $t_{\text{pulse}} \leq t_{\text{pign}}$                    |  |  |  |

| Uncertain | 3 < t <sub>pulse</sub> < 4 | bus clocks        | t <sub>pign</sub> < t <sub>pulse</sub> < t <sub>pval</sub> |  |  |  |

| Valid     | t <sub>pulse</sub> ≥ 4     | bus clocks        | $t_{\text{pulse}} \ge t_{\text{pval}}$                     |  |  |  |

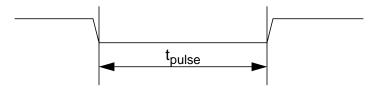

Table 2-72. Pulse Detection Criteria

<sup>&</sup>lt;sup>1</sup>These values include the spread of the oscillator frequency over temperature, voltage and process.

Figure 2-75. Pulse Illustration

A valid edge on an input is detected if 4 consecutive samples of a passive level are followed by 4 consecutive samples of an active level directly or indirectly.

The filters are continuously clocked by the bus clock in RUN and WAIT mode. In STOP mode the clock is generated by an RC-oscillator in the Port Integration Module. To maximize current saving the RC oscillator runs only if the following condition is true on any pin individually:

Sample count <= 4 and interrupt enabled (PIE=1) and interrupt flag not set (PIF=0).

#### 2.5 Initialization Information

## 2.5.1 Port Data and Data Direction Register writes

It is not recommended to write PORTx/PTx and DDRx in a word access. When changing the register pins from inputs to outputs, the data may have extra transitions during the write access. Initialize the port data register before enabling the outputs.

S12X Debug (S12XDBGV3) Module

#### 6.4.5.3.1 Information Byte Organization

The format of the control information byte is dependent upon the active trace mode as described below. In Normal, Loop1, or Pure PC modes tracing of CPU12X activity, CINF is used to store control information. In Detail Mode, CXINF contains the control information.

#### **CPU12X Information Byte**

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |   |

|-------|-------|-------|-------|-------|-------|-------|-------|---|

| CSD   | CVA   | 0     | CDV   | 0     | 0     | 0     | 0     | ] |

Figure 6-23. CPU12X Information Byte CINF

#### **Table 6-41. CINF Field Descriptions**

| Field    | Description                                                                                                                                                                                                                                                                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CSD | Source Destination Indicator — This bit indicates if the corresponding stored address is a source or destination address. This is only used in Normal and Loop1 mode tracing.  O Source address  Destination address                                                                                                                                                 |

| 6<br>CVA | Vector Indicator — This bit indicates if the corresponding stored address is a vector address. Vector addresses are destination addresses, thus if CVA is set, then the corresponding CSD is also set. This is only used in Normal and Loop1 mode tracing. This bit has no meaning in Pure PC mode.  0 Indexed jump destination address 1 Vector destination address |

| 4<br>CDV | Data Invalid Indicator — This bit indicates if the trace buffer entry is invalid. It is only used when tracing from both sources in Normal, Loop1 and Pure PC modes, to indicate that the CPU12X trace buffer entry is valid.  0 Trace buffer entry is invalid 1 Trace buffer entry is valid                                                                         |

#### **CXINF Information Byte**

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|

|       | CSZ   | CRW   |       |       |       |       |       |  |

Figure 6-24. Information Byte CXINF

This describes the format of the information byte used only when tracing in Detail Mode. When tracing from the CPU12X in Detail Mode, information is stored to the trace buffer on all cycles except opcode fetch and free cycles. In this case the CSZ and CRW bits indicate the type of access being made by the CPU12X.

**Table 6-42. CXINF Field Descriptions**

| Field    | Description                                                                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>CSZ | Access Type Indicator — This bit indicates if the access was a byte or word size access. This bit only contains valid information when tracing CPU12X activity in Detail Mode.  0 Word Access  1 Byte Access |

S12XS Family Reference Manual, Rev. 1.13

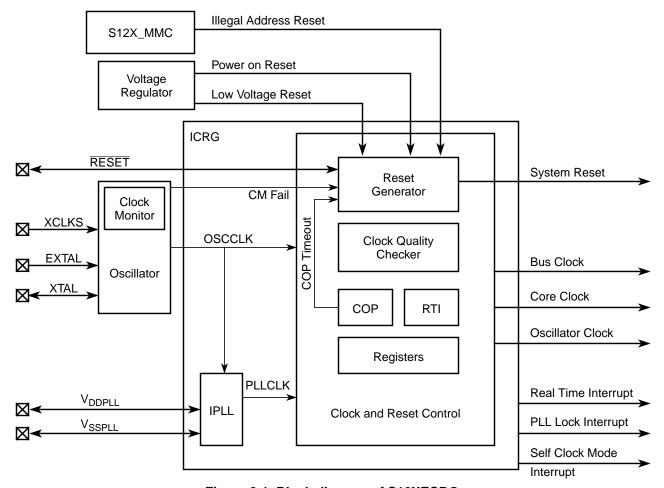

# Chapter 8 S12XE Clocks and Reset Generator (S12XECRGV1)

**Table 8-1. Revision History**

| Revision<br>Number | Revision<br>Date | Sections<br>Affected           | Description of Changes                                                                                                                     |

|--------------------|------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| V01.00             | 26 Oct. 2005     |                                | Initial release                                                                                                                            |

| V01.01             | 02 Nov 2006      | 8.4.1.1/8-254                  | Table "Examples of IPLL Divider settings": corrected \$32 to \$31                                                                          |

| V01.02             | 4 Mar. 2008      | 8.4.1.4/8-257<br>8.4.3.3/8-261 | Corrected details                                                                                                                          |

| V01.03             | 1 Sep. 2008      | Table 8-14                     | added 100MHz example for PLL                                                                                                               |

| V01.04             | 20 Nov. 2008     | 8.3.2.4/8-243                  | S12XECRG Flags Register: corrected address to Module Base + 0x0003                                                                         |

| V01.05             | 19. Sep 2009     | 8.5.1/8-263                    | Modified Note below Table 8-17./8-263                                                                                                      |

| V01.06             | 18. Sep 2012     | Table 8-14<br>8.5.1            | Added footnote concerning maximum clock frequencies to table Removed redundant examples from table Replaced reference to MMC documentation |

#### 8.1 Introduction

This specification describes the function of the Clocks and Reset Generator (S12XECRG).

#### 8.1.1 Features

The main features of this block are:

- Phase Locked Loop (IPLL) frequency multiplier with internal filter

- Reference divider

- Post divider

- Configurable internal filter (no external pin)

- Optional frequency modulation for defined jitter and reduced emission

- Automatic frequency lock detector

- Interrupt request on entry or exit from locked condition

- Self Clock Mode in absence of reference clock

- System Clock Generator

- Clock Quality Check

- User selectable fast wake-up from Stop in Self-Clock Mode for power saving and immediate program execution

- Clock switch for either Oscillator or PLL based system clocks

- Computer Operating Properly (COP) watchdog timer with time-out clear window.

S12XS Family Reference Manual, Rev. 1.13

Figure 8-1. Block diagram of S12XECRG

# 8.2 Signal Description

This section lists and describes the signals that connect off chip.

# 8.2.1 V<sub>DDPLL</sub>, V<sub>SSPLL</sub>

These pins provides operating voltage ( $V_{DDPLL}$ ) and ground ( $V_{SSPLL}$ ) for the IPLL circuitry. This allows the supply voltage to the IPLL to be independently bypassed. Even if IPLL usage is not required  $V_{DDPLL}$  and  $V_{SSPLL}$  must be connected to properly.

## 8.2.2 **RESET**

RESET is an active low bidirectional reset pin. As an input it initializes the MCU asynchronously to a known start-up state. As an open-drain output it indicates that an system reset (internal to MCU) has been triggered.

S12XE Clocks and Reset Generator (S12XECRGV1)

Table 8-8. FM Amplitude selection

| FM1 | FM0 | FM Amplitude / f <sub>VCO</sub> Variation |

|-----|-----|-------------------------------------------|

| 0   | 0   | FM off                                    |

| 0   | 1   | ±1%                                       |

| 1   | 0   | ±2%                                       |

| 1   | 1   | ±4%                                       |

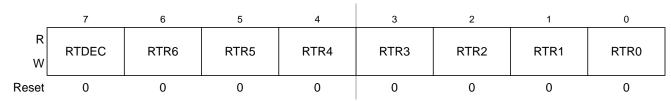

## 8.3.2.8 S12XECRG RTI Control Register (RTICTL)

This register selects the timeout period for the Real Time Interrupt.

Module Base + 0x0007

Figure 8-10. S12XECRG RTI Control Register (RTICTL)

Read: Anytime

Write: Anytime

#### **NOTE**

A write to this register initializes the RTI counter.

**Table 8-9. RTICTL Field Descriptions**

| Field           | Description                                                                                                                                                                                                                                                                  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTDEC      | Decimal or Binary Divider Select Bit — RTDEC selects decimal or binary based prescaler values.  0 Binary based divider value. See Table 8-10  1 Decimal based divider value. See Table 8-11                                                                                  |

| 6–4<br>RTR[6:4] | Real Time Interrupt Prescale Rate Select Bits — These bits select the prescale rate for the RTI. See Table 8-10 and Table 8-11.                                                                                                                                              |

| 3–0<br>RTR[3:0] | Real Time Interrupt Modulus Counter Select Bits — These bits select the modulus counter target value to provide additional granularity. Table 8-10 and Table 8-11 show all possible divide values selectable by the RTICTL register. The source clock for the RTI is OSCCLK. |

Table 8-10. RTI Frequency Divide Rates for RTDEC = 0

| RTR[3:0]  | RTR[6:4] =         |                           |                           |                           |                           |                           |                           |                           |

|-----------|--------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

|           | 000<br>(OFF)       | 001<br>(2 <sup>10</sup> ) | 010<br>(2 <sup>11</sup> ) | 011<br>(2 <sup>12</sup> ) | 100<br>(2 <sup>13</sup> ) | 101<br>(2 <sup>14</sup> ) | 110<br>(2 <sup>15</sup> ) | 111<br>(2 <sup>16</sup> ) |

| 0000 (÷1) | OFF <sup>(1)</sup> | 2 <sup>10</sup>           | 2 <sup>11</sup>           | 2 <sup>12</sup>           | 2 <sup>13</sup>           | 2 <sup>14</sup>           | 2 <sup>15</sup>           | 2 <sup>16</sup>           |

S12XS Family Reference Manual, Rev. 1.13

Table 10-22. Conversion result mapping to ATDDRn

| A/D resolution | DJM | conversion result mapping to ATDDR <i>n</i> |

|----------------|-----|---------------------------------------------|

| 8-bit data     | 0   | Bit[11:4] = result, Bit[3:0]=0000           |

| 8-bit data     | 1   | Bit[7:0] = result, Bit[11:8]=0000           |

| 10-bit data    | 0   | Bit[11:2] = result, Bit[1:0]=00             |

| 10-bit data    | 1   | Bit[9:0] = result, Bit[11:10]=00            |

| 12-bit data    | Х   | Bit[11:0] = result                          |

## 10.4 Functional Description

The ADC12B16C is structured into an analog sub-block and a digital sub-block.

## 10.4.1 Analog Sub-Block

The analog sub-block contains all analog electronics required to perform a single conversion. Separate power supplies  $V_{DDA}$  and  $V_{SSA}$  allow to isolate noise of other MCU circuitry from the analog sub-block.

#### 10.4.1.1 Sample and Hold Machine

The Sample and Hold (S/H) Machine accepts analog signals from the external world and stores them as capacitor charge on a storage node.

During the sample process the analog input connects directly to the storage node.

The input analog signals are unipolar and must fall within the potential range of V<sub>SSA</sub> to V<sub>DDA</sub>.

During the hold process the analog input is disconnected from the storage node.

# 10.4.1.2 Analog Input Multiplexer

The analog input multiplexer connects one of the 16 external analog input channels to the sample and hold machine.

## 10.4.1.3 Analog-to-Digital (A/D) Machine

The A/D Machine performs analog to digital conversions. The resolution is program selectable at either 8 or 10 or 12 bits. The A/D machine uses a successive approximation architecture. It functions by comparing the stored analog sample potential with a series of digitally generated analog potentials. By following a binary search algorithm, the A/D machine locates the approximating potential that is nearest to the sampled potential.

When not converting the A/D machine is automatically powered down.

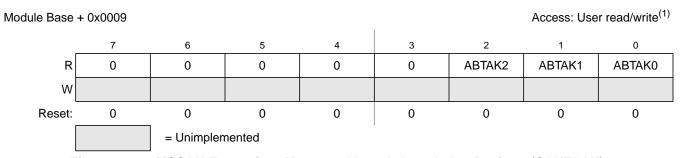

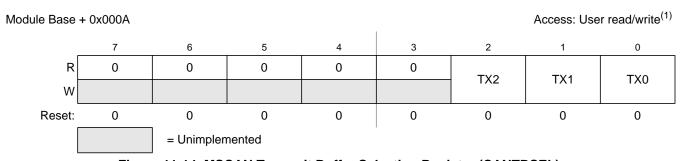

## 11.3.2.10 MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

The CANTAAK register indicates the successful abort of a queued message, if requested by the appropriate bits in the CANTARQ register.

Figure 11-13. MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

1. Read: Anytime

Write: Unimplemented

#### NOTE

The CANTAAK register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1).

**Table 11-16. CANTAAK Register Field Descriptions**

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0<br>ABTAK[2:0] | Abort Acknowledge — This flag acknowledges that a message was aborted due to a pending abort request from the CPU. After a particular message buffer is flagged empty, this flag can be used by the application software to identify whether the message was aborted successfully or was sent anyway. The ABTAKx flag is cleared whenever the corresponding TXE flag is cleared.  1 The message was aborted. |

## 11.3.2.11 MSCAN Transmit Buffer Selection Register (CANTBSEL)

The CANTBSEL register allows the selection of the actual transmit message buffer, which then will be accessible in the CANTXFG register space.

Figure 11-14. MSCAN Transmit Buffer Selection Register (CANTBSEL)

1. Read: Find the lowest ordered bit set to 1, all other bits will be read as 0 Write: Anytime when not in initialization mode

S12XS Family Reference Manual Rev. 1.13

#### 13.2.1 PWM7 — PWM Channel 7

This pin serves as waveform output of PWM channel 7 and as an input for the emergency shutdown feature.

#### 13.2.2 **PWM6** — **PWM** Channel 6

This pin serves as waveform output of PWM channel 6.

#### 13.2.3 **PWM5** — **PWM** Channel 5

This pin serves as waveform output of PWM channel 5.

#### 13.2.4 PWM4 — PWM Channel 4

This pin serves as waveform output of PWM channel 4.

#### 13.2.5 **PWM3** — **PWM** Channel 3

This pin serves as waveform output of PWM channel 3.

#### 13.2.6 **PWM3** — **PWM** Channel 2

This pin serves as waveform output of PWM channel 2.

#### 13.2.7 PWM3 — PWM Channel 1

This pin serves as waveform output of PWM channel 1.

#### 13.2.8 **PWM3** — **PWM** Channel 0

This pin serves as waveform output of PWM channel 0.

## 13.3 Memory Map and Register Definition

This section describes in detail all the registers and register bits in the PWM module.

The special-purpose registers and register bit functions that are not normally available to device end users, such as factory test control registers and reserved registers, are clearly identified by means of shading the appropriate portions of address maps and register diagrams. Notes explaining the reasons for restricting access to the registers and functions are also explained in the individual register descriptions.

## 13.3.1 Module Memory Map

This section describes the content of the registers in the PWM module. The base address of the PWM module is determined at the MCU level when the MCU is defined. The register decode map is fixed and begins at the first address of the module address offset. The figure below shows the registers associated

S12XS Family Reference Manual, Rev. 1.13

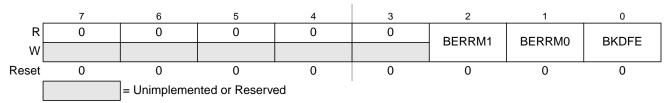

## 14.3.2.5 SCI Alternative Control Register 2 (SCIACR2)

Module Base + 0x0002

Figure 14-8. SCI Alternative Control Register 2 (SCIACR2)

Read: Anytime, if AMAP = 1 Write: Anytime, if AMAP = 1

#### Table 14-8. SCIACR2 Field Descriptions

| Field             | Description                                                                                                                              |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 2:1<br>BERRM[1:0] | Bit Error Mode — Those two bits determines the functionality of the bit error detect feature. See Table 14-9.                            |

| 0<br>BKDFE        | Break Detect Feature Enable — BKDFE enables the break detect circuitry.  0 Break detect circuit disabled  1 Break detect circuit enabled |

#### **Table 14-9. Bit Error Mode Coding**

| BERRM1 | BERRM0 | Function                                                                                             |

|--------|--------|------------------------------------------------------------------------------------------------------|

| 0      | 0      | Bit error detect circuit is disabled                                                                 |

| 0      | 1      | Receive input sampling occurs during the 9th time tick of a transmitted bit (refer to Figure 14-19)  |

| 1      | 0      | Receive input sampling occurs during the 13th time tick of a transmitted bit (refer to Figure 14-19) |

| 1      | 1      | Reserved                                                                                             |

Voltage Regulator (S12VREGL3V3V1)

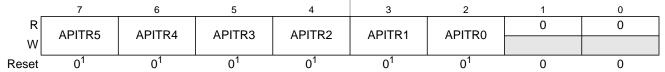

# 17.3.2.4 Autonomous Periodical Interrupt Trimming Register (VREGAPITR)

The VREGAPITR register allows to trim the API timeout period.

0x02F3

1. Reset value is either 0 or preset by factory. See Section 1 (Device Overview) for details.

= Unimplemented or Reserved

Figure 17-4. Autonomous Periodical Interrupt Trimming Register (VREGAPITR)

**Table 17-7. VREGAPITR Field Descriptions**

| Field             | Description                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------|

| 7–2<br>APITR[5:0] | Autonomous Periodical Interrupt Period Trimming Bits — See Table 17-8 for trimming effects. |

Table 17-8. Trimming Effect of APIT

| Bit      | Trimming Effect                                  |

|----------|--------------------------------------------------|

| APITR[5] | Increases period                                 |

| APITR[4] | Decreases period less than APITR[5] increased it |

| APITR[3] | Decreases period less than APITR[4]              |

| APITR[2] | Decreases period less than APITR[3]              |

| APITR[1] | Decreases period less than APITR[2]              |

| APITR[0] | Decreases period less than APITR[1]              |

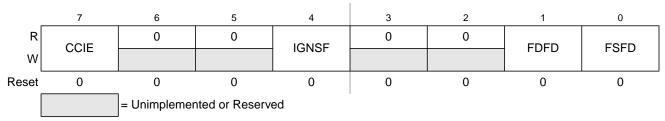

## 18.3.2.5 Flash Configuration Register (FCNFG)

The FCNFG register enables the Flash command complete interrupt and forces ECC faults on Flash array read access from the CPU or XGATE.

Offset Module Base + 0x0004

Figure 18-9. Flash Configuration Register (FCNFG)

CCIE, IGNSF, FDFD, and FSFD bits are readable and writable while remaining bits read 0 and are not writable.

Table 18-13. FCNFG Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>CCIE  | Command Complete Interrupt Enable — The CCIE bit controls interrupt generation when a Flash command has completed.  0 Command complete interrupt disabled  1 An interrupt will be requested whenever the CCIF flag in the FSTAT register is set (see Section 18.3.2.7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 4<br>IGNSF | Ignore Single Bit Fault — The IGNSF controls single bit fault reporting in the FERSTAT register (see Section 18.3.2.8).  O All single bit faults detected during array reads are reported  Single bit faults detected during array reads are not reported and the single bit fault interrupt will not be generated                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 1<br>FDFD  | Force Double Bit Fault Detect — The FDFD bit allows the user to simulate a double bit fault during Flash array read operations and check the associated interrupt routine. The FDFD bit is cleared by writing a 0 to FDFD. The FECCR registers will not be updated during the Flash array read operation with FDFD set unless an actual double bit fault is detected.  O Flash array read operations will set the DFDIF flag in the FERSTAT register only if a double bit fault is detected 1 Any Flash array read operation will force the DFDIF flag in the FERSTAT register to be set (see Section 18.3.2.7) and an interrupt will be generated as long as the DFDIE interrupt enable in the FERCNFG register is set (see Section 18.3.2.6) |  |  |  |  |  |  |

| 0<br>FSFD  | Force Single Bit Fault Detect — The FSFD bit allows the user to simulate a single bit fault during Flash array read operations and check the associated interrupt routine. The FSFD bit is cleared by writing a 0 to FSFD. The FECCR registers will not be updated during the Flash array read operation with FSFD set unless an actual single bit fault is detected.  0 Flash array read operations will set the SFDIF flag in the FERSTAT register only if a single bit fault is detected.  1 Flash array read operation will force the SFDIF flag in the FERSTAT register to be set (see Section 18.3.2.7) and an interrupt will be generated as long as the SFDIE interrupt enable in the FERCNFG register is set (see Section 18.3.2.6)   |  |  |  |  |  |  |

## **18.3.2.6** Flash Error Configuration Register (FERCNFG)

The FERCNFG register enables the Flash error interrupts for the FERSTAT flags.

128 KByte Flash Module (S12XFTMR128K1V1)

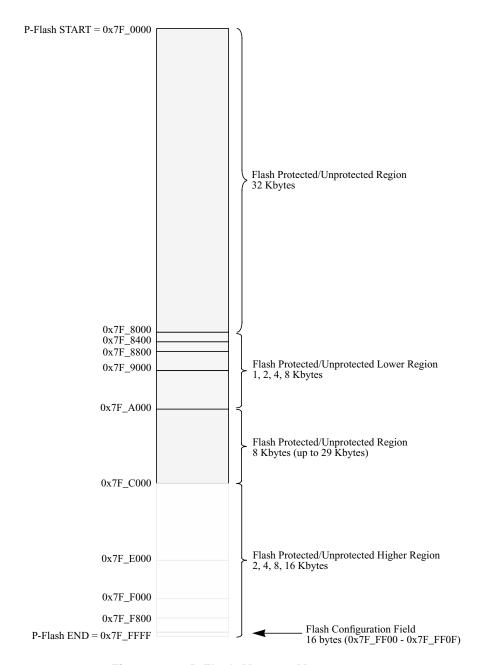

Table 19-20. P-Flash Protection Lower Address Range

| FPLS[1:0] | Global Address Range | Protected Size |  |  |

|-----------|----------------------|----------------|--|--|

| 00        | 0x7F_8000-0x7F_83FF  | 1 Kbyte        |  |  |

| 01        | 0x7F_8000-0x7F_87FF  | 2 Kbytes       |  |  |

| 10        | 0x7F_8000-0x7F_8FFF  | 4 Kbytes       |  |  |

| 11        | 0x7F_8000-0x7F_9FFF  | 8 Kbytes       |  |  |

All possible P-Flash protection scenarios are shown in Figure 19-14. Although the protection scheme is loaded from the Flash memory at global address 0x7F\_FF0C during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

128 KByte Flash Module (S12XFTMR128K1V1)

#### 19.3.2.9.1 P-Flash Protection Restrictions

The general guideline is that P-Flash protection can only be added and not removed. Table 19-21 specifies all valid transitions between P-Flash protection scenarios. Any attempt to write an invalid scenario to the FPROT register will be ignored. The contents of the FPROT register reflect the active protection scenario. See the FPHS and FPLS bit descriptions for additional restrictions.

| From<br>Protection<br>Scenario | To Protection Scenario <sup>1</sup> |   |   |   |   |   |   |   |  |

|--------------------------------|-------------------------------------|---|---|---|---|---|---|---|--|

|                                | 0                                   | 1 | 2 | 3 | 4 | 5 | 6 | 7 |  |

| 0                              | Х                                   | Х | Х | Х |   |   |   |   |  |

| 1                              |                                     | Х |   | Х |   |   |   |   |  |

| 2                              |                                     |   | Х | Х |   |   |   |   |  |

| 3                              |                                     |   |   | Х |   |   |   |   |  |

| 4                              |                                     |   |   | Х | Х |   |   |   |  |

| 5                              |                                     |   | Х | Х | Х | Х |   |   |  |

| 6                              |                                     | Х |   | Х | Х |   | Х |   |  |

| 7                              | Х                                   | Х | Х | Х | Х | Х | Х | Х |  |

Table 19-21. P-Flash Protection Scenario Transitions

#### 19.3.2.10 D-Flash Protection Register (DFPROT)

The DFPROT register defines which D-Flash sectors are protected against program and erase operations.

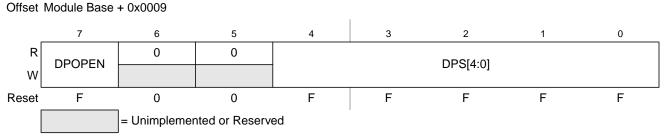

Figure 19-15. D-Flash Protection Register (DFPROT)

The (unreserved) bits of the DFPROT register are writable with the restriction that protection can be added but not removed. Writes must increase the DPS value and the DPOEN bit can only be written from 1 (protection disabled) to 0 (protection enabled). If the DPOPEN bit is set, the state of the DPS bits is irrelevant.

During the reset sequence, the DFPROT register is loaded with the contents of the D-Flash protection byte in the Flash configuration field at global address  $0x7F_FF0D$  located in P-Flash memory (see Table 19-3) as indicated by reset condition F in Figure 19-15. To change the D-Flash protection that will be loaded during the reset sequence, the P-Flash sector containing the D-Flash protection byte must be unprotected, then the D-Flash protection byte must be programmed. If a double bit fault is detected while reading the

578 Freescale Semiconductor

#### S12XS Family Reference Manual, Rev. 1.13

Allowed transitions marked with X, see Figure 19-14 for a definition of the scenarios.

64 KByte Flash Module (S12XFTMR64K1V1)

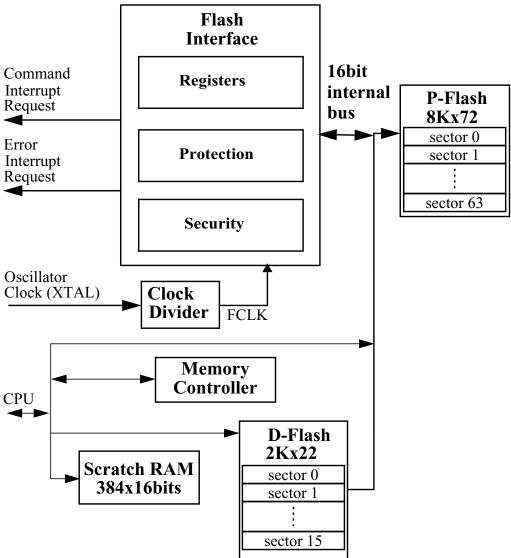

## 20.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 20-1.

Figure 20-1. FTMR64K1 Block Diagram

## 20.2 External Signal Description

The Flash module contains no signals that connect off-chip.

Figure 20-2. P-Flash Memory Map

#### A.1.3.4 TEST

This pin is used for production testing only. The TEST pin must be tied to V<sub>SS</sub> in all applications.

## A.1.4 Current Injection

Power supply must maintain regulation within operating  $V_{DD35}$  or  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD35}$ ) is greater than  $I_{DD35}$ , the injection current may flow out of  $V_{DD35}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD35}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power; e.g., if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

## A.1.5 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only. A functional operation under or outside those maxima is not guaranteed. Stress beyond those limits may affect the reliability or cause permanent damage of the device.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either  $V_{SS35}$  or  $V_{DD35}$ ).

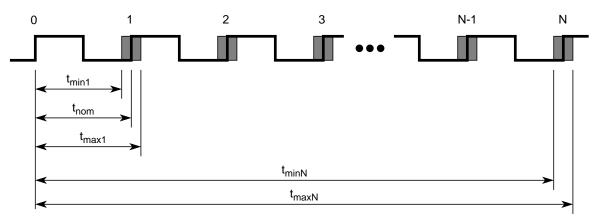

## A.6.3 Phase Locked Loop

#### A.6.3.1 Jitter Information

With each transition of the clock  $f_{cmp}$ , the deviation from the reference clock  $f_{ref}$  is measured and input voltage to the VCO is adjusted accordingly. The adjustment is done continuously with no abrupt changes in the clock output frequency. Noise, voltage, temperature and other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real minimum and maximum clock periods as illustrated in Figure A-4.

Figure A-4. Jitter Definitions

The relative deviation of  $t_{nom}$  is at its maximum for one clock period, and decreases towards zero for larger number of clock periods (N).

Defining the jitter as:

$$J(N) = \max \left( \left| 1 - \frac{t_{max}(N)}{N \cdot t_{nom}} \right|, \left| 1 - \frac{t_{min}(N)}{N \cdot t_{nom}} \right| \right)$$

#### **Detailed Register Address Map**

## 0x0240-0x027F Port Integration Module (PIM) Map 5 of 5

| Address | Name     |             | Bit 7  | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-------------|--------|--------|-------|--------|-------|-------|-------|-------|

| 0x0248  | PTS      | R<br>W      | PTS7   | PTS6   | PTS5  | PTS4   | PTS3  | PTS2  | PTS1  | PTS0  |

| 0x0249  | PTIS     | R<br>W      | PTIS7  | PTIS6  | PTIS5 | PTIS4  | PTIS3 | PTIS2 | PTIS1 | PTIS0 |

| 0x024A  | DDRS     | R<br>W      | DDRS7  | DDRS6  | DDRS5 | DDRS4  | DDRS3 | DDRS2 | DDRS1 | DDRS0 |

| 0x024B  | RDRS     | R<br>W      | RDRS7  | RDRS6  | RDRS5 | RDRS4  | RDRS3 | RDRS2 | RDRS1 | RDRS0 |

| 0x024C  | PERS     | R<br>W      | PERS7  | PERS6  | PERS5 | PERS4  | PERS3 | PERS2 | PERS1 | PERS0 |

| 0x024D  | PPSS     | R<br>W      | PPSS7  | PPSS6  | PPSS5 | PPSS4  | PPSS3 | PPSS2 | PPSS1 | PPSS0 |

| 0x024E  | WOMS     | R<br>W      | WOMS7  | WOMS6  | WOMS5 | WOMS4  | WOMS3 | WOMS2 | WOMS1 | WOMS0 |

| 0x024F  | Reserved | R<br>W      | 0      | 0      | 0     | 0      | 0     | 0     | 0     | 0     |

| 0x0250  | PTM      | R<br>W      | PTM7   | PTM6   | PTM5  | PTM4   | PTM3  | PTM2  | PTM1  | PTM0  |

| 0x0251  | PTIM     | R           | PTIM7  | PTIM6  | PTIM5 | PTIM4  | PTIM3 | PTIM2 | PTIM1 | PTIM0 |

| 0x0252  | DDRM     | W<br>R<br>W | DDRM7  | DDRM6  | DDRM5 | DDRM4  | DDRM3 | DDRM2 | DDRM1 | DDRM0 |

| 0x0253  | RDRM     | R<br>W      | RDRM7  | RDRM6  | RDRM5 | RDRM4  | RDRM3 | RDRM2 | RDRM1 | RDRM0 |

| 0x0254  | PERM     | R<br>W      | PERM7  | PERM6  | PERM5 | PERM4  | PERM3 | PERM2 | PERM1 | PERM0 |

| 0x0255  | PPSM     | R<br>W      | PPSM7  | PPSM6  | PPSM5 | PPSM4  | PPSM3 | PPSM2 | PPSM1 | PPSM0 |

| 0x0256  | WOMM     | R<br>W      | WOMM7  | WOMM6  | WOMM5 | WOMM4  | WOMM3 | WOMM2 | WOMM1 | WOMM0 |

| 0x0257  | MODRR    | R<br>W      | MODRR7 | MODRR6 | 0     | MODRR4 | 0     | 0     | 0     | 0     |

| 0x0258  | PTP      | R<br>W      | PTP7   | PTP6   | PTP5  | PTP4   | PTP3  | PTP2  | PTP1  | PTP0  |

| 0x0259  | PTIP     | R<br>W      | PTIP7  | PTIP6  | PTIP5 | PTIP4  | PTIP3 | PTIP2 | PTIP1 | PTIP0 |

| 0x025A  | DDRP     | R<br>W      | DDRP7  | DDRP6  | DDRP5 | DDRP4  | DDRP3 | DDRP2 | DDRP1 | DDRP0 |

| 0x025B  | RDRP     | R<br>W      | RDRP7  | RDRP6  | RDRP5 | RDRP4  | RDRP3 | RDRP2 | RDRP1 | RDRP0 |

| 0x025C  | PERP     | R<br>W      | PERP7  | PERP6  | PERP5 | PERP4  | PERP3 | PERP2 | PERP1 | PERP0 |

| 0x025D  | PPSP     | R<br>W      | PPSP7  | PPSP6  | PPSP5 | PPSP4  | PPSP3 | PPSP2 | PPSP1 | PPSS0 |

| 0x025E  | PIEP     | R<br>W      | PIEP7  | PIEP6  | PIEP5 | PIEP4  | PIEP3 | PIEP2 | PIEP1 | PIEP0 |

| 0x025F  | PIFP     | R<br>W      | PIFP7  | PIFP6  | PIFP5 | PIFP4  | PIFP3 | PIFP2 | PIFP1 | PIFP0 |