Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | HCS12X                                                      |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 40MHz                                                       |

| Connectivity               | CANbus, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 44                                                          |

| Program Memory Size        | 64KB (64K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 4K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                |

| Data Converters            | A/D 8x12b                                                   |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 64-LQFP                                                     |

| Supplier Device Package    | 64-LQFP (10x10)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s12xs64j1cae |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register<br>Name                                 |        | Bit 7 | 6             | 5              | 4           | 3           | 2     | 1     | Bit 0 |

|--------------------------------------------------|--------|-------|---------------|----------------|-------------|-------------|-------|-------|-------|

| 0x001C<br>ECLKCTL                                | R<br>W | NECLK | NCLKX2        | DIV16          | EDIV4       | EDIV3       | EDIV2 | EDIV1 | EDIV0 |

| 0x001D                                           | R      | 0     | 0             | 0              | 0           | 0           | 0     | 0     | 0     |

| Reserved                                         | W      |       |               |                |             |             |       |       |       |

| 0x001E<br>IRQCR                                  | R<br>W | IRQE  | IRQEN         | 0              | 0           | 0           | 0     | 0     | 0     |

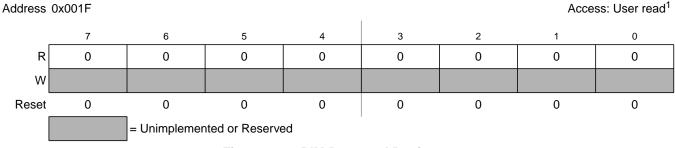

| 0x001F                                           | R      | 0     | 0             | 0              | 0           | 0           | 0     | 0     | 0     |

| Reserved                                         | W      |       |               |                |             |             |       |       |       |

| 0x0020–<br>0x0031<br>Non-PIM<br>Address<br>Range | R<br>W |       |               |                | Non-PIM Add | dress Range |       |       |       |

| 0x0032<br>PORTK                                  | R<br>W | PK7   | 0             | PK5            | PK4         | PK3         | PK2   | PK1   | PK0   |

| 0x0033<br>DDRK                                   | R<br>W | DDRK7 | 0             | DDRK5          | DDRK4       | DDRK3       | DDRK2 | DDRK1 | DDRK0 |

| 0x0034–<br>0x023F<br>Non-PIM<br>Address<br>Range | R<br>W |       |               |                | Non-PIM Ade | dress Range |       |       |       |

| 0x0240<br>PTT                                    | R<br>W | PTT7  | PTT6          | PTT5           | PTT4        | PTT3        | PTT2  | PTT1  | PTT0  |

| 0x0241                                           | R      | PTIT7 | PTIT6         | PTIT5          | PTIT4       | PTIT3       | PTIT2 | PTIT1 | PTIT0 |

| PTIT                                             | W      |       |               |                |             |             |       |       |       |

| 0x0242<br>DDRT                                   | R<br>W | DDRT7 | DDRT6         | DDRT5          | DDRT4       | DDRT3       | DDRT2 | DDRT1 | DDRT0 |

| 0x0243<br>RDRT                                   | R<br>W | RDRT7 | RDRT6         | RDRT5          | RDRT4       | RDRT3       | RDRT2 | RDRT1 | RDRT0 |

| 0x0244<br>PERT                                   | R<br>W | PERT7 | PERT6         | PERT5          | PERT4       | PERT3       | PERT2 | PERT1 | PERT0 |

| 0x0245<br>PPST                                   | R<br>W | PPST7 | PPST6         | PPST5          | PPST4       | PPST3       | PPST2 | PPST1 | PPST0 |

|                                                  |        |       | ] = Unimpleme | ented or Reser | ved         |             |       |       |       |

Port Integration Module (S12XSPIMV1)

# 2.3.14 IRQ Control Register (IRQCR)

#### Figure 2-12. IRQ Control Register (IRQCR)

Read: See individual bit descriptions below Write: See individual bit descriptions below

#### Table 2-13. IRQCR Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IRQE  | IRQ select edge sensitive only—<br>Special mode: Read or write anytime<br>Normal mode: Read anytime, write once                                                                                                                                                       |

|            | <ol> <li>IRQ configured to respond only to falling edges. Falling edges on the IRQ pin will be detected anytime IRQE=1<br/>and will be cleared only upon a reset or the servicing of the IRQ interrupt.</li> <li>IRQ configured for low level recognition.</li> </ol> |

| 6<br>IRQEN | IRQ enable—<br>Read or write anytime                                                                                                                                                                                                                                  |

|            | 1 IRQ pin is connected to interrupt logic.<br>0 IRQ pin is disconnected from interrupt logic.                                                                                                                                                                         |

# 2.3.15 PIM Reserved Register PIMTEST<sup>1</sup>

This register is reserved for factory testing of the PIM module and is not available in normal operation. Writing to this register when in special modes can alter the pin functionality.

1. Implementation pim\_xe.01.01 and later

#### Table 2-24. PTIS Register Field Descriptions

| Field | Description                                                                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0   | Port S input data—                                                                                                                                  |

| PTIS  | A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

# 2.3.28 Port S Data Direction Register (DDRS)

Address 0x0249

Access: User read/write<sup>1</sup>

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | DDRS7 | DDRS6 | DDRS5 | DDRS4 | DDRS3 | DDRS2 | DDRS1 | DDRS0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 2-26. Port S Data Direction Register (DDRS)

<sup>1</sup> Read: Anytime Write: Anytime

#### Table 2-25. DDRS Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4<br>DDRS | Port S data direction—<br>This bit determines whether the associated pin is an input or output.<br>Depending on the configuration of the enabled SPI0 the I/O state will be forced to be input or output. In this case the<br>data direction bit will not change. |

|             | 1 Associated pin configured as output<br>0 Associated pin configured as input                                                                                                                                                                                     |

| 3-2<br>DDRS | Port S data direction—<br>This bit determines whether the associated pin is an input or output.<br>Depending on the configuration of the enabled SCI1 the I/O state will be forced to be input or output. In this case the<br>data direction bit will not change. |

|             | 1 Associated pin configured as output<br>0 Associated pin configured as input                                                                                                                                                                                     |

| 1-0<br>DDRS | Port S data direction—<br>This bit determines whether the associated pin is an input or output.<br>Depending on the configuration of the enabled SCI0 the I/O state will be forced to be input or output. In this case the<br>data direction bit will not change. |

|             | 1 Associated pin configured as output<br>0 Associated pin configured as input                                                                                                                                                                                     |

# 2.3.67 Port AD0 Data Register 1 (PT1AD0)

| Address 0x0271 Access: User read/write <sup>1</sup> |         |            |         |         | ser read/write <sup>1</sup> |         |         |         |

|-----------------------------------------------------|---------|------------|---------|---------|-----------------------------|---------|---------|---------|

|                                                     | 7       | 6          | 5       | 4       | 3                           | 2       | 1       | 0       |

| R<br>W                                              | PT1AD07 | PT1AD06    | PT1AD05 | PT1AD04 | PT1AD03                     | PT1AD02 | PT1AD01 | PT1AD00 |

| Altern.<br>Function                                 | AN7     | AN6        | AN5     | AN4     | AN3                         | AN2     | AN1     | AN0     |

| Reset                                               | 0       | 0          | 0       | 0       | 0                           | 0       | 0       | 0       |

|                                                     |         | <b>F</b> * |         |         |                             |         |         |         |

Figure 2-65. Port AD0 Data Register 1 (PT1AD0)

<sup>1</sup> Read: Anytime, the data source depends on the data direction value Write: Anytime

| Field  | Description                                                                                                                                                                     |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0    | Port AD0 general purpose input/output data—Data Register, ATD AN analog input                                                                                                   |

| PT1AD0 | When not used with the alternative function, the associated pin can be used as general purpose I/O. In general purpose output mode the register bit value is driven to the pin. |

|        | If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered pin input state is read.                            |

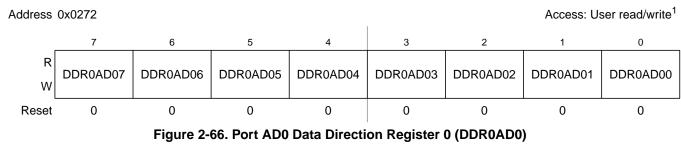

# 2.3.68 Port AD0 Data Direction Register 0 (DDR0AD0)

<sup>1</sup> Read: Anytime

Write: Anytime

#### Table 2-65. DDR0AD0 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>DDR0AD0 | <ul> <li>Port AD0 data direction—</li> <li>This bit determines whether the associated pin is an input or output.</li> <li>To use the digital input function the ATD Digital Input Enable Register (ATD0DIEN) has to be set to logic level "1".</li> <li>1 Associated pin configured as output</li> <li>0 Associated pin configured as input</li> </ul> |

Memory Mapping Control (S12XMMCV4)

### 3.4.2.1.1 Expansion of the Local Address Map

### Expansion of the CPU Local Address Map

The program page index register in MMC allows accessing up to 4MB of FLASH or ROM in the global memory map by using the eight page index bits to page 256 16KB blocks into the program page window located from address 0x8000 to address 0xBFFF in the local CPU memory map.

The page value for the program page window is stored in the PPAGE register. The value of the PPAGE register can be read or written by normal memory accesses as well as by the CALL and RTC instructions (see Section 3.5.1, "CALL and RTC Instructions).

Control registers, vector space and parts of the on-chip memories are located in unpaged portions of the 64KB local CPU address space.

The starting address of an interrupt service routine must be located in unpaged memory unless the user is certain that the PPAGE register will be set to the appropriate value when the service routine is called. However an interrupt service routine can call other routines that are in paged memory. The upper 16KB block of the local CPU memory space (0xC000-0xFFFF) is unpaged. It is recommended that all reset and interrupt vectors point to locations in this area or to the other unpaged sections of the local CPU memory map.

The RAM page index register allows accessing up to 1MB minus 2KB of RAM in the global memory map by using the eight RPAGE index bits to page 4KB blocks into the RAM page window located in the local CPU memory space from address 0x1000 to address 0x1FFF. The Data FLASH page index register EPAGE allows accessing up to 256KB of Data Flash in the system by using the eight EPAGE index bits to page 1KB blocks into the Data FLASH page window located in the local CPU memory space from address 0x0800 to address 0x0BFF. Background Debug Module (S12XBDMV2)

# 5.4.1 Security

If the user resets into special single chip mode with the system secured, a secured mode BDM firmware lookup table is brought into the map overlapping a portion of the standard BDM firmware lookup table. The secure BDM firmware verifies that the on-chip non-volatile memory (e.g. EEPROM and Flash EEPROM) is erased. This being the case, the UNSEC and ENBDM bit will get set. The BDM program jumps to the start of the standard BDM firmware and the secured mode BDM firmware is turned off and all BDM commands are allowed. If the non-volatile memory does not verify as erased, the BDM firmware sets the ENBDM bit, without asserting UNSEC, and the firmware enters a loop. This causes the BDM hardware commands to become enabled, but does not enable the firmware commands. This allows the BDM hardware to be used to erase the non-volatile memory.

BDM operation is not possible in any other mode than special single chip mode when the device is secured. The device can be unsecured via BDM serial interface in special single chip mode only. More information regarding security is provided in the security section of the device documentation.

# 5.4.2 Enabling and Activating BDM

The system must be in active BDM to execute standard BDM firmware commands. BDM can be activated only after being enabled. BDM is enabled by setting the ENBDM bit in the BDM status (BDMSTS) register. The ENBDM bit is set by writing to the BDM status (BDMSTS) register, via the single-wire interface, using a hardware command such as WRITE\_BD\_BYTE.

After being enabled, BDM is activated by one of the following<sup>1</sup>:

- Hardware BACKGROUND command

- CPU BGND instruction

- External instruction tagging mechanism<sup>2</sup>

- Breakpoint force or tag mechanism<sup>2</sup>

When BDM is activated, the CPU finishes executing the current instruction and then begins executing the firmware in the standard BDM firmware lookup table. When BDM is activated by a breakpoint, the type of breakpoint used determines if BDM becomes active before or after execution of the next instruction.

### NOTE

If an attempt is made to activate BDM before being enabled, the CPU resumes normal instruction execution after a brief delay. If BDM is not enabled, any hardware BACKGROUND commands issued are ignored by the BDM and the CPU is not delayed.

In active BDM, the BDM registers and standard BDM firmware lookup table are mapped to addresses 0x7FFF00 to 0x7FFFF. BDM registers are mapped to addresses 0x7FFF00 to 0x7FFF0B. The BDM uses these registers which are readable anytime by the BDM. However, these registers are not readable by user programs.

<sup>1.</sup> BDM is enabled and active immediately out of special single-chip reset.

<sup>2.</sup> This method is provided by the S12X\_DBG module.

| SSF[2:0]    | Current State     |

|-------------|-------------------|

| 000         | State0 (disarmed) |

| 001         | State1            |

| 010         | State2            |

| 011         | State3            |

| 100         | Final State       |

| 101,110,111 | Reserved          |

#### Table 6-7. SSF[2:0] — State Sequence Flag Bit Encoding

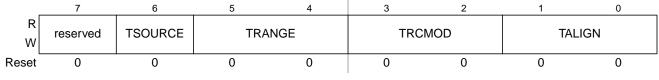

### 6.3.2.3 Debug Trace Control Register (DBGTCR)

Address: 0x0022

Figure 6-5. Debug Trace Control Register (DBGTCR)

Read: Anytime

Write: Bits 7:6 only when S12XDBG is neither secure nor armed. Bits 5:0 anytime the module is disarmed.

#### WARNING

DBGTCR[7] is reserved. Setting this bit maps the tracing to an unimplemented bus, thus preventing proper operation.

#### Table 6-8. DBGTCR Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>TSOURCE  | <ul> <li>Trace Source Control Bits — The TSOURCE enables the tracing session. If the MCU system is secured, this bit cannot be set and tracing is inhibited.</li> <li>0 No tracing selected</li> <li>1 Tracing selected</li> </ul>                                                                                                                                           |

| 5–4<br>TRANGE | <b>Trace Range Bits</b> — The TRANGE bits allow filtering of trace information from a selected address range when tracing from the CPU12X in Detail Mode. To use a comparator for range filtering, the corresponding COMPE bits must remain cleared. If the COMPE bit is not clear then the comparator will also be used to generate state sequence triggers. See Table 6-9. |

| 3–2<br>TRCMOD | <b>Trace Mode Bits</b> — See Section 6.4.5.2 for detailed Trace Mode descriptions. In Normal Mode, change of flow information is stored. In Loop1 Mode, change of flow information is stored but redundant entries into trace memory are inhibited. In Detail Mode, address and data for all memory and register accesses is stored. See Table 6-10.                         |

| 1–0<br>TALIGN | <b>Trigger Align Bits</b> — These bits control whether the trigger is aligned to the beginning, end or the middle of a tracing session. See Table 6-11.                                                                                                                                                                                                                      |

# Chapter 8 S12XE Clocks and Reset Generator (S12XECRGV1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected           | Description of Changes                                                                                                                           |  |

|--------------------|------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V01.00             | 26 Oct. 2005     |                                | Initial release                                                                                                                                  |  |

| V01.01             | 02 Nov 2006      | 8.4.1.1/8-254                  | Table "Examples of IPLL Divider settings": corrected \$32 to \$31                                                                                |  |

| V01.02             | 4 Mar. 2008      | 8.4.1.4/8-257<br>8.4.3.3/8-261 | Corrected details                                                                                                                                |  |

| V01.03             | 1 Sep. 2008      | Table 8-14                     | added 100MHz example for PLL                                                                                                                     |  |

| V01.04             | 20 Nov. 2008     | 8.3.2.4/8-243                  | S12XECRG Flags Register: corrected address to Module Base + 0x0003                                                                               |  |

| V01.05             | 19. Sep 2009     | 8.5.1/8-263                    | Modified Note below Table 8-17./8-263                                                                                                            |  |

| V01.06             | 18. Sep 2012     | Table 8-14<br>8.5.1            | Added footnote concerning maximum clock frequencies to table<br>Removed redundant examples from table<br>Replaced reference to MMC documentation |  |

Table 8-1. Revision History

## 8.1 Introduction

This specification describes the function of the Clocks and Reset Generator (S12XECRG).

### 8.1.1 Features

The main features of this block are:

- Phase Locked Loop (IPLL) frequency multiplier with internal filter

- Reference divider

- Post divider

- Configurable internal filter (no external pin)

- Optional frequency modulation for defined jitter and reduced emission

- Automatic frequency lock detector

- Interrupt request on entry or exit from locked condition

- Self Clock Mode in absence of reference clock

- System Clock Generator

- Clock Quality Check

- User selectable fast wake-up from Stop in Self-Clock Mode for power saving and immediate program execution

- Clock switch for either Oscillator or PLL based system clocks

- Computer Operating Properly (COP) watchdog timer with time-out clear window.

S12XE Clocks and Reset Generator (S12XECRGV1)

| CR2                                                                  | CR1 | CR0 | OSCCLK<br>Cycles to Timeout |  |  |

|----------------------------------------------------------------------|-----|-----|-----------------------------|--|--|

| 1                                                                    | 1   | 1   | 2 <sup>24</sup>             |  |  |

| 1. OSCCLK cycles are referenced from the previous COP time-out reset |     |     |                             |  |  |

Table 8-13. COP Watchdog Rates<sup>(1)</sup>

(writing \$55/\$AA to the ARMCOP register)

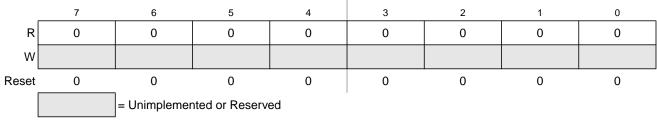

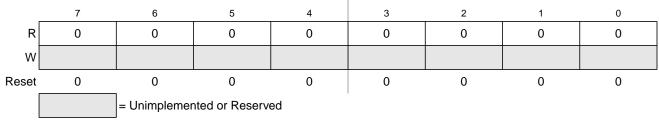

#### 8.3.2.10 **Reserved Register (FORBYP)**

### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in special modes can alter the S12XECRG's functionality.

Module Base + 0x0009

Figure 8-12. Reserved Register (FORBYP)

Read: Always read \$00 except in special modes

Write: Only in special modes

#### 8.3.2.11 **Reserved Register (CTCTL)**

NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in special test modes can alter the S12XECRG's functionality.

Module Base + 0x000A

### Figure 8-13. Reserved Register (CTCTL)

Read: Always read \$00 except in special modes

S12XE Clocks and Reset Generator (S12XECRGV1)

### NOTE

In order to detect a potential clock loss the CME bit should always be enabled (CME = 1).

If CME bit is disabled and the MCU is configured to run on PLLCLK, a loss of external clock (OSCCLK) will not be detected and will cause the system clock to drift towards lower frequencies. As soon as the external clock is available again the system clock ramps up to its IPLL target frequency. If the MCU is running on external clock any loss of clock will cause the system to go static.

## 8.4.3 Low Power Options

This section summarizes the low power options available in the S12XECRG.

### 8.4.3.1 Run Mode

This is the default mode after reset.

The RTI can be stopped by setting the associated rate select bits to zero.

The COP can be stopped by setting the associated rate select bits to zero.

### 8.4.3.2 Wait Mode

The WAI instruction puts the MCU in a low power consumption stand-by mode depending on setting of the individual bits in the CLKSEL register. All individual Wait Mode configuration bits can be superposed. This provides enhanced granularity in reducing the level of power consumption during Wait Mode. Table 8-15 lists the individual configuration bits and the parts of the MCU that are affected in Wait Mode.

|      |         | -       | -       |

|------|---------|---------|---------|

|      | PLLWAI  | RTIWAI  | COPWAI  |

| IPLL | Stopped | _       | _       |

| RTI  | —       | Stopped | _       |

| COP  | _       | _       | Stopped |

Table 8-15. MCU Configuration During Wait Mode

After executing the WAI instruction the core requests the S12XECRG to switch MCU into Wait Mode. The S12XECRG then checks whether the PLLWAI bit is asserted. Depending on the configuration the S12XECRG switches the system and core clocks to OSCCLK by clearing the PLLSEL bit and disables the IPLL.

There are two ways to restart the MCU from Wait Mode:

- 1. Any reset

- 2. Any interrupt

#### Analog-to-Digital Converter (ADC12B16CV1)

| Field                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DJM                     | <ul> <li>Result Register Data Justification — Result data format is always unsigned. This bit controls justification of conversion data in the result registers.</li> <li>0 Left justified data in the result registers.</li> <li>1 Right justified data in the result registers.</li> <li>Table 10-10 gives examples ATD results for an input signal range between 0 and 5.12 Volts.</li> </ul>                                                                                                               |

| 6–3<br>S8C, S4C,<br>S2C, S1C | <b>Conversion Sequence Length</b> — These bits control the number of conversions per sequence. Table 10-11 shows all combinations. At reset, S4C is set to 1 (sequence length is 4). This is to maintain software continuity to HC12 family.                                                                                                                                                                                                                                                                   |

| 2<br>FIFO                    | <b>Result Register FIFO Mode</b> — If this bit is zero (non-FIFO mode), the A/D conversion results map into the result registers based on the conversion sequence; the result of the first conversion appears in the first result register (ATDDR0), the second result in the second result register (ATDDR1), and so on.                                                                                                                                                                                      |

|                              | If this bit is one (FIFO mode) the conversion counter is not reset at the beginning or ending of a conversion sequence; sequential conversion results are placed in consecutive result registers. In a continuously scanning conversion sequence, the result register counter will wrap around when it reaches the end of the result register file. The conversion counter value (CC3-0 in ATDSTAT0) can be used to determine where in the result register file, the current conversion result will be placed. |

|                              | Aborting a conversion or starting a new conversion clears the conversion counter even if FIFO=1. So the first result of a new conversion sequence, started by writing to ATDCTL5, will always be place in the first result register (ATDDDR0). Intended usage of FIFO mode is continuos conversion (SCAN=1) or triggered conversion (ETRIG=1).                                                                                                                                                                 |

|                              | Which result registers hold valid data can be tracked using the conversion complete flags. Fast flag clear mode may or may not be useful in a particular application to track valid data.                                                                                                                                                                                                                                                                                                                      |

|                              | If this bit is one, automatic compare of result registers is always disabled, that is ADC12B16C will behave as if ACMPIE and all CPME[ <i>n</i> ] were zero.<br>0 Conversion results are placed in the corresponding result register up to the selected sequence length.<br>1 Conversion results are placed in consecutive result registers (wrap around at end).                                                                                                                                              |

| 1–0<br>FRZ[1:0]              | <b>Background Debug Freeze Enable</b> — When debugging an application, it is useful in many cases to have the ATD pause when a breakpoint (Freeze Mode) is encountered. These 2 bits determine how the ATD will respond to a breakpoint as shown in Table 10-12. Leakage onto the storage node and comparator reference capacitors may compromise the accuracy of an immediately frozen conversion depending on the length of the freeze period.                                                               |

### Table 10-9. ATDCTL3 Field Descriptions

#### 256 KByte Flash Module (S12XFTMR256K1V1)

| OSCCLK Frequency<br>(MHz) |                  | FDIV[6:0] |                  | Frequency<br>Hz) | FDIV[6:0] |

|---------------------------|------------------|-----------|------------------|------------------|-----------|

| MIN <sup>1</sup>          | MAX <sup>2</sup> |           | MIN <sup>1</sup> | MAX <sup>2</sup> | 1 .       |

| 1.60                      | 2.10             | 0x01      | 33.60            | 34.65            | 0x20      |

| 2.40                      | 3.15             | 0x02      | 34.65            | 35.70            | 0x21      |

| 3.20                      | 4.20             | 0x03      | 35.70            | 36.75            | 0x22      |

| 4.20                      | 5.25             | 0x04      | 36.75            | 37.80            | 0x23      |

| 5.25                      | 6.30             | 0x05      | 37.80            | 38.85            | 0x24      |

| 6.30                      | 7.35             | 0x06      | 38.85            | 39.90            | 0x25      |

| 7.35                      | 8.40             | 0x07      | 39.90            | 40.95            | 0x26      |

| 8.40                      | 9.45             | 0x08      | 40.95            | 42.00            | 0x27      |

| 9.45                      | 10.50            | 0x09      | 42.00            | 43.05            | 0x28      |

| 10.50                     | 11.55            | 0x0A      | 43.05            | 44.10            | 0x29      |

| 11.55                     | 12.60            | 0x0B      | 44.10            | 45.15            | 0x2A      |

| 12.60                     | 13.65            | 0x0C      | 45.15            | 46.20            | 0x2B      |

| 13.65                     | 14.70            | 0x0D      | 46.20            | 47.25            | 0x2C      |

| 14.70                     | 15.75            | 0x0E      | 47.25            | 48.30            | 0x2D      |

| 15.75                     | 16.80            | 0x0F      | 48.30            | 49.35            | 0x2E      |

| 16.80                     | 17.85            | 0x10      | 49.35            | 50.40            | 0x2F      |

| 17.85                     | 18.90            | 0x11      |                  |                  |           |

| 18.90                     | 19.95            | 0x12      |                  |                  |           |

| 19.95                     | 21.00            | 0x13      |                  |                  |           |

| 21.00                     | 22.05            | 0x14      |                  |                  |           |

| 22.05                     | 23.10            | 0x15      |                  |                  |           |

| 23.10                     | 24.15            | 0x16      |                  |                  |           |

| 24.15                     | 25.20            | 0x17      |                  |                  |           |

| 25.20                     | 26.25            | 0x18      |                  |                  |           |

| 26.25                     | 27.30            | 0x19      |                  |                  |           |

| 27.30                     | 28.35            | 0x1A      |                  |                  |           |

| 28.35                     | 29.40            | 0x1B      |                  |                  |           |

| 29.40                     | 30.45            | 0x1C      |                  |                  |           |

| 30.45                     | 31.50            | 0x1D      |                  |                  |           |

| 31.50                     | 32.55            | 0x1E      |                  |                  |           |

| 32.55                     | 33.60            | 0x1F      |                  |                  |           |

#### Table 18-7. FDIV vs OSCCLK Frequency

<sup>1</sup> FDIV shown generates an FCLK frequency of >0.8 MHz

<sup>2</sup> FDIV shown generates an FCLK frequency of 1.05 MHz

#### 128 KByte Flash Module (S12XFTMR128K1V1)

| OSCCLK Frequency<br>(MHz) |                  | FDIV[6:0] |                  | OSCCLK Frequency<br>(MHz) |           |

|---------------------------|------------------|-----------|------------------|---------------------------|-----------|

| MIN <sup>1</sup>          | MAX <sup>2</sup> |           | MIN <sup>1</sup> | MAX <sup>2</sup>          | FDIV[6:0] |

| 1.60                      | 2.10             | 0x01      | 33.60            | 34.65                     | 0x20      |

| 2.40                      | 3.15             | 0x02      | 34.65            | 35.70                     | 0x21      |

| 3.20                      | 4.20             | 0x03      | 35.70            | 36.75                     | 0x22      |

| 4.20                      | 5.25             | 0x04      | 36.75            | 37.80                     | 0x23      |

| 5.25                      | 6.30             | 0x05      | 37.80            | 38.85                     | 0x24      |

| 6.30                      | 7.35             | 0x06      | 38.85            | 39.90                     | 0x25      |

| 7.35                      | 8.40             | 0x07      | 39.90            | 40.95                     | 0x26      |

| 8.40                      | 9.45             | 0x08      | 40.95            | 42.00                     | 0x27      |

| 9.45                      | 10.50            | 0x09      | 42.00            | 43.05                     | 0x28      |

| 10.50                     | 11.55            | 0x0A      | 43.05            | 44.10                     | 0x29      |

| 11.55                     | 12.60            | 0x0B      | 44.10            | 45.15                     | 0x2A      |

| 12.60                     | 13.65            | 0x0C      | 45.15            | 46.20                     | 0x2B      |

| 13.65                     | 14.70            | 0x0D      | 46.20            | 47.25                     | 0x2C      |

| 14.70                     | 15.75            | 0x0E      | 47.25            | 48.30                     | 0x2D      |

| 15.75                     | 16.80            | 0x0F      | 48.30            | 49.35                     | 0x2E      |

| 16.80                     | 17.85            | 0x10      | 49.35            | 50.40                     | 0x2F      |

| 17.85                     | 18.90            | 0x11      |                  |                           |           |

| 18.90                     | 19.95            | 0x12      |                  |                           |           |

| 19.95                     | 21.00            | 0x13      |                  |                           |           |

| 21.00                     | 22.05            | 0x14      |                  |                           |           |

| 22.05                     | 23.10            | 0x15      |                  |                           |           |

| 23.10                     | 24.15            | 0x16      |                  |                           |           |

| 24.15                     | 25.20            | 0x17      |                  |                           |           |

| 25.20                     | 26.25            | 0x18      |                  |                           |           |

| 26.25                     | 27.30            | 0x19      |                  |                           |           |

| 27.30                     | 28.35            | 0x1A      |                  |                           |           |

| 28.35                     | 29.40            | 0x1B      |                  |                           |           |

| 29.40                     | 30.45            | 0x1C      |                  |                           |           |

| 30.45                     | 31.50            | 0x1D      |                  |                           |           |

| 31.50                     | 32.55            | 0x1E      |                  |                           |           |

| 32.55                     | 33.60            | 0x1F      |                  |                           |           |

#### Table 19-7. FDIV vs OSCCLK Frequency

<sup>1</sup> FDIV shown generates an FCLK frequency of >0.8 MHz

$^2\,$  FDIV shown generates an FCLK frequency of 1.05 MHz

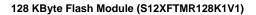

Figure 19-25. Flash Reserved4 Register (FRSV4)

All bits in the FRSV4 register read 0 and are not writable.

# **19.4 Functional Description**

# 19.4.1 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

Offset Module Base + 0x0013

- How to write the FCLKDIV register that is used to generate a time base (FCLK) derived from OSCCLK for Flash program and erase command operations

- The command write sequence used to set Flash command parameters and launch execution

- Valid Flash commands available for execution

### 19.4.1.1 Writing the FCLKDIV Register

Prior to issuing any Flash program or erase command after a reset, the user is required to write the FCLKDIV register to divide OSCCLK down to a target FCLK of 1 MHz. Table 19-7 shows recommended values for the FDIV field based on OSCCLK frequency.

### NOTE

Programming or erasing the Flash memory cannot be performed if the bus clock runs at less than 1 MHz. Setting FDIV too high can destroy the Flash memory due to overstress. Setting FDIV too low can result in incomplete programming or erasure of the Flash memory cells.

When the FCLKDIV register is written, the FDIVLD bit is set automatically. If the FDIVLD bit is 0, the FCLKDIV register has not been written since the last reset. If the FCLKDIV register has not been written, any Flash program or erase command loaded during a command write sequence will not execute and the ACCERR bit in the FSTAT register will set.

| Register | Error Bit Error Condition |                                                                                     |

|----------|---------------------------|-------------------------------------------------------------------------------------|

|          |                           | Set if CCOBIX[2:0] != 101 at command launch                                         |

|          | ACCERR                    | Set if command not available in current mode (see Table 19-28)                      |

|          | AUGERR                    | Set if an invalid global address [22:0] is supplied                                 |

| FSTAT    |                           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL                    | Set if the global address [22:0] points to a protected area                         |

|          | MGSTAT1                   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0                   | Set if any non-correctable errors have been encountered during the verify operation |

#### Table 19-40. Program P-Flash Command Error Handling

### 19.4.2.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash block 0. The Program Once reserved field can be read using the Read Once command as described in Section 19.4.2.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash block 0 cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |                   |  |

|-------------|---------------------------------------------|-------------------|--|

| 000         | 0x07                                        | 0x07 Not Required |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |                   |  |

| 010         | Program Once word 0 value                   |                   |  |

| 011         | Program Once word 1 value                   |                   |  |

| 100         | Program Once word 2 value                   |                   |  |

| 101         | Program Once word 3 value                   |                   |  |

Table 19-41. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash block 0 will return invalid data.

#### 128 KByte Flash Module (S12XFTMR128K1V1)

Table 19-3). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters  |  |  |

|-------------|-------------------|--|--|

| 000         | 0x0C Not required |  |  |

| 001         | Key 0             |  |  |

| 010         | Key 1             |  |  |

| 011         | Key 2             |  |  |

| 100         | Key 3             |  |  |

Table 19-51. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x7F\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

Table 19-52. Verify Backdoor Access Key Command Error Handling

| Register | Error Bit | Error Condition                                                                             |  |

|----------|-----------|---------------------------------------------------------------------------------------------|--|

|          |           | Set if CCOBIX[2:0] != 100 at command launch                                                 |  |

|          |           | Set if an incorrect backdoor key is supplied                                                |  |

|          | ACCERR    | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see<br>Section 19.3.2.2) |  |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                                 |  |

|          | FPVIOL    | None                                                                                        |  |

|          | MGSTAT1   | None                                                                                        |  |

|          | MGSTAT0   | None                                                                                        |  |

### 19.4.2.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of a specific P-Flash or D-Flash block.

### Table 19-53. Set User Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters     |                                                       |  |

|-------------|----------------------|-------------------------------------------------------|--|

| 000         | 0x0D                 | Global address [22:16] to identify the<br>Flash block |  |

| 001         | Margin level setting |                                                       |  |

#### 64 KByte Flash Module (S12XFTMR64K1V1)

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |  |

|-------------|----------------------------------------------------------|----------------------------------------------|--|

| 000         | 0x03                                                     | Global address [22:16] of<br>a P-Flash block |  |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |  |

| 010         | Number of phrases to be verified                         |                                              |  |

Table 20-35. Erase Verify P-Flash Section Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed.

| Register | Error Bit | Error Condition                                                              |  |  |  |  |  |

|----------|-----------|------------------------------------------------------------------------------|--|--|--|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                                  |  |  |  |  |  |

|          |           | Set if command not available in current mode (see Table 20-28)               |  |  |  |  |  |

|          |           | Set if an invalid global address [22:0] is supplied <sup>1</sup>             |  |  |  |  |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000) |  |  |  |  |  |

| FSTAL    |           | Set if the requested section crosses a 128 Kbyte boundary                    |  |  |  |  |  |

|          | FPVIOL    | None                                                                         |  |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read <sup>2</sup>         |  |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read      |  |  |  |  |  |

Table 20-36. Erase Verify P-Flash Section Command Error Handling

<sup>1</sup> As defined by the memory map for FTMR128K1.

100

<sup>2</sup> As found in the memory map for FTMR128K1.

### 20.4.2.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash block 0. The Read Once field is programmed using the Program Once command described in Section 20.4.2.6. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                         |              |  |  |

|-------------|------------------------------------------|--------------|--|--|

| 000         | 0x04                                     | Not Required |  |  |

| 001         | Read Once phrase index (0x0000 - 0x0007) |              |  |  |

| 010         | Read Once word 0 value                   |              |  |  |

| 011         | Read Once word 1 value                   |              |  |  |

Read Once word 2 value

Read Once word 3 value

Table 20-37. Read Once Command FCCOB Requirements

| Register | Error Bit | Error Condition                                                                     |  |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                         |  |  |  |  |

|          |           | Set if command not available in current mode (see Table 20-28)                      |  |  |  |  |

|          |           | Set if an invalid global address [22:0] is supplied <sup>1</sup>                    |  |  |  |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |  |  |  |

|          | FPVIOL    | Set if the global address [22:0] points to a protected area                         |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |  |

#### Table 20-40. Program P-Flash Command Error Handling

<sup>1</sup> As defined by the memory map for FTMR128K1.

### 20.4.2.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash block 0. The Program Once reserved field can be read using the Read Once command as described in Section 20.4.2.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash block 0 cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |  |  |  |  |

|-------------|---------------------------------------------|--|--|--|--|

| 000         | 0x07 Not Required                           |  |  |  |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |  |  |  |  |

| 010         | Program Once word 0 value                   |  |  |  |  |

| 011         | Program Once word 1 value                   |  |  |  |  |

| 100         | Program Once word 2 value                   |  |  |  |  |

| 101         | Program Once word 3 value                   |  |  |  |  |

Table 20-41. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash block 0 will return invalid data.

Electrical Characteristics

# A.6 Reset, Oscillator and PLL

This section summarizes the electrical characteristics of the various startup scenarios for oscillator and phase-locked loop (PLL).

# A.6.1 Startup

Table A-22 summarizes several startup characteristics explained in this section. Detailed description of the startup behavior can be found in the Clock and Reset Generator (CRG) block description

| Conditions are shown in Table A-4unless otherwise noted |   |                                             |                    |     |     |     |                  |

|---------------------------------------------------------|---|---------------------------------------------|--------------------|-----|-----|-----|------------------|

| Num                                                     | С | Rating                                      | Symbol             | Min | Тур | Max | Unit             |

| 1                                                       | D | Reset input pulse width, minimum input time | PW <sub>RSTL</sub> | 2   | _   | _   | t <sub>osc</sub> |

| 2                                                       | D | Startup from reset                          | n <sub>RST</sub>   | 192 | _   | 196 | n <sub>osc</sub> |

| 3                                                       | D | Wait recovery startup time                  | t <sub>WRS</sub>   | —   | _   | 14  | t <sub>cyc</sub> |

| 4                                                       | D | Fast wakeup from STOP <sup>1</sup>          | t <sub>fws</sub>   | —   | 50  | 100 | μs               |

Table A-22. Startup Characteristics

<sup>1</sup> Including voltage regulator startup;  $V_{DD} / V_{DDF}$  filter capacitors 220 nF,  $V_{DD35} = 5$  V, T= 25°C

### A.6.1.1 POR

The release level  $V_{PORR}$  and the assert level  $V_{PORA}$  are derived from the  $V_{DD}$  supply. They are also valid if the device is powered externally. After releasing the POR reset the oscillator and the clock quality check are started. If after a time  $t_{CQOUT}$  no valid oscillation is detected, the MCU will start using the internal self clock. The fastest startup time possible is given by  $n_{uposc}$ .

### A.6.1.2 SRAM Data Retention

Provided an appropriate external reset signal is applied to the MCU, preventing the CPU from executing code when  $V_{DD35}$  is out of specification limits, the SRAM contents integrity is guaranteed if after the reset the PORF bit in the CRG flags register has not been set.

### A.6.1.3 External Reset

When external reset is asserted for a time greater than  $PW_{RSTL}$  the CRG module generates an internal reset, and the CPU starts fetching the reset vector without doing a clock quality check, if there was an oscillation before reset.

### A.6.1.4 Stop Recovery

Out of stop the controller can be woken up by an external interrupt. A clock quality check as after POR is performed before releasing the clocks to the system.

If the MCU is woken-up by an interrupt and the fast wake-up feature is enabled (FSTWKP = 1 and SCME = 1), the system will resume operation in self-clock mode after  $t_{fws}$ .

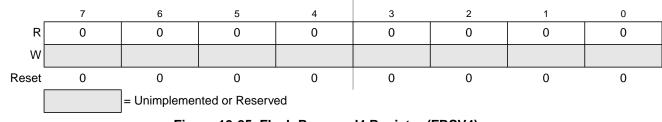

Package Information

VIEW AA

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. |              | LOUTLINE       | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--------------|----------------|------------------|-------------|

| TITLE: 64LD LQFP,                                       | DOCUMENT NO  | : 98ASS23234W  | REV: E           |             |

| 10 X 10 X 1.4 P                                         | CASE NUMBER  | 2: 840F-02     | 11 AUG 2006      |             |

| 0.5 PITCH, CASE OU                                      | STANDARD: JE | DEC MS-026 BCD |                  |             |

### Figure B-7. 64-pin LQFP (case no. 840F) - page 2