Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 80MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, UART/USART    |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                 |

| Number of I/O              | 38                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 160K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l451ccu3 |

|   | 3.17  | Voltage reference buffer (VREFBUF)                                | 41   |

|---|-------|-------------------------------------------------------------------|------|

|   | 3.18  | Comparators (COMP)                                                | 42   |

|   | 3.19  | Operational amplifier (OPAMP)                                     | 42   |

|   | 3.20  | Touch sensing controller (TSC)                                    | 42   |

|   | 3.21  | Digital filter for Sigma-Delta Modulators (DFSDM)                 | 43   |

|   | 3.22  | Random number generator (RNG)                                     | 45   |

|   | 3.23  | Timers and watchdogs                                              | 45   |

|   |       | 3.23.1 Advanced-control timer (TIM1)                              | . 46 |

|   |       | 3.23.2 General-purpose timers (TIM2, TIM3, TIM15, TIM16)          | . 46 |

|   |       | 3.23.3 Basic timer (TIM6)                                         | . 46 |

|   |       | 3.23.4 Low-power timer (LPTIM1 and LPTIM2)                        | . 47 |

|   |       | 3.23.5 Infrared interface (IRTIM)                                 | . 47 |

|   |       | 3.23.6 Independent watchdog (IWDG)                                | . 47 |

|   |       | 3.23.7 System window watchdog (WWDG)                              |      |

|   |       | 3.23.8 SysTick timer                                              |      |

|   | 3.24  | Real-time clock (RTC) and backup registers                        |      |

|   | 3.25  | Inter-integrated circuit interface (I <sup>2</sup> C)             | 49   |

|   | 3.26  | Universal synchronous/asynchronous receiver transmitter (USART)   | 50   |

|   | 3.27  | Low-power universal asynchronous receiver transmitter (LPUART)    | 51   |

|   | 3.28  | Serial peripheral interface (SPI)                                 | 52   |

|   | 3.29  | Serial audio interfaces (SAI)                                     | 52   |

|   | 3.30  | Controller area network (CAN)                                     | 53   |

|   | 3.31  | Secure digital input/output and MultiMediaCards Interface (SDMMC) | 53   |

|   | 3.32  | Clock recovery system (CRS)                                       | 54   |

|   | 3.33  | Quad SPI memory interface (QUADSPI)                               | 54   |

|   | 3.34  | Development support                                               |      |

|   |       | 3.34.1 Serial wire JTAG debug port (SWJ-DP)                       | . 56 |

|   |       | 3.34.2 Embedded Trace Macrocell™                                  | . 56 |

| 4 | Pino  | uts and pin description                                           | 57   |

| 5 | Mem   | ory mapping                                                       | 82   |

| 6 | Elect | rical characteristics                                             | 86   |

|   | 6.1   | Parameter conditions                                              |      |

|   |       |                                                                   |      |

STM32L451xx List of figures

| LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline | 184                                                                             |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------|

| LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package         |                                                                                 |

| recommended footprint                                             | 185                                                                             |

| LQFP64 marking (package top view)                                 | 186                                                                             |

|                                                                   |                                                                                 |

| array package outline                                             | 186                                                                             |

|                                                                   |                                                                                 |

|                                                                   | 187                                                                             |

|                                                                   |                                                                                 |

|                                                                   |                                                                                 |

| ·                                                                 | 189                                                                             |

|                                                                   |                                                                                 |

|                                                                   | 190                                                                             |

| ·                                                                 |                                                                                 |

| - · · · · · · · · · · · · · · · · · · ·                           |                                                                                 |

|                                                                   | 102                                                                             |

|                                                                   | 192                                                                             |

|                                                                   | 102                                                                             |

|                                                                   |                                                                                 |

|                                                                   |                                                                                 |

| LQFP64 P <sub>D</sub> max vs. I <sub>A</sub>                      | 197                                                                             |

|                                                                   | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package recommended footprint |

DS11910 Rev 4 11/201

Functional overview STM32L451xx

# 3.4 Embedded Flash memory

STM32L451xx devices feature up to 512 Kbyte of embedded Flash memory available for storing programs and data in single bank architecture. The Flash memory contains 256 pages of 2 Kbyte.

Flexible protections can be configured thanks to option bytes:

- Readout protection (RDP) to protect the whole memory. Three levels are available:

- Level 0: no readout protection

- Level 1: memory readout protection: the Flash memory cannot be read from or written to if either debug features are connected, boot in RAM or bootloader is selected

- Level 2: chip readout protection: debug features (Cortex-M4 JTAG and serial wire), boot in RAM and bootloader selection are disabled (JTAG fuse). This selection is irreversible.

| Area      | Protection | User execution |       |                    | Debug, boot from RAM or bo<br>from system memory (loade |       |                    |  |

|-----------|------------|----------------|-------|--------------------|---------------------------------------------------------|-------|--------------------|--|

|           | level      | Read           | Write | Erase              | Read                                                    | Write | Erase              |  |

| Main      | 1          | Yes            | Yes   | Yes                | No                                                      | No    | No                 |  |

| memory    | 2          | Yes            | Yes   | Yes                | N/A                                                     | N/A   | N/A                |  |

| System    | 1          | Yes            | No    | No                 | Yes                                                     | No    | No                 |  |

| memory    | 2          | Yes            | No    | No                 | N/A                                                     | N/A   | N/A                |  |

| Option    | 1          | Yes            | Yes   | Yes                | Yes                                                     | Yes   | Yes                |  |

| bytes     | 2          | Yes            | No    | No                 | N/A                                                     | N/A   | N/A                |  |

| Backup    | 1          | Yes            | Yes   | N/A <sup>(1)</sup> | No                                                      | No    | N/A <sup>(1)</sup> |  |

| registers | 2          | Yes            | Yes   | N/A                | N/A                                                     | N/A   | N/A                |  |

|           | 1          | Yes            | Yes   | Yes <sup>(1)</sup> | No                                                      | No    | No <sup>(1)</sup>  |  |

Yes

N/A

N/A

N/A

Table 3. Access status versus readout protection level and execution modes

Yes

SRAM2

• Write protection (WRP): the protected area is protected against erasing and programming. Two areas can be selected, with 2-Kbyte granularity.

Yes

Proprietary code readout protection (PCROP): a part of the flash memory can be protected against read and write from third parties. The protected area is execute-only: it can only be reached by the STM32 CPU, as an instruction code, while all other accesses (DMA, debug and CPU data read, write and erase) are strictly prohibited. The PCROP area granularity is 64-bit wide. An additional option bit (PCROP\_RDP) allows to select if the PCROP area is erased or not when the RDP protection is changed from Level 1 to Level 0.

<sup>1.</sup> Erased when RDP change from Level 1 to Level 0.

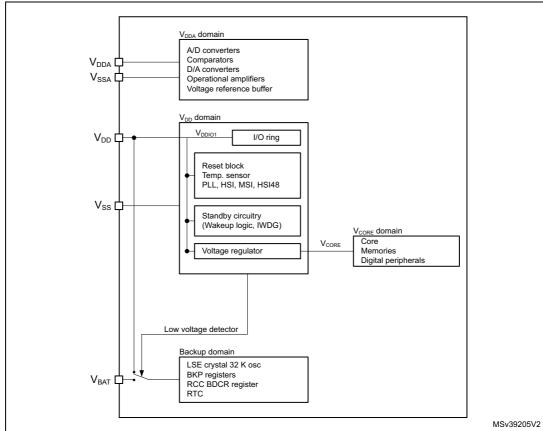

Figure 2. Power supply overview

During power-up and power-down phases, the following power sequence requirements must be respected:

- When V<sub>DD</sub> is below 1 V, other power supplies (V<sub>DDA</sub>) must remain below V<sub>DD</sub> + 300 mV.

- When V<sub>DD</sub> is above 1 V, all power supplies are independent.

During the power-down phase,  $V_{DD}$  can temporarily become lower than other supplies only if the energy provided to the MCU remains below 1 mJ; this allows external decoupling capacitors to be discharged with different time constants during the power- down transient phase.

Functional overview STM32L451xx

#### Shutdown mode

The Shutdown mode allows to achieve the lowest power consumption. The internal regulator is switched off so that the  $V_{CORE}$  domain is powered off. The PLL, the HSI16, the MSI, the LSI and the HSE oscillators are also switched off.

The RTC can remain active (Shutdown mode with RTC, Shutdown mode without RTC).

The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to Backup domain is not supported.

SRAM1, SRAM2 and register contents are lost except for registers in the Backup domain.

The device exits Shutdown mode when an external reset (NRST pin), a WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper).

The system clock after wakeup is MSI at 4 MHz.

|                      |     |       |                      |                        | Stop | o 0/1             | Sto | р 2               | Star | ndby              | Shut | down              |      |

|----------------------|-----|-------|----------------------|------------------------|------|-------------------|-----|-------------------|------|-------------------|------|-------------------|------|

| Peripheral           | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | -    | Wakeup capability | -   | Wakeup capability | -    | Wakeup capability | -    | Wakeup capability | VBAT |

| CRC calculation unit | 0   | 0     | 0                    | 0                      | -    | -                 | -   | -                 | -    | -                 | -    | -                 | -    |

| GPIOs                | 0   | 0     | 0                    | 0                      | 0    | 0                 | 0   | 0                 | (9)  | 5<br>pins<br>(10) | (11) | 5<br>pins<br>(10) | -    |

Table 5. Functionalities depending on the working mode<sup>(1)</sup> (continued)

- 1. Legend: Y = Yes (Enable). O = Optional (Disable by default. Can be enabled by software). = Not available.

- 2. The Flash can be configured in power-down mode. By default, it is not in power-down mode.

- 3. The SRAM clock can be gated on or off.

- 4. SRAM2 content is preserved when the bit RRS is set in PWR CR3 register.

- Some peripherals with wakeup from Stop capability can request HSI16 to be enabled. In this case, HSI16 is woken up by the peripheral, and only feeds the peripheral which requested it. HSI16 is automatically put off when the peripheral does not need it anymore.

- UART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

- 7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

- 8. Voltage scaling Range 1 only.

- 9. I/Os can be configured with internal pull-up, pull-down or floating in Standby mode.

- 10. The I/Os with wakeup from Standby/Shutdown capability are: PA0, PC13, PE6, PA2, PC5.

- 11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

#### 3.9.5 Reset mode

In order to improve the consumption under reset, the I/Os state under and after reset is "analog state" (the I/O schmitt trigger is disable). In addition, the internal reset pull-up is deactivated when the reset source is internal.

#### 3.9.6 VBAT operation

The VBAT pin allows to power the device VBAT domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present. The VBAT pin supplies the RTC with LSE and the backup registers. Three antitamper detection pins are available in VBAT mode.

VBAT operation is automatically activated when V<sub>DD</sub> is not present.

An internal VBAT battery charging circuit is embedded and can be activated when  $V_{DD}$  is present.

Note: When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from VBAT operation.

577

DS11910 Rev 4 31/201

## 3.23.4 Low-power timer (LPTIM1 and LPTIM2)

The devices embed two low-power timers. These timers have an independent clock and are running in Stop mode if they are clocked by LSE, LSI or an external clock. They are able to wakeup the system from Stop mode.

LPTIM1 is active in Stop 0, Stop 1 and Stop 2 modes.

LPTIM2 is active in Stop 0 and Stop 1 mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- · Continuous/ one shot mode

- Selectable software/hardware input trigger

- Selectable clock source

- Internal clock sources: LSE, LSI, HSI16 or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by pulse counter application).

- Programmable digital glitch filter

- Encoder mode (LPTIM1 only)

#### 3.23.5 Infrared interface (IRTIM)

The STM32L451xx includes one infrared interface (IRTIM). It can be used with an infrared LED to perform remote control functions. It uses TIM15 and TIM16 output channels to generate output signal waveforms on IR\_OUT pin.

#### 3.23.6 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC (LSI) and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.23.7 System window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

DS11910 Rev 4 47/201

|                                                        | ••                     |

|--------------------------------------------------------|------------------------|

| SAI features                                           | Support <sup>(1)</sup> |

| I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97         | X                      |

| Mute mode                                              | X                      |

| Stereo/Mono audio frame capability.                    | X                      |

| 16 slots                                               | X                      |

| Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit | X                      |

| FIFO Size                                              | X (8 Word)             |

| SPDIF                                                  | X                      |

Table 14. SAI implementation

# 3.30 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

The CAN peripheral supports:

- Supports CAN protocol version 2.0 A, B Active

- Bit rates up to 1 Mbit/s

- Transmission

- Three transmit mailboxes

- Configurable transmit priority

- Reception

- Two receive FIFOs with three stages

- 14 Scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

- Time-triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Time Stamp sent in last two data bytes

- Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

# 3.31 Secure digital input/output and MultiMediaCards Interface (SDMMC)

The card host interface (SDMMC) provides an interface between the APB peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

DS11910 Rev 4 53/201

<sup>1.</sup> X: supported

Functional overview STM32L451xx

## 3.34 Development support

#### 3.34.1 Serial wire JTAG debug port (SWJ-DP)

The Arm<sup>®</sup> SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

#### 3.34.2 Embedded Trace Macrocell™

The Arm<sup>®</sup> Embedded Trace Macrocell™ provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32L451xx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. Real-time instruction and data flow activity be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell™ operates with third party debugger software tools.

Table 18. Alternate function AF8 to AF15<sup>(1)</sup> (continued)

|        |      | AF8                        | AF9        | AF10                | AF11 | AF12                       | AF13        | AF14                        | AF15     |

|--------|------|----------------------------|------------|---------------------|------|----------------------------|-------------|-----------------------------|----------|

| Po     | ort  | UART4/<br>LPUART1/<br>CAN1 | CAN1/TSC   | CAN1/<br>QUADSPI    | -    | SDMMC1/<br>COMP1/<br>COMP2 | SAI1        | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |

|        | PB0  | -                          | -          | QUADSPI_<br>BK1_IO1 | -    | COMP1_OUT                  | SAI1_EXTCLK | -                           | EVENTOUT |

|        | PB1  | LPUART1_RTS<br>_DE         | -          | QUADSPI_<br>BK1_IO0 | -    | -                          | -           | LPTIM2_IN1                  | EVENTOUT |

|        | PB2  | -                          | -          | -                   | -    | -                          | -           | -                           | EVENTOUT |

| •      | PB3  | -                          | -          | -                   | -    | -                          | SAI1_SCK_B  | -                           | EVENTOUT |

|        | PB4  | -                          | TSC_G2_IO1 | -                   | -    | -                          | SAI1_MCLK_B | -                           | EVENTOUT |

|        | PB5  | -                          | TSC_G2_IO2 | -                   | -    | COMP2_OUT                  | SAI1_SD_B   | TIM16_BKIN                  | EVENTOUT |

|        | PB6  | CAN1_TX                    | TSC_G2_IO3 | -                   | -    | -                          | SAI1_FS_B   | TIM16_CH1N                  | EVENTOUT |

| Port B | PB7  | UART4_CTS                  | TSC_G2_IO4 | -                   | -    | -                          | -           | -                           | EVENTOUT |

| lone   | PB8  | -                          | CAN1_RX    | -                   | -    | SDMMC1_D4                  | SAI1_MCLK_A | TIM16_CH1                   | EVENTOUT |

|        | PB9  | -                          | CAN1_TX    | -                   | -    | SDMMC1_D5                  | SAI1_FS_A   | -                           | EVENTOUT |

|        | PB10 | LPUART1_RX                 | TSC_SYNC   | QUADSPI_CLK         | -    | COMP1_OUT                  | SAI1_SCK_A  | -                           | EVENTOUT |

|        | PB11 | LPUART1_TX                 | -          | QUADSPI_<br>BK1_NCS | -    | COMP2_OUT                  | -           | -                           | EVENTOUT |

|        | PB12 | LPUART1_RTS<br>_DE         | TSC_G1_IO1 | CAN1_RX             | -    | -                          | SAI1_FS_A   | TIM15_BKIN                  | EVENTOUT |

| ,      | PB13 | LPUART1_CTS                | TSC_G1_IO2 | CAN1_TX             | -    | -                          | SAI1_SCK_A  | TIM15_CH1N                  | EVENTOUT |

| ,      | PB14 | -                          | TSC_G1_IO3 | -                   | -    | -                          | SAI1_MCLK_A | TIM15_CH1                   | EVENTOUT |

|        | PB15 | -                          | TSC_G1_IO4 | -                   | -    | -                          | SAI1_SD_A   | TIM15_CH2                   | EVENTOUT |

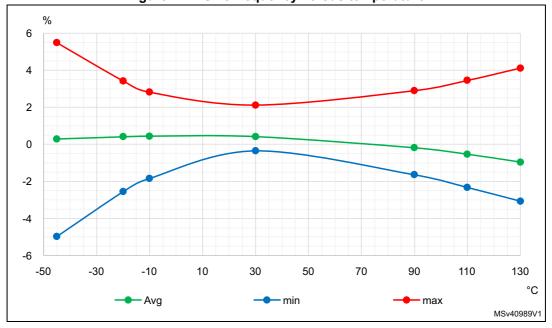

Figure 24. HSI48 frequency versus temperature

Low-speed internal (LSI) RC oscillator

Table 52. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                                 | Parameter                         | Conditions                                      | Min   | Тур | Max   | Unit  |

|----------------------------------------|-----------------------------------|-------------------------------------------------|-------|-----|-------|-------|

| f                                      | LSI Frequency                     | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 30 °C | 31.04 | -   | 32.96 | kHz   |

| f <sub>LSI</sub>                       | LSI Frequency                     | $V_{DD}$ = 1.62 to 3.6 V, $T_A$ = -40 to 125 °C | 29.5  | -   | 34    | KI IZ |

| t <sub>SU</sub> (LSI) <sup>(2)</sup>   | LSI oscillator start-<br>up time  | -                                               | -     | 80  | 130   | μs    |

| t <sub>STAB</sub> (LSI) <sup>(2)</sup> | LSI oscillator stabilization time | 5% of final frequency                           | -     | 125 | 180   | μs    |

| I <sub>DD</sub> (LSI) <sup>(2)</sup>   | LSI oscillator power consumption  | -                                               | -     | 110 | 180   | nA    |

<sup>1.</sup> Guaranteed by characterization results.

#### 6.3.9 PLL characteristics

The parameters given in *Table 53* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23: General operating conditions*.

Table 53. PLL, PLLSAI1 characteristics<sup>(1)</sup>

| Symbol  | Parameter                      | Conditions | Min | Тур | Max | Unit |

|---------|--------------------------------|------------|-----|-----|-----|------|

| f       | PLL input clock <sup>(2)</sup> | -          | 4   | ı   | 16  | MHz  |

| TPLL_IN | PLL input clock duty cycle     | -          | 45  | ı   | 55  | %    |

<sup>2.</sup> Guaranteed by design.

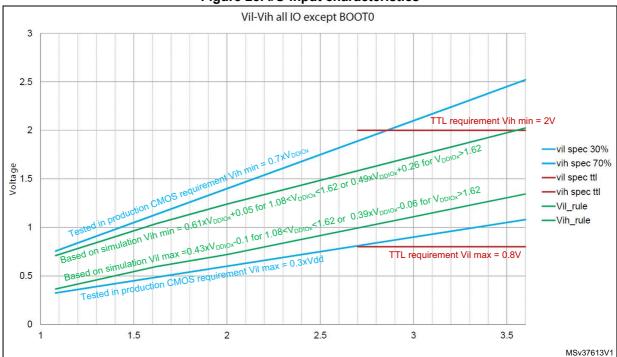

- 1. Refer to Figure 25: I/O input characteristics.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. All FT\_xx IO except PA11, PA12 and PC3 I/O.

- 5. Max(V<sub>DDXXX</sub>) is the maximum value of all the I/O supplies.

- $6. \quad \text{To sustain a voltage higher than } \text{Min}(\text{V}_{\text{DD}},\text{V}_{\text{DDA}}) + 0.3 \text{ V}, \text{ the internal Pull-up and Pull-Down resistors must be disabled}.$

- 7. This value represents the pad leakage of the IO itself. The total product pad leakage is provided by this formula:  $I_{Total\_Ileak\_max} = 10 \ \mu A + [number of IOs where V_{IN} is applied on the pad]_x I_{Ikg}(Max).$

- 8. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 25* for standard I/Os, and in *Figure 25* for 5 V tolerant I/Os.

Figure 25. I/O input characteristics

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed  $V_{OL}/V_{OH}$ ).

# 6.3.20 Voltage reference buffer characteristics

Table 75. VREFBUF characteristics<sup>(1)</sup>

| Symbol                | Parameter                                                                                       | Condition                                                                                                    | ons                        | Min                      | Тур   | Max                                     | Unit    |

|-----------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------|-------|-----------------------------------------|---------|

|                       |                                                                                                 | Normal made                                                                                                  | V <sub>RS</sub> = 0        | 2.4                      | -     | 3.6                                     |         |

|                       | Analog supply                                                                                   | Normal mode                                                                                                  | V <sub>RS</sub> = 1        | 2.8                      | -     | 3.6                                     |         |

| $V_{DDA}$             | voltage                                                                                         | Degraded mode <sup>(2)</sup>                                                                                 | V <sub>RS</sub> = 0        | 1.65                     | -     | 2.4                                     |         |

|                       |                                                                                                 | Degraded mode(=)                                                                                             | V <sub>RS</sub> = 1        | 1.65                     | -     | 2.8                                     | V       |

|                       |                                                                                                 | Normal made                                                                                                  | V <sub>RS</sub> = 0        | 2.046 <sup>(3)</sup>     | 2.048 | 2.049 <sup>(3)</sup>                    | V       |

| V <sub>REFBUF</sub> _ | Voltage reference                                                                               | Normal mode                                                                                                  | V <sub>RS</sub> = 1        | 2.498 <sup>(3)</sup>     | 2.5   | 2.502 <sup>(3)</sup>                    |         |

| OUT                   | output                                                                                          | Degraded mode <sup>(2)</sup>                                                                                 | V <sub>RS</sub> = 0        | V <sub>DDA</sub> -150 mV | -     | $V_{DDA}$                               |         |

|                       |                                                                                                 | Degraded mode( )                                                                                             | V <sub>RS</sub> = 1        | V <sub>DDA</sub> -150 mV | -     | $V_{DDA}$                               |         |

| TRIM                  | Trim step resolution                                                                            | -                                                                                                            | -                          | -                        | ±0.05 | ±0.1                                    | %       |

| CL                    | Load capacitor                                                                                  | -                                                                                                            | -                          | 0.5                      | 1     | 1.5                                     | μF      |

| esr                   | Equivalent<br>Serial Resistor<br>of Cload                                                       | -                                                                                                            | -                          | -                        | -     | 2                                       | Ω       |

| I <sub>load</sub>     | Static load current                                                                             | -                                                                                                            | -                          | -                        | -     | 4                                       | mA      |

|                       | Line regulation                                                                                 | 201/61/ 6261/                                                                                                | I <sub>load</sub> = 500 μA | -                        | 200   | 1000                                    | nnm/\/  |

| I <sub>line_reg</sub> | Line regulation                                                                                 | ulation $  2.8 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V} $ $  I_{\text{load}} = 4 \text{ mA} $ - | -                          | 100                      | 500   | ppm/V                                   |         |

| I <sub>load_reg</sub> | Load regulation                                                                                 | 500 μA ≤ I <sub>load</sub> ≤4 mA                                                                             | Normal mode                | -                        | 50    | 500                                     | ppm/mA  |

| т.                    | Temperature                                                                                     | -40 °C < T <sub>J</sub> < +125 °C                                                                            | ;                          | -                        | -     | T <sub>coeff</sub> _<br>vrefint +       | ppm/ °C |

| T <sub>Coeff</sub>    | coefficient                                                                                     | 0 °C < T <sub>J</sub> < +50 °C                                                                               |                            | -                        | -     | T <sub>coeff</sub> _<br>vrefint +<br>50 | ррпі С  |

| PSRR                  | Power supply                                                                                    | DC                                                                                                           |                            | 40                       | 60    | -                                       | dB      |

| FORK                  | rejection                                                                                       | 100 kHz                                                                                                      |                            | 25                       | 40    | -                                       | uБ      |

|                       |                                                                                                 | $CL = 0.5  \mu F^{(4)}$                                                                                      |                            | -                        | 300   | 350                                     |         |

| t <sub>START</sub>    | Start-up time                                                                                   | CL = 1.1 µF <sup>(4)</sup>                                                                                   |                            | -                        | 500   | 650                                     | μs      |

|                       |                                                                                                 | CL = 1.5 µF <sup>(4)</sup>                                                                                   |                            | -                        | 650   | 800                                     |         |

| I <sub>INRUSH</sub>   | Control of<br>maximum DC<br>current drive<br>on VREFBUF_<br>OUT during<br>start-up phase<br>(5) | -                                                                                                            | -                          | -                        | 8     | -                                       | mA      |

# 6.3.24 V<sub>BAT</sub> monitoring characteristics

Table 79. V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                               | Min | Тур | Max | Unit |

|------------------------------------|-----------------------------------------|-----|-----|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>    | -   | 39  | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement   | -   | 3   | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                              | -10 | -   | 10  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the VBAT | 12  | -   | -   | μs   |

<sup>1.</sup> Guaranteed by design.

Table 80. V<sub>BAT</sub> charging characteristics

| Symbol          | Parameter         | Conditions | Min | Тур | Max | Unit |

|-----------------|-------------------|------------|-----|-----|-----|------|

| R <sub>BC</sub> | Battery           | VBRS = 0   | -   | 5   | -   |      |

|                 | charging resistor | VBRS = 1   | -   | 1.5 | -   | kΩ   |

#### 6.3.25 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to *Section 6.3.14: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

Table 81. TIMx<sup>(1)</sup> characteristics

| Symbol                 | Parameter               | Conditions                    | Min    | Max                     | Unit                 |

|------------------------|-------------------------|-------------------------------|--------|-------------------------|----------------------|

| +                      | Timer resolution time   | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time   | f <sub>TIMxCLK</sub> = 80 MHz | 12.5   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock    | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| EXT                    | frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 80 MHz | 0      | 40                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution        | TIMx (except<br>TIM2)         | -      | 16                      | bit                  |

|                        |                         | TIM2                          | -      | 32                      |                      |

| +                      | 16-bit counter clock    | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> COUNTER   | period                  | f <sub>TIMxCLK</sub> = 80 MHz | 0.0125 | 819.2                   | μs                   |

| t <sub>MAX_COUNT</sub> | Maximum possible count  | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

|                        | with 32-bit counter     | f <sub>TIMxCLK</sub> = 80 MHz | -      | 53.68                   | s                    |

<sup>1.</sup> TIMx is used as a general term in which x stands for 1,2,3,4,5,6,7,8,15,16 or 17.

| Table 85. S | PI characteristics <sup>(1)</sup> | (continued) |

|-------------|-----------------------------------|-------------|

|-------------|-----------------------------------|-------------|

|                    | ,                      |                                                              |             |         |      |      |

|--------------------|------------------------|--------------------------------------------------------------|-------------|---------|------|------|

| Symbol             | Parameter              | Conditions                                                   | Min         | Тур     | Max  | Unit |

| t <sub>v(SO)</sub> | Data output valid time | Slave mode 2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  | - 12.5 13.5 |         | 13.5 |      |

|                    |                        | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 | -           | 12.5 24 |      | ns   |

|                    |                        | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 2 | -           | 12.5    | 33   |      |

| t <sub>v(MO)</sub> |                        | Master mode                                                  | -           | 4.5     | 6    |      |

| t <sub>h(SO)</sub> | Data output hold time  | Slave mode                                                   | 7           | -       | -    | ns   |

| t <sub>h(MO)</sub> | Data output noid time  | Master mode                                                  | 0           | -       | -    | 113  |

<sup>1.</sup> Guaranteed by characterization results.

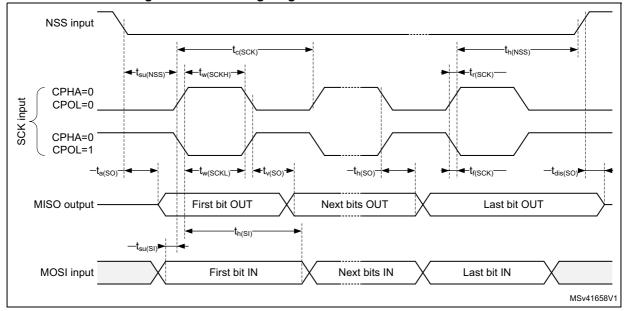

Figure 31. SPI timing diagram - slave mode and CPHA = 0

Maximum frequency in Slave transmitter mode is determined by the sum of t<sub>v(SO)</sub> and t<sub>su(MI)</sub> which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having t<sub>su(MI)</sub> = 0 while Duty(SCK) = 50 %.

Table 88. SAI characteristics<sup>(1)</sup> (continued)

| Symbol                  | Parameter              | Conditions                                                            | Min | Max | Unit |

|-------------------------|------------------------|-----------------------------------------------------------------------|-----|-----|------|

| t                       | Data output valid time | Slave transmitter (after enable edge) $2.7 \le V_{DD} \le 3.6$        | -   | 22  | ns   |

| t <sub>v(SD_B_ST)</sub> | Data output valid time | Slave transmitter (after enable edge)<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6 | ı   | 34  |      |

| t <sub>h(SD_B_ST)</sub> | Data output hold time  | Slave transmitter (after enable edge)                                 | 10  | -   | ns   |

| t <sub>v(SD_A_MT)</sub> | Data output valid time | Master transmitter (after enable edge) $2.7 \le V_{DD} \le 3.6$       | -   | 27  | ns   |

|                         | Data output valid time | Master transmitter (after enable edge) $1.71 \le V_{DD} \le 3.6$      | -   | 40  | 115  |

| t <sub>h(SD_A_MT)</sub> | Data output hold time  | Master transmitter (after enable edge)                                | 10  | -   | ns   |

- 1. Guaranteed by characterization results.

- 2. APB clock frequency must be at least twice SAI clock frequency.

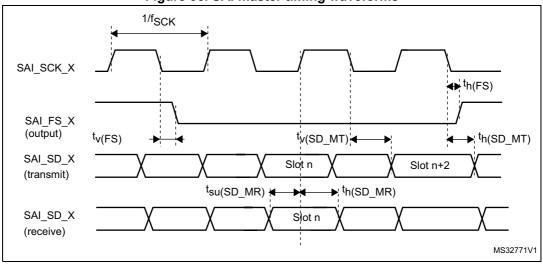

Figure 36. SAI master timing waveforms

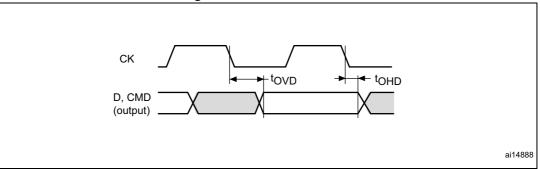

Figure 39. SD default mode

### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

177/201

STM32L451xx Package information

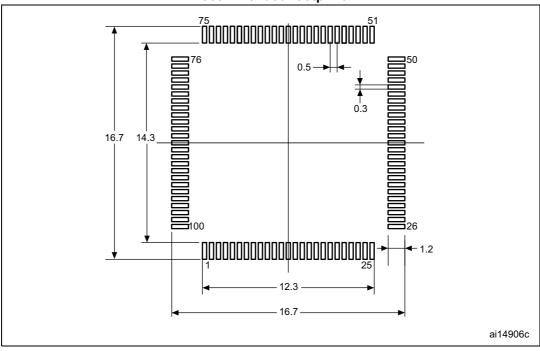

Table 91. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data (continued)

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |

|--------|--------|-------------|--------|-----------------------|--------|--------|

|        | Min    | Тур         | Max    | Min                   | Тур    | Max    |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| D3     | -      | 12.000      | -      | -                     | 0.4724 | -      |

| E      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| E3     | -      | 12.000      | -      | -                     | 0.4724 | -      |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |

| k      | 0.0°   | 3.5°        | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |

| ccc    | -      | -           | 0.080  | -                     | -      | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 41. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

Package information STM32L451xx

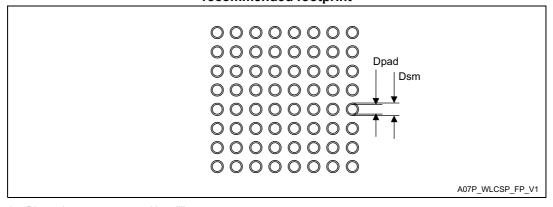

Table 97. WLCSP64 - 64-ball, 3.357x3.657 mm 0.4 mm pitch wafer level chip scale mechanical data

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

|        | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| Α      | 0.525 | 0.555       | 0.585 | 0.0207 | 0.0219                | 0.0230 |

| A1     | -     | 0.175       | -     | -      | 0.0069                | -      |

| A2     | -     | 0.380       | -     | -      | 0.0150                | -      |

| A3     | -     | 0.025       | -     | -      | 0.0010                | -      |

| b      | 0.220 | 0.250       | 0.280 | 0.0087 | 0.0098                | 0.0110 |

| D      | 3.322 | 3.357       | 3.392 | 0.1308 | 0.1322                | 0.1335 |

| E      | 3.622 | 3.657       | 3.692 | 0.1426 | 0.1440                | 0.1454 |

| е      | -     | 0.400       | -     | -      | 0.0157                | -      |

| e1     | -     | 2.800       | -     | -      | 0.1102                | -      |

| e2     | -     | 2.800       | -     | -      | 0.1102                | -      |

| F      | -     | 0.278       | -     | -      | 0.0109                | -      |

| G      | -     | 0.428       | -     | -      | 0.0169                | -      |

| aaa    | -     | -           | 0.100 | -      | -                     | 0.0039 |

| bbb    | -     | -           | 0.100 | -      | -                     | 0.0039 |

| ccc    | -     | -           | 0.100 | -      | -                     | 0.0039 |

| ddd    | -     | -           | 0.050 | -      | -                     | 0.0020 |

| eee    | -     | -           | 0.050 | -      | -                     | 0.0020 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 53. WLCSP64 - 64-pin, 3.357x3.657 mm 0.4 mm pitch wafer level chip scale recommended footprint

<sup>1.</sup> Dimensions are expressed in millimeters.

Ordering information STM32L451xx

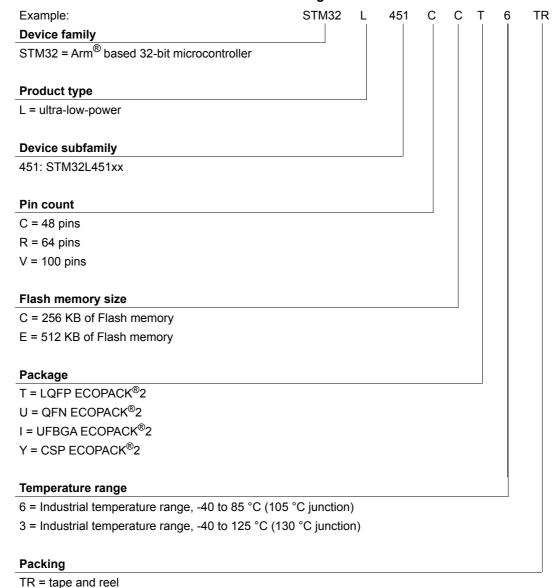

# 8 Ordering information

xxx = programmed parts

Table 101. STM32L451xx ordering information scheme

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.