Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 80MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, UART/USART      |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                   |

| Number of I/O              | 38                                                                      |

| Program Memory Size        | 256КВ (256К х 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 160K × 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

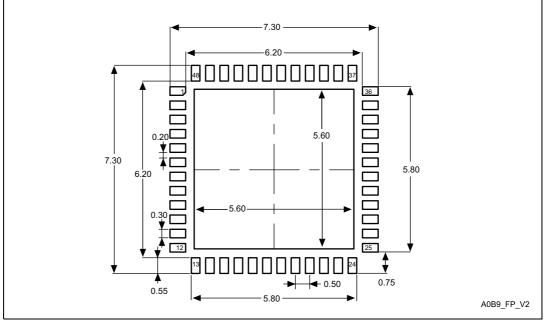

| Package / Case             | 48-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l451ccu6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4 Embedded Flash memory

STM32L451xx devices feature up to 512 Kbyte of embedded Flash memory available for storing programs and data in single bank architecture. The Flash memory contains 256 pages of 2 Kbyte.

Flexible protections can be configured thanks to option bytes:

- Readout protection (RDP) to protect the whole memory. Three levels are available:

- Level 0: no readout protection

- Level 1: memory readout protection: the Flash memory cannot be read from or written to if either debug features are connected, boot in RAM or bootloader is selected

- Level 2: chip readout protection: debug features (Cortex-M4 JTAG and serial wire), boot in RAM and bootloader selection are disabled (JTAG fuse). This selection is irreversible.

| Area                                | Protection | U    | ser executio | on                 | Debug, boot from RAM or boot<br>from system memory (loader) |       |                    |  |

|-------------------------------------|------------|------|--------------|--------------------|-------------------------------------------------------------|-------|--------------------|--|

| level                               |            | Read | Write        | Erase              | Read                                                        | Write | Erase              |  |

| Main                                | 1          | Yes  | Yes          | Yes                | No                                                          | No    | No                 |  |

| memory                              | 2          | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |

| System<br>memory<br>Option<br>bytes | 1          | Yes  | No           | No                 | Yes                                                         | No    | No                 |  |

|                                     | 2          | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |

|                                     | 1          | Yes  | Yes          | Yes                | Yes                                                         | Yes   | Yes                |  |

|                                     | 2          | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |

| Backup                              | 1          | Yes  | Yes          | N/A <sup>(1)</sup> | No                                                          | No    | N/A <sup>(1)</sup> |  |

| registers                           | 2          | Yes  | Yes          | N/A                | N/A                                                         | N/A   | N/A                |  |

| SRAM2                               | 1          | Yes  | Yes          | Yes <sup>(1)</sup> | No                                                          | No    | No <sup>(1)</sup>  |  |

| SNAIVIZ                             | 2          | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |

#### Table 3. Access status versus readout protection level and execution modes

1. Erased when RDP change from Level 1 to Level 0.

- Write protection (WRP): the protected area is protected against erasing and programming. Two areas can be selected, with 2-Kbyte granularity.

- Proprietary code readout protection (PCROP): a part of the flash memory can be

protected against read and write from third parties. The protected area is execute-only:

it can only be reached by the STM32 CPU, as an instruction code, while all other

accesses (DMA, debug and CPU data read, write and erase) are strictly prohibited.

The PCROP area granularity is 64-bit wide. An additional option bit (PCROP\_RDP)

allows to select if the PCROP area is erased or not when the RDP protection is

changed from Level 1 to Level 0.

## 3.11 Clocks and startup

The clock controller (see *Figure 4*) distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source:** four different clock sources can be used to drive the master clock SYSCLK:

- 4-48 MHz high-speed external crystal or ceramic resonator (HSE), that can supply a PLL. The HSE can also be configured in bypass mode for an external clock.

- 16 MHz high-speed internal RC oscillator (HSI16), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 12 frequencies from 100 kHz to 48 MHz. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be automatically trimmed by hardware to reach better than ±0.25% accuracy. The MSI can supply a PLL.

- System PLL which can be fed by HSE, HSI16 or MSI, with a maximum frequency at 80 MHz.

- **RC48 with clock recovery system (HSI48)**: internal RC48 MHz clock source can be used to drive the SDMMC or the RNG peripherals. This clock can be output on the MCO.

- **Auxiliary clock source:** two ultralow-power clock sources that can be used to drive the real-time clock:

- 32.768 kHz low-speed external crystal (LSE), supporting four drive capability modes. The LSE can also be configured in bypass mode for an external clock.

- 32 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock accuracy is ±5% accuracy.

- **Peripheral clock sources:** Several peripherals (SDMMC, RNG, SAI, USARTs, I2Cs, LPTimers, ADC) have their own independent clock whatever the system clock. Two PLLs, each having three independent outputs allowing the highest flexibility, can generate independent clocks for the ADC, the SDMMC/RNG and the SAI.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 4 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- **Clock security system (CSS):** this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI16 and a software

The main features of the touch sensing controller are the following:

- Proven and robust surface charge transfer acquisition principle

- Supports up to 21 capacitive sensing channels

- Up to 3 capacitive sensing channels can be acquired in parallel offering a very good response time

- Spread spectrum feature to improve system robustness in noisy environments

- Full hardware management of the charge transfer acquisition sequence

- Programmable charge transfer frequency

- Programmable sampling capacitor I/O pin

- Programmable channel I/O pin

- Programmable max count value to avoid long acquisition when a channel is faulty

- Dedicated end of acquisition and max count error flags with interrupt capability

- One sampling capacitor for up to 3 capacitive sensing channels to reduce the system components

- Compatible with proximity, touchkey, linear and rotary touch sensor implementation

- Designed to operate with STMTouch touch sensing firmware library

## 3.21 Digital filter for Sigma-Delta Modulators (DFSDM)

The device embeds one DFSDM with 2 digital filters modules and 4 external input serial channels (transceivers) or alternately 4 internal parallel inputs support.

The DFSDM peripheral is dedicated to interface the external  $\Sigma\Delta$  modulators to microcontroller and then to perform digital filtering of the received data streams (which represent analog value on  $\Sigma\Delta$  modulators inputs). DFSDM can also interface PDM (Pulse Density Modulation) microphones and perform PDM to PCM conversion and filtering in

*Note:* The number of capacitive sensing channels is dependent on the size of the packages and subject to I/O availability.

The Quad SPI interface supports:

- Three functional modes: indirect, status-polling, and memory-mapped

- Dual-flash mode, where 8 bits can be sent/received simultaneously by accessing two flash memories in parallel.

- SDR and DDR support

- Fully programmable opcode for both indirect and memory mapped mode

- Fully programmable frame format for both indirect and memory mapped mode

- Each of the 5 following phases can be configured independently (enable, length, single/dual/quad communication)

- Instruction phase

- Address phase

- Alternate bytes phase

- Dummy cycles phase

- Data phase

- Integrated FIFO for reception and transmission

- 8, 16, and 32-bit data accesses are allowed

- DMA channel for indirect mode operations

- Programmable masking for external flash flag management

- Timeout management

- Interrupt generation on FIFO threshold, timeout, status match, operation complete, and access error

|   | 1                            | 2    | 3   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5        | 6   | 7               | 8                       | 9           | 10                    | 11                    | 12   |  |  |

|---|------------------------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-----------------|-------------------------|-------------|-----------------------|-----------------------|------|--|--|

|   | · · ·                        | -    |     | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -        |     |                 |                         | ,           | .•                    |                       |      |  |  |

| Α | PE3                          | PE1  | PB8 | PH3-BOOT0<br>(BOOT0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PD7      | PD5 | PB4<br>(NJTRST) | PB3 (JTDO/<br>TRACESWO) | PA15 (JTDI) | PA14 (JTCK/<br>SWCLK) | PA13 (JTMS/<br>SWDIO) | PA12 |  |  |

| в | PE4                          | PE2  | PB9 | PB7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PB6      | PD6 | PD4             | PD3                     | PD1         | PC12                  | PC10                  | PA11 |  |  |

| с | PC13                         | PE5  | PE0 | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PB5      |     |                 | PD2                     | PD0         | PC11                  | VDD                   | PA10 |  |  |

| D | PC14-<br>OSC32_IN<br>(PC14)  | PE6  | vss |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PA9      |     |                 |                         |             |                       |                       | PC9  |  |  |

| E | PC15-<br>OSC32_OUT<br>(PC15) | VBAT | vss |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PC8      |     |                 |                         |             |                       | PC7                   | PC6  |  |  |

| F | PH0-OSC_IN<br>(PH0)          | VSS  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | UFBGA100 |     |                 |                         |             |                       | VSS                   | VSS  |  |  |

| G | PH1-<br>OSC_OUT<br>(PH1)     | VDD  |     | VDD         VID         VID <td colspan="6" rowspan="2"></td> |          |     |                 |                         |             |                       |                       |      |  |  |

| н | PC0                          | NRST | VDD |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |     |                 |                         |             |                       |                       |      |  |  |

| L | VSSA                         | PC1  | PC2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |     |                 |                         |             | PD12                  | PD11                  | PD10 |  |  |

| к | VREF-                        | PC3  | PA2 | PA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PC4      |     |                 | PD9                     | PD8         | PB15                  | PB14                  | PB13 |  |  |

| L | VREF+                        | PA0  | PA3 | PA6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PC5      | PB2 | PE8             | PE10                    | PE12        | PB10                  | PB11                  | PB12 |  |  |

| м | VDDA                         | PA1  | PA4 | PA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PB0      | PB1 | PE7             | PE9                     | PE11        | PE13                  | PE14                  | PE15 |  |  |

|   |                              |      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |     |                 |                         |             |                       |                       | MSv4 |  |  |

Figure 7. STM32L451Vx UFBGA100 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

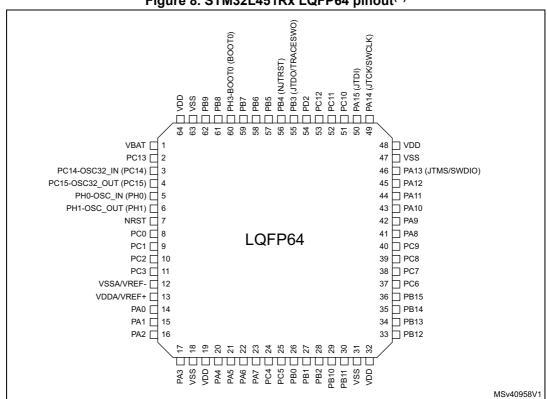

Figure 8. STM32L451Rx LQFP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

|                 | I       | Pin I  | Num     | ber     |          | fer                                   |          |               |       |                                                                              |                      | Pin fund | ctions |

|-----------------|---------|--------|---------|---------|----------|---------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------|----------------------|----------|--------|

| <b>UFQFPN48</b> | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                          | Additional functions |          |        |

| 45              | A6      | 61     | B3      | 95      | A3       | PB8                                   | I/O      | FT_f          | -     | I2C1_SCL, CAN1_RX,<br>SDMMC1_D4,<br>SAI1_MCLK_A,<br>TIM16_CH1, EVENTOUT      | -                    |          |        |

| 46              | C6      | 62     | A3      | 96      | В3       | PB9                                   | I/O      | FT_f          | -     | IR_OUT, I2C1_SDA,<br>SPI2_NSS, CAN1_TX,<br>SDMMC1_D5, SAI1_FS_A,<br>EVENTOUT | -                    |          |        |

| -               | -       | -      | -       | 97      | C3       | PE0                                   | I/O      | FT            | -     | TIM16_CH1, EVENTOUT                                                          | -                    |          |        |

| -               | -       | -      | -       | 98      | A2       | PE1                                   | I/O      | FT            | -     | EVENTOUT                                                                     | -                    |          |        |

| 47              | A7      | 63     | D4      | 99      | D3       | VSS                                   | S        | -             | -     | -                                                                            | -                    |          |        |

| 48              | A8      | 64     | E4      | 100     | C4       | VDD                                   | S        | -             | -     | -                                                                            | -                    |          |        |

#### Table 16. STM32L451xx pin definitions (continued)

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF

These GPIOs must not be used as current sources (e.g. to drive an LED).

After a Backup domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the RTC registers which are not reset by the system reset. For details on how to manage these GPIOs, refer to the Backup domain and RTC register descriptions in the RM0394 reference manual.

3. After reset, these pins are configured as JTAG/SW debug alternate functions, and the internal pull-up on PA15, PA13, PB4 pins and the internal pull-down on PA14 pin are activated.

| ST      |  |

|---------|--|

| $\leq$  |  |

| S       |  |

| 2       |  |

| 4       |  |

| ъ       |  |

| <u></u> |  |

| X       |  |

| $\sim$  |  |

Pinouts and pin description

|        |      |                            | Tabl       | e 18. Alternate     | function AF8 | to AF15 <sup>(1)</sup> (cont | inued)      |                             |          |

|--------|------|----------------------------|------------|---------------------|--------------|------------------------------|-------------|-----------------------------|----------|

|        |      | AF8                        | AF9        | AF10                | AF11         | AF12                         | AF13        | AF14                        | AF15     |

| Po     | ort  | UART4/<br>LPUART1/<br>CAN1 | CAN1/TSC   | CAN1/<br>QUADSPI    | -            | SDMMC1/<br>COMP1/<br>COMP2   | SAI1        | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |

|        | PB0  | -                          | -          | QUADSPI_<br>BK1_IO1 | -            | COMP1_OUT                    | SAI1_EXTCLK | -                           | EVENTOUT |

|        | PB1  | LPUART1_RTS<br>_DE         | -          | QUADSPI_<br>BK1_IO0 | -            | -                            | -           | LPTIM2_IN1                  | EVENTOUT |

|        | PB2  | -                          | -          | -                   | -            | -                            | -           | -                           | EVENTOUT |

|        | PB3  | -                          | -          | -                   | -            | -                            | SAI1_SCK_B  | -                           | EVENTOUT |

|        | PB4  | -                          | TSC_G2_IO1 | -                   | -            | -                            | SAI1_MCLK_B | -                           | EVENTOUT |

|        | PB5  | -                          | TSC_G2_IO2 | -                   | -            | COMP2_OUT                    | SAI1_SD_B   | TIM16_BKIN                  | EVENTOUT |

|        | PB6  | CAN1_TX                    | TSC_G2_IO3 | -                   | -            | -                            | SAI1_FS_B   | TIM16_CH1N                  | EVENTOUT |

| Port B | PB7  | UART4_CTS                  | TSC_G2_IO4 | -                   | -            | -                            | -           | -                           | EVENTOUT |

| POILE  | PB8  | -                          | CAN1_RX    | -                   | -            | SDMMC1_D4                    | SAI1_MCLK_A | TIM16_CH1                   | EVENTOUT |

|        | PB9  | -                          | CAN1_TX    | -                   | -            | SDMMC1_D5                    | SAI1_FS_A   | -                           | EVENTOUT |

|        | PB10 | LPUART1_RX                 | TSC_SYNC   | QUADSPI_CLK         | -            | COMP1_OUT                    | SAI1_SCK_A  | -                           | EVENTOUT |

|        | PB11 | LPUART1_TX                 | -          | QUADSPI_<br>BK1_NCS | -            | COMP2_OUT                    | -           | -                           | EVENTOUT |

|        | PB12 | LPUART1_RTS<br>_DE         | TSC_G1_IO1 | CAN1_RX             | -            | -                            | SAI1_FS_A   | TIM15_BKIN                  | EVENTOUT |

|        | PB13 | LPUART1_CTS                | TSC_G1_IO2 | CAN1_TX             | -            | -                            | SAI1_SCK_A  | TIM15_CH1N                  | EVENTOUT |

|        | PB14 | -                          | TSC_G1_IO3 | -                   | -            | -                            | SAI1_MCLK_A | TIM15_CH1                   | EVENTOUT |

|        | PB15 | -                          | TSC_G1_IO4 | -                   | -            | -                            | SAI1_SD_A   | TIM15_CH2                   | EVENTOUT |

DS11910 Rev 4

5

77/201

### 6.1.6 Power supply scheme

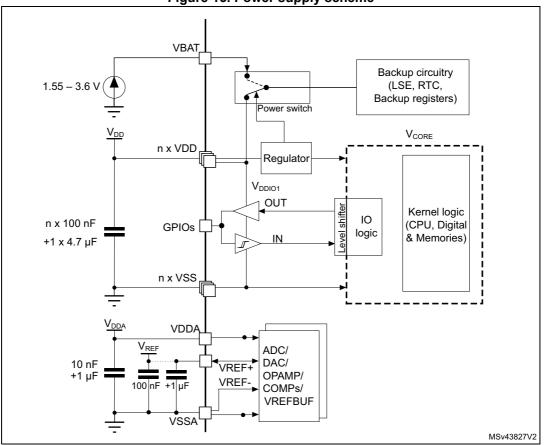

Figure 15. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

## 6.3.4 Embedded voltage reference

The parameters given in *Table 26* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

| [                                         |                                                                     | 1                                 |                  | 1     |                     |                          |

|-------------------------------------------|---------------------------------------------------------------------|-----------------------------------|------------------|-------|---------------------|--------------------------|

| Symbol                                    | Parameter                                                           | Conditions                        | Min              | Тур   | Мах                 | Unit                     |

| V <sub>REFINT</sub>                       | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +130 °C | 1.182            | 1.212 | 1.232               | V                        |

| t <sub>S_vrefint</sub> <sup>(1)</sup>     | ADC sampling time when<br>reading the internal reference<br>voltage | -                                 | 4 <sup>(2)</sup> | -     | -                   | μs                       |

| t <sub>start_vrefint</sub>                | Start time of reference voltage buffer when ADC is enable           | -                                 | -                | 8     | 12 <sup>(2)</sup>   | μs                       |

| I <sub>DD</sub> (V <sub>REFINTBUF</sub> ) | $V_{REFINT}$ buffer consumption from $V_{DD}$ when converted by ADC | -                                 | -                | 12.5  | 20 <sup>(2)</sup>   | μA                       |

| $\Delta V_{REFINT}$                       | Internal reference voltage spread over the temperature range        | V <sub>DD</sub> = 3 V             | -                | 5     | 7.5 <sup>(2)</sup>  | mV                       |

| T <sub>Coeff</sub>                        | Temperature coefficient                                             | –40°C < T <sub>A</sub> < +130°C   | -                | 30    | 50 <sup>(2)</sup>   | ppm/°C                   |

| A <sub>Coeff</sub>                        | Long term stability                                                 | 1000 hours, T = 25°C              | -                | 300   | 1000 <sup>(2)</sup> | ppm                      |

| V <sub>DDCoeff</sub>                      | Voltage coefficient                                                 | $3.0 V < V_{DD} < 3.6 V$          | -                | 250   | 1200 <sup>(2)</sup> | ppm/V                    |

| V <sub>REFINT_DIV1</sub>                  | 1/4 reference voltage                                               |                                   | 24               | 25    | 26                  |                          |

| V <sub>REFINT_DIV2</sub>                  | 1/2 reference voltage                                               | -                                 | 49               | 50    | 51                  | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub>                  | 3/4 reference voltage                                               |                                   | 74               | 75    | 76                  |                          |

1. The shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 61: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 41: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

${\rm I}_{\rm SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DDIOx</sub> is the I/O supply voltage

$f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$  +  $C_{S}$

$C_S$  is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 41*. The MCU is placed under the following conditions:

- All I/O pins are in Analog mode

- The given value is calculated by measuring the difference of the current consumptions:

- when the peripheral is clocked on

- when the peripheral is clocked off

- Ambient operating temperature and supply voltage conditions summarized in *Table 20: Voltage characteristics*

- The power consumption of the digital part of the on-chip peripherals is given in *Table 41*. The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

| Peripheral |                                   | Range 1 | Range 2 | Low-power run<br>and sleep | Unit   |

|------------|-----------------------------------|---------|---------|----------------------------|--------|

|            | Bus Matrix <sup>(1)</sup>         | 3.2     | 2.9     | 3.1                        |        |

|            | ADC independent clock domain      | 0.4     | 0.1     | 0.2                        |        |

|            | ADC clock domain                  | 2.1     | 1.9     | 1.9                        |        |

|            | CRC                               | 0.4     | 0.2     | 0.3                        |        |

|            | DMA1                              | 1.4     | 1.3     | 1.4                        |        |

|            | DMA2                              | 1.5     | 1.3     | 1.4                        |        |

|            | FLASH                             | 6.2     | 5.2     | 5.8                        |        |

|            | GPIOA <sup>(2)</sup>              | 1.7     | 1.4     | 1.6                        |        |

|            | GPIOB <sup>(2)</sup> )            | 1.6     | 1.3     | 1.6                        |        |

|            | GPIOC <sup>(2)</sup>              | 1.7     | 1.5     | 1.6                        |        |

| AHB        | GPIOD <sup>(2)</sup>              | 1.8     | 1.6     | 1.7                        |        |

|            | GPIOE <sup>(2)</sup>              | 1.7     | 1.6     | 1.6                        | µA/MHz |

|            | GPIOH <sup>(2)</sup>              | 0.6     | 0.6     | 0.5                        |        |

|            | QSPI                              | 7.0     | 5.8     | 7.3                        |        |

|            | RNG independent clock domain      | 2.2     | N/A     | N/A                        |        |

|            | RNG clock domain                  | 0.5     | N/A     | N/A                        |        |

|            | SRAM1                             | 0.8     | 0.9     | 0.7                        |        |

|            | SRAM2                             | 1.0     | 0.8     | 0.8                        |        |

|            | TSC                               | 1.6     | 1.3     | 1.3                        |        |

|            | All AHB Peripherals               | 25.2    | 21.7    | 23.6                       |        |

|            | AHB to APB1 bridge <sup>(3)</sup> | 0.9     | 0.7     | 0.9                        |        |

| APB1       | CAN1                              | 4.1     | 3.2     | 3.9                        |        |

|            | DAC1                              | 2.4     | 1.8     | 2.2                        |        |

#### Table 41. Peripheral current consumption

|      | Peripheral                       | Range 1 | Range 2 | Low-power run<br>and sleep | Unit   |

|------|----------------------------------|---------|---------|----------------------------|--------|

|      | RTCA                             | 1.7     | 1.1     | 2.1                        |        |

|      | CRS                              | 0.3     | 0.3     | 0.6                        |        |

|      | I2C1 independent clock domain    | 3.5     | 2.8     | 3.4                        |        |

|      | I2C1 clock domain                | 1.1     | 0.9     | 1.0                        |        |

|      | I2C2 independent clock domain    | 3.5     | 3.0     | 3.4                        |        |

|      | I2C2 clock domain                | 1.1     | 0.7     | 0.9                        |        |

|      | I2C3 independent clock domain    | 2.9     | 2.3     | 2.5                        |        |

|      | I2C3 clock domain                | 0.9     | 0.4     | 0.8                        |        |

|      | LPUART1 independent clock domain | 1.9     | 1.6     | 1.8                        |        |

|      | LPUART1 clock domain             | 0.6     | 0.6     | 0.6                        |        |

|      | LPTIM1 independent clock domain  | 2.9     | 2.4     | 2.8                        |        |

|      | LPTIM1 clock domain              | 0.8     | 0.4     | 0.7                        |        |

| APB1 | LPTIM2 independent clock domain  | 3.1     | 2.7     | 3.9                        | µA/MHz |

|      | LPTIM2 clock domain              | 0.8     | 0.7     | 0.8                        |        |

|      | OPAMP                            | 0.4     | 0.2     | 0.4                        |        |

|      | PWR                              | 0.4     | 0.1     | 0.4                        |        |

|      | SPI2                             | 1.8     | 1.6     | 1.6                        |        |

|      | SPI3                             | 1.7     | 1.3     | 1.6                        |        |

|      | TIM2                             | 6.2     | 5.0     | 5.9                        |        |

|      | TIM6                             | 1.0     | 0.6     | 0.9                        |        |

|      | USART2 independent clock domain  | 4.1     | 3.6     | 3.8                        |        |

|      | USART2 clock domain              | 1.3     | 0.9     | 1.1                        |        |

|      | USART3 independent clock domain  | 4.3     | 3.5     | 4.2                        |        |

|      | USART3 clock domain              | 1.5     | 1.1     | 1.3                        |        |

|      | WWDG                             | 0.5     | 0.5     | 0.5                        |        |

|      | All APB1 on                      | 51.5    | 35.5    | 48.6                       |        |

Table 41. Peripheral current consumption (continued)

## 6.3.7 External clock source characteristics

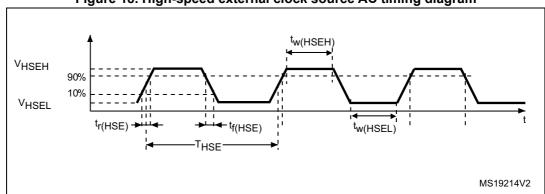

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 18: High-speed external clock source AC timing diagram*.

| Symbol               | Parameter                            | Conditions                 | Min                    | Тур | Max                    | Unit |

|----------------------|--------------------------------------|----------------------------|------------------------|-----|------------------------|------|

| f                    | User external clock source frequency | Voltage scaling<br>Range 1 | -                      | 8   | 48                     | MHz  |

| f <sub>HSE_ext</sub> |                                      | Voltage scaling<br>Range 2 | -                      | 8   | 26                     |      |

| V <sub>HSEH</sub>    | OSC_IN input pin high level voltage  | -                          | $0.7 V_{\text{DDIOx}}$ | -   | V <sub>DDIOx</sub>     | V    |

| V <sub>HSEL</sub>    | OSC_IN input pin low level voltage   | -                          | V <sub>SS</sub>        | -   | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(HSEH)</sub> | OSC IN high or low time              | Voltage scaling<br>Range 1 | 7                      | -   | -                      | 2    |

| t <sub>w(HSEL)</sub> |                                      | Voltage scaling<br>Range 2 | 18                     | -   | -                      | ns   |

|  | Table 45. High-speed | external user clo | ck characteristics <sup>(1)</sup> |

|--|----------------------|-------------------|-----------------------------------|

|--|----------------------|-------------------|-----------------------------------|

1. Guaranteed by design.

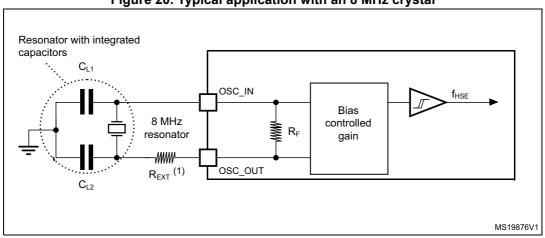

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 48*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                                  | Parameter                                    | Conditions <sup>(2)</sup>                        | Min | Тур | Max  | Unit |  |

|-----------------------------------------|----------------------------------------------|--------------------------------------------------|-----|-----|------|------|--|

| I <sub>DD(LSE)</sub> LSE current consur |                                              | LSEDRV[1:0] = 00<br>Low drive capability         | -   | 250 | -    |      |  |

|                                         |                                              | LSEDRV[1:0] = 01<br>Medium low drive capability  | -   | 315 | -    | nA   |  |

|                                         |                                              | LSEDRV[1:0] = 10<br>Medium high drive capability | -   | 500 | -    | ПА   |  |

|                                         |                                              | LSEDRV[1:0] = 11<br>High drive capability        | -   | 630 | -    |      |  |

|                                         | Maximum critical crystal<br><sup>ax</sup> gm | LSEDRV[1:0] = 00<br>Low drive capability         | -   | -   | 0.5  |      |  |

| Gm <sub>critmax</sub>                   |                                              | LSEDRV[1:0] = 01<br>Medium low drive capability  | -   | -   | 0.75 |      |  |

|                                         |                                              | LSEDRV[1:0] = 10<br>Medium high drive capability | -   | -   | 1.7  | μΑ/V |  |

|                                         |                                              | LSEDRV[1:0] = 11<br>High drive capability        | -   | -   | 2.7  |      |  |

| t <sub>SU(LSE)</sub> <sup>(3)</sup>     | Startup time                                 | V <sub>DD</sub> is stabilized                    | -   | 2   | -    | s    |  |

| Table 48. LSE oscillator ch | aracteristics (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|-----------------------------|--------------------------------------------------------------|

|-----------------------------|--------------------------------------------------------------|

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions      | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |

|------------------|------------|-----------------|-----------------------------|---------------------------------------------------|------|

|                  |            |                 | inequency band              | 8 MHz/ 80 MHz                                     |      |

|                  |            | LOEP100 package | 0.1 MHz to 30 MHz           | -8                                                |      |

|                  |            |                 | 30 MHz to 130 MHz           | 2                                                 | dBµV |

| S <sub>EMI</sub> | Peak level |                 | 130 MHz to 1 GHz            | 5                                                 | υσμν |

|                  |            |                 | 1 GHz to 2 GHz              | 8                                                 |      |

|                  |            |                 | EMI Level                   | 2.5                                               | -    |

Table 57. EMI characteristics

## 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                               | Conditions                                                         | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \degree C$ , conforming<br>to ANSI/ESDA/JEDEC<br>JS-001 | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C},$<br>conforming to ANSI/ESD<br>STM5.3.1      | C3    | 250                             | v    |

| Table 58. | ESD absolute | maximum | ratings |

|-----------|--------------|---------|---------|

| 14010 001 |              |         |         |

1. Guaranteed by characterization results.

| Sym-<br>bol           | Parameter               | Conditions <sup>(4)</sup>                                                                                                  |                         |                          |      | Тур  | Max | Unit |

|-----------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|------|------|-----|------|

|                       |                         |                                                                                                                            | Single                  | Fast channel (max speed) | -    | 4    | 5   |      |

| ст.                   | Total                   |                                                                                                                            | ended                   | Slow channel (max speed) | -    | 4    | 5   |      |

| ET                    | unadjusted<br>error     |                                                                                                                            | Differential            | Fast channel (max speed) | -    | 3.5  | 4.5 |      |

|                       |                         |                                                                                                                            | Differential            | Slow channel (max speed) | -    | 3.5  | 4.5 |      |

|                       |                         |                                                                                                                            | Single                  | Fast channel (max speed) | -    | 1    | 2.5 |      |

| EO                    | Offset                  |                                                                                                                            | ended                   | Slow channel (max speed) | -    | 1    | 2.5 |      |

| EO                    | error                   |                                                                                                                            | Differential            | Fast channel (max speed) | -    | 1.5  | 2.5 |      |

|                       |                         |                                                                                                                            | Differential            | Slow channel (max speed) | -    | 1.5  | 2.5 |      |

|                       |                         |                                                                                                                            | Single                  | Fast channel (max speed) | -    | 2.5  | 4.5 |      |

| 50                    |                         |                                                                                                                            | ended                   | Slow channel (max speed) | -    | 2.5  | 4.5 |      |

| EG                    | Gain error              |                                                                                                                            | Differential            | Fast channel (max speed) | -    | 2.5  | 3.5 | LSB  |

|                       |                         |                                                                                                                            | Differential            | Slow channel (max speed) | -    | 2.5  | 3.5 | -    |

|                       |                         |                                                                                                                            | Single<br>ended         | Fast channel (max speed) | -    | 1    | 1.5 |      |

|                       | Differential            | rentialerityADC clock frequency $\leq$ 80 MHz,ISampling rate $\leq$ 5.33 Msps,V <sub>DDA</sub> = VREF+ = 3 V,ralTA = 25 °C |                         | Slow channel (max speed) | -    | 1    | 1.5 |      |

| ED linearity<br>error | -                       |                                                                                                                            | Differential            | Fast channel (max speed) | -    | 1    | 1.2 |      |

|                       |                         |                                                                                                                            |                         | Slow channel (max speed) | -    | 1    | 1.2 |      |

|                       |                         |                                                                                                                            | A = VREF+ = 3 V, Single | Fast channel (max speed) | -    | 1.5  | 2.5 |      |

| -                     | Integral                |                                                                                                                            |                         | Slow channel (max speed) | -    | 1.5  | 2.5 | -    |

| EL                    | linearity<br>error      |                                                                                                                            | Differential            | Fast channel (max speed) | -    | 1    | 2   |      |

|                       |                         |                                                                                                                            |                         | Slow channel (max speed) | -    | 1    | 2   |      |

|                       |                         |                                                                                                                            | Single                  | Fast channel (max speed) | 10.4 | 10.5 | -   |      |

|                       | Effective               |                                                                                                                            | ended                   | Slow channel (max speed) | 10.4 | 10.5 | -   | 1,   |

| ENOB                  | number of bits          |                                                                                                                            | Differential            | Fast channel (max speed) | 10.8 | 10.9 | -   | bits |

|                       |                         |                                                                                                                            | Dillerential            | Slow channel (max speed) | 10.8 | 10.9 | -   | 1    |

|                       | Signal to               |                                                                                                                            | Single                  | Fast channel (max speed) | 64.4 | 65   | -   |      |

| SINAD                 | Signal-to-<br>noise and |                                                                                                                            | ended                   | Slow channel (max speed) | 64.4 | 65   | -   | 1    |

| SINAD                 | distortion<br>ratio     |                                                                                                                            | Differential            | Fast channel (max speed) | 66.8 | 67.4 | -   |      |

|                       | Tallo                   |                                                                                                                            | Differential            | Slow channel (max speed) | 66.8 | 67.4 | -   | ٩D   |

|                       |                         |                                                                                                                            | Single                  | Fast channel (max speed) | 65   | 66   | -   | dB   |

|                       | Signal-to-              |                                                                                                                            | ended                   | Slow channel (max speed) | 65   | 66   | -   |      |

| SNR                   | noise ratio             |                                                                                                                            | Differential            | Fast channel (max speed) | 67   | 68   | -   |      |

|                       |                         |                                                                                                                            | Differential            | Slow channel (max speed) | 67   | 68   | -   |      |

## Table 69. ADC accuracy - limited test conditions $1^{(1)(2)(3)}$

| Sym-<br>bol           | Parameter               | Conditions <sup>(4)</sup>                                                                                                |                    |                          | Min  | Тур  | Max | Unit |

|-----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------|------|------|-----|------|

|                       |                         |                                                                                                                          | Single             | Fast channel (max speed) | -    | 4    | 6.5 |      |

| ET                    | Total                   |                                                                                                                          | ended              | Slow channel (max speed) | -    | 4    | 6.5 |      |

|                       | unadjusted<br>error     |                                                                                                                          | Differential       | Fast channel (max speed) | -    | 3.5  | 5.5 |      |

|                       |                         |                                                                                                                          | Dillerential       | Slow channel (max speed) | -    | 3.5  | 5.5 |      |

|                       |                         |                                                                                                                          | Single             | Fast channel (max speed) | -    | 1    | 4.5 |      |

| EO                    | Offset                  |                                                                                                                          | ended              | Slow channel (max speed) | -    | 1    | 5   |      |

| EU                    | error                   |                                                                                                                          | Differential       | Fast channel (max speed) | -    | 1.5  | 3   |      |

|                       |                         |                                                                                                                          | Dillerential       | Slow channel (max speed) | -    | 1.5  | 3   |      |

|                       |                         |                                                                                                                          | Single             | Fast channel (max speed) | -    | 2.5  | 6   |      |

| EG                    | Coin orror              |                                                                                                                          | ended              | Slow channel (max speed) | -    | 2.5  | 6   | LSB  |

| EG                    | Gain error              | error                                                                                                                    | Differential       | Fast channel (max speed) | -    | 2.5  | 3.5 | LOD  |

|                       |                         |                                                                                                                          | Dillerential       | Slow channel (max speed) | -    | 2.5  | 3.5 | -    |

|                       |                         |                                                                                                                          | Single<br>ended    | Fast channel (max speed) | -    | 1    | 1.5 |      |

| ED                    | Differential            | earity<br>ror<br>ADC clock frequency $\leq$<br>80 MHz,<br>Sampling rate $\leq$ 5.33 Msps,<br>2 V $\leq$ V <sub>DDA</sub> |                    | Slow channel (max speed) | -    | 1    | 1.5 |      |

| ED linearity<br>error | -                       |                                                                                                                          | Differential       | Fast channel (max speed) | -    | 1    | 1.2 |      |

|                       |                         |                                                                                                                          |                    | Slow channel (max speed) | -    | 1    | 1.2 |      |

|                       |                         |                                                                                                                          | s, Single<br>ended | Fast channel (max speed) | -    | 1.5  | 3.5 |      |

| EL                    | Integral                |                                                                                                                          |                    | Slow channel (max speed) | -    | 1.5  | 3.5 | -    |

| EL                    | error                   |                                                                                                                          | Differential       | Fast channel (max speed) | -    | 1    | 3   |      |

|                       |                         |                                                                                                                          |                    | Slow channel (max speed) | -    | 1    | 2.5 |      |

|                       |                         |                                                                                                                          | Single<br>ended    | Fast channel (max speed) | 10   | 10.5 | -   | 1    |

|                       | Effective               |                                                                                                                          |                    | Slow channel (max speed) | 10   | 10.5 | -   | hita |

| ENOB                  | number of bits          |                                                                                                                          | Differential       | Fast channel (max speed) | 10.7 | 10.9 | -   | bits |

|                       |                         |                                                                                                                          | Differential       | Slow channel (max speed) | 10.7 | 10.9 | -   |      |

|                       | Olarral ta              |                                                                                                                          | Single             | Fast channel (max speed) | 62   | 65   | -   |      |

|                       | Signal-to-<br>noise and |                                                                                                                          | ended              | Slow channel (max speed) | 62   | 65   | -   |      |