#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 80MHz                                                                      |

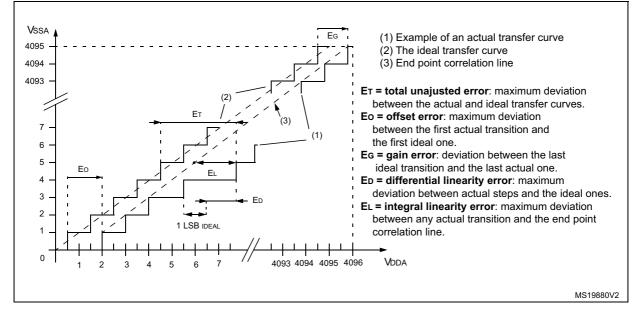

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                      |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 256КВ (256К х 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 160K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-UFBGA                                                                   |

| Supplier Device Package    | 64-UFBGA (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l451rci6      |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

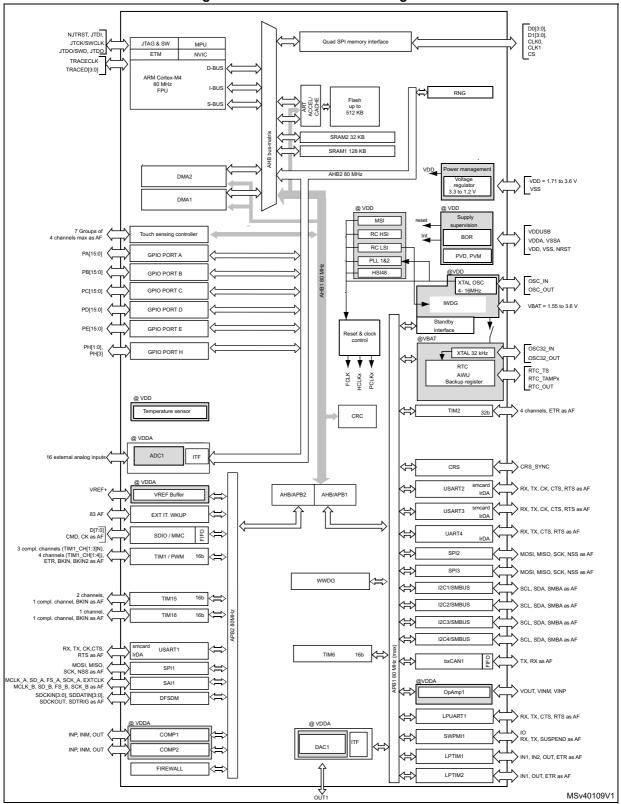

Figure 1. STM32L451xx block diagram

## 3.4 Embedded Flash memory

STM32L451xx devices feature up to 512 Kbyte of embedded Flash memory available for storing programs and data in single bank architecture. The Flash memory contains 256 pages of 2 Kbyte.

Flexible protections can be configured thanks to option bytes:

- Readout protection (RDP) to protect the whole memory. Three levels are available:

- Level 0: no readout protection

- Level 1: memory readout protection: the Flash memory cannot be read from or written to if either debug features are connected, boot in RAM or bootloader is selected

- Level 2: chip readout protection: debug features (Cortex-M4 JTAG and serial wire), boot in RAM and bootloader selection are disabled (JTAG fuse). This selection is irreversible.

| Area      | Protection<br>level | U    | ser executio | on                 | Debug, boot from RAM or boot<br>from system memory (loader) |       |                    |  |  |

|-----------|---------------------|------|--------------|--------------------|-------------------------------------------------------------|-------|--------------------|--|--|

|           | level               | Read | Write        | Erase              | Read                                                        | Write | Erase              |  |  |

| Main      | 1                   | Yes  | Yes          | Yes                | No                                                          | No    | No                 |  |  |

| memory    | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |  |

| System    | 1                   | Yes  | No           | No                 | Yes                                                         | No    | No                 |  |  |

| memory    | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |  |

| Option    | 1                   | Yes  | Yes          | Yes                | Yes                                                         | Yes   | Yes                |  |  |

| bytes     | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |  |

| Backup    | 1                   | Yes  | Yes          | N/A <sup>(1)</sup> | No                                                          | No    | N/A <sup>(1)</sup> |  |  |

| registers | 2                   | Yes  | Yes          | N/A                | N/A                                                         | N/A   | N/A                |  |  |

| SRAM2     | 1                   | Yes  | Yes          | Yes <sup>(1)</sup> | No                                                          | No    | No <sup>(1)</sup>  |  |  |

| SNAIVIZ   | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |  |

#### Table 3. Access status versus readout protection level and execution modes

1. Erased when RDP change from Level 1 to Level 0.

- Write protection (WRP): the protected area is protected against erasing and programming. Two areas can be selected, with 2-Kbyte granularity.

- Proprietary code readout protection (PCROP): a part of the flash memory can be

protected against read and write from third parties. The protected area is execute-only:

it can only be reached by the STM32 CPU, as an instruction code, while all other

accesses (DMA, debug and CPU data read, write and erase) are strictly prohibited.

The PCROP area granularity is 64-bit wide. An additional option bit (PCROP\_RDP)

allows to select if the PCROP area is erased or not when the RDP protection is

changed from Level 1 to Level 0.

## 3.9.3 Voltage regulator

Two embedded linear voltage regulators supply most of the digital circuitries: the main regulator (MR) and the low-power regulator (LPR).

- The MR is used in the Run and Sleep modes and in the Stop 0 mode.

- The LPR is used in Low-Power Run, Low-Power Sleep, Stop 1 and Stop 2 modes. It is also used to supply the 32 Kbyte SRAM2 in Standby with SRAM2 retention.

- Both regulators are in power-down in Standby and Shutdown modes: the regulator output is in high impedance, and the kernel circuitry is powered down thus inducing zero consumption.

The ultralow-power STM32L451xx supports dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the Main Regulator that supplies the logic ( $V_{CORF}$ ) can be adjusted according to the system's maximum operating frequency.

There are two power consumption ranges:

- Range 1 with the CPU running at up to 80 MHz.

- Range 2 with a maximum CPU frequency of 26 MHz. All peripheral clocks are also limited to 26 MHz.

The  $V_{CORE}$  can be supplied by the low-power regulator, the main regulator being switched off. The system is then in Low-power run mode.

Low-power run mode with the CPU running at up to 2 MHz. Peripherals with independent clock can be clocked by HSI16.

## 3.9.4 Low-power modes

The ultra-low-power STM32L451xx supports seven low-power modes to achieve the best compromise between low-power consumption, short startup time, available peripherals and available wakeup sources.

## 3.11 Clocks and startup

The clock controller (see *Figure 4*) distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source:** four different clock sources can be used to drive the master clock SYSCLK:

- 4-48 MHz high-speed external crystal or ceramic resonator (HSE), that can supply a PLL. The HSE can also be configured in bypass mode for an external clock.

- 16 MHz high-speed internal RC oscillator (HSI16), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 12 frequencies from 100 kHz to 48 MHz. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be automatically trimmed by hardware to reach better than ±0.25% accuracy. The MSI can supply a PLL.

- System PLL which can be fed by HSE, HSI16 or MSI, with a maximum frequency at 80 MHz.

- **RC48 with clock recovery system (HSI48)**: internal RC48 MHz clock source can be used to drive the SDMMC or the RNG peripherals. This clock can be output on the MCO.

- **Auxiliary clock source:** two ultralow-power clock sources that can be used to drive the real-time clock:

- 32.768 kHz low-speed external crystal (LSE), supporting four drive capability modes. The LSE can also be configured in bypass mode for an external clock.

- 32 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock accuracy is ±5% accuracy.

- **Peripheral clock sources:** Several peripherals (SDMMC, RNG, SAI, USARTs, I2Cs, LPTimers, ADC) have their own independent clock whatever the system clock. Two PLLs, each having three independent outputs allowing the highest flexibility, can generate independent clocks for the ADC, the SDMMC/RNG and the SAI.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 4 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- **Clock security system (CSS):** this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI16 and a software

## 4 Pinouts and pin description

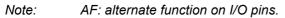

Figure 6. STM32L451Vx LQFP100 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

| Pinouts       |  |

|---------------|--|

| and pin       |  |

| 1 descriptior |  |

STM32L451xx

|        |      |         | Tabl                | e 17. Alternate                | function AF0 to           | o AF7 <sup>(1)</sup> (conti | nued)          |                      |                              |

|--------|------|---------|---------------------|--------------------------------|---------------------------|-----------------------------|----------------|----------------------|------------------------------|

|        |      | AF0     | AF1                 | AF2                            | AF3                       | AF4                         | AF5            | AF6                  | AF7                          |

| Po     | ort  | SYS_AF  | TIM1/TIM2<br>LPTIM1 | <b>I2C4/TIM1/</b><br>TIM2/TIM3 | I2C4/USART2/<br>CAN1/TIM1 | 2C1/ 2C2/<br> 2C3/ 2C4      | SPI1/SPI2/I2C4 | SPI3/DFSDM/<br>COMP1 | USART1/<br>USART2/<br>USART3 |

|        | PC0  | -       | LPTIM1_IN1          | I2C4_SCL                       | -                         | I2C3_SCL                    | -              | -                    | -                            |

|        | PC1  | TRACED0 | LPTIM1_OUT          | I2C4_SDA                       | -                         | I2C3_SDA                    | -              | -                    | -                            |

|        | PC2  | -       | LPTIM1_IN2          | -                              | -                         | -                           | SPI2_MISO      | DFSDM1_<br>CKOUT     | -                            |

|        | PC3  | -       | LPTIM1_ETR          | -                              | -                         | -                           | SPI2_MOSI      | -                    | -                            |

|        | PC4  | -       | -                   | -                              | -                         | -                           | -              | -                    | USART3_TX                    |

|        | PC5  | -       | -                   | -                              | -                         | -                           | -              | -                    | USART3_RX                    |

|        | PC6  | -       | TIM3                | TIM3_CH1                       | -                         | -                           | -              | DFSDM1_<br>CKIN3     | -                            |

| Port C | PC7  | -       | -                   | TIM3_CH2                       | -                         | -                           | -              | DFSDM1_<br>DATIN3    | -                            |

|        | PC8  | -       | -                   | TIM3_CH3                       | -                         | -                           | -              | -                    | -                            |

|        | PC9  | -       | -                   | TIM3_CH4                       | -                         | -                           | -              | -                    | -                            |

|        | PC10 | TRACED1 | -                   | -                              | -                         | -                           | -              | SPI3_SCK             | USART3_TX                    |

|        | PC11 | -       | -                   | -                              | -                         | -                           | -              | SPI3_MISO            | USART3_RX                    |

|        | PC12 | TRACED3 | -                   | -                              | -                         | -                           | -              | SPI3_MOSI            | USART3_CK                    |

|        | PC13 | -       | -                   | -                              | -                         | -                           | -              | -                    | -                            |

|        | PC14 | -       | -                   | -                              | -                         | -                           | -              | -                    | -                            |

|        | PC15 | -       | -                   | -                              | -                         | -                           | -              | -                    | -                            |

DS11910 Rev 4

72/201

5

# Table 19. STM32L451xx memory map and peripheral register boundary addresses<sup>(1)</sup> \_\_\_\_\_\_(continued)

| Bus  | Boundary address          | Size(bytes) | Peripheral |

|------|---------------------------|-------------|------------|

|      | 0x4000 2800 - 0x4000 2BFF | 1 KB        | RTC        |

|      | 0x4000 1400 - 0x4000 27FF | 5 KB        | Reserved   |

| APB1 | 0x4000 1000 - 0x4000 13FF | 1 KB        | TIM6       |

| AFDI | 0x4000 0800- 0x4000 0FFF  | 2 KB        | Reserved   |

|      | 0x4000 0400 - 0x4000 07FF | 1 KB        | TIM3       |

|      | 0x4000 0000 - 0x4000 03FF | 1 KB        | TIM2       |

1. The gray color is used for reserved boundary addresses.

|                                 |                                                      | Tabi            | e 37. Ci | unent | consun | iption i | i Stop t           | ,     |       |       |               |                     |      |

|---------------------------------|------------------------------------------------------|-----------------|----------|-------|--------|----------|--------------------|-------|-------|-------|---------------|---------------------|------|

| Symbol                          | Parameter                                            | Conditions      | ТҮР      |       |        |          | MAX <sup>(1)</sup> |       |       |       |               | Unit                |      |

| Symbol                          | Falameter                                            | V <sub>DD</sub> | 25 °C    | 55 °C | 85 °C  | 105 °C   | 125 °C             | 25 °C | 55 °C | 85 °C | 105 °C 125 °C | 125 °C              | Unit |

| I <sub>DD_ALL</sub><br>(Stop 0) | Supply<br>current in<br>Stop 0 mode,<br>RTC disabled | 1.8 V           | 125      | 150   | 240    | 390      | 645                | 145   | 190   | 350   | 600           | 1150                |      |

|                                 |                                                      | 2.4 V           | 125      | 150   | 240    | 390      | 645                | 150   | 195   | 355   | 605           | 1150                | μA   |

|                                 |                                                      | 3 V             | 125      | 150   | 245    | 395      | 650                | 155   | 195   | 360   | 610           | 1150                |      |

|                                 |                                                      | 3.6 V           | 125      | 155   | 245    | 400      | 655                | 155   | 200   | 365   | 615           | 1150 <sup>(2)</sup> |      |

## Table 37. Current consumption in Stop 0

1. Guaranteed by characterization results, unless otherwise specified.

2. Guaranteed by test in production.

**N**

| Symbol                                          | Parameter                                                    | Conditions                                                       |          |       | ТҮР   |       |        |        | MAX <sup>(1)</sup> |       |       |        |        | Ur    |

|-------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------|----------|-------|-------|-------|--------|--------|--------------------|-------|-------|--------|--------|-------|

| Symbol                                          | Farameter                                                    | -                                                                | $V_{DD}$ | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C              | 55 °C | 85 °C | 105 °C | 125 °C |       |

|                                                 |                                                              |                                                                  | 1.8 V    | 165   | 275   | 950   | 2600   | 6550   | -                  | -     | -     | -      | -      |       |

|                                                 | Supply current                                               | RTC clocked by LSE                                               | 2.4 V    | 235   | 370   | 1150  | 3100   | 7650   | -                  | -     | -     | -      | -      | 1     |

|                                                 | in Shutdown<br>mode<br>(backup<br>registers<br>retained) RTC | bypassed at 32768 Hz                                             | 3 V      | 325   | 485   | 1450  | 3750   | 9050   | -                  | -     | -     | -      | -      | 1     |

| I <sub>DD_ALL</sub><br>(Shutdown                |                                                              |                                                                  | 3.6 V    | 445   | 655   | 1900  | 4800   | 11500  | -                  | -     | -     | -      | -      | ] _ n |

| with RTC)                                       |                                                              | RTC clocked by LSE<br>quartz <sup>(2)</sup> in low drive<br>mode | 1.8 V    | 290   | 410   | 1050  | 2550   | 6700   | -                  | -     | -     | -      | -      | 1 ''  |

| ,                                               |                                                              |                                                                  | 2.4 V    | 375   | 515   | 1250  | 3050   | 7800   | -                  | -     | -     | -      | -      | 1     |

|                                                 | enabled                                                      |                                                                  | 3 V      | 480   | 645   | 1550  | 3700   | 8800   | -                  | -     | -     | -      | -      | 1     |

|                                                 |                                                              |                                                                  | 3.6 V    | 625   | 840   | 1950  | 4950   | 11500  | -                  | -     | -     | -      | -      | 1     |

| I <sub>DD_ALL</sub><br>wakeup from<br>Shutdown) | Supply current<br>during wakeup<br>from Shutdown<br>mode     | Wakeup clock is<br>MSI = 4 MHz.<br>See <sup>(3)</sup> .          | 3 V      | 1.00  | -     | -     | -      | -      | -                  | -     | -     | -      | -      | m     |

1. Guaranteed by characterization results, unless otherwise specified.

2. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

3. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in Table 42: Low-power mode wakeup timings.

| Symbol                         | Parameter      | Conditions   |                  |       | ТҮР   |       |        |        |       |       | MAX <sup>(1)</sup> |        |        | Unit |

|--------------------------------|----------------|--------------|------------------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|------|

| Cymbol                         | Falanetei      | -            | V <sub>BAT</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C |      |

|                                |                |              | 1.8 V            | 3.00  | -     | -     | -      | -      | -     | -     | -                  | -      | -      |      |

|                                |                | RTC disabled | 2.4 V            | 4.00  | -     | -     | -      | -      | -     | -     | -                  | -      | -      |      |

|                                |                |              | 3 V              | 5.00  | -     | -     | -      | -      | -     | -     | -                  | -      | -      |      |

| I <sub>DD VBAT</sub>           | Backup domain  |              | 3.6 V            | 11.0  | -     | -     | -      | -      | -     | -     | -                  | -      | -      | nA   |

| I <sub>DD_VBAT</sub><br>(VBAT) | supply current |              | 1.8 V            | 145   | 165   | 285   | 550    | -      | -     | -     | -                  | -      | -      | ПА   |

|                                |                |              | 2.4 V            | 205   | 235   | 370   | 670    | -      | -     | -     | -                  | -      | -      |      |

|                                |                |              | 3 V              | 285   | 315   | 470   | 820    | -      | -     | -     | -                  | -      | -      |      |

|                                |                |              | 3.6 V            | 375   | 430   | 715   | 1350   | -      | -     | -     | -                  | -      | -      |      |

1. Guaranteed by characterization results, unless otherwise specified.

DS11910 Rev 4

108/201

STM32L451xx

| Symbol               | Parameter                                        |         | Conditions                  | Тур    | Мах    | Unit |  |

|----------------------|--------------------------------------------------|---------|-----------------------------|--------|--------|------|--|

|                      |                                                  | Danga 1 | Wakeup clock MSI = 48 MHz   | 7.93   | 9.1    |      |  |

|                      | Wake up time from Stop 2                         | Range 1 | Wakeup clock HSI16 = 16 MHz | 7.32   | 8.5    |      |  |

|                      | mode to Run mode in                              |         | Wakeup clock MSI = 24 MHz   | 8.25   | 9.4    |      |  |

|                      | Flash                                            | Range 2 | Wakeup clock HSI16 = 16 MHz | 7.32   | 8.4    |      |  |

|                      |                                                  |         | Wakeup clock MSI = 4 MHz    | 11.43  | 13.3   |      |  |

| t <sub>WUSTOP2</sub> | Wake up time from Stop 2<br>mode to Run mode in  | Dense 1 | Wakeup clock MSI = 48 MHz   | 5.23   | 6      | μs   |  |

|                      |                                                  | Range 1 | Wakeup clock HSI16 = 16 MHz | 6.33   | 7.1    |      |  |

|                      |                                                  |         | Wakeup clock MSI = 24 MHz   | 5.78   | 6.5    |      |  |

|                      | SRAM1                                            | Range 2 | Wakeup clock HSI16 = 16 MHz | 6.33   | 7.1    |      |  |

|                      |                                                  |         | Wakeup clock MSI = 4 MHz 11 |        | 12.9   |      |  |

|                      | Wakeup time from Standby                         | Dense 1 | Wakeup clock MSI = 8 MHz    | 16.13  | 18.2   |      |  |

| twustby              | mode to Run mode                                 | Range 1 | Wakeup clock MSI = 4 MHz    | 24.06  | 26.6   | μs   |  |

| t <sub>WUSTBY</sub>  | Wakeup time from Standby                         | Range 1 | Wakeup clock MSI = 8 MHz    | 16.09  | 18.2   |      |  |

| SRAM2                | with CDAMO to Due mode                           |         | Wakeup clock MSI = 4 MHz    | 24     | 26.6   | μs   |  |

| t <sub>WUSHDN</sub>  | Wakeup time from<br>Shutdown mode to Run<br>mode | Range 1 | Wakeup clock MSI = 4 MHz    | 255.38 | 316.41 | μs   |  |

Table 42. Low-power mode wakeup timings<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

## Table 43. Regulator modes transition times<sup>(1)</sup>

| Symbol               | Parameter                                                                       | Conditions               | Тур | Max | Unit |

|----------------------|---------------------------------------------------------------------------------|--------------------------|-----|-----|------|

| t <sub>WULPRUN</sub> | Wakeup time from Low-power run mode to Run mode $^{\left( 2\right) }$           | Code run with MSI 2 MHz  | 5   | 7   |      |

| t <sub>VOST</sub>    | Regulator transition time from Range 2 to Range 1 or Range 1 to Range $2^{(3)}$ | Code run with MSI 24 MHz | 20  | 40  | μs   |

1. Guaranteed by characterization results.

2. Time until REGLPF flag is cleared in PWR\_SR2.

3. Time until VOSF flag is cleared in PWR\_SR2.

## Table 44. Wakeup time using USART/LPUART<sup>(1)</sup>

| Symbol                                        | Parameter                                                                                                           | Conditions                  | Тур | Max | Unit |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|-----|------|

|                                               | Wakeup time needed to calculate the                                                                                 | Stop 0 mode                 | -   | 1.7 |      |

| t <sub>WUUSART</sub><br>t <sub>WULPUART</sub> | maximum USART/LPUART baudrate<br>allowing to wakeup up from stop mode<br>when USART/LPUART clock source is<br>HSI16 | Stop 1 mode and Stop 2 mode | -   | 8.5 | μs   |

1. Guaranteed by design.

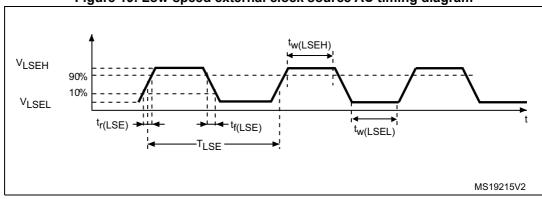

## Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in *Figure 19*.

| Symbol                                       | Parameter                             | Conditions | Min                    | Тур    | Max                    | Unit |

|----------------------------------------------|---------------------------------------|------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -          | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | -          | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage  | -          | $V_{SS}$               | -      | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | -          | 250                    | -      | -                      | ns   |

| Table 46. Low-speed external user cloc | k characteristics <sup>(1)</sup> |

|----------------------------------------|----------------------------------|

|----------------------------------------|----------------------------------|

1. Guaranteed by design.

## High-speed internal 48 MHz (HSI48) RC oscillator

| Symbol                                                         | Parameter                                                                  | Conditions                                                         | Min               | Тур                    | Мах                 | Unit |

|----------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------|------------------------|---------------------|------|

| f <sub>HSI48</sub>                                             | HSI48 Frequency                                                            | V <sub>DD</sub> =3.0V, T <sub>A</sub> =30°C                        | -                 | 48                     | -                   | MHz  |

| TRIM                                                           | HSI48 user trimming step                                                   | -                                                                  | -                 | 0.11 <sup>(2)</sup>    | 0.18 <sup>(2)</sup> | %    |

| USER TRIM<br>COVERAGE                                          | HSI48 user trimming coverage                                               | ±32 steps                                                          | ±3 <sup>(3)</sup> | ±3.5 <sup>(3)</sup>    | -                   | %    |

| DuCy(HSI48)                                                    | Duty Cycle                                                                 | -                                                                  | 45 <sup>(2)</sup> | -                      | 55 <sup>(2)</sup>   | %    |

| 100                                                            | Accuracy of the HSI48 oscillator                                           | V <sub>DD</sub> = 3.0 V to 3.6 V,<br>T <sub>A</sub> = -15 to 85 °C | -                 | -                      | ±3 <sup>(3)</sup>   | %    |

| ACC <sub>HSI48_REL</sub> over temperature (factory calibrated) |                                                                            | $V_{DD}$ = 1.65 V to 3.6 V,<br>T <sub>A</sub> = -40 to 125 °C      | -                 | -                      | ±4.5 <sup>(3)</sup> | - 70 |

|                                                                | HSI48 oscillator frequency drift                                           | V <sub>DD</sub> = 3 V to 3.6 V                                     | -                 | 0.025 <sup>(3)</sup>   | 0.05 <sup>(3)</sup> | %    |

| D <sub>VDD</sub> (HSI48)                                       | with V <sub>DD</sub>                                                       | V <sub>DD</sub> = 1.65 V to 3.6 V                                  | -                 | 0.05 <sup>(3)</sup>    | 0.1 <sup>(3)</sup>  | 70   |

| t <sub>su</sub> (HSI48)                                        | HSI48 oscillator start-up time                                             | -                                                                  | -                 | 2.5 <sup>(2)</sup>     | 6 <sup>(2)</sup>    | μs   |

| I <sub>DD</sub> (HSI48)                                        | HSI48 oscillator power<br>consumption                                      | -                                                                  | -                 | 340 <sup>(2)</sup>     | 380 <sup>(2)</sup>  | μA   |

| N <sub>T</sub> jitter                                          | Next transition jitter<br>Accumulated jitter on 28 cycles <sup>(4)</sup>   | -                                                                  | -                 | +/-0.15 <sup>(2)</sup> | -                   | ns   |

| P <sub>T</sub> jitter                                          | Paired transition jitter<br>Accumulated jitter on 56 cycles <sup>(4)</sup> | -                                                                  | -                 | +/-0.25 <sup>(2)</sup> | -                   | ns   |

## Table 51. HSI48 oscillator characteristics<sup>(1)</sup>

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 125°C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Jitter measurement are performed without clock source activated in parallel.

## 6.3.10 Flash memory characteristics

| Table 54. Flash memory characteristics |                                       |                    |               |       |      |

|----------------------------------------|---------------------------------------|--------------------|---------------|-------|------|

| Symbol                                 | Parameter                             | Conditions         | Тур           | Max   | Unit |

| t <sub>prog</sub>                      | 64-bit programming time               | -                  | 81.69         | 90.76 | μs   |

| +                                      | one row (32 double                    | normal programming | 2.61          | 2.90  |      |

| <sup>t</sup> prog_row                  | word) programming time                | fast programming   | 1.91          | 2.12  |      |

| +                                      | one page (2 Kbyte)                    | normal programming | 20.91         | 23.24 | ms   |

| <sup>l</sup> prog_page                 | programming time                      | fast programming   | 15.29         | 16.98 |      |

| t <sub>ERASE</sub>                     | Page (2 KB) erase time                | -                  | 22.02         | 24.47 |      |

| +                                      | one bank (512 Kbyte)                  | normal programming | 5.35          | 5.95  | s    |

| t <sub>prog_bank</sub>                 | programming time                      | fast programming   | 3.91          | 4.35  | 5    |

| t <sub>ME</sub>                        | Mass erase time<br>(one or two banks) | -                  | 22.13         | 24.59 | ms   |

|                                        | Average consumption                   | Write mode         | 3.4           | -     |      |

|                                        | from V <sub>DD</sub>                  | Erase mode         | 3.4           | -     | mA   |

| I <sub>DD</sub>                        | Maximum aurrant (naak)                | Write mode         | 7 (for 2 µs)  | -     | mA   |

|                                        | Maximum current (peak)                | Erase mode         | 7 (for 41 µs) | -     |      |

## Table 54. Flash memory characteristics<sup>(1)</sup>

1. Guaranteed by design.

| Symbol           | Parameter                                          | Conditions                                           | Min <sup>(1)</sup> | Unit    |

|------------------|----------------------------------------------------|------------------------------------------------------|--------------------|---------|

| N <sub>END</sub> | Endurance                                          | T <sub>A</sub> = -40 to +105 °C                      | 10                 | kcycles |

|                  |                                                    | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C    | 30                 |         |

|                  | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 15                                                   |                    |         |

| +                | t <sub>RET</sub> Data retention                    | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 125 °C   | 7                  | Years   |

| <b>'</b> RET     |                                                    | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C  | 30                 | Tears   |

|                  |                                                    | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 15                 |         |

|                  |                                                    | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 |         |

## Table 55. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

| Sym-<br>bol | Parameter               | (                                                                    | Conditions <sup>(4</sup> | )                        | Min  | Тур  | Max | Unit |

|-------------|-------------------------|----------------------------------------------------------------------|--------------------------|--------------------------|------|------|-----|------|

|             |                         |                                                                      | Single F                 |                          | -    | 5    | 5.4 |      |

| ET          | Total                   |                                                                      | ended                    | Slow channel (max speed) | -    | 4    | 5   |      |

|             | unadjusted<br>error     |                                                                      | Differential             | Fast channel (max speed) | -    | 4    | 5   |      |

|             |                         |                                                                      | Differential             | Slow channel (max speed) | -    | 3.5  | 4.5 |      |

|             |                         |                                                                      | olligic                  | Fast channel (max speed) | -    | 2    | 4   |      |

| EO          | Offset                  |                                                                      | ended                    | Slow channel (max speed) | -    | 2    | 4   |      |

| EO          | error                   |                                                                      | Differential             | Fast channel (max speed) | -    | 2    | 3.5 |      |

|             |                         |                                                                      | Differential             | Slow channel (max speed) | -    | 2    | 3.5 |      |

|             |                         |                                                                      | Single                   | Fast channel (max speed) | -    | 4    | 4.5 |      |

| EG          | Gain error              |                                                                      | ended                    | Slow channel (max speed) | -    | 4    | 4.5 |      |

| EG          | Gainenor                |                                                                      | Differential             | Fast channel (max speed) | -    | 3    | 4   | LSB  |

|             |                         | Differential                                                         | Slow channel (max speed) | -                        | 3    | 4    |     |      |

|             |                         | rential<br>rity<br>ADC clock frequency ≤ Differential<br>Fast channe | Single                   | Fast channel (max speed) | -    | 1    | 1.5 |      |

| ED          | Differential            |                                                                      | Slow channel (max speed) | -                        | 1    | 1.5  |     |      |

| ED          | ED linearity<br>error   |                                                                      | Differential             | Fast channel (max speed) | -    | 1    | 1.2 | 1    |

|             |                         | 26 MHz,<br>1.65 V ≤ V <sub>DDA</sub> = VREF+ ≤                       | Differential             | Slow channel (max speed) | -    | 1    | 1.2 |      |

|             |                         | 3.6 V,                                                               | Single                   | Fast channel (max speed) | -    | 2.5  | 3   |      |

| EL          | Integral                | Voltage scaling Range 2                                              | ended                    | Slow channel (max speed) | -    | 2.5  | 3   |      |

| EL          | linearity<br>error      |                                                                      | Differential             | Fast channel (max speed) | -    | 2    | 2.5 |      |

|             |                         |                                                                      | Differential             | Slow channel (max speed) | -    | 2    | 2.5 |      |

|             |                         |                                                                      | Single                   | Fast channel (max speed) | 10.2 | 10.5 | -   |      |

| ENOB        | Effective number of     |                                                                      | ended                    | Slow channel (max speed) | 10.2 | 10.5 | -   | bits |

| ENOD        | bits                    |                                                                      | Differential             | Fast channel (max speed) | 10.6 | 10.7 | -   | DILS |

|             |                         |                                                                      | Differential             | Slow channel (max speed) | 10.6 | 10.7 | -   |      |

|             | Signal to               |                                                                      | Single                   | Fast channel (max speed) | 63   | 65   | -   |      |

|             | Signal-to-<br>noise and |                                                                      | ended                    | Slow channel (max speed) | 63   | 65   | -   |      |

| distortion  |                         | Differential                                                         | Fast channel (max speed) | 65                       | 66   | -    |     |      |

|             | ratio                   |                                                                      | Differential             | Slow channel (max speed) | 65   | 66   | -   | d٦   |

|             |                         |                                                                      | Single                   | Fast channel (max speed) | 64   | 65   | -   | dB   |

| <b>CNID</b> | Signal-to-              |                                                                      | ended                    | Slow channel (max speed) | 64   | 65   | -   |      |

| SNR         | noise ratio             |                                                                      | Differential             | Fast channel (max speed) | 66   | 67   | -   |      |

|             |                         |                                                                      | Differential             | Slow channel (max speed) | 66   | 67   | -   |      |

| Table 72. ADC accuracy | v - limited test conditio | ns 4 <sup>(1)(2)(3)</sup> |

|------------------------|---------------------------|---------------------------|

| Table 12. ADC accuracy | y - miniteu test conultio | 113 4                     |

|             | Table 72. Abc accuracy - initied test conditions 4. A A (continued) |                                                |                           |                          |     |     |     |      |

|-------------|---------------------------------------------------------------------|------------------------------------------------|---------------------------|--------------------------|-----|-----|-----|------|

| Sym-<br>bol | Parameter                                                           | C                                              | Conditions <sup>(4)</sup> |                          |     | Тур | Max | Unit |

|             |                                                                     | ADC clock frequency ≤                          | Single                    | Fast channel (max speed) | -   | -71 | -69 |      |

| THD         | Total<br>harmonic                                                   | 26 MHz,<br>1.65 V ≤ V <sub>DDA</sub> = VREF+ ≤ | ended                     | Slow channel (max speed) | -   | -71 | -69 | dB   |

|             | distortion                                                          | 36V                                            | Differential              | Fast channel (max speed) | -   | -73 | -72 | uВ   |

|             | Voltage scaling Range 2                                             | Dillerential                                   | Slow channel (max speed)  | -                        | -73 | -72 |     |      |

Table 72. ADC accuracy - limited test conditions  $4^{(1)(2)(3)}$  (continued)

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when  $V_{DDA} < 2.4 \text{ V}$  (BOOSTEN = 1 in the SYSCFG\_CFGR1 when  $V_{DDA} < 2.4 \text{ V}$ ). It is disable when  $V_{DDA} \ge 2.4 \text{ V}$ . No oversampling.

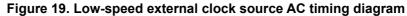

#### Figure 28. ADC accuracy characteristics

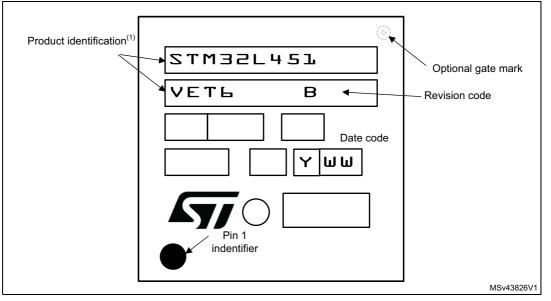

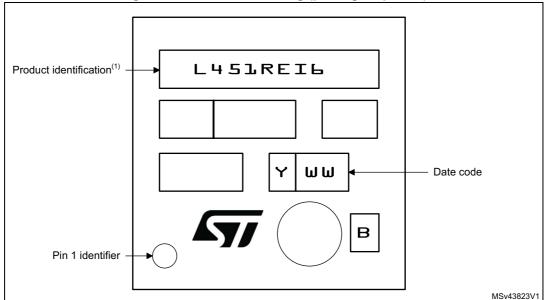

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

1. Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

#### Table 96. UFBGA64 recommended PCB design rules (0.5 mm pitch BGA) (continued)

| Dimension         | Recommended values            |

|-------------------|-------------------------------|

| Stencil thickness | Between 0.100 mm and 0.125 mm |

| Pad trace width   | 0.100 mm                      |

## Device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 51. UFBGA64 marking (package top view)

Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

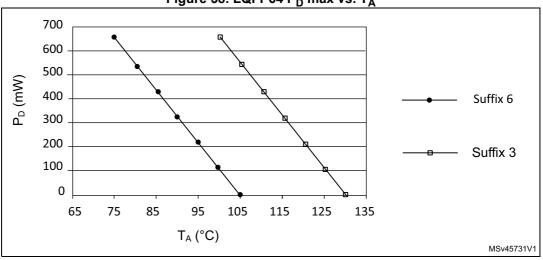

In this case, parts must be ordered at least with the temperature range suffix 3 (see *Section 8: Ordering information*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to *Figure 58* to select the required temperature range (suffix 6 or 3) according to your ambient temperature or power requirements.

| Date        | Revision         | Changes                                                                                                                                                                                   |

|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-May-2018 | 4<br>(continued) | Added Section 6.3.16: Extended interrupt and event<br>controller input (EXTI) characteristics.<br>Updated Table 61: I/O static characteristics.<br>Updated Table 73: DAC characteristics. |

## Table 102. Document revision history (continued)