# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 80MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                      |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 160K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l451ret6      |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

interrupt is generated if enabled. LSE failure can also be detected and generated an interrupt.

- Clock-out capability:

- MCO: microcontroller clock output: it outputs one of the internal clocks for external use by the application. Low frequency clocks (LSI, LSE) are available down to Stop 1 low power state.

- LSCO: low speed clock output: it outputs LSI or LSE in all low-power modes down to Standby mode. LSE can also be output on LSCO in Shutdown mode. LSCO is not available in VBAT mode.

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 80 MHz.

This digital interface supports the following features:

- Up to two DAC output channels

- 8-bit or 12-bit output mode

- Buffer offset calibration (factory and user trimming)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

- Sample and hold low-power mode, with internal or external capacitor

The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

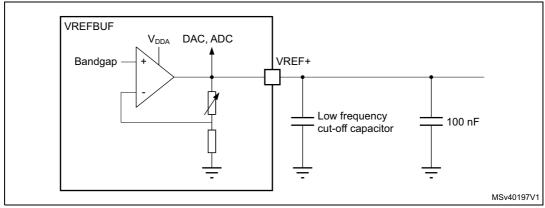

## 3.17 Voltage reference buffer (VREFBUF)

The STM32L451xx devices embed an voltage reference buffer which can be used as voltage reference for ADCs, DAC and also as voltage reference for external components through the VREF+ pin.

The internal voltage reference buffer supports two voltages:

- 2.048 V

- 2.5 V

An external voltage reference can be provided through the VREF+ pin when the internal voltage reference buffer is off.

The VREF+ pin is double-bonded with VDDA on some packages. In these packages the internal voltage reference buffer is not available.

Figure 5. Voltage reference buffer

|                 |         |        |         |         | - 1      |                                       |          | 4318/         | r hi  | in definitions (continued) Pin functions                                                     |                                                             |  |  |

|-----------------|---------|--------|---------|---------|----------|---------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

|                 | F       | Pin l  | Numl    | ber     | 1        | fter                                  |          |               |       | Pin functions                                                                                |                                                             |  |  |

| <b>UFQFPN48</b> | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                          | Additional functions                                        |  |  |

| -               | D5      | 9      | E2      | 16      | J2       | PC1                                   | I/O      | FT_fa         | -     | TRACED0, LPTIM1_OUT,<br>I2C4_SDA, I2C3_SDA,<br>LPUART1_TX, EVENTOUT                          | ADC1_IN2                                                    |  |  |

| -               | D6      | 10     | F2      | 17      | J3       | PC2                                   | I/O      | FT_a          | -     | LPTIM1_IN2, SPI2_MISO,<br>DFSDM1_CKOUT,<br>EVENTOUT                                          | ADC1_IN3                                                    |  |  |

| -               | E7      | 11     | G1      | 18      | K2       | PC3                                   | I/O      | FT_a          | -     | LPTIM1_ETR, SPI2_MOSI,<br>SAI1_SD_A, LPTIM2_ETR,<br>EVENTOUT                                 | ADC1_IN4                                                    |  |  |

| -               | -       | -      | -       | 19      | J1       | VSSA                                  | S        | -             | -     | -                                                                                            | -                                                           |  |  |

| -               | -       | -      | -       | 20      | K1       | VREF-                                 | S        | -             | -     | -                                                                                            | -                                                           |  |  |

| 8               | G8      | 12     | F1      | -       | -        | VSSA/<br>VREF-                        | S        | -             | -     | -                                                                                            | -                                                           |  |  |

| -               | -       | -      | -       | 21      | L1       | VREF+                                 | S        | -             | -     | -                                                                                            | VREFBUF_OUT                                                 |  |  |

| -               | -       | -      | -       | 22      | M1       | VDDA                                  | S        | -             | -     | -                                                                                            | -                                                           |  |  |

| 9               | F7      | 13     | H1      | -       | -        | VDDA/<br>VREF+                        | S        | -             | -     | -                                                                                            | -                                                           |  |  |

| 10              | H8      | 14     | G2      | 23      | L2       | PA0                                   | I/O      | FT_a          | -     | TIM2_CH1, USART2_CTS,<br>UART4_TX, COMP1_OUT,<br>SAI1_EXTCLK, TIM2_ETR,<br>EVENTOUT          | OPAMP1_VINP,<br>COMP1_INM,<br>ADC1_IN5, RTC_TAMP2,<br>WKUP1 |  |  |

| 11              | E6      | 15     | H2      | 24      | M2       | PA1                                   | I/O      | FT_a          | -     | TIM2_CH2, I2C1_SMBA,<br>SPI1_SCK,<br>USART2_RTS_DE,<br>UART4_RX, TIM15_CH1N,<br>EVENTOUT     | OPAMP1_VINM,<br>COMP1_INP, ADC1_IN6                         |  |  |

| 12              | G7      | 16     | F3      | 25      | K3       | PA2                                   | I/O      | FT_a          | -     | TIM2_CH3, USART2_TX,<br>LPUART1_TX,<br>QUADSPI_BK1_NCS,<br>COMP2_OUT, TIM15_CH1,<br>EVENTOUT | COMP2_INM,<br>ADC1_IN7,<br>WKUP4,LSCO                       |  |  |

| 13              | F6      | 17     | G3      | 26      | L3       | PA3                                   | I/O      | TT_a          | -     | TIM2_CH4, USART2_RX,<br>LPUART1_RX,<br>QUADSPI_CLK,<br>SAI1_MCLK_A,<br>TIM15_CH2, EVENTOUT   | OPAMP1_VOUT,<br>COMP2_INP, ADC1_IN8                         |  |  |

| -               | -       | 18     | C2      | 27      | E3       | VSS                                   | S        | -             | -     | -                                                                                            | -                                                           |  |  |

| -               | H7      | 19     | D2      | 28      | H3       | VDD                                   | S        | -             | -     | -                                                                                            | -                                                           |  |  |

| Table 16. STM32L451xx pin definitions (continued) |

|---------------------------------------------------|

|---------------------------------------------------|

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

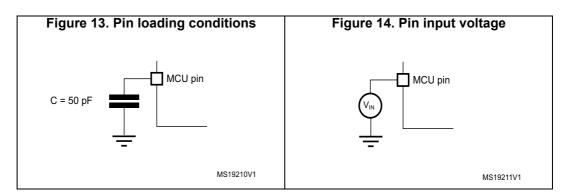

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 13*.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 14.

4. To sustain a voltage higher than 4 V the internal pull-up/pull-down resistors must be disabled.

5. Include VREF- pin.

| Symbol                               | Ratings                                                                           | Max                  | Unit |

|--------------------------------------|-----------------------------------------------------------------------------------|----------------------|------|

| $\Sigma IV_{DD}$                     | Total current into sum of all V <sub>DD</sub> power lines (source) <sup>(1)</sup> | 140                  |      |

| $\Sigma IV_{SS}$                     | Total current out of sum of all $V_{SS}$ ground lines (sink) <sup>(1)</sup>       | 140                  |      |

| IV <sub>DD(PIN)</sub>                | Maximum current into each V <sub>DD</sub> power pin (source) <sup>(1)</sup>       | 100                  |      |

| IV <sub>SS(PIN)</sub>                | Maximum current out of each V <sub>SS</sub> ground pin (sink) <sup>(1)</sup>      | 100                  |      |

| I <sub>IO(PIN)</sub>                 | Output current sunk by any I/O and control pin except FT_f                        | 20                   |      |

|                                      | Output current sunk by any FT_f pin                                               | 20                   |      |

|                                      | Output current sourced by any I/O and control pin                                 | 20                   | mA   |

| ΣI                                   | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>      | 100                  |      |

| $\Sigma I_{IO(PIN)}$                 | Total output current sourced by sum of all I/Os and control $pins^{(2)}$          | 100                  |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on FT_xxx, TT_xx, RST and B pins, except PA4, PA5                | -5/+0 <sup>(4)</sup> |      |

| - \ /                                | Injected current on PA4, PA5                                                      | -5/0                 | ]    |

| ∑II <sub>INJ(PIN)</sub> I            | Total injected current (sum of all I/Os and control pins) <sup>(5)</sup>          | 25                   | 1    |

#### Table 21. Current characteristics

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>BAT</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supplies, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

3. Positive injection (when  $V_{IN} > V_{DDIOx}$ ) is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

A negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer also to *Table 20: Voltage characteristics* for the maximum allowed input voltage values.

5. When several inputs are submitted to a current injection, the maximum  $\sum |I_{INJ(PIN)}|$  is the absolute sum of the negative injected currents (instantaneous values).

#### Table 22. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

| Symbol               | Parameter                                                          |                            | Тур                         | Max   | Unit |    |

|----------------------|--------------------------------------------------------------------|----------------------------|-----------------------------|-------|------|----|

|                      |                                                                    | Range 1                    | Wakeup clock MSI = 48 MHz   | 3.34  | 4.3  |    |

|                      | Wake up time from Stop 0                                           | Range                      | Wakeup clock HSI16 = 16 MHz | 3.7   | 6.5  |    |

|                      | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 3.8   | 7.1  |    |

|                      | Flash                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 3.7   | 6.5  |    |

| +                    |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 9.3   | 7.1  |    |

| twustop0             |                                                                    | Range 1                    | Wakeup clock MSI = 48 MHz   | 1.85  | 2.7  | μs |

|                      | Wake up time from Stop 0                                           | Range                      | Wakeup clock HSI16 = 16 MHz | 2.68  | 3    |    |

|                      | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 2.47  | 3.4  |    |

|                      | SRAM1                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 2.68  | 3    |    |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 9.67  | 12.5 |    |

|                      |                                                                    | Range 1                    | Wakeup clock MSI = 48 MHz   | 6.75  | 7.6  | μs |

|                      | Wake up time from Stop 1<br>mode to Run in Flash                   |                            | Wakeup clock HSI16 = 16 MHz | 7.14  | 8    |    |

|                      |                                                                    | Range 2                    | Wakeup clock MSI = 24 MHz   | 7     | 7.82 |    |

|                      |                                                                    |                            | Wakeup clock HSI16 = 16 MHz | 7.14  | 7.9  |    |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 10.44 | 11.9 |    |

|                      |                                                                    | Range 1                    | Wakeup clock MSI = 48 MHz   | 5.21  | 5.9  |    |

|                      | Wake up time from Stop 1                                           | Range                      | Wakeup clock HSI16 = 16 MHz | 6.23  | 6.9  |    |

| t <sub>WUSTOP1</sub> | mode to Run mode in                                                | Range 2                    | Wakeup clock MSI = 24 MHz   | 5.73  | 6.4  |    |

|                      | SRAM1                                                              |                            | Wakeup clock HSI16 = 16 MHz | 6.23  | 6.9  |    |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 10.9  | 12.3 |    |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in Flash | Regulator in<br>low-power  | Wakeup daak MSL = 2 ML      | 16.05 | 19.2 |    |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in SRAM1 | mode (LPR=1<br>in PWR_CR1) | Wakeup clock MSI = 2 MHz    | 17.06 | 20.3 |    |

Table 42. Low-power mode wakeup timings<sup>(1)</sup> (continued)

| Symbol              | Parameter                                                |         | Conditions                  | Тур    | Мах    | Unit |  |

|---------------------|----------------------------------------------------------|---------|-----------------------------|--------|--------|------|--|

|                     |                                                          | Danga 1 | Wakeup clock MSI = 48 MHz   | 7.93   | 9.1    |      |  |

|                     | Wake up time from Stop 2                                 | Range 1 | Wakeup clock HSI16 = 16 MHz | 7.32   | 8.5    |      |  |

|                     | mode to Run mode in                                      |         | Wakeup clock MSI = 24 MHz   | 8.25   | 9.4    |      |  |

|                     | Flash                                                    | Range 2 | Wakeup clock HSI16 = 16 MHz | 7.32   | 8.4    |      |  |

|                     |                                                          |         | Wakeup clock MSI = 4 MHz    | 11.43  | 13.3   |      |  |

| twustop2            |                                                          | Dense 1 | Wakeup clock MSI = 48 MHz   | 5.23   | 6      | μs   |  |

|                     | Wake up time from Stop 2<br>mode to Run mode in<br>SRAM1 | Range 1 | Wakeup clock HSI16 = 16 MHz | 6.33   | 7.1    |      |  |

|                     |                                                          | Range 2 | Wakeup clock MSI = 24 MHz   | 5.78   | 6.5    |      |  |

|                     |                                                          |         | Wakeup clock HSI16 = 16 MHz | 6.33   | 7.1    |      |  |

|                     |                                                          |         | Wakeup clock MSI = 4 MHz    | 11.37  | 12.9   |      |  |

|                     | Wakeup time from Standby                                 | Dense 1 | Wakeup clock MSI = 8 MHz    | 16.13  | 18.2   | μs   |  |

| twustby             | mode to Run mode                                         | Range 1 | Wakeup clock MSI = 4 MHz    | 24.06  | 26.6   |      |  |

| t <sub>WUSTBY</sub> | Wakeup time from Standby                                 | Dense 1 | Wakeup clock MSI = 8 MHz    | 16.09  | 18.2   |      |  |

| SRAM2               | with SRAM2 to Run mode                                   | Range 1 | Wakeup clock MSI = 4 MHz    | 24     | 26.6   | - μs |  |

| t <sub>WUSHDN</sub> | Wakeup time from<br>Shutdown mode to Run<br>mode         | Range 1 | Wakeup clock MSI = 4 MHz    | 255.38 | 316.41 | μs   |  |

Table 42. Low-power mode wakeup timings<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

#### Table 43. Regulator modes transition times<sup>(1)</sup>

| Symbol               | Parameter                                                                       | Conditions               | Тур | Max | Unit |

|----------------------|---------------------------------------------------------------------------------|--------------------------|-----|-----|------|

| t <sub>WULPRUN</sub> | Wakeup time from Low-power run mode to Run mode $^{\left( 2\right) }$           | Code run with MSI 2 MHz  | 5   | 7   |      |

| t <sub>VOST</sub>    | Regulator transition time from Range 2 to Range 1 or Range 1 to Range $2^{(3)}$ | Code run with MSI 24 MHz | 20  | 40  | μs   |

1. Guaranteed by characterization results.

2. Time until REGLPF flag is cleared in PWR\_SR2.

3. Time until VOSF flag is cleared in PWR\_SR2.

## Table 44. Wakeup time using USART/LPUART<sup>(1)</sup>

| Symbol                                        | Parameter                                                             | Conditions                  | Тур | Max | Unit |

|-----------------------------------------------|-----------------------------------------------------------------------|-----------------------------|-----|-----|------|

|                                               | maximum USART/LPUART baudrate<br>allowing to wakeup up from stop mode | Stop 0 mode                 | -   | 1.7 |      |

| t <sub>WUUSART</sub><br>t <sub>WULPUART</sub> |                                                                       | Stop 1 mode and Stop 2 mode | -   | 8.5 | μs   |

1. Guaranteed by design.

- 1. Guaranteed by design.

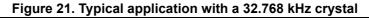

- 2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

- t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

## High-speed internal 48 MHz (HSI48) RC oscillator

|                          |                                                                            |                                                                      |                   |                        |                     | 1    |  |

|--------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------|------------------------|---------------------|------|--|

| Symbol                   | Parameter                                                                  | Conditions                                                           | Min               | Тур                    | Мах                 | Unit |  |

| f <sub>HSI48</sub>       | HSI48 Frequency                                                            | V <sub>DD</sub> =3.0V, T <sub>A</sub> =30°C                          | -                 | 48                     | -                   | MHz  |  |

| TRIM                     | HSI48 user trimming step                                                   | -                                                                    | -                 | 0.11 <sup>(2)</sup>    | 0.18 <sup>(2)</sup> | %    |  |

| USER TRIM<br>COVERAGE    | HSI48 user trimming coverage                                               | ±32 steps                                                            | ±3 <sup>(3)</sup> | ±3.5 <sup>(3)</sup>    | -                   | %    |  |

| DuCy(HSI48)              | Duty Cycle                                                                 | -                                                                    | 45 <sup>(2)</sup> | -                      | 55 <sup>(2)</sup>   | %    |  |

| ACC                      | Accuracy of the HSI48 oscillator                                           | V <sub>DD</sub> = 3.0 V to 3.6 V,<br>T <sub>A</sub> = -15 to 85 °C   | -                 | -                      | ±3 <sup>(3)</sup>   | %    |  |

| ACC <sub>HSI48_REL</sub> | over temperature (factory calibrated)                                      | V <sub>DD</sub> = 1.65 V to 3.6 V,<br>T <sub>A</sub> = -40 to 125 °C | -                 | -                      | ±4.5 <sup>(3)</sup> | 70   |  |

|                          | HSI48 oscillator frequency drift                                           | V <sub>DD</sub> = 3 V to 3.6 V                                       | -                 | 0.025 <sup>(3)</sup>   | 0.05 <sup>(3)</sup> | - %  |  |

| D <sub>VDD</sub> (HSI48) | with V <sub>DD</sub>                                                       | V <sub>DD</sub> = 1.65 V to 3.6 V                                    | -                 | 0.05 <sup>(3)</sup>    | 0.1 <sup>(3)</sup>  |      |  |

| t <sub>su</sub> (HSI48)  | HSI48 oscillator start-up time                                             | -                                                                    | -                 | 2.5 <sup>(2)</sup>     | 6 <sup>(2)</sup>    | μs   |  |

| I <sub>DD</sub> (HSI48)  | HSI48 oscillator power<br>consumption                                      | -                                                                    | -                 | 340 <sup>(2)</sup>     | 380 <sup>(2)</sup>  | μA   |  |

| N <sub>T</sub> jitter    | Next transition jitter<br>Accumulated jitter on 28 cycles <sup>(4)</sup>   | -                                                                    | -                 | +/-0.15 <sup>(2)</sup> | -                   | ns   |  |

| P <sub>T</sub> jitter    | Paired transition jitter<br>Accumulated jitter on 56 cycles <sup>(4)</sup> | -                                                                    | -                 | +/-0.25 <sup>(2)</sup> | -                   | ns   |  |

## Table 51. HSI48 oscillator characteristics<sup>(1)</sup>

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 125°C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Jitter measurement are performed without clock source activated in parallel.

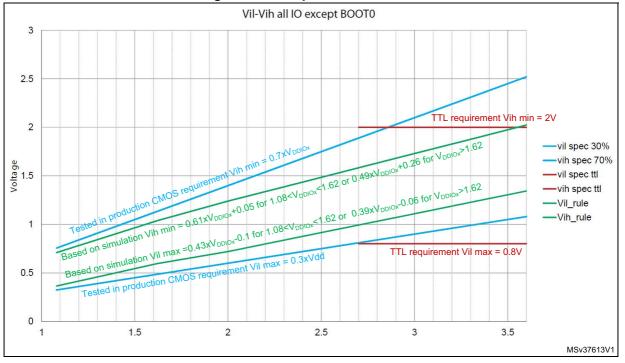

- 1. Refer to Figure 25: I/O input characteristics.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. All FT\_xx IO except PA11, PA12 and PC3 I/O.

- 5. Max(V<sub>DDXXX</sub>) is the maximum value of all the I/O supplies.

- 6. To sustain a voltage higher than Min( $V_{DD}$ ,  $V_{DDA}$ ) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- 7. This value represents the pad leakage of the IO itself. The total product pad leakage is provided by this formula:  $I_{Total\_Ileak\_max} = 10 \ \mu A + [number of IOs where V_{IN} is applied on the pad] \times I_{Ikg}(Max).$

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 25* for standard I/Os, and in *Figure 25* for 5 V tolerant I/Os.

Figure 25. I/O input characteristics

#### Output driving current

The GPIOs (general purpose input/outputs) can sink or source up to ±8 mA, and sink or source up to ± 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

| Sym-<br>bol | Parameter                          | (                       | Conditions <sup>(4</sup> | )                        | Min  | Тур  | Max | Unit                           |

|-------------|------------------------------------|-------------------------|--------------------------|--------------------------|------|------|-----|--------------------------------|

|             |                                    |                         | Single                   | Fast channel (max speed) | -    | 5    | 5.4 |                                |

| ET          | Total                              |                         | ended                    | Slow channel (max speed) | -    | 4    | 5   |                                |

|             | unadjusted<br>error                |                         | Differential             | Fast channel (max speed) | -    | 4    | 5   |                                |

|             |                                    |                         | Differential             | Slow channel (max speed) | -    | 3.5  | 4.5 |                                |

|             |                                    |                         | Single                   | Fast channel (max speed) | -    | 2    | 4   |                                |

| EO          | Offset                             |                         | ended                    | Slow channel (max speed) | -    | 2    | 4   |                                |

| EU          | error                              |                         | Differential             | Fast channel (max speed) | -    | 2    | 3.5 |                                |

|             |                                    |                         | Differential             | Slow channel (max speed) | -    | 2    | 3.5 |                                |

|             |                                    |                         | Single                   | Fast channel (max speed) | -    | 4    | 4.5 |                                |

| EG          | Gain error                         |                         | ended                    | Slow channel (max speed) | -    | 4    | 4.5 |                                |

| EG          | Gainenoi                           | fferential<br>earity    | Differential             | Fast channel (max speed) | -    | 3    | 4   | - LSB<br>-<br>-<br>-<br>-<br>- |

|             |                                    |                         | Differential             | Slow channel (max speed) | -    | 3    | 4   |                                |

|             | Differential<br>linearity<br>error |                         | Single<br>ended          | Fast channel (max speed) | -    | 1    | 1.5 |                                |

| ED          |                                    |                         |                          | Slow channel (max speed) | -    | 1    | 1.5 |                                |

| ED          |                                    |                         | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |                                |

|             |                                    |                         |                          | Slow channel (max speed) | -    | 1    | 1.2 |                                |

|             |                                    | 3.6 V,                  | Single<br>ended          | Fast channel (max speed) | -    | 2.5  | 3   |                                |

| EL          | Integral                           | Voltage scaling Range 2 |                          | Slow channel (max speed) | -    | 2.5  | 3   |                                |

| EL          | linearity<br>error                 | -                       | Differential             | Fast channel (max speed) | -    | 2    | 2.5 |                                |

|             |                                    |                         |                          | Slow channel (max speed) | -    | 2    | 2.5 |                                |

|             |                                    |                         | Single                   | Fast channel (max speed) | 10.2 | 10.5 | -   |                                |

| ENOB        | Effective                          |                         | ended                    | Slow channel (max speed) | 10.2 | 10.5 | -   | bite                           |

| ENOD        | bits                               | umber of<br>its         | Differential             | Fast channel (max speed) | 10.6 | 10.7 | -   | - bits                         |

|             |                                    |                         | Differential             | Slow channel (max speed) | 10.6 | 10.7 | -   |                                |

|             | Signal-to-                         |                         | Single                   | Fast channel (max speed) | 63   | 65   | -   |                                |

| SINAD       | noise and                          |                         | ended                    | Slow channel (max speed) | 63   | 65   | -   |                                |

| SINAD       | distortion<br>ratio                |                         | Differential             | Fast channel (max speed) | 65   | 66   | -   | 1                              |

|             | 1410                               |                         |                          | Slow channel (max speed) | 65   | 66   | -   | dB                             |

|             |                                    |                         | Single                   | Fast channel (max speed) | 64   | 65   | -   | чD                             |

| SNR         | Signal-to-                         |                         | ended                    | Slow channel (max speed) | 64   | 65   | -   | 1                              |

| SINK        | noise ratio                        |                         | Differential             | Fast channel (max speed) | 66   | 67   | -   |                                |

|             |                                    |                         | Differential             | Slow channel (max speed) | 66   | 67   | -   |                                |

| Table 72. ADC accuracy | v - limited test conditio | ns 4 <sup>(1)(2)(3)</sup> |

|------------------------|---------------------------|---------------------------|

| Table 12. ADC accuracy | y - miniteu test conultio | 13 4                      |

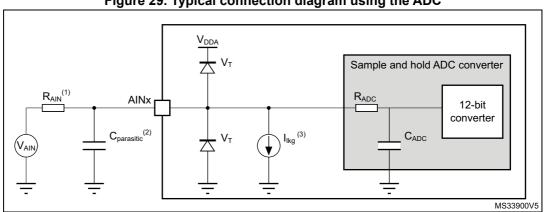

Figure 29. Typical connection diagram using the ADC

- Refer to Table 67: ADC characteristics for the values of  $\mathsf{R}_{AIN}$  and  $\mathsf{C}_{ADC}.$ 1.

- $C_{\text{parasitic}}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (refer to *Table 61: I/O static characteristics* for the value of the pad capacitance). A high  $C_{\text{parasitic}}$  value will downgrade conversion accuracy. To remedy this,  $f_{\text{ADC}}$  should be reduced. 2.

- 3. Refer to Table 61: I/O static characteristics for the values of Ilkg.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 15: Power supply* scheme. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

# 6.3.20 Voltage reference buffer characteristics

| Table 75. VREFBUF characteristics <sup>(1)</sup> |                                                                                                 |                                   |                            |                          |                                         |                                       |         |  |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|--------------------------|-----------------------------------------|---------------------------------------|---------|--|--|

| Symbol                                           | Parameter                                                                                       | Conditio                          | ons                        | Min                      | Тур                                     | Мах                                   | Unit    |  |  |

|                                                  |                                                                                                 |                                   | V <sub>RS</sub> = 0        | 2.4                      | -                                       | 3.6                                   |         |  |  |

|                                                  | Analog supply                                                                                   | Normal mode                       | V <sub>RS</sub> = 1        | 2.8                      | -                                       | 3.6                                   |         |  |  |

| V <sub>DDA</sub>                                 | voltage                                                                                         | Degraded mode <sup>(2)</sup>      | V <sub>RS</sub> = 0        | 1.65                     | -                                       | 2.4                                   | 1       |  |  |

|                                                  |                                                                                                 |                                   | V <sub>RS</sub> = 1        | 1.65                     | -                                       | 2.8                                   | V       |  |  |

|                                                  | Voltage                                                                                         | Normal mode                       | V <sub>RS</sub> = 0        | 2.046 <sup>(3)</sup>     | 2.048                                   | 2.049 <sup>(3)</sup>                  | V       |  |  |

| V <sub>REFBUF</sub> _                            |                                                                                                 |                                   | V <sub>RS</sub> = 1        | 2.498 <sup>(3)</sup>     | 2.5                                     | 2.502 <sup>(3)</sup>                  |         |  |  |

| OUT                                              | reference<br>output                                                                             | Degraded mode <sup>(2)</sup>      | V <sub>RS</sub> = 0        | V <sub>DDA</sub> -150 mV | -                                       | V <sub>DDA</sub>                      |         |  |  |

|                                                  |                                                                                                 |                                   | V <sub>RS</sub> = 1        | V <sub>DDA</sub> -150 mV | -                                       | V <sub>DDA</sub>                      |         |  |  |

| TRIM                                             | Trim step resolution                                                                            | -                                 | -                          | -                        | ±0.05                                   | ±0.1                                  | %       |  |  |

| CL                                               | Load capacitor                                                                                  | -                                 | -                          | 0.5                      | 1                                       | 1.5                                   | μF      |  |  |

| esr                                              | Equivalent<br>Serial Resistor<br>of Cload                                                       | -                                 | -                          | -                        | -                                       | 2                                     | Ω       |  |  |

| I <sub>load</sub>                                | Static load current                                                                             | -                                 | -                          | -                        | -                                       | 4                                     | mA      |  |  |

| I                                                | Line regulation                                                                                 | 2.8 V ≤ V <sub>DDA</sub> ≤ 3.6 V  | I <sub>load</sub> = 500 μA | -                        | 200                                     | 1000                                  | nnm//   |  |  |

| I <sub>line_reg</sub>                            |                                                                                                 |                                   | I <sub>load</sub> = 4 mA   | -                        | 100                                     | 500                                   | ppm/V   |  |  |

| I <sub>load_reg</sub>                            | Load<br>regulation                                                                              | 500 µA ≤ I <sub>load</sub> ≤4 mA  | Normal mode                | -                        | 50                                      | 500                                   | ppm/mA  |  |  |

| T <sub>Coeff</sub>                               | Temperature<br>coefficient                                                                      | -40 °C < T <sub>J</sub> < +125 °C |                            |                          | T <sub>coeff</sub> _<br>vrefint +<br>50 | · ppm/ °C                             |         |  |  |

|                                                  |                                                                                                 | 0 °C < T <sub>J</sub> < +50 °C    |                            | -                        | -                                       | T <sub>coeff</sub><br>vrefint +<br>50 | ppin/ C |  |  |

| PSRR                                             | Power supply                                                                                    | DC<br>100 kHz                     |                            | 40                       | 60                                      | -                                     | dB      |  |  |

| FORR                                             | rejection                                                                                       |                                   |                            | 25                       | 40                                      | -                                     | uв      |  |  |

|                                                  | Start-up time                                                                                   | $CL = 0.5 \ \mu F^{(4)}$          |                            | -                        | 300                                     | 350                                   |         |  |  |

| t <sub>START</sub>                               |                                                                                                 | $CL = 1.1 \ \mu F^{(4)}$          |                            | -                        | 500                                     | 650                                   | μs      |  |  |

|                                                  |                                                                                                 | $CL = 1.5  \mu F^{(4)}$           |                            | -                        | 650                                     | 800                                   |         |  |  |

| I <sub>INRUSH</sub>                              | Control of<br>maximum DC<br>current drive<br>on VREFBUF_<br>OUT during<br>start-up phase<br>(5) | -                                 | -                          | -                        | 8                                       | -                                     | mA      |  |  |

## Table 75. VREFBUF characteristics<sup>(1)</sup>

# 6.3.21 Comparator characteristics

| Symbol                         | Parameter                                                              | Co                       | onditions                | Min                 | Тур  | Мах              | Unit |

|--------------------------------|------------------------------------------------------------------------|--------------------------|--------------------------|---------------------|------|------------------|------|

| V <sub>DDA</sub>               | Analog supply voltage                                                  |                          | -                        | 1.62                | -    | 3.6              |      |

| V <sub>IN</sub>                | Comparator input voltage range                                         | -                        |                          | 0                   | -    | V <sub>DDA</sub> | V    |

| V <sub>BG</sub> <sup>(2)</sup> | Scaler input voltage                                                   |                          | -                        | V <sub>REFINT</sub> |      |                  |      |

| V <sub>SC</sub>                | Scaler offset voltage                                                  |                          | -                        | -                   | ±5   | ±10              | mV   |

|                                | Scaler static consumption                                              | BRG_EN=0 (br             | ridge disable)           | -                   | 200  | 300              | nA   |

| I <sub>DDA</sub> (SCALER)      | from V <sub>DDA</sub>                                                  | BRG_EN=1 (bridge enable) |                          | -                   | 0.8  | 1                | μA   |

| t <sub>START_SCALER</sub>      | Scaler startup time                                                    |                          | -                        | -                   | 100  | 200              | μs   |

|                                | Comparator startup time to<br>reach propagation delay<br>specification | High-speed<br>mode       | V <sub>DDA</sub> ≥ 2.7 V | -                   | -    | 5                |      |

|                                |                                                                        |                          | V <sub>DDA</sub> < 2.7 V | -                   | -    | 7                | μs   |

| t <sub>START</sub>             |                                                                        | Medium mode              | V <sub>DDA</sub> ≥ 2.7 V | -                   | -    | 15               |      |

|                                |                                                                        |                          | V <sub>DDA</sub> < 2.7 V | -                   | -    | 25               |      |

|                                |                                                                        | Ultra-low-power mode     |                          | -                   | -    | 40               |      |

|                                | Propagation delay with                                                 | High-speed<br>mode       | V <sub>DDA</sub> ≥ 2.7 V | -                   | 55   | 80               | 20   |

| t <sub>D</sub> <sup>(3)</sup>  |                                                                        |                          | V <sub>DDA</sub> < 2.7 V | -                   | 65   | 100              | ns   |

| <sup>LD</sup>                  | 100 mV overdrive                                                       | Medium mode              |                          | -                   | 0.55 | 0.9              |      |

|                                |                                                                        | Ultra-low-power mode     |                          | -                   | 4    | 7                | μs   |

| V <sub>offset</sub>            | Comparator offset error                                                | Full common mode range   | -                        | -                   | ±5   | ±20              | mV   |

|                                |                                                                        | No hysteresis            |                          | -                   | 0    | -                | - mV |

| M                              |                                                                        | Low hysteresis           |                          | -                   | 8    | -                |      |

| V <sub>hys</sub>               | Comparator hysteresis                                                  | Medium hysteresis        |                          | -                   | 15   | -                |      |

|                                |                                                                        | High hysteresis          |                          | -                   | 27   | -                |      |

# Table 76. COMP characteristics<sup>(1)</sup>

| Symbol                            | Parameter                                              | Cor            | nditions                                                                          | Min                       | Тур  | Max  | Unit   |

|-----------------------------------|--------------------------------------------------------|----------------|-----------------------------------------------------------------------------------|---------------------------|------|------|--------|

| I <sub>LOAD</sub>                 | Drive current                                          | Normal mode    |                                                                                   | -                         | -    | 500  | μΑ     |

|                                   |                                                        | Low-power mode | V <sub>DDA</sub> ≥ 2 V                                                            | -                         | -    | 100  |        |

|                                   | Drive current in PGA mode                              | Normal mode    | V <sub>DDA</sub> ≥2V                                                              | -                         | -    | 450  |        |

| I <sub>LOAD_</sub> PGA            |                                                        | Low-power mode |                                                                                   | -                         | -    | 50   |        |

| P                                 | Resistive load<br>(connected to<br>VSSA or to<br>VDDA) | Normal mode    | - V <sub>DDA</sub> < 2 V                                                          | 4                         | -    | -    | - kΩ   |

| R <sub>LOAD</sub>                 |                                                        | Low-power mode |                                                                                   | 20                        | -    | -    |        |

| D                                 | Resistive load<br>in PGA mode                          | Normal mode    | V < 2 V                                                                           | 4.5                       | -    | -    |        |

| R <sub>LOAD_PGA</sub>             | (connected to<br>VSSA or to<br>V <sub>DDA</sub> )      | Low-power mode | – V <sub>DDA</sub> < 2 V                                                          | 40                        | -    | -    |        |

| C <sub>LOAD</sub>                 | Capacitive load                                        |                | -                                                                                 | -                         | -    | 50   | pF     |

| CMRR                              | Common mode                                            | Normal mode    |                                                                                   | -                         | -85  | -    | - dB   |

| CINIKK                            | rejection ratio                                        | Low-power mode |                                                                                   | -                         | -90  | -    |        |

| PSRR                              | Power supply rejection ratio                           | Normal mode    | C <sub>LOAD</sub> ≤ 50 pf,<br>R <sub>LOAD</sub> ≥ 4 kΩ DC                         | 70                        | 85   | -    | - dB   |

| PORK                              |                                                        | Low-power mode | C <sub>LOAD</sub> ≤ 50 pf,<br>R <sub>LOAD</sub> ≥ 20 kΩ DC                        | 72                        | 90   | -    |        |

|                                   | Gain Bandwidth<br>Product                              | Normal mode    | V <sub>DDA</sub> ≥ 2.4 V<br>(OPA_RANGE = 1)                                       | 550                       | 1600 | 2200 | - kHz  |

| GBW                               |                                                        | Low-power mode |                                                                                   | 100                       | 420  | 600  |        |

| GBW                               |                                                        | Normal mode    | V <sub>DDA</sub> < 2.4 V<br>(OPA_RANGE = 0)                                       | 250                       | 700  | 950  |        |

|                                   |                                                        | Low-power mode |                                                                                   | 40                        | 180  | 280  |        |

|                                   | Slew rate<br>(from 10 and<br>90% of output<br>voltage) | Normal mode    | - V <sub>DDA</sub> ≥ 2.4 V                                                        | -                         | 700  | -    | 1      |

| SR <sup>(3)</sup>                 |                                                        | Low-power mode |                                                                                   | -                         | 180  | -    | V/mo   |

| 36.7                              |                                                        | Normal mode    | - V <sub>DDA</sub> < 2.4 V                                                        | -                         | 300  | -    | - V/ms |

|                                   |                                                        | Low-power mode |                                                                                   | -                         | 80   | -    |        |

| 40                                | Open loop gain                                         | Normal mode    |                                                                                   | 55                        | 110  | -    | ٩D     |

| AO                                |                                                        | Low-power mode |                                                                                   | 45                        | 110  | -    | - dB   |

| V <sub>OHSAT</sub> <sup>(3)</sup> | High saturation voltage                                | Normal mode    | I <sub>load</sub> = max or R <sub>load</sub> =<br>min Input at V <sub>DDA</sub> . | V <sub>DDA</sub> -<br>100 | -    | -    | mV     |

| ♥ OHSAT`´                         |                                                        | Low-power mode |                                                                                   | V <sub>DDA</sub> -<br>50  | -    | -    |        |

| V <sub>OLSAT</sub> <sup>(3)</sup> | Low saturation voltage                                 | Normal mode    | I <sub>load</sub> = max or R <sub>load</sub> =                                    | -                         | -    | 100  |        |

| VOLSAT`                           |                                                        | Low-power mode | min Input at 0.                                                                   | -                         | -    | 50   |        |

| (1)                               | Phase margin                                           | Normal mode    | -                                                                                 |                           | 74   | -    | 0      |

| φ <sub>m</sub>                    | r nase maryin                                          | Low-power mode |                                                                                   | -                         | 66   | -    | ]      |

Table 77. OPAMP characteristics<sup>(1)</sup> (continued)

Г

#### **SPI characteristics**

Unless otherwise specified, the parameters given in *Table 85* for SPI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 23: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                                | Parameter                | Conditions                                                                              | Min                              | Тур               | Мах                  | Unit |

|-------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------|----------------------------------|-------------------|----------------------|------|

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>             | SPI clock frequency      | Master mode receiver/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1    |                                  |                   | 40                   |      |

|                                                       |                          | Master mode receiver/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1   |                                  |                   | 16                   |      |

|                                                       |                          | Master mode transmitter<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1            |                                  |                   | 40                   |      |

|                                                       |                          | Slave mode receiver<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                | -                                | -                 | 40                   | MHz  |

|                                                       |                          | Slave mode transmitter/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  |                                  |                   | 37 <sup>(2)</sup>    |      |

|                                                       |                          | Slave mode transmitter/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 |                                  |                   | 20 <sup>(2)</sup>    |      |

|                                                       |                          | Voltage Range 2                                                                         |                                  |                   | 13                   |      |

| t <sub>su(NSS)</sub>                                  | NSS setup time           | Slave mode, SPI prescaler = 2                                                           | 4 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |

| t <sub>h(NSS)</sub>                                   | NSS hold time            | Slave mode, SPI prescaler = 2                                                           | 2 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |

| $\begin{array}{c}t_{w(SCKH)}\\t_{w(SCKL)}\end{array}$ | SCK high and low time    | Master mode                                                                             | T <sub>PCLK</sub> -2             | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2 | ns   |

| t <sub>su(MI)</sub>                                   | Data input setup time    | Master mode                                                                             | 4                                | -                 | -                    | ns   |

| t <sub>su(SI)</sub>                                   |                          | Slave mode                                                                              | 1.5                              | -                 | -                    | 115  |

| t <sub>h(MI)</sub>                                    | Deta input hold time     | Master mode                                                                             | 6.5                              | -                 | -                    | ns   |

| t <sub>h(SI)</sub>                                    | Data input hold time     | Slave mode                                                                              | 1.5                              | -                 | -                    | 115  |

| t <sub>a(SO)</sub>                                    | Data output access time  | Slave mode                                                                              | 9                                | -                 | 36                   | ns   |

| t <sub>dis(SO)</sub>                                  | Data output disable time | Slave mode                                                                              | 9                                | -                 | 16                   | ns   |

### Table 85. SPI characteristics<sup>(1)</sup>

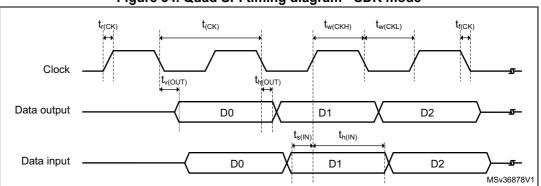

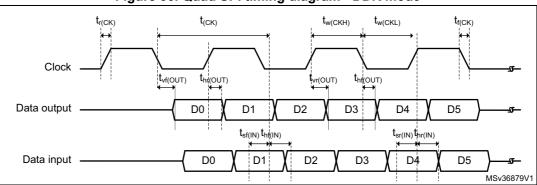

### **Quad SPI characteristics**

Unless otherwise specified, the parameters given in *Table 86* and *Table 87* for Quad SPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 23: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 15 or 20 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics.

| Symbol              | Parameter                | Conditions                                                                   | Min                    | Тур | Мах                    | Unit |

|---------------------|--------------------------|------------------------------------------------------------------------------|------------------------|-----|------------------------|------|

|                     | Quad SPI clock frequency | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 20 pF<br>Voltage Range 1 | -                      | -   | 40                     |      |

| F <sub>CK</sub>     |                          | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 15 pF<br>Voltage Range 1 | -                      | -   | 48                     | MHz  |

| 1/t <sub>(CK)</sub> |                          | 2.7 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 15 pF<br>Voltage Range 1  | -                      | -   | 60                     | MHZ  |

|                     |                          | 1.71 < V <sub>DD</sub> < 3.6 V C <sub>LOAD</sub> = 20 pF<br>Voltage Range 2  | -                      | -   | 26                     |      |

| t <sub>w(CKH)</sub> | Quad SPI clock high and  | f <sub>AHBCLK</sub> = 48 MHz, presc=0                                        | t <sub>(CK)</sub> /2-2 | -   | t <sub>(CK)</sub> /2   |      |

| t <sub>w(CKL)</sub> | low time                 |                                                                              | t <sub>(СК)</sub> /2   | -   | t <sub>(CK)</sub> /2+2 |      |

| t ann               | Data input setup time    | Voltage Range 1                                                              | 2                      | -   | -                      |      |

| t <sub>s(IN)</sub>  | Data input setup time    | Voltage Range 2                                                              | 3.5                    | -   | -                      |      |

| +                   | Data input hold time     | Voltage Range 1                                                              | 5                      | -   | -                      | ns   |

| t <sub>h(IN)</sub>  |                          | Voltage Range 2                                                              | 6.5                    | -   | -                      | 115  |

| +                   | Data output valid time   | Voltage Range 1                                                              | -                      | 1   | 5                      |      |

| t <sub>v(OUT)</sub> | Data output valid time   | Voltage Range 2                                                              | -                      | 3   | 5                      |      |

| +                   | Data output hold time    | Voltage Range 1                                                              | 0                      | -   | -                      |      |

| <sup>t</sup> h(OUT) | Data output hold time    | Voltage Range 2                                                              | 0                      | -   | -                      |      |

1. Guaranteed by characterization results.

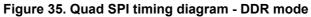

Figure 45. UFBGA100 marking (package top view)

Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature T<sub>Amax</sub> = 75 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 8 I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax</sub> = 20 × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 272 mW:

P<sub>Dmax</sub> = 175 + 272 = 447 mW

Using the values obtained in *Table 100*  $T_{Jmax}$  is calculated as follows:

– For LQFP64, 58 °C/W

T<sub>Jmax</sub> = 75 °C + (58 °C/W × 447 mW) = 75 °C + 25.926 °C = 100.926 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ) see Section 8: Ordering information.

In this case, parts must be ordered at least with the temperature range suffix 6 (see Part numbering).

Note:

With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 3).

Suffix 6:  $T_{Amax} = T_{Jmax} - (58^{\circ}C/W \times 447 \text{ mW}) = 105-25.926 = 79.074 ^{\circ}C$ Suffix 3:  $T_{Amax} = T_{Jmax} - (58^{\circ}C/W \times 447 \text{ mW}) = 130-25.926 = 104.074 ^{\circ}C$

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 100 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 20 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V

$P_{INTmax} = 20 \text{ mA} \times 3.5 \text{ V} = 70 \text{ mW}$  $P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives: P<sub>INTmax</sub> = 70 mW and P<sub>IOmax</sub> = 64 mW:

P<sub>Dmax</sub> = 70 + 64 = 134 mW

Thus: P<sub>Dmax</sub> = 134 mW

Using the values obtained in *Table 100*  $T_{Jmax}$  is calculated as follows:

For LQFP64, 58 °C/W

T<sub>Jmax</sub> = 100 °C + (58 °C/W × 134 mW) = 100 °C + 7.772 °C = 107.772 °C

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).