# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 80MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                      |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 160K × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l451ret6tr    |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| - 11 |

|------|

| 2    |

| -    |

| ō    |

| Ë.   |

| ō    |

| ž    |

| 20   |

| =    |

| 0    |

| Ş    |

| 2    |

| Ť    |

| <    |

| Ξ.   |

| 9    |

| 2    |

DS11910 Rev 4

5

|   |         |                          |     |                                                                                                                             | Та                                                                                                | ble 4. Sl            | M32L451xx modes over                                                                                                  | view                                                                                           |                            |                                       |

|---|---------|--------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------|

|   | Mode    | Regulator <sup>(1)</sup> | CPU | Flash                                                                                                                       | SRAM                                                                                              | Clocks               | DMA & Peripherals <sup>(2)</sup>                                                                                      | Wakeup source                                                                                  | Consumption <sup>(3)</sup> | Wakeup time                           |

|   | Run     | MR range 1               | Yes | ON <sup>(4)</sup>                                                                                                           | ON                                                                                                | Any                  | All                                                                                                                   | N/A                                                                                            | 94 µA/MHz                  | N/A                                   |

|   | Run     | MR range2                | res | UN.                                                                                                                         | ON                                                                                                | Any                  | All except RNG                                                                                                        |                                                                                                | 85 µA/MHz                  | IN/A                                  |

|   | LPRun   | LPR                      | Yes | ON <sup>(4)</sup>                                                                                                           | ON                                                                                                | Any<br>except<br>PLL | All except RNG                                                                                                        | N/A                                                                                            | 95 µA/MHz                  | to Range 1: 4 μs<br>to Range 2: 64 μs |

|   | Sleep   | MR range 1               | No  | ON <sup>(4)</sup>                                                                                                           | ON <sup>(5)</sup>                                                                                 | Any                  | All                                                                                                                   | Any interrupt or                                                                               | 27 µA/MHz                  | 6 cycles                              |

|   | Sleep   | MR range2                |     |                                                                                                                             | UN.                                                                                               | Any                  | All except RNG                                                                                                        | event                                                                                          | 27 µA/MHz                  | o cycles                              |

| I | LPSleep | LPR                      | No  | ON <sup>(4)</sup>                                                                                                           | ON <sup>(5)</sup>                                                                                 | Any<br>except<br>PLL | All except RNG                                                                                                        | Any interrupt or<br>event 38 μA/MHz                                                            |                            | 6 cycles                              |

|   | Stop 0  |                          |     | BOR, PVD, PVM<br>RTC, IWDG<br>COMPx (x=1,2)<br>DAC1<br>OPAMPx (x=1)<br>USARTx (x=13) <sup>(6)</sup><br>UART4 <sup>(6)</sup> | Reset pin, all I/Os<br>BOR, PVD, PVM<br>RTC, IWDG<br>COMPx (x=12)<br>USARTx (x=13) <sup>(6)</sup> | 125 µA               | 2.47 µs in SRAM                                                                                                       |                                                                                                |                            |                                       |

|   |         | MR Range 2               |     |                                                                                                                             |                                                                                                   | LSI                  | LPUART1 <sup>(6)</sup><br>I2Cx (x=14) <sup>(7)</sup><br>LPTIMx (x=1,2)<br>***<br>All other peripherals are<br>frozen. | UART4 <sup>(6)</sup><br>LPUART1 <sup>(6)</sup><br>I2Cx (x=14) <sup>(7)</sup><br>LPTIMx (x=1,2) | 125 µA                     | 4.1 μs in Flash                       |

24/201

STM32L451xx

# 3.11 Clocks and startup

The clock controller (see *Figure 4*) distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source:** four different clock sources can be used to drive the master clock SYSCLK:

- 4-48 MHz high-speed external crystal or ceramic resonator (HSE), that can supply a PLL. The HSE can also be configured in bypass mode for an external clock.

- 16 MHz high-speed internal RC oscillator (HSI16), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 12 frequencies from 100 kHz to 48 MHz. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be automatically trimmed by hardware to reach better than ±0.25% accuracy. The MSI can supply a PLL.

- System PLL which can be fed by HSE, HSI16 or MSI, with a maximum frequency at 80 MHz.

- **RC48 with clock recovery system (HSI48)**: internal RC48 MHz clock source can be used to drive the SDMMC or the RNG peripherals. This clock can be output on the MCO.

- **Auxiliary clock source:** two ultralow-power clock sources that can be used to drive the real-time clock:

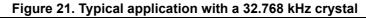

- 32.768 kHz low-speed external crystal (LSE), supporting four drive capability modes. The LSE can also be configured in bypass mode for an external clock.

- 32 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock accuracy is ±5% accuracy.

- **Peripheral clock sources:** Several peripherals (SDMMC, RNG, SAI, USARTs, I2Cs, LPTimers, ADC) have their own independent clock whatever the system clock. Two PLLs, each having three independent outputs allowing the highest flexibility, can generate independent clocks for the ADC, the SDMMC/RNG and the SAI.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 4 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- **Clock security system (CSS):** this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI16 and a software

# 3.14 Interrupts and events

### 3.14.1 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 67 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\mathbb{B}}$ -M4.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved on interrupt entry, and restored on interrupt exit, with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

### 3.14.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 37 edge detector lines used to generate interrupt/event requests and wake-up the system from Stop mode. Each external line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The internal lines are connected to peripherals with wakeup from Stop mode capability. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 83 GPIOs can be connected to the 16 external interrupt lines.

hardware. DFSDM features optional parallel data stream inputs from microcontrollers memory (through DMA/CPU transfers into DFSDM).

DFSDM transceivers support several serial interface formats (to support various  $\Sigma\Delta$  modulators). DFSDM digital filter modules perform digital processing according user selected filter parameters with up to 24-bit final ADC resolution.

The DFSDM peripheral supports:

- 4 multiplexed input digital serial channels:

- configurable SPI interface to connect various SD modulator(s)

- configurable Manchester coded 1 wire interface support

- PDM (Pulse Density Modulation) microphone input support

- maximum input clock frequency up to 20 MHz (10 MHz for Manchester coding)

- clock output for SD modulator(s): 0..20 MHz

- alternative inputs from 8 internal digital parallel channels (up to 16 bit input resolution):

- internal sources: device memory data streams (DMA)

- 2 digital filter modules with adjustable digital signal processing:

- Sinc<sup>x</sup> filter: filter order/type (1..5), oversampling ratio (up to 1..1024)

- integrator: oversampling ratio (1..256)

- up to 24-bit output data resolution, signed output data format

- automatic data offset correction (offset stored in register by user)

- continuous or single conversion

- start-of-conversion triggered by:

- software trigger

- internal timers

- external events

- start-of-conversion synchronously with first digital filter module (DFSDM1\_FLT0)

- analog watchdog feature:

- low value and high value data threshold registers

- dedicated configurable Sincx digital filter (order = 1..3, oversampling ratio = 1..32)

- input from final output data or from selected input digital serial channels

- continuous monitoring independently from standard conversion

- short circuit detector to detect saturated analog input values (bottom and top range):

- up to 8-bit counter to detect 1..256 consecutive 0's or 1's on serial data stream

- monitoring continuously each input serial channel

- break signal generation on analog watchdog event or on short circuit detector event

- extremes detector:

- storage of minimum and maximum values of final conversion data

- refreshed by software

- DMA capability to read the final conversion data

- interrupts: end of conversion, overrun, analog watchdog, short circuit, input serial channel clock absence

- "regular" or "injected" conversions:

- "regular" conversions can be requested at any time or even in continuous mode

### 3.23.1 Advanced-control timer (TIM1)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIMx timers (described in *Section 3.23.2*) using the same architecture, so the advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

### 3.23.2 General-purpose timers (TIM2, TIM3, TIM15, TIM16)

There are up to three synchronizable general-purpose timers embedded in the STM32L451xx (see *Table 11* for differences). Each general-purpose timer can be used to generate PWM outputs, or act as a simple time base.

• TIM2, TIM3

They are full-featured general-purpose timers:

- TIM2 has a 32-bit auto-reload up/downcounter and 32-bit prescaler.

- TIM3 has 16-bit auto-reload up/downcounter and 16-bit prescaler.

These timers feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. They can work with the other general-purpose timers via the Timer Link feature for synchronization or event chaining.

The counters can be frozen in debug mode.

All have independent DMA request generation and support quadrature encoder.

TIM15 and 16

They are general-purpose timers with mid-range features:

They have 16-bit auto-reload upcounters and 16-bit prescalers.

- TIM15 has 2 channels and 1 complementary channel

- TIM16 has 1 channel and 1 complementary channel

All channels can be used for input capture/output compare, PWM or one-pulse mode output.

The timers can work together via the Timer Link feature for synchronization or event chaining. The timers have independent DMA request generation.

The counters can be frozen in debug mode.

### 3.23.3 Basic timer (TIM6)

The basic timer is mainly used for DAC trigger generation. It can also be used as generic 16-bit timebase.

# 4 Pinouts and pin description

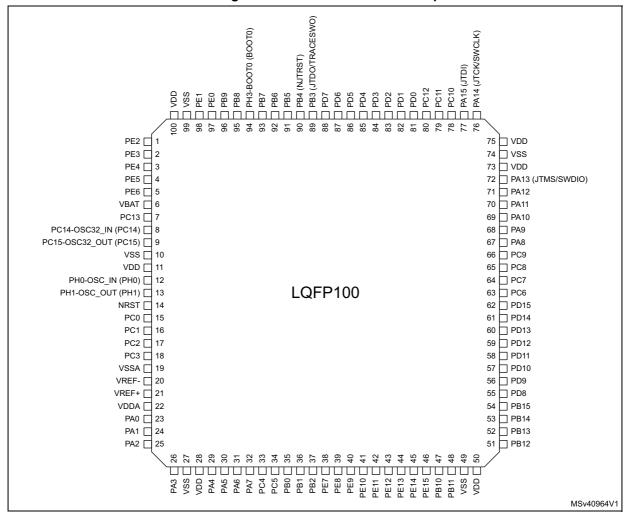

Figure 6. STM32L451Vx LQFP100 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

|                 | I       | Pin I  | Num     | ber     | -        |                                       |          |               |       | n definitions (continued)<br>Pin fund                                                                                                               | ctions               |

|-----------------|---------|--------|---------|---------|----------|---------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <b>UFQFPN48</b> | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                 | Additional functions |

| -               | -       | -      | -       | 86      | A6       | PD5                                   | I/O      | FT            | -     | USART2_TX,<br>QUADSPI_BK2_IO1,<br>EVENTOUT                                                                                                          | -                    |

| -               | -       | -      | -       | 87      | В6       | PD6                                   | I/O      | FT            | -     | DFSDM1_DATIN1,<br>USART2_RX,<br>QUADSPI_BK2_IO2,<br>SAI1_SD_A, EVENTOUT                                                                             | -                    |

| -               | -       | -      | -       | 88      | A5       | PD7                                   | I/O      | FT            | -     | DFSDM1_CKIN1,<br>USART2_CK,<br>QUADSPI_BK2_IO3,<br>EVENTOUT                                                                                         | -                    |

| 39              | B4      | 55     | A5      | 89      | A8       | PB3<br>(JTDO/<br>TRACE<br>SWO)        | I/O      | FT_a          | (3)   | JTDO/TRACESWO,<br>TIM2_CH2, SPI1_SCK,<br>SPI3_SCK,<br>USART1_RTS_DE,<br>SAI1_SCK_B, EVENTOUT                                                        | COMP2_INM            |

| 40              | A4      | 56     | A4      | 90      | A7       | PB4<br>(NJTRST)                       | I/O      | FT_fa         | (3)   | NJTRST, TIM3_CH1,<br>I2C3_SDA, SPI1_MISO,<br>SPI3_MISO,<br>USART1_CTS,<br>TSC_G2_IO1,<br>SAI1_MCLK_B,<br>EVENTOUT                                   | COMP2_INP            |

| 41              | C5      | 57     | C4      | 91      | C5       | PB5                                   | I/O      | FT            | -     | LPTIM1_IN1, TIM3_CH2,<br>CAN1_RX, I2C1_SMBA,<br>SPI1_MOSI, SPI3_MOSI,<br>USART1_CK,<br>TSC_G2_IO2,<br>COMP2_OUT, SAI1_SD_B,<br>TIM16_BKIN, EVENTOUT | -                    |

| 42              | B5      | 58     | D3      | 92      | B5       | PB6                                   | I/O      | FT_fa         | -     | LPTIM1_ETR, I2C1_SCL,<br>I2C4_SCL, USART1_TX,<br>CAN1_TX, TSC_G2_IO3,<br>SAI1_FS_B, TIM16_CH1N,<br>EVENTOUT                                         | COMP2_INP            |

| 43              | A5      | 59     | C3      | 93      | В4       | PB7                                   | I/O      | FT_fa         | -     | LPTIM1_IN2, I2C1_SDA,<br>I2C4_SDA, USART1_RX,<br>UART4_CTS,<br>TSC_G2_IO4, EVENTOUT                                                                 | COMP2_INM, PVD_IN    |

| 44              | В6      | 60     | B4      | 94      | A4       | PH3-<br>BOOT0<br>(BOOT0)              | I/O      | -             | -     | EVENTOUT                                                                                                                                            | BOOT0                |

Table 16. STM32L451xx pin definitions (continued)

#### 5

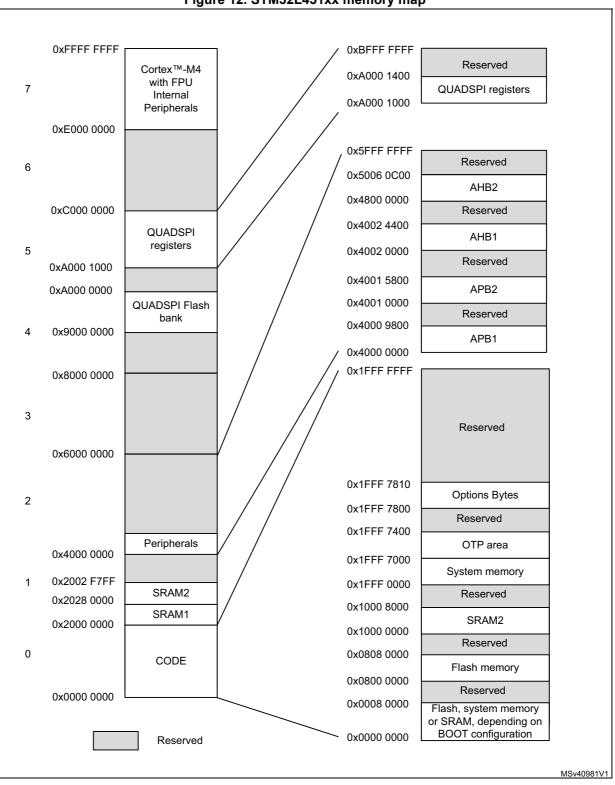

# Memory mapping

Figure 12. STM32L451xx memory map

DS11910 Rev 4

- 1. When RESET is released functionality is guaranteed down to  $V_{BOR0}$  Min.

- 2. This formula has to be applied only on the power supplies related to the IO structure described by the pin definition table. Maximum I/O input voltage is the smallest value between  $Min(V_{DD}, V_{DDA})$ +3.6 V and 5.5V.

- 3. For operation with voltage higher than Min ( $V_{DD}$ ,  $V_{DDA}$ ) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- 4. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.7: Thermal characteristics).

- In low-power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.7: Thermal characteristics).

#### 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 24* are derived from tests performed under the ambient temperature condition summarized in *Table 23*.

| Symbol            | Parameter                       | Conditions | Min | Мах | Unit  |  |  |  |  |  |  |

|-------------------|---------------------------------|------------|-----|-----|-------|--|--|--|--|--|--|

| +                 | V <sub>DD</sub> rise time rate  |            | 0   | 8   | us/V  |  |  |  |  |  |  |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate  | -          | 10  | 8   | μ5/ν  |  |  |  |  |  |  |

| t                 | V <sub>DDA</sub> rise time rate | _          | 0   | 8   | us/V  |  |  |  |  |  |  |

| <sup>t</sup> VDDA | V <sub>DDA</sub> fall time rate | -          | 10  | 8   | μ3/ ν |  |  |  |  |  |  |

Table 24. Operating conditions at power-up / power-down

The requirements for power-up/down sequence specified in *Section 3.9.1: Power supply schemes* must be respected.

#### 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 25* are derived from tests performed under the ambient temperature conditions summarized in *Table 23: General operating conditions*.

| Symbol                               | Parameter                                     | Conditions <sup>(1)</sup> | Min  | Тур  | Мах  | Unit |  |

|--------------------------------------|-----------------------------------------------|---------------------------|------|------|------|------|--|

| t <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization after<br>BOR0 is detected | V <sub>DD</sub> rising    | -    | 250  | 400  | μs   |  |

| V <sub>BOR0</sub> <sup>(2)</sup>     | Brown-out reset threshold 0                   | Rising edge               | 1.62 | 1.66 | 1.7  | V    |  |

| VBOR0                                | brown-out reset threshold o                   | Falling edge              | 1.6  | 1.64 | 1.69 | v    |  |

| V <sub>BOR1</sub>                    | Brown-out reset threshold 1                   | Rising edge               | 2.06 | 2.1  | 2.14 | V    |  |

|                                      | Brown-out reset threshold 1                   | Falling edge              | 1.96 | 2    | 2.04 |      |  |

| V                                    | Brown-out reset threshold 2                   | Rising edge               | 2.26 | 2.31 | 2.35 | V    |  |

| V <sub>BOR2</sub>                    | brown-out reset threshold 2                   | Falling edge              | 2.16 | 2.20 | 2.24 |      |  |

| V                                    | Brown-out reset threshold 3                   | Rising edge               | 2.56 | 2.61 | 2.66 | V    |  |

| V <sub>BOR3</sub>                    | Brown-out reset threshold 5                   | Falling edge              | 2.47 | 2.52 | 2.57 | v    |  |

| N .                                  | Brown-out reset threshold 4                   | Rising edge               | 2.85 | 2.90 | 2.95 | V    |  |

| V <sub>BOR4</sub>                    | Brown-out reset tilleshold 4                  | Falling edge              | 2.76 | 2.81 | 2.86 | v    |  |

Table 25. Embedded reset and power control block characteristics

|                                 |              | Tabi            | e 37. Ci | unent | consun | iption i | i Stop t | ,                  |       |       |        |                     |      |    |

|---------------------------------|--------------|-----------------|----------|-------|--------|----------|----------|--------------------|-------|-------|--------|---------------------|------|----|

| Symbol                          | Parameter    | Conditions      | ТҮР      |       |        |          |          | MAX <sup>(1)</sup> |       |       |        |                     | Unit |    |

|                                 | Farameter    | V <sub>DD</sub> | 25 °C    | 55 °C | 85 °C  | 105 °C   | 125 °C   | 25 °C              | 55 °C | 85 °C | 105 °C | 125 °C              | Onit |    |

| I <sub>DD_ALL</sub><br>(Stop 0) |              | Supply          | 1.8 V    | 125   | 150    | 240      | 390      | 645                | 145   | 190   | 350    | 600                 | 1150 |    |

|                                 | current in   | 2.4 V           | 125      | 150   | 240    | 390      | 645      | 150                | 195   | 355   | 605    | 1150                | uА   |    |

|                                 | (Stop 0)     | Stop 0 mode,    | 3 V      | 125   | 150    | 245      | 395      | 650                | 155   | 195   | 360    | 610                 | 1150 | μΛ |

|                                 | RTC disabled | 3.6 V           | 125      | 155   | 245    | 400      | 655      | 155                | 200   | 365   | 615    | 1150 <sup>(2)</sup> |      |    |

#### Table 37. Current consumption in Stop 0

1. Guaranteed by characterization results, unless otherwise specified.

2. Guaranteed by test in production.

**N**

| Ш        |

|----------|

| e        |

| ¥        |

| ö        |

| a        |

| <u>0</u> |

| ş        |

| T,       |

| ត្តី     |

| ē        |

| Ţ.       |

| Ť.       |

| S        |

|          |

|                                 | T                            | Table 38.                                                  | Curre    | nt con | sumpti |       | tanuby | mode   |                    |       |       |        |        | -    |       |  |

|---------------------------------|------------------------------|------------------------------------------------------------|----------|--------|--------|-------|--------|--------|--------------------|-------|-------|--------|--------|------|-------|--|

| Symbol                          | Parameter                    | Conditions                                                 |          |        |        | TYP   |        |        | MAX <sup>(1)</sup> |       |       |        |        |      |       |  |

| Symbol                          | Falameter                    | -                                                          | $V_{DD}$ | 25 °C  | 55 °C  | 85 °C | 105 °C | 125 °C | 25 °C              | 55 °C | 85 °C | 105 °C | 125 °C |      |       |  |

|                                 |                              |                                                            | 1.8 V    | 100    | 270    | 1200  | 3300   | 8650   | 205                | 650   | 3250  | 9250   | 25000  | ٦    |       |  |

|                                 |                              | na indonandant watabdag                                    | 2.4 V    | 110    | 305    | 1400  | 3850   | 10000  | 225                | 750   | 3750  | 11000  | 29000  | -    |       |  |

|                                 | Supply current<br>in Standby | no independent watchdog                                    | 3 V      | 125    | 360    | 1650  | 4550   | 12000  | 290                | 950   | 4450  | 13000  | 33500  |      |       |  |

| I <sub>DD ALL</sub>             | mode (backup                 |                                                            | 3.6 V    | 160    | 445    | 2000  | 5500   | 14500  | 355                | 1150  | 5250  | 15000  | 38500  |      |       |  |

| (Standby)                       | registers                    |                                                            | 1.8 V    | 265    | 435    | 1350  | 3450   | 8700   | -                  | -     | -     | -      | -      |      |       |  |

|                                 | retained),<br>RTC disabled   | with independent                                           | 2.4 V    | 335    | 540    | 1650  | 4100   | 10500  | -                  | -     | -     | -      | -      |      |       |  |

|                                 |                              | watchdog                                                   | 3 V      | 420    | 655    | 1950  | 4850   | 12500  | -                  | -     | -     | -      | -      |      |       |  |

|                                 |                              |                                                            | 3.6 V    | 580    | 895    | 2450  | 5950   | 14500  | -                  | -     | -     | -      | -      |      |       |  |

|                                 | Supply current               |                                                            |          |        | 1.8 V  | 345   | 505    | 1400   | 3450               | 8600  | 720   | 1150   | 3750   | 9550 | 25000 |  |

|                                 |                              | RTC clocked by LSI, no                                     | 2.4 V    | 420    | 620    | 1650  | 4050   | 10000  | 875                | 1450  | 4400  | 11500  | 29000  |      |       |  |

|                                 |                              |                                                            | 3 V      | 510    | 745    | 2000  | 4750   | 12000  | 1070               | 1700  | 5100  | 13500  | 34000  |      |       |  |

|                                 |                              |                                                            | 3.6 V    | 635    | 915    | 2450  | 5900   | 14500  | 1320               | 2100  | 6000  | 15500  | 39000  |      |       |  |

|                                 |                              |                                                            | 1.8 V    | 375    | 540    | 1450  | 3550   | 8800   | -                  | -     | -     | -      | -      |      |       |  |

|                                 |                              |                                                            | 2.4 V    | 490    | 690    | 1800  | 4250   | 10500  | -                  | -     | -     | -      | -      |      |       |  |

|                                 |                              |                                                            | 3 V      | 620    | 860    | 2150  | 5100   | 12500  | -                  | -     | -     | -      | -      |      |       |  |

| I <sub>DD_ALL</sub><br>(Standby | mode (backup                 |                                                            | 3.6 V    | 845    | 1150   | 2700  | 6200   | 15000  | -                  | -     | -     | -      | -      |      |       |  |

| with RTC)                       | registers<br>retained),      |                                                            | 1.8 V    | 395    | -      | -     | -      | -      | -                  | -     | -     | -      | -      |      |       |  |

|                                 | RTC enabled                  | RTC clocked by LSE                                         | 2.4 V    | 500    | -      | -     | -      | -      | -                  | -     | -     | -      | -      |      |       |  |

|                                 |                              | bypassed at 32768Hz                                        | 3 V      | 625    | -      | -     | -      | -      | -                  | -     | -     | -      | -      |      |       |  |

|                                 |                              |                                                            | 3.6 V    | 795    | -      | -     | -      | -      | -                  | -     | -     | -      | -      |      |       |  |

|                                 |                              |                                                            | 1.8 V    | 375    | 550    | 1500  | 3550   | 8800   | -                  | -     | -     | -      | -      |      |       |  |

|                                 |                              | RTC clocked by LSE quartz <sup>(2)</sup> in low drive mode | 2.4 V    | 460    | 665    | 1750  | 4250   | 10500  | -                  | -     | -     | -      | -      | _    |       |  |

|                                 |                              |                                                            | 3 V      | 565    | 810    | 2100  | 5050   | 12500  | -                  | -     | -     | -      | -      | _    |       |  |

|                                 |                              |                                                            | 3.6 V    | 720    | 1000   | 2600  | 5900   | 15000  | -                  | -     | -     | -      | -      |      |       |  |

106/201

DS11910 Rev 4

5

- 1. Guaranteed by design.

- 2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

- 3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

### 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 56*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                      | Level/<br>Class |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------|--|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, $T_A$ = +25 °C,<br>f <sub>HCLK</sub> = 80 MHz,<br>conforming to IEC 61000-4-2 | 3B              |  |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = +25 °C,<br>f <sub>HCLK</sub> = 80 MHz,<br>conforming to IEC 61000-4-4 | 5A              |  |

#### Table 56. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

| Speed | Symbol | Parameter                 | Conditions                                 | Min | Max | Unit |  |  |  |  |  |

|-------|--------|---------------------------|--------------------------------------------|-----|-----|------|--|--|--|--|--|

|       |        |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 5   |      |  |  |  |  |  |

|       |        |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1   |      |  |  |  |  |  |

|       | Fmax   | Maximum frequency         | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 | MHz  |  |  |  |  |  |

|       | FIIIdX |                           | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 10  |      |  |  |  |  |  |

|       |        |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1.5 |      |  |  |  |  |  |

| 00    |        |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 |      |  |  |  |  |  |

| 00    |        |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |      |  |  |  |  |  |

|       |        |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 52  |      |  |  |  |  |  |

|       | Tr/Tf  | Output rise and fall time | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 140 | nc   |  |  |  |  |  |

|       | 11/11  |                           | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 17  | ns   |  |  |  |  |  |

|       |        |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 37  |      |  |  |  |  |  |

|       |        |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 110 |      |  |  |  |  |  |

|       |        |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |      |  |  |  |  |  |

|       |        |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 10  | 7    |  |  |  |  |  |

|       | Fmax   |                           | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   | MHz  |  |  |  |  |  |

|       | Fillax | Maximum frequency         | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 50  |      |  |  |  |  |  |

|       |        |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 15  |      |  |  |  |  |  |

| 01    |        |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   |      |  |  |  |  |  |

| 01    |        |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 9   |      |  |  |  |  |  |

|       |        |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 16  |      |  |  |  |  |  |

|       | Tr/Tf  | Output rise and fall time | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 40  | 20   |  |  |  |  |  |

|       | 11/11  | Output rise and fall time | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 4.5 | ns   |  |  |  |  |  |

|       |        |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 9   | 1    |  |  |  |  |  |

|       |        |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 21  |      |  |  |  |  |  |

Table 63. I/O AC characteristics<sup>(1)(2)</sup>

| Sym-<br>bol                  | Parameter               | (                                                                                                | Conditions <sup>(4</sup> | )                        | Min  | Тур  | Max | Unit |

|------------------------------|-------------------------|--------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------|------|-----|------|

|                              |                         |                                                                                                  | Single                   | Fast channel (max speed) | -    | 4    | 6.5 |      |

| ET                           | Total                   |                                                                                                  | ended                    | Slow channel (max speed) | -    | 4    | 6.5 |      |

|                              | unadjusted<br>error     |                                                                                                  | Differential             | Fast channel (max speed) | -    | 3.5  | 5.5 |      |

|                              |                         |                                                                                                  | Dillerential             | Slow channel (max speed) | -    | 3.5  | 5.5 |      |

|                              |                         |                                                                                                  | Single                   | Fast channel (max speed) | -    | 1    | 4.5 |      |

| EO                           | Offset                  |                                                                                                  | ended                    | Slow channel (max speed) | -    | 1    | 5   |      |

| EU                           | error                   |                                                                                                  | Differential             | Fast channel (max speed) | -    | 1.5  | 3   |      |

|                              |                         |                                                                                                  | Dillerential             | Slow channel (max speed) | -    | 1.5  | 3   |      |

|                              |                         |                                                                                                  | Single                   | Fast channel (max speed) | -    | 2.5  | 6   |      |

| EG Gain error                |                         | ended                                                                                            | Slow channel (max speed) | -                        | 2.5  | 6    | LSB |      |

|                              | _                       | Differential                                                                                     | Fast channel (max speed) | -                        | 2.5  | 3.5  | LOD |      |

|                              |                         | Dillerential                                                                                     | Slow channel (max speed) | -                        | 2.5  | 3.5  |     |      |

| Differential<br>ED linearity |                         | Single                                                                                           | Fast channel (max speed) | -                        | 1    | 1.5  |     |      |

|                              |                         | rity<br>ADC clock frequency ≤<br>80 MHz,<br>Sampling rate ≤ 5.33 Msps,<br>2 V ≤ V <sub>DDA</sub> | ended                    | Slow channel (max speed) | -    | 1    | 1.5 | -    |

| ED                           | error                   |                                                                                                  | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |      |

|                              |                         |                                                                                                  | Differential             | Slow channel (max speed) | -    | 1    | 1.2 |      |

|                              |                         |                                                                                                  | Single<br>ended          | Fast channel (max speed) | -    | 1.5  | 3.5 |      |

| EL                           | Integral                |                                                                                                  |                          | Slow channel (max speed) | -    | 1.5  | 3.5 |      |

| EL                           | linearity<br>error      |                                                                                                  | Differential             | Fast channel (max speed) | -    | 1    | 3   |      |

|                              |                         |                                                                                                  |                          | Slow channel (max speed) | -    | 1    | 2.5 |      |

|                              |                         |                                                                                                  | Single                   | Fast channel (max speed) | 10   | 10.5 | -   |      |

|                              | Effective               |                                                                                                  | ended                    | Slow channel (max speed) | 10   | 10.5 | -   | hita |

| ENOB                         | number of bits          |                                                                                                  | Differential             | Fast channel (max speed) | 10.7 | 10.9 | -   | bits |

|                              |                         |                                                                                                  | Differential             | Slow channel (max speed) | 10.7 | 10.9 | -   |      |

|                              | Oisse al ta             |                                                                                                  | Single                   | Fast channel (max speed) | 62   | 65   | -   |      |

| SINAD                        | Signal-to-<br>noise and |                                                                                                  | ended                    | Slow channel (max speed) | 62   | 65   | -   |      |

| SINAD                        | distortion              |                                                                                                  | Differential             | Fast channel (max speed) | 66   | 67.4 | -   |      |

|                              | ratio                   |                                                                                                  | Differential             | Slow channel (max speed) | 66   | 67.4 | -   |      |

|                              |                         |                                                                                                  | Single                   | Fast channel (max speed) | 64   | 66   | -   | dB   |

|                              | Signal-to-              |                                                                                                  | ended                    | Slow channel (max speed) | 64   | 66   | -   | 1    |

| SNR                          | noise ratio             |                                                                                                  | Differential             | Fast channel (max speed) | 66.5 | 68   | -   |      |

|                              |                         |                                                                                                  | Differential             | Slow channel (max speed) | 66.5 | 68   | -   |      |

| Table 70. ADC accuracy - limited test conditions $2^{(1)(2)(3)}$ | Table 70. ADC accurac | v - limited test conditions 2 <sup>(1)(</sup> | (2)(3) |

|------------------------------------------------------------------|-----------------------|-----------------------------------------------|--------|

|------------------------------------------------------------------|-----------------------|-----------------------------------------------|--------|

|             | Table 72. ADC accuracy - minicul test conditions 4. A.A. (continued) |                           |                          |                          |     |     |     |      |

|-------------|----------------------------------------------------------------------|---------------------------|--------------------------|--------------------------|-----|-----|-----|------|

| Sym-<br>bol | Parameter                                                            | Conditions <sup>(4)</sup> |                          |                          |     |     | Max | Unit |

|             | Total 26 MHz,<br>THD harmonic $1.65 V \le V_{DDA} = VREF + \le -$    | Single                    | Fast channel (max speed) | -                        | -71 | -69 |     |      |

| тно         |                                                                      | ended                     | Slow channel (max speed) | -                        | -71 | -69 | dB  |      |

|             |                                                                      | 22/1                      | Differential             | Fast channel (max speed) | -   | -73 | -72 | uВ   |

|             |                                                                      | Dillerential              | Slow channel (max speed) | -                        | -73 | -72 |     |      |

Table 72. ADC accuracy - limited test conditions  $4^{(1)(2)(3)}$  (continued)

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when  $V_{DDA} < 2.4 \text{ V}$  (BOOSTEN = 1 in the SYSCFG\_CFGR1 when  $V_{DDA} < 2.4 \text{ V}$ ). It is disable when  $V_{DDA} \ge 2.4 \text{ V}$ . No oversampling.

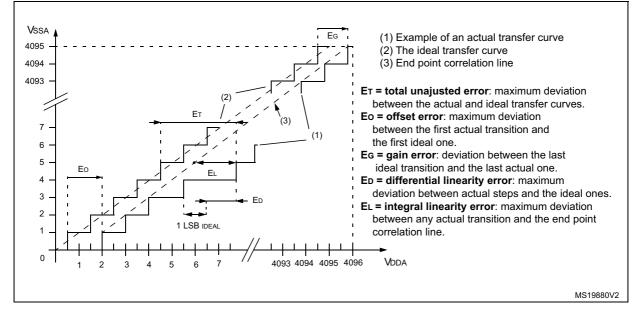

#### Figure 28. ADC accuracy characteristics

# 6.3.21 Comparator characteristics

| Symbol                         | Parameter                                                              | Conditions             |                          | Min                 | Тур  | Мах              | Unit |

|--------------------------------|------------------------------------------------------------------------|------------------------|--------------------------|---------------------|------|------------------|------|

| V <sub>DDA</sub>               | Analog supply voltage                                                  | -                      |                          | 1.62                | -    | 3.6              |      |

| V <sub>IN</sub>                | Comparator input voltage range                                         | -                      |                          | 0                   | -    | V <sub>DDA</sub> | V    |

| V <sub>BG</sub> <sup>(2)</sup> | Scaler input voltage                                                   |                        | -                        | V <sub>REFINT</sub> |      |                  |      |

| V <sub>SC</sub>                | Scaler offset voltage                                                  |                        | -                        | -                   | ±5   | ±10              | mV   |

|                                | Scaler static consumption                                              | BRG_EN=0 (br           | ridge disable)           | -                   | 200  | 300              | nA   |

| I <sub>DDA</sub> (SCALER)      | from V <sub>DDA</sub>                                                  | BRG_EN=1 (bi           | ridge enable)            | -                   | 0.8  | 1                | μA   |

| t <sub>START_SCALER</sub>      | Scaler startup time                                                    |                        | -                        | -                   | 100  | 200              | μs   |

|                                | Comparator startup time to<br>reach propagation delay<br>specification | High-speed             | V <sub>DDA</sub> ≥ 2.7 V | -                   | -    | 5                |      |

| t <sub>start</sub>             |                                                                        | mode                   | V <sub>DDA</sub> < 2.7 V | -                   | -    | 7                | μs   |

|                                |                                                                        | Medium mode            | V <sub>DDA</sub> ≥ 2.7 V | -                   | -    | 15               |      |

|                                |                                                                        |                        | V <sub>DDA</sub> < 2.7 V | -                   | -    | 25               |      |

|                                |                                                                        | Ultra-low-powe         | r mode                   | -                   | -    | 40               |      |

|                                | Propagation delay with<br>100 mV overdrive                             | High-speed             | V <sub>DDA</sub> ≥ 2.7 V | -                   | 55   | 80               | 20   |

| t <sub>D</sub> <sup>(3)</sup>  |                                                                        | mode                   | V <sub>DDA</sub> < 2.7 V | -                   | 65   | 100              | ns   |

| ۲D                             |                                                                        | Medium mode            |                          | -                   | 0.55 | 0.9              |      |

|                                |                                                                        | Ultra-low-power mode   |                          | -                   | 4    | 7                | μs   |

| V <sub>offset</sub>            | Comparator offset error                                                | Full common mode range | -                        | -                   | ±5   | ±20              | mV   |

|                                |                                                                        | No hysteresis          |                          | -                   | 0    | -                | - mV |

| M                              | Comparator hysteresis                                                  | Low hysteresis         |                          | -                   | 8    | -                |      |

| V <sub>hys</sub>               |                                                                        | Medium hyster          | -                        | 15                  | -    |                  |      |

|                                |                                                                        | High hysteresis        | -                        | 27                  | -    |                  |      |

# Table 76. COMP characteristics<sup>(1)</sup>

| Symbol                                    | Parameter                                                    | Conditions                                                   | Min  | Тур  | Max  | Unit |

|-------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------|------|------|------|

|                                           |                                                              | Slave mode 2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  | -    | 12.5 | 13.5 |      |

| <sup>I</sup> v(SO) Data output valid time | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 |                                                              | 12.5 | 24   | ns   |      |

|                                           |                                                              | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 2 | -    | 12.5 | 33   |      |

| t <sub>v(MO)</sub>                        |                                                              | Master mode                                                  | -    | 4.5  | 6    |      |

| t <sub>h(SO)</sub>                        | Data output hold time                                        | Slave mode                                                   | 7    | -    | -    | ns   |

| t <sub>h(MO)</sub>                        |                                                              | Master mode                                                  | 0    | -    | -    | 115  |

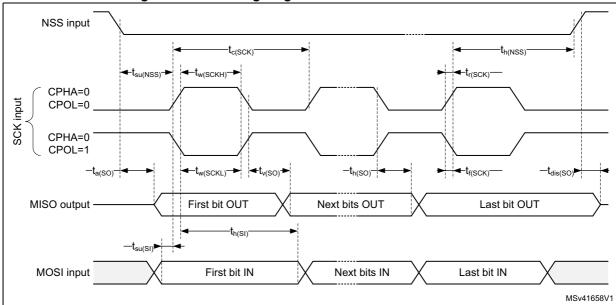

## Table 85. SPI characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

2. Maximum frequency in Slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty(SCK) = 50 %.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

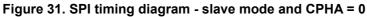

# 7.1 LQFP100 package information

Figure 40. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 91. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

| Symbol | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|-------|-----------------------|-----|--------|

| Symbol | Min         | Тур | Max   | Min                   | Тур | Мах    |

| А      | -           | -   | 1.600 | -                     | -   | 0.0630 |

| A1     | 0.050       | -   | 0.150 | 0.0020                | -   | 0.0059 |

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Apr-2017 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 05-May-2017 | 2        | <ul> <li>Updated some power consumptions on cover page.</li> <li>Added Table 4: STM32L451xx modes overview.</li> <li>Updated Table 35: Current consumption in Stop 2 mode.</li> <li>Updated Table 36: Current consumption in Stop 1 mode.</li> <li>Updated Table 38: Current consumption in Standby mode.</li> <li>Updated Table 67: ADC characteristics.</li> <li>Update note below Figure 29: Typical connection diagram using the ADC.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 26-May-2017 | 3        | <ul> <li>Added missing LPUART communication interface on cover page.</li> <li>Fixed OPAMP index in <i>Table 4: STM32L451xx modes overview</i>.</li> <li>Replaced RAM2 by SRAM2 in <i>Section 3.9.3: Voltage regulator</i> and <i>Section 3.9.4: Low-power modes</i>.</li> <li>Updated <i>Section 3.7: Boot modes</i>.</li> <li>Added <i>Table 10: DFSDM1 implementation</i>.</li> <li>Updated <i>Table 61: I/O static characteristics</i>.</li> <li>Updated <i>Section 7.2: UFBGA100 package information</i>.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 21-May-2018 | 4        | <ul> <li>Updated DAC terminology in all the document for clarification: single DAC instance (= DAC1) with 2 output channels.</li> <li>Added ECOPACK2® information in <i>Features</i>.</li> <li>Updated LPUART bullet in <i>Features</i>.</li> <li>Updated Section 3.9.1: Power supply schemes.</li> <li>Added Figure 3: Power-up/down sequence.</li> <li>Added DFSDM1 in <i>Table</i> 6: STM32L451xx peripherals interconnect matrix.</li> <li>Updated Clock-out capability in Section 3.11: Clocks and startup.</li> <li>Updated Figure 4: Clock tree.</li> <li>Updated Section 3.14.1: Nested vectored interrupt controller (NVIC).</li> <li>Removed a footnote in <i>Table</i> 16: STM32L451xx pin definitions.</li> <li>Updated Section 6.3.2: Operating conditions at power-up / power-down.</li> <li>Updated A<sub>Coeff</sub> in <i>Table</i> 26: Embedded internal voltage reference.</li> <li>Updated Table 41: Peripheral current consumption.</li> </ul> |