Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | LINbusSCI, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 15                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 256 x 8                                                              |

| RAM Size                   | 384 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | 20-50                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fl39f2mae |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

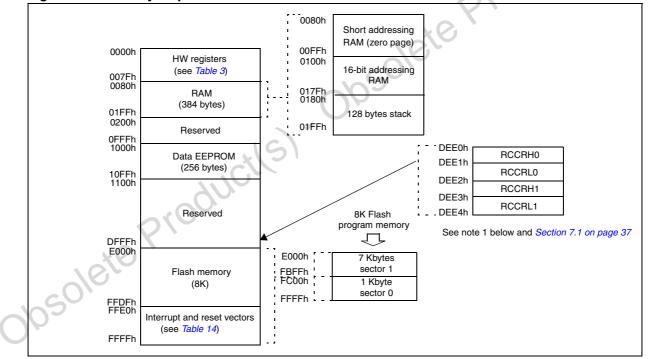

# 3 Register and memory map

As shown in Figure 4, the MCU can address 64 Kbytes of memories and I/O registers.

The available memory locations consist of 128 bytes of register locations, 384 bytes of RAM, 256 bytes of data EEPROM and up to 8 Kbytes of user program memory. The RAM space includes up to 128 bytes for the stack from 180h to 1FFh.

The highest address bytes contain the user reset and interrupt vectors.

The Flash memory contains two sectors (see *Figure 4*) mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

The size of Flash sector 0 and other device options are configurable by option byte (refer to *Section 15.2: Option bytes on page 215*).

Note: Memory locations marked as 'Reserved' must never be accessed. Accessing a reserved area can have unpredictable effects on the device.

#### Figure 4. Memory map

DEE0h, DEE1h, DEE2h and DEE3h addresses are located in a reserved area but are special bytes containing also the RC calibration values which are read-accessible only in user mode. If all the EEPROM data or Flash space (including the RC calibration values locations) has been erased (after the readout protection removal), then the RC calibration values can still be obtained through these four addresses.

## 5.4 Power saving modes

#### Wait mode

The data EEPROM can enter wait mode on execution of the WFI instruction of the microcontroller or when the microcontroller enters active halt mode. The data EEPROM immediately enters this mode if there is no programming in progress, otherwise the data EEPROM finishes the cycle and then enters wait mode.

### Active halt mode

Refer to wait mode.

#### Halt mode

The data EEPROM immediately enters halt mode if the microcontroller executes the HALT instruction. Therefore, the EEPROM stops the function in progress, and data may be corrupted.

# 5.5 Access error handling

If a read access occurs while E2LAT = 1, then the data bus is not driven.

If a write access occurs while E2LAT = 0, then the data on the bus is not latched.

If a programming cycle is interrupted (by reset action), the integrity of the data in memory is not guaranteed.

# 5.6 Data EEPROM readout protection

The readout protection is enabled through an option bit (see *Section 15.2: Option bytes on page 215*).

When this option is selected, the programs and data stored in the EEPROM memory are protected against readout (including a rewrite protection). In Flash devices, when this protection is removed by reprogramming the option byte, the entire program memory and EEPROM is first automatically erased.

Note:

Both program memory and data EEPROM are protected using the same option bit.

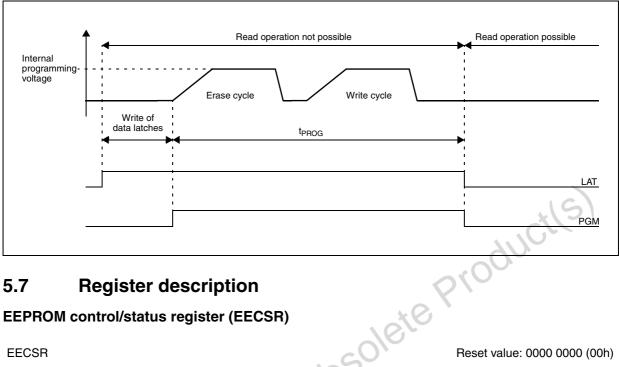

#### **Register description** 5.7

## EEPROM control/status register (EECSR)

| EECSR    |          |          |          | <u> </u> | F        | Reset value: 00 | 00 0000 (00h) |

|----------|----------|----------|----------|----------|----------|-----------------|---------------|

| 7        | 6        | 5        | 4        | 3        | 2        | 1               | 0             |

| Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | E2LAT           | E2PGM         |

| -        | -        | -        | -        | -        | -        | R/W             | R/W           |

#### Table 4. **EECSR register description**

|   | Bit | Bit name | Function                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|---|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|   | 7:2 | 50       | Reserved, forced by hardware to 0                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|   |     | E2LAT    | Latch access transfer<br>This bit is set by software. It is cleared by hardware at the end of the programming<br>cycle. It can only be cleared by software if the E2PGM bit is cleared.<br>0: Read mode<br>1: Write mode                                                                                                                                                                                  |  |  |  |  |  |

| 5 | 0   | E2PGM    | <ul> <li>Programming control and status</li> <li>This bit is set by software to begin the programming cycle. At the end of the programming cycle, this bit is cleared by hardware.</li> <li>0: Programming finished or not yet started</li> <li>1: Programming cycle is in progress</li> <li>Note: If the E2PGM bit is cleared during the programming cycle, the memory data is not guaranteed</li> </ul> |  |  |  |  |  |

#### Data EEPROM register map and reset values Table 5.

| Address (Hex.) | Register label       | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0          |

|----------------|----------------------|---|---|---|---|---|---|------------|------------|

| 0030h          | EECSR<br>Reset value | 0 | 0 | 0 | 0 | 0 | 0 | E2LAT<br>0 | E2PGM<br>0 |

| Bit | Bit name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4   | WDGRF    | Watchdog reset flag<br>This bit indicates that the last reset was generated by the watchdog<br>peripheral. It is set by hardware (watchdog reset) and cleared by<br>software (by reading SICSR register) or an LVD reset (to ensure a<br>stable cleared state of the WDGRF flag when CPU starts).<br>Combined with the LVDRF flag information, the flag description is<br>given as follows:<br>00 (LVDRF, WDGRF): Reset sources = External RESET pin<br>01 (LVDRF, WDGRF): Reset sources = Watchdog<br>1X (LVDRF, WDGRF): Reset sources = LVD |

| 3   | LOCKED   | <ul> <li>PLL locked flag</li> <li>This bit is set and cleared by hardware. It is set automatically when the PLL reaches its operating frequency.</li> <li>0: PLL not locked</li> <li>1: PLL locked</li> </ul>                                                                                                                                                                                                                                                                                                                                 |

| 2   | LVDRF    | LVD reset flag<br>This bit indicates that the last reset was generated by the LVD block.<br>It is set by hardware (LVD reset) and cleared by software (by<br>reading). When the LVD is disabled by option byte, the LVDRF bit<br>value is undefined.<br>Note: The LVDRF flag is not cleared when another reset type occurs<br>(external or watchdog), the LVDRF flag remains set to keep<br>trace of the original failure. In this case, a watchdog reset can<br>be detected by software while an external reset can not.                     |

| 1   | AVDF     | <ul> <li>Voltage detector flag</li> <li>This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit is set. Refer to <i>Figure 20</i> and to <i>Monitoring the VDD main supply on page 48</i> for additional details.</li> <li>0: V<sub>DD</sub> over AVD threshold</li> <li>1: V<sub>DD</sub> under AVD threshold</li> </ul>                                                                                                                                             |

| 0   | AVDIE    | <ul> <li>Voltage detector interrupt enable</li> <li>This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag is set. The pending interrupt information is automatically cleared when software enters the AVD interrupt routine.</li> <li>0: AVD interrupt disabled</li> <li>1: AVD interrupt enabled</li> </ul>                                                                                                                                                                                    |

Table 13. SICSR register description (continued)

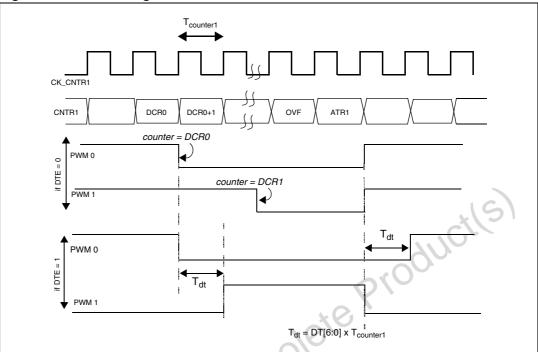

Figure 40. Dead time generation

In the above example, when the DTE bit is set:

- PWM goes low at DCR0 match and goes high at ATR1 + T<sub>dt</sub>

- PWM1 goes high at DCR0 + T<sub>dt</sub> and goes low at ATR match.

With this programmable delay ( $T_{dt}$ ), the PWM0 and PWM1 signals which are generated are not overlapped.

### **Break function**

The break function can be used to perform an emergency shutdown of the application being driven by the PWM signals.

The break function is activated by the external BREAK pin (active low). In order to use the break pin it must be previously enabled by software setting the BPEN bit in the BREAKCR register.

When a low level is detected on the break pin, the BA bit is set and the break function is activated. In this case, the four PWM signals are stopped.

Software can set the BA bit to activate the break function without using the break pin.

When a break function is activated (BA bit = 1 and BREN1/BREN2 = 1):

- The break pattern (PWM[3:0] bits in the BREAKCR is forced directly on the PWMx output pins (after the inverter)

- The 12-bit PWM counter CNTR1 is put to its reset value, that is, 00h

- The 12-bit PWM counter CNTR2 is put to its reset value, that is 00h

- ATR1, ATR2, preload and active DCRx are put to their reset values

- The PWMCR register is reset

- Counters stop counting

| Add<br>(Hex.) | Register<br>label       | 7         | 6         | 5         | 4         | 3          | 2          | 1         | 0         |  |  |  |

|---------------|-------------------------|-----------|-----------|-----------|-----------|------------|------------|-----------|-----------|--|--|--|

| 22            | BREAKCR<br>Reset value  | 0         | 0         | BA<br>0   | BPEN<br>0 | PWM3<br>0  | PWM2<br>0  | PWM1<br>0 | PWM0<br>0 |  |  |  |

| 23            | ATR2H<br>Reset value    | 0         | 0         | 0         | 0         | ATR11<br>0 | ATR10<br>0 | ATR9<br>0 | ATR8<br>0 |  |  |  |

| 24            | ATR2L<br>Reset value    | ATR7<br>0 | ATR6<br>0 | ATR5<br>0 | ATR4<br>0 | ATR3<br>0  | ATR2<br>0  | ATR1<br>0 | ATR0<br>0 |  |  |  |

| 25            | DTGR<br>Reset value     | DTE<br>0  | DT6<br>0  | DT5<br>0  | DT4<br>0  | DT3<br>0   | DT2<br>0   | DT1<br>0  | DT0<br>0  |  |  |  |

| 11.3          | 11.3 Lite timer 2 (LT2) |           |           |           |           |            |            |           |           |  |  |  |

| 11.3.1        | 11.3.1 Introduction     |           |           |           |           |            |            |           |           |  |  |  |

Table 47. Register map and reset values (continued)

#### 11.3 Lite timer 2 (LT2)

#### 11.3.1 Introduction

The lite timer is used for general-purpose timing functions. It is based on two free-running 8-bit upcounters and an 8-bit input capture register. sole

#### 11.3.2 Main features

- Real-time clock (RTC)

- One 8-bit upcounter 1 ms or 2 ms timebase period (@ 8 MHz f<sub>OSC</sub>) \_

- One 8-bit upcounter with autoreload and programmable timebase period from 4µs to 1.024ms \_ in 4µs increments (@ 8 MHz f<sub>OSC</sub>)

- 2 maskable timebase interrupts \_

- Input capture

- 8-bit input capture register (LTICR)

- ..ab Maskable interrupt with wakeup from halt mode capability

## 11.3.3 Functional description

#### **Timebase counter 1**

The 8-bit value of counter 1 cannot be read or written by software. After an MCU reset, it starts incrementing from 0 at a frequency of  $f_{OSC}/32$ . An overflow event occurs when the counter rolls over from F9h to 00h. If  $f_{OSC} = 8$  MHz, then the time period between two counter overflow events is 1 ms. This period can be doubled by setting the TB bit in the LTCSR1 register.

When counter 1 overflows, the TB1F bit is set by hardware and an interrupt request is generated if the TB1IE bit is set. The TB1F bit is cleared by software reading the LTCSR1 register.

#### **Timebase counter 2**

Counter 2 is an 8-bit autoreload upcounter. It can be read by accessing the LTCNTR register. After an MCU reset, it increments at a frequency of f<sub>OSC</sub>/32 starting from the value stored in the LTARR register. A counter overflow event occurs when the counter rolls over from FFh to the LTARR reload value. Software can write a new value at anytime in the LTARR register, this value will be automatically loaded in the counter when the next overflow occurs.

When counter 2 overflows, the TB2F bit in the LTCSR2 register is set by hardware and an interrupt request is generated if the TB2IE bit is set. The TB2F bit is cleared by software reading the LTCSR2 register.

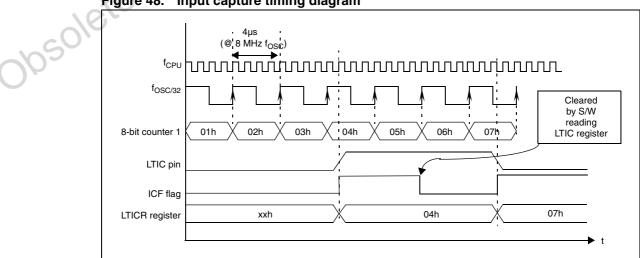

#### Input capture

The 8-bit input capture register is used to latch the free-running upcounter (counter 1) 1 after a rising or falling edge is detected on the LTIC pin. When an input capture occurs, the ICF bit is set and the LTICR register contains the value of counter 1. An interrupt is generated if the ICIE bit is set. The ICF bit is cleared by reading the LTICR register.

The LTICR is a read-only register and always contains the data from the last input capture. Input capture is inhibited if the ICF bit is set.

#### Figure 48. Input capture timing diagram

- Note: 1 While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

- 2 The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an overrun condition (see Overrun condition (OVR) on page 115).

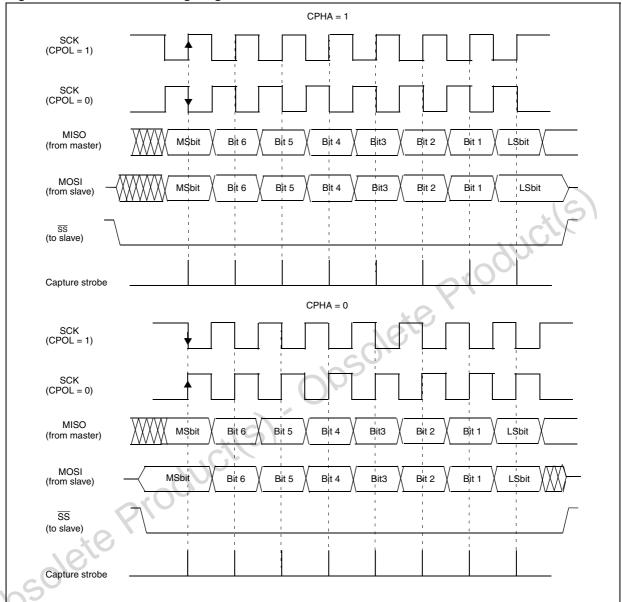

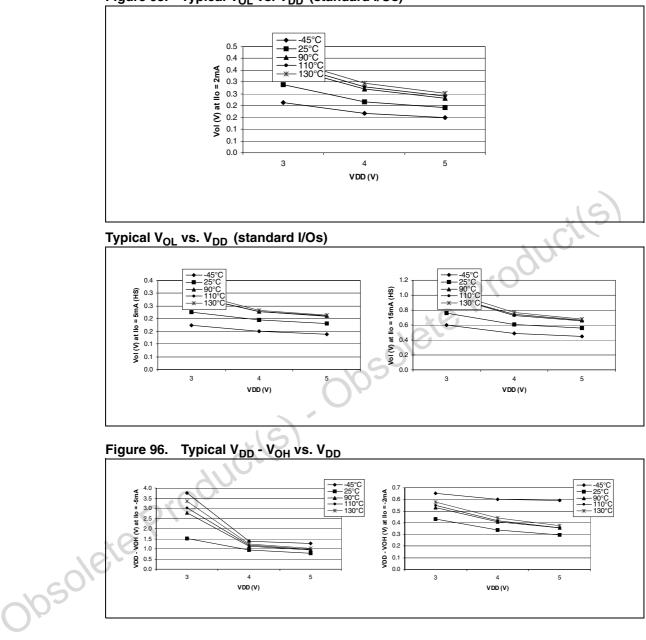

### 11.4.4 Clock phase and clock polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (see *Figure 53: Data clock timing diagram on page 114*).

Note: The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge.

*Figure 53: Data clock timing diagram on page 114* shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin and the MOSI pin are directly connected between the master and the slave device.

Note: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

#### Figure 53. Data clock timing diagram

This figure should not be used as a replacement for parametric information. Refer to Section 13: Electrical characteristics.

1.

| able ob. Shi register map and reset values |                       |           |           |           |           |           |           |           |           |  |

|--------------------------------------------|-----------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|

| Address (Hex.)                             | Register label        | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |  |

| 0031h                                      | SPIDR<br>Reset Value  | MSB<br>x  | x         | x         | x         | x         | x         | x         | LSB<br>x  |  |

| 0032h                                      | SPICR<br>Reset Value  | SPIE<br>0 | SPE<br>0  | SPR2<br>0 | MSTR<br>0 | CPOL<br>x | CPHA<br>x | SPR1<br>x | SPR0<br>x |  |

| 0033h                                      | SPICSR<br>Reset Value | SPIF<br>0 | WCOL<br>0 | OVR<br>0  | MODF<br>0 | 0         | SOD<br>0  | SSM<br>0  | SSI<br>0  |  |

Table 60.

SPI register map and reset values

# 11.5 LINSCI serial communication interface (LIN master/slave)

## 11.5.1 Introduction

The serial communications interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

The LIN-dedicated features support the LIN (local interconnect network) protocol for both master and slave nodes.

This chapter is divided into SCI Mode and LIN mode sections. For information on general SCI communications, refer to the SCI mode section. For LIN applications, refer to both the SCI mode and LIN mode sections.

Setting the RWU bit by software puts the SCI in sleep mode:

All the reception status bits cannot be set.

All the receive interrupts are inhibited.

A muted receiver may be woken up in one of the following ways:

- by idle line detection if the WAKE bit is reset,

- by address mark detection if the WAKE bit is set.

#### Idle line detection

The receiver wakes up by idle line detection when the receive line has recognized an idle line. Then the RWU bit is reset by hardware but the IDLE bit is not set.

This feature is useful in a multiprocessor system when the first characters of the message determine the address and when each message ends by an idle line: As soon as the line becomes idle, every receiver is awakened and the first characters of the message are analysed which indicates the addressed receiver. The receivers which are not addressed set the RWU bit to enter in mute mode. Consequently, they will not read the next characters constituting the next part of the message. At the end of the message, an idle line is sent by the transmitter: this wakes up every receiver which are ready to analyse the addressing characters of the new message.

In such a system, the inter-characters space must be smaller than the idle time.

#### Address mark detection

The receiver wakes up by address mark detection when it receives a '1' as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

This feature is useful in a multiprocessor system when the most significant bit of each character (except for the break character) is reserved for address detection. As soon as the receivers receive an address character (most significant bit = '1'), the receivers are woken up. The receivers which are not addressed set RWU bit to enter in mute mode. Consequently, they will not treat the next characters constituting the next part of the message.

## **Parity control**

Hardware byte parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the character format defined by the M bit, the possible SCI character formats are as listed in *Table 61*.

Note:

In case of wake-up by an address mark, the MSB bit of the data is taken into account and not the parity bit

| M bit | PCE bit | Character format           |

|-------|---------|----------------------------|

| 0     | 0       | SB   8 bit data   STB      |

| 0     | 1       | SB   7-bit data   PB   STB |

| 4     | 0       | SB   9-bit data   STB      |

| 1     | 1       | SB   8-bit data   PB   STB |

#### Table 61. Character formats<sup>(1)</sup>

1. Legend: SB = start bit, STB = stop bit, PB = parity bit

|        | Bit   | Bit name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 4     | IDLE     | Idle line detect<br>This bit is set by hardware when an idle line is detected. An interrupt<br>is generated if the ILIE = 1 in the SCICR2 register. It is cleared by a<br>software sequence (an access to the SCISR register followed by a<br>read to the SCIDR register).<br>0: No idle line is detected<br>1: Idle line is detected<br>Note: The IDLE bit is not set again until the RDRF bit is set (i.e. a new<br>idle line occurs).                                                                                                                                                                                                             |

|        | 3     | OR       | Overrun error<br>This bit is set by hardware when the word currently being received in<br>the shift register is ready to be transferred into the RDR register<br>while RDRF = 1. An interrupt is generated if RIE = 1 in the SCICR2<br>register. It is cleared by a software sequence (an access to the<br>SCISR register followed by a read to the SCIDR register).<br>0: No overrun error<br>1: Overrun error is detected<br>Note: When the IDLE bit is set the RDR register content is not lost but<br>the shift register is overwritten.                                                                                                         |

|        | 2     | NF       | <ul> <li>Noise flag</li> <li>This bit is set by hardware when noise is detected on a received character. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).</li> <li>0: No noise is detected</li> <li>1: Noise is detected</li> <li>Note: The NF bit does not generate an interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt.</li> </ul>                                                                                                                                                                                                     |

| Obsole | te Pr | FE       | <ul> <li>Framing error</li> <li>This bit is set by hardware when a de-synchronization, excessive noise or a break character is detected. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).</li> <li>0: No framing error is detected</li> <li>1: Framing error or break character is detected</li> <li>Note: The FE bit does not generate an interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt. If the word currently being transferred causes both frame error and overrun error, it is transferred and only the OR bit is set.</li> </ul> |

|        | 0     | PE       | Parity error<br>This bit is set by hardware when a parity error occurs (if the PCE bit<br>is set) in receiver mode. It is cleared by a software sequence (a read<br>to the status register followed by an access to the SCIDR data<br>register). An interrupt is generated if PIE = 1 in the SCICR1 register.<br>0: No parity error<br>1: Parity error                                                                                                                                                                                                                                                                                               |

Table 64. SCISR register description (continued)

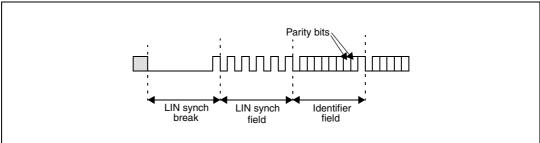

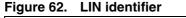

#### Figure 61. LIN header

The bits involved are the two MSB positions (7th and 8th bits if M = 0; 8th and 9th bits if M = 0) of the identifier character. The check is performed as specified in *Figure 62* by the LIN specification.

#### LIN error detection

#### LIN header error flag

The LIN header error flag indicates that an invalid LIN header has been detected.

When a LIN header error occurs:

- The LHE flag is set

- An interrupt is generated if the RIE bit is set and the I[1:0] bits are cleared in the CCR register.

If autosynchronization is enabled (LASE bit = 1), this can mean that the LIN synch field is corrupted, and that the SCI is in a blocked state (LSF bit is set). The only way to recover is to reset the LSF bit and then to clear the LHE bit.

• The LHE bit is reset by an access to the SCISR register followed by a read of the SCIDR register.

#### LHE/OVR error conditions

When auto resynchronization is disabled (LASE bit = 0), the LHE flag detects:

- That the received LIN synch field is not equal to 55h.

- That an overrun occurred (as in standard SCI mode)

- Furthermore, if LHDM is set it also detects that a LIN header reception timeout occurred (only if LHDM is set).

| lat | ole 70. | SCISR register description <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7   | TDRE    | <ul> <li>Transmit data register empty</li> <li>This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).</li> <li>0: Data is not transferred to the shift register</li> <li>1: Data is transferred to the shift register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6   | тс      | <ul> <li>Transmission complete</li> <li>This bit is set by hardware when transmission of a character containing data is complete. An interrupt is generated if TCIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).</li> <li>0: Transmission is not complete <ol> <li>1: Transmission is complete</li> </ol> </li> <li>Note: TC is not set after the transmission of a preamble or a break.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5   | RDRF    | Received data ready flag<br>This bit is set by hardware when the content of the RDR register has been transferred<br>to the SCIDR register. An interrupt is generated if RIE = 1 in the SCICR2 register. It is<br>cleared by a software sequence (an access to the SCISR register followed by a read<br>to the SCIDR register).<br>0: Data is not received<br>1: Received data are ready to be read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | IDLE    | Idle line detected<br>This bit is set by hardware when an idle line is detected. An interrupt is generated if<br>the ILIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to<br>the SCISR register followed by a read to the SCIDR register).<br>0: No idle line is detected<br>1: idle line is detected<br><i>Note: The IDLE bit is not set again until the RDRF bit has been set itself (that is, a new<br/>idle line occurs).</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3   | LHE     | <ul> <li>LIN header error</li> <li>During LIN header this bit signals three error types:</li> <li>The LIN synch field is corrupted and the SCI is blocked in LIN synch state (LSF bit = 1).</li> <li>A timeout occurred during LIN header reception.</li> <li>An overrun error was detected on one of the header field (see OR bit description in <i>Status register (SCISR) on page 134</i>).</li> <li>An interrupt is generated if RIE = 1 in the SCICR2 register. If blocked in the LIN synch state, the LSF bit must first be reset (to exit LIN synch field state and then to be able to clear LHE flag). Then it is cleared by the following software sequence: An access to the SCISR register followed by a read to the SCIDR register.</li> <li>0: No LIN header error</li> <li>1: LIN header error detected</li> <li>Note: Apart from the LIN header this bit signals an overrun error as in SCI mode, (see description in Status register (SCISR) on page 134).</li> </ul> |

Table 70.

SCISR register description<sup>(1)</sup>

- ...

| Table 103. | Operating cond | itions (tested for $T_A = -40$ to + | 125 °C) @ V <sub>DD</sub> = 3 | 3.0 to 3.6 V |  |

|------------|----------------|-------------------------------------|-------------------------------|--------------|--|

|            |                |                                     | Flash                         | BOM          |  |

| Symbol            | Parameter                               | Conditions                                                                                   | Flash |  |    | ROM |      |      |      |  |

|-------------------|-----------------------------------------|----------------------------------------------------------------------------------------------|-------|--|----|-----|------|------|------|--|

|                   | Falameter                               | Min. Typ. M                                                                                  |       |  |    |     | Тур. | Max. | Unit |  |

|                   | RC resolution                           | V <sub>DD</sub> = 3.3 V                                                                      | -1    |  | +1 | TBD |      | TBD  |      |  |

| ACC <sub>RC</sub> | Accuracy of internal RC oscillator with | $T_A = -40 \text{ to } +125 \text{ °C},$<br>$V_{DD} = 3.3 \text{ V}$                         | -3    |  | +5 | TBD |      | TBD  | %    |  |

|                   | $RCCR = RCCR0^{(2)(3)}$                 | $T_A = -40 \text{ to } +125 \text{ °C},$<br>$V_{DD} = 3.0 \text{ V to } 3.6 \text{ V}^{(4)}$ | -4    |  | +6 | TBD |      | TBD  |      |  |

1. If the RC oscillator clock is selected, to improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the  $V_{DD}$  and  $V_{SS}$  pins as close as possible to the ST7 device.

2. See Section 7.1: Internal RC oscillator adjustment on page 37.

3. Minimum value is obtained for hot temperature and max. value is obtained for cold temperature.

Data based on characterization results, not tested in production. 4.

# Table 104. Operating conditions (tested for $T_A = -40$ to +125 °C) @ $V_{DD} = 3.0$ to 3.6 V<sup>(1)</sup>

|                     | Parameter <sup>(1)</sup>          | Conditions                                      | Fla  |                    |                   |    |

|---------------------|-----------------------------------|-------------------------------------------------|------|--------------------|-------------------|----|

|                     |                                   | Conditions                                      | Min. | Тур.               | Max.              | ]  |

| I <sub>DD(RC)</sub> | RC oscillator current consumption | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.3 V |      | 500 <sup>(2)</sup> |                   | μA |

| t <sub>su(RC)</sub> | RC oscillator setup time          | $O_{\mathcal{V}}$                               |      |                    | 10 <sup>(2)</sup> | μs |

1. Data based on characterization results, not tested in production.

2. Measurement made with RC calibrated at 1 MHz.

# Figure 75. Typical accuracy with RCCR = RCCR1 vs. $V_{DD}$ = 3 to 3.6 V and

#### Figure 101. SPI master timing diagram

- 1. Measurement points are done at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}.$

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

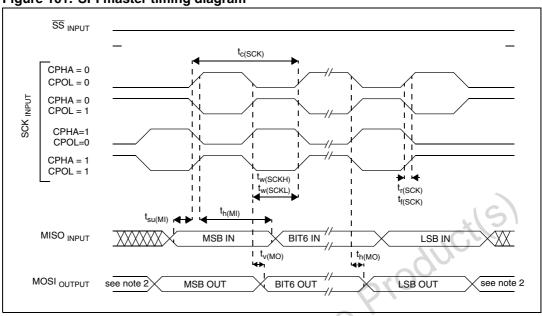

# 14 Package characteristics

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at www.st.com.

# 14.1 Package mechanical data

| Dim. |    | mm    |      |       | inches |       |       |  |

|------|----|-------|------|-------|--------|-------|-------|--|

|      |    | Min.  | Тур. | Max.  | Min.   | Тур.  | Max.  |  |

| 20   | A  | 2.35  |      | 2.65  | 0.093  |       | 0.104 |  |

| SO   | A1 | 0.10  |      | 0.30  | 0.004  |       | 0.012 |  |

| 00   | В  | 0.33  |      | 0.51  | 0.013  |       | 0.020 |  |

| U    | С  | 0.23  |      | 0.32  | 0.009  |       | 0.013 |  |

|      | D  | 12.60 |      | 13.00 | 0.496  |       | 0.512 |  |

|      | E  | 7.40  |      | 7.60  | 0.291  |       | 0.299 |  |

|      | е  |       | 1.27 |       |        | 0.050 |       |  |

|      | Н  | 10.00 |      | 10.65 | 0.394  |       | 0.419 |  |

|      | h  | 0.25  |      | 0.75  | 0.010  |       | 0.030 |  |

|      | α  | 0°    |      | 8°    | 0°     |       | 8°    |  |

|      | L  | 0.40  |      | 1.27  | 0.016  |       | 0.050 |  |

| Table 127. | 20-pin plastic small outline pa | ckage, 300-mil width, mechanical data |

|------------|---------------------------------|---------------------------------------|

|------------|---------------------------------|---------------------------------------|

| Example:                                | ST7                         | Ρ       | L34   | М   | А          | /xxx X | S  |

|-----------------------------------------|-----------------------------|---------|-------|-----|------------|--------|----|

| Product class                           |                             |         |       |     |            |        |    |

| ST7 microcontroller                     |                             |         |       |     |            |        |    |

| Family type                             |                             |         |       |     |            |        |    |

| P = FASTROM                             |                             |         |       |     |            |        |    |

| Sub-family type                         |                             |         |       |     |            |        |    |

| L34 = without data EEPROM, w            | ithout LIN                  |         |       |     |            |        |    |

| L35 = without data EEPROM, w            | ith LIN                     |         |       |     |            |        |    |

| L38 = with data EEPROM, without         | out LIN                     |         |       |     |            |        | 17 |

| L39 = with data EEPROM, with            | LIN                         |         |       |     |            | . KG   |    |

| Package type                            |                             |         |       |     |            | 96.    |    |

| M = SO                                  |                             |         |       | - 1 | $\bigcirc$ |        |    |

| U = QFN                                 |                             |         |       |     |            |        |    |

| Temperature range                       |                             | 4       | 0     |     |            |        |    |

| A = -40 °C to 85 °C                     |                             | 0       |       |     |            |        |    |

| A = -40 °C to 125 °C                    | CCC                         |         |       |     |            |        |    |

| <b>Code name</b>                        | ~03                         |         |       |     |            |        |    |

| Defined by                              | 05                          |         |       |     |            |        |    |

| STMicroelectronics.                     |                             |         |       |     |            |        |    |

| Denotes ROM code, pinout                |                             |         |       |     |            |        |    |

| and program memory size.                |                             |         |       |     |            |        |    |

| Tape and Reel conditioning or           | tions (loft blan            | . if Te | ov) — |     |            |        |    |

| TR or $R = Pin 1$ left-oriented         | blions (left blan           | K II II | ay)   |     |            |        |    |

| TX or $X = Pin 1$ right-oriented (E     | IA 481-C compli             | ant)    |       |     |            |        |    |

| ECOPACK/Fab code                        |                             |         |       |     |            |        |    |

| Blank or E = Lead-free ECOPAC           | CK <sup>®</sup> Phoenix Fal | C       |       |     |            |        |    |

| S = Lead-free ECOPACK <sup>®</sup> Cata | nia Fab                     |         |       |     |            |        |    |

#### Figure 108. ST7FL3x FASTROM commercial product structure

Obsole

# 15.4 Development tools

## 15.4.1 Starter Kits

ST offers complete, affordable **starter kits**. Starter kits are complete, affordable hardware/software tool packages that include features and samples to help you quickly start developing your application.

## **15.4.2** Development and debugging tools

Application development for ST7 is supported by fully optimizing C compilers and the ST7 assembler-linker toolchain, which are all seamlessly integrated in the ST7 integrated development environments in order to facilitate the debugging and fine-tuning of your application. The cosmic C compiler is available in a free version that outputs up to 16 Kbytes of code.

The range of hardware tools includes full featured ST7-EMU3 series emulators, cost effective ST7-DVP3 series emulators and the low-cost RLink in-circuit debugger/programmer. These tools are supported by the ST7 Toolset from STMicroelectronics, which includes the STVD7 integrated development environment (IDE) with high-level language debugger, editor, project manager and integrated programming interface.

## 15.4.3 **Programming tools**

During the development cycle, the ST7-DVP3 and ST7-EMU3 series emulators and the RLink provide in-circuit programming capability for programming the Flash microcontroller on your application board.

ST also provides a low-cost dedicated in-circuit programmer, the ST7-STICK, as well as ST7 socket boards which provide all the sockets required for programming any of the devices in a specific ST7 subfamily on a platform that can be used with any tool with in-circuit programming capability for ST7.

For production programming of ST7 devices, ST's third-party tool partners also provide a complete range of gang and automated programming solutions, which are ready to integrate into your production environment.