Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Supplier Device Package      | PG-TSSOP-16-8                              |

|------------------------------|--------------------------------------------|

| Mounting Type Package / Case | 16-TSSOP (0.173", 4.40mm Width)            |

| Operating Temperature        | -40°C ~ 85°C (TA)  Surface Mount           |

| Oscillator Type              | Internal                                   |

| Data Converters              | A/D 6x12b                                  |

| Voltage - Supply (Vcc/Vdd)   | 1.8V ~ 5.5V                                |

| RAM Size                     | 16K x 8                                    |

| EEPROM Size                  | -                                          |

| Program Memory Type          | FLASH                                      |

| Program Memory Size          | 8KB (8K x 8)                               |

| Number of I/O                | 11                                         |

| Peripherals                  | Brown-out Detect/Reset, I2S, POR, PWM, WDT |

| Connectivity                 | I <sup>2</sup> C, LINbus, SPI, UART/USART  |

| Speed                        | 32MHz                                      |

| Core Size                    | 32-Bit Single-Core                         |

| Core Processor               | ARM® Cortex®-M0                            |

| Product Status               | Obsolete                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2014-05

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2014 Infineon Technologies AG

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (<a href="https://www.infineon.com">www.infineon.com</a>).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# XMC1100

Microcontroller Series for Industrial Applications

XMC1000 Family

ARM<sup>®</sup> Cortex<sup>™</sup>-M0 32-bit processor core

Data Sheet V1.4 2014-05

Microcontrollers

#### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4                                                                                                                                                             | Summary of Features Ordering Information Device Types Device Type Features Chip Identification Number  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8<br>9<br>10                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2<br>2.2.1<br>2.2.2                                                                                                                                                         | General Device Information1Logic Symbols1Pin Configuration and Definition1Package Pin Summary1Port I/O Functions2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12<br>14<br>17                                                                               |

| 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.7.1<br>3.3.7.2<br>3.3.7.3 | Electrical Parameter2General Parameters2Parameter Interpretation2Absolute Maximum Ratings2Operating Conditions2DC Parameters2Input/Output Characteristics2Analog to Digital Converters (ADC)2Temperature Sensor Characteristics3Power Supply Current3Flash Memory Parameters3AC Parameters3Testing Waveforms3Output Rise/Fall Times3Power-Up and Supply Threshold Charcteristics3On-Chip Oscillator Characteristics3Serial Wire Debug Port (SW-DP) Timing4SPD Timing Requirements4Peripheral Timings4Synchronous Serial Interface (USIC SSC) Timing4Inter-IC (IIC) Interface Timing4Inter-IC Sound (IIS) Interface Timing5 | 23<br>24<br>25<br>26<br>26<br>29<br>33<br>34<br>36<br>37<br>38<br>41<br>43<br>44<br>45<br>45 |

| <b>4</b><br>4.1<br>4.1.1<br>4.2                                                                                                                                                                  | Package and Reliability5Package Parameters5Thermal Considerations5Package Outlines5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52<br>52<br>54                                                                               |

| 5                                                                                                                                                                                                | Quality Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58                                                                                           |

**About this Document**

#### **About this Document**

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC1100 series devices.

The document describes the characteristics of a superset of the XMC1100 series devices. For simplicity, the various device types are referred to by the collective term XMC1100 throughout this document.

#### XMC1000 Family User Documentation

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by **Users Guides** and **Application Notes**.

Please refer to <a href="http://www.infineon.com/xmc1000">http://www.infineon.com/xmc1000</a> to get access to the latest versions of those documents.

#### **Summary of Features**

- High code density with 32-bit performance

- Single cycle 32-bit hardware multiplier

- System timer (SysTick) for Operating System support

- Ultra low power consumption

- Nested Vectored Interrupt Controller (NVIC)

- Event Request Unit (ERU) for programmable processing of external and internal service requests

#### **On-Chip Memories**

- 8 kbytes on-chip ROM

- 16 kbytes on-chip high-speed SRAM

- up to 64 kbytes on-chip Flash program and data memory

#### **On-Chip Peripherals**

- Two Universal Serial Interface Channels (USIC), usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

- A/D Converters, up to 12 channels, includes a 12-bit analog to digital converter

- Capture/Compare Units 4 (CCU4) for use as general purpose timers

- · Window Watchdog Timer (WDT) for safety sensitive applications

- Real Time Clock module with alarm support (RTC)

- System Control Unit (SCU) for system configuration and control

- Pseudo random number generator (PRNG), provides random data with fast generation times

- Temperature Sensor (TSE)

#### Input/Output Lines

- Programmable port driver control module (PORTS)

- Individual bit addressability

- · Tri-stated in input mode

- Push/pull or open drain output mode

- · Configurable pad hysteresis

#### **On-Chip Debug Support**

- Support for debug features: 4 breakpoints, 2 watchpoints

- Various interfaces: ARM serial wire debug (SWD), single pin debug (SPD)

# 1.1 Ordering Information

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. The code "XMC1<DDD>-<Z><PPP><T><FFFF>" identifies:

<DDD> the derivatives function set

#### **Summary of Features**

Table 1 Synopsis of XMC1100 Device Types (cont'd)

| Derivative        | Package       | Flash<br>Kbytes | SRAM<br>Kbytes |

|-------------------|---------------|-----------------|----------------|

| XMC1100-Q040F0032 | PG-VQFN-40-13 | 32              | 16             |

| XMC1100-Q040F0064 | PG-VQFN-40-13 | 64              | 16             |

#### 1.3 Device Type Features

The following table lists the available features per device type.

Table 2 Features of XMC1100 Device Types<sup>1)</sup>

| Derivative   | ADC channel |

|--------------|-------------|

| XMC1100-T016 | 6           |

| XMC1100-T038 | 12          |

| XMC1100-Q024 | 8           |

| XMC1100-Q040 | 12          |

<sup>1)</sup> Features that are not included in this table are available in all the derivatives

Table 3 ADC Channels

| Package     | VADC0 G0 | VADC0 G1     |

|-------------|----------|--------------|

| PG-TSSOP-16 | CH0CH5   | _            |

| PG-TSSOP-38 | CH0CH7   | CH1, CH5 CH7 |

| PG-VQFN-24  | CH0CH7   | _            |

| PG-VQFN-40  | CH0CH7   | CH1, CH5 CH7 |

## 1.4 Chip Identification Number

The Chip Identification Number allows software to identify the marking. It is a 8 words value with the most significant 7 words stored in Flash configuration sector 0 (CS0) at address location:  $1000~0F00_H~(MSB)$  -  $1000~0F1B_H~(LSB)$ . The least significant word and most significant word of the Chip Identification Number are the value of registers DBGROMID and IDCHIP, respectively.

# 2.2 Pin Configuration and Definition

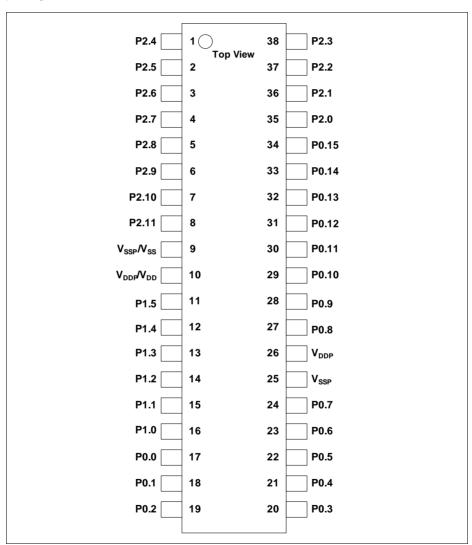

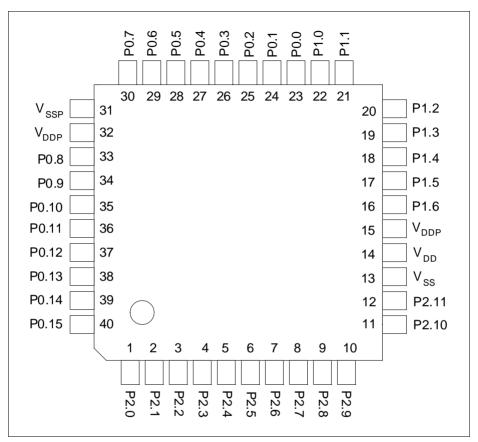

The following figures summarize all pins, showing their locations on the different packages.

Figure 4 XMC1100 PG-TSSOP-38 Pin Configuration (top view)

Subject to Agreement on the Use of Product Information

Figure 7 XMC1100 PG-VQFN-40 Pin Configuration (top view)

Subject to Agreement on the Use of Product Information

### 2.2.1 Package Pin Summary

The following general building block is used to describe each pin:

Table 5 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad Type |

|----------|-----------|-----------|--------------|

| Px.y     | N         | N         | Pad Class    |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type:

- STD\_INOUT (standard bi-directional pads)

- STD\_INOUT/AN (standard bi-directional pads with analog input)

- High Current (high current bi-directional pads)

- STD\_IN/AN (standard input pads with analog input)

- Power (power supply)

Details about the pad properties are defined in the Electrical Parameters.

Table 6 Package Pin Mapping

| Function | VQFN<br>40 | TSSOP<br>38 | VQFN<br>24 | TSSOP<br>16 | Pad Type  | Notes |

|----------|------------|-------------|------------|-------------|-----------|-------|

| P0.0     | 23         | 17          | 15         | 7           | STD_INOUT |       |

| P0.1     | 24         | 18          | -          | -           | STD_INOUT |       |

| P0.2     | 25         | 19          | -          | -           | STD_INOUT |       |

| P0.3     | 26         | 20          | -          | -           | STD_INOUT |       |

| P0.4     | 27         | 21          | -          | -           | STD_INOUT |       |

| P0.5     | 28         | 22          | 16         | 8           | STD_INOUT |       |

| P0.6     | 29         | 23          | 17         | 9           | STD_INOUT |       |

| P0.7     | 30         | 24          | 18         | 10          | STD_INOUT |       |

| P0.8     | 33         | 27          | 19         | 11          | STD_INOUT |       |

| P0.9     | 34         | 28          | 20         | 12          | STD_INOUT |       |

| P0.10    | 35         | 29          | -          | -           | STD_INOUT |       |

| P0.11    | 36         | 30          | -          | -           | STD_INOUT |       |

| P0.12    | 37         | 31          | 21         | -           | STD_INOUT |       |

Table 6 Package Pin Mapping

| Function | VQFN<br>40  | TSSOP<br>38 | VQFN<br>24  | TSSOP<br>16 | Pad Type | Notes                                                                                                                                                                                                                                |

|----------|-------------|-------------|-------------|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDP     | 15          | 10          | 10          | 6           | Power    | I/O port supply                                                                                                                                                                                                                      |

| VSSP     | 31          | 25          | -           | -           | Power    | I/O port ground                                                                                                                                                                                                                      |

| VDDP     | 32          | 26          | -           | -           | Power    | I/O port supply                                                                                                                                                                                                                      |

| VSSP     | Exp.<br>Pad | -           | Exp.<br>Pad | -           | Power    | Exposed Die Pad The exposed die pad is connected internally to VSSP. For proper operation, it is mandatory to connect the exposed pad to the board ground. For thermal aspects, please refer to the Package and Reliability chapter. |

# 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Table 9 Absolute Maximum Rating Parameters

| Parameter                                                     | Symbol               |    |      | Va   | lues                          | Unit | Note /             |  |

|---------------------------------------------------------------|----------------------|----|------|------|-------------------------------|------|--------------------|--|

|                                                               |                      |    | Min. | Тур. | Max.                          |      | Test Cond ition    |  |

| Junction temperature                                          | $T_{J}$              | SR | -40  | _    | 115                           | °C   | _                  |  |

| Storage temperature                                           | $T_{S}$              | SR | -40  | _    | 125                           | °C   | _                  |  |

| Voltage on power supply pin with respect to $V_{\rm SSP}$     | $V_{DDP}$            | SR | -0.3 | _    | 6                             | V    | -                  |  |

| Voltage on any pin with respect to $V_{\rm SSP}$              | $V_{IN}$             | SR | -0.5 | _    | $V_{\rm DDP}$ + 0.5 or max. 6 | V    | whichever is lower |  |

| Voltage on any analog input pin with respect to $V_{\rm SSP}$ | $V_{AIN} \ V_{AREF}$ | SR | -0.5 | _    | $V_{\rm DDP}$ + 0.5 or max. 6 | V    | _                  |  |

| Input current on any pin during overload condition            | $I_{IN}$             | SR | -10  | _    | 10                            | mA   | -                  |  |

| Absolute sum of all input currents during overload condition  | $\Sigma  I_{IN} $    | SR | _    | _    | 50                            | mA   | -                  |  |

| Analog comparator input voltage                               | $V_{CM}$             | SR | -0.3 | _    | $V_{\rm DDP}$ + 0.3           | V    |                    |  |

Table 11 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                                                                                           | Symbol            |    | Limit Values                |                              | Unit | Test Conditions                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----|-----------------------------|------------------------------|------|-----------------------------------------------------------------------|

|                                                                                                                                                     |                   |    | Min.                        | Max.                         |      |                                                                       |

| Input high voltage on port pins (Large Hysteresis)                                                                                                  | $V_{IHPL}$        | SR | $0.85 \times V_{DDP}$       | -                            | V    | CMOS Mode<br>(5 V, 3.3 V & 2.2 V) <sup>3)</sup>                       |

| Input Hysteresis <sup>1)</sup>                                                                                                                      | HYS               | CC | $0.08 	imes V_{ m DDP}$     | _                            | V    | CMOS Mode (5 V),<br>Standard Hysteresis                               |

|                                                                                                                                                     |                   |    | $V_{\text{DDP}}$            | _                            | V    | CMOS Mode (3.3 V),<br>Standard Hysteresis                             |

|                                                                                                                                                     |                   |    | $V_{ m DDP}$                | _                            | V    | CMOS Mode (2.2 V),<br>Standard Hysteresis                             |

|                                                                                                                                                     |                   |    | $0.5 	imes V_{	extsf{DDP}}$ | $0.75 \times \\ V_{\rm DDP}$ | V    | CMOS Mode(5 V),<br>Large Hysteresis                                   |

|                                                                                                                                                     |                   |    | $0.4 	imes V_{	extsf{DDP}}$ | $0.75 \times \\ V_{\rm DDP}$ | V    | CMOS Mode(3.3 V),<br>Large Hysteresis                                 |

|                                                                                                                                                     |                   |    | $V_{	extsf{DDP}}$           | $0.65 \times \\ V_{\rm DDP}$ | V    | CMOS Mode(2.2 V),<br>Large Hysteresis                                 |

| Pull-up resistor on port pins                                                                                                                       | $R_{PUP}$         | CC | 20                          | 50                           | kohm | $V_{IN} = V_{SSP}$                                                    |

| Pull-down resistor on port pins                                                                                                                     | $R_{PDP}$         | CC | 20                          | 50                           | kohm | $V_{IN} = V_{DDP}$                                                    |

| Input leakage current <sup>2)</sup>                                                                                                                 | $I_{OZP}$         | CC | -1                          | 1                            | μА   | $0 < V_{\rm IN} < V_{\rm DDP}, \\ T_{\rm A} \leq 105~{\rm ^{\circ}C}$ |

| Overload current on any pin                                                                                                                         | $I_{OVP}$         | SR | -5                          | 5                            | mA   |                                                                       |

| Absolute sum of overload currents                                                                                                                   | $\Sigma  I_{OV} $ | SR | _                           | 25                           | mA   | 3)                                                                    |

| Voltage on any pin during $V_{\mathrm{DDP}}$ power off                                                                                              | $V_{PO}$          | SR | _                           | 0.3                          | V    | 4)                                                                    |

| $\label{eq:maximum} \begin{array}{l} \text{Maximum current per} \\ \text{pin (excluding P1, $V_{\rm DDP}$} \\ \text{and $V_{\rm SS}$)} \end{array}$ | $I_{MP}$          | SR | -10                         | 11                           | mA   | _                                                                     |

| Maximum current per high currrent pins                                                                                                              | $I_{MP1A}$        | SR | -10                         | 50                           | mA   | _                                                                     |

# 3.2.5 Flash Memory Parameters

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 16 Flash Memory Parameters

| Parameter              | Symbol                  |      | Value | S                 | Unit   | Note /                          |

|------------------------|-------------------------|------|-------|-------------------|--------|---------------------------------|

|                        |                         | Min. | Тур.  | Max.              |        | Test Condition                  |

| Erase Time per page    | t <sub>ERASE</sub> CC   | 6.8  | 7.1   | 7.6               | ms     |                                 |

| Program time per block | t <sub>PSER</sub> CC    | 102  | 152   | 204               | μS     |                                 |

| Wake-Up time           | t <sub>WU</sub> CC      | _    | 32.2  | -                 | μS     |                                 |

| Read time per word     | t <sub>a</sub> CC       | _    | 50    | -                 | ns     |                                 |

| Data Retention Time    | t <sub>RET</sub> CC     | 10   | _     | _                 | years  | Max. 100 erase / program cycles |

| Flash Wait States 1)   | N <sub>WSFLASH</sub> CC | 0    | 0.5   | -                 |        | $f_{\rm MCLK} = 8  \rm MHz$     |

|                        |                         | 0    | 1.4   | -                 |        | $f_{\rm MCLK} = 16 \ \rm MHz$   |

|                        |                         | 1    | 1.9   | -                 |        | $f_{\rm MCLK} = 32 \ \rm MHz$   |

| Erase Cycles per page  | $N_{ECYC}$ CC           | _    | _     | 5*10 <sup>4</sup> | cycles |                                 |

| Total Erase Cycles     | N <sub>TECYC</sub> CC   | _    | _     | 2*10 <sup>6</sup> | cycles |                                 |

<sup>1)</sup> Flash wait states are automatically inserted by the Flash module during memory read when needed. Typical values are calculated from the execution of the Dhrystone benchmark program.

### 3.3.2 Output Rise/Fall Times

**Table 17** provides the characteristics of the output rise/fall times in the XMC1100. **Figure 9** describes the rise time and fall time parameters.

Table 17 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                                              | Symbol        | Limit | Values | Unit | Test Conditions               |

|--------------------------------------------------------|---------------|-------|--------|------|-------------------------------|

|                                                        |               | Min.  | Max.   |      |                               |

| Rise/fall times on High<br>Current Pad <sup>1)2)</sup> | $t_{HCPR},$   | _     | 9      | ns   | 50 pF @ 5 V <sup>3)</sup>     |

|                                                        | $t_{HCPF}$    | _     | 12     | ns   | 50 pF @ 3.3 V <sup>4)</sup>   |

|                                                        |               | _     | 25     | ns   | 50 pF @ 1.8 V <sup>5)</sup>   |

| Rise/fall times on                                     | $t_{R},t_{F}$ | _     | 12     | ns   | 50 pF @ 5 V <sup>6)</sup>     |

| Standard Pad <sup>1)2)</sup>                           |               | _     | 15     | ns   | 50 pF @ 3.3 V <sup>7)</sup> . |

|                                                        |               | _     | 31     | ns   | 50 pF @ 1.8 V <sup>8)</sup> . |

<sup>1)</sup> Rise/Fall time parameters are taken with 10% - 90% of supply.

<sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterisation and test correlation.

<sup>3)</sup> Additional rise/fall time valid for  $C_L = 50 \text{ pF} - C_L = 100 \text{ pF} @ 0.150 \text{ ns/pF}$  at 5 V supply voltage.

<sup>4)</sup> Additional rise/fall time valid for  $C_L = 50 \text{ pF} - C_L = 100 \text{ pF} @ 0.205 \text{ ns/pF}$  at 3.3 V supply voltage.

<sup>5)</sup> Additional rise/fall time valid for C<sub>1</sub> = 50 pF - C<sub>1</sub> = 100 pF @ 0.445 ns/pF at 1.8 V supply voltage.

<sup>6)</sup> Additional rise/fall time valid for  $C_L = 50 \text{ pF} - C_L = 100 \text{ pF} @ 0.225 \text{ ns/pF}$  at 5 V supply voltage.

<sup>7)</sup> Additional rise/fall time valid for C<sub>L</sub> = 50 pF - C<sub>L</sub> = 100 pF @ 0.288 ns/pF at 3.3 V supply voltage.

<sup>8)</sup> Additional rise/fall time valid for C<sub>L</sub> = 50 pF - C<sub>L</sub> = 100 pF @ 0.588 ns/pF at 1.8 V supply voltage.

- 3) Valid for a 100 nF buffer capacitor connected to supply pin where current from capacitor is forwarded only to the chip. A larger capacitor value has to be chosen if the power source sink a current.

- 4) This values does not include the ramp-up time. During startup firmware execution, MCLK is running at 32 MHz and the clocks to peripheral as specified in register CGATSTATO are gated.

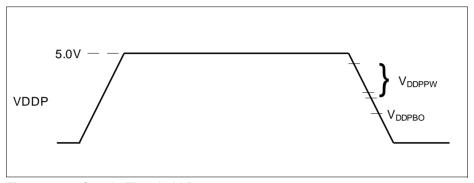

Figure 12 Supply Threshold Parameters

Table 24 USIC SSC Slave Mode Timing (cont'd)

| Parameter                                                                           | Symbol          |    | Values |      |      | Unit | Note /         |

|-------------------------------------------------------------------------------------|-----------------|----|--------|------|------|------|----------------|

|                                                                                     |                 |    | Min.   | Тур. | Max. |      | Test Condition |

| Receive data input DX0/DX[5:3] setup time to shift clock receive edge <sup>1)</sup> | t <sub>12</sub> | SR | 10     | _    | _    | ns   |                |

| Data input DX0/DX[5:3] hold time from clock input DX1 receive edge <sup>1)</sup>    | t <sub>13</sub> | SR | 10     | _    | -    | ns   |                |

| Data output DOUT[3:0] valid time                                                    | t <sub>14</sub> | СС | -      | _    | 80   | ns   |                |

<sup>1)</sup> These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

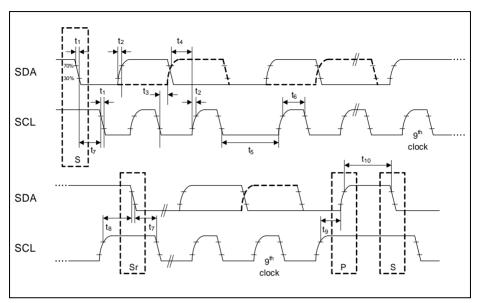

Figure 16 USIC IIC Stand and Fast Mode Timing

## 3.3.7.3 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode.  $\label{eq:using_parameters}$

Note: Operating Conditions apply.

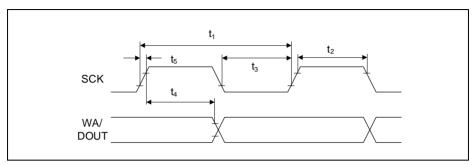

Table 27 USIC IIS Master Transmitter Timing

| Parameter       | Symbol            |              | Values |            | Unit | Note /<br>Test Condition |

|-----------------|-------------------|--------------|--------|------------|------|--------------------------|

|                 |                   | Min.         | Тур.   | Max.       |      |                          |

| Clock period    | t <sub>1</sub> CC | $2/f_{MCLK}$ | -      | -          | ns   | $V_{DDP} \geq 3\;V$      |

|                 |                   | $4/f_{MCLK}$ | -      | -          | ns   | $V_{DDP}\!<\!3\;V$       |

| Clock HIGH      | t <sub>2</sub> CC | 0.35 x       | -      | -          | ns   |                          |

|                 |                   | $t_{1min}$   |        |            |      |                          |

| Clock Low       | t <sub>3</sub> CC | 0.35 x       | -      | -          | ns   |                          |

|                 |                   | $t_{1min}$   |        |            |      |                          |

| Hold time       | t <sub>4</sub> CC | 0            | -      | -          | ns   |                          |

| Clock rise time | t <sub>5</sub> CC | -            | -      | 0.15 x     | ns   |                          |

|                 |                   |              |        | $t_{1min}$ |      |                          |

Figure 17 USIC IIS Master Transmitter Timing

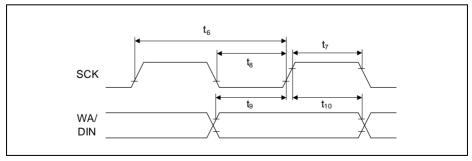

Table 28 USIC IIS Slave Receiver Timing

| Parameter    | Symbol             |                             | Values | i    | Unit | Note /<br>Test Condition |

|--------------|--------------------|-----------------------------|--------|------|------|--------------------------|

|              |                    | Min.                        | Тур.   | Max. |      |                          |

| Clock period | t <sub>6</sub> SR  | $4/f_{MCLK}$                | -      | -    | ns   |                          |

| Clock HIGH   | t <sub>7</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -      | -    | ns   |                          |

| Clock Low    | t <sub>8</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -      | -    | ns   |                          |

| Set-up time  | t <sub>9</sub> SR  | 0.2 x t <sub>6min</sub>     | -      | -    | ns   |                          |

| Hold time    | t <sub>10</sub> SR | 10                          | -      | -    | ns   |                          |

Figure 18 USIC IIS Slave Receiver Timing

### Package and Reliability

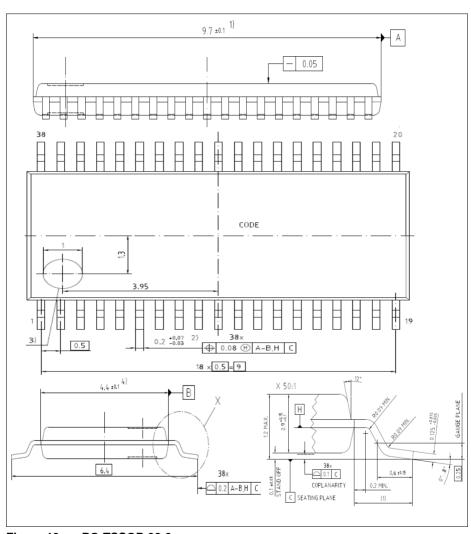

# 4.2 Package Outlines

Figure 19 PG-TSSOP-38-9

**Quality Declaration**

# 5 Quality Declaration

Table 30 shows the characteristics of the quality parameters in the XMC1100.

Table 30 Quality Parameters

| Parameter                                                             | Symbol                 | Limit Val | ues  | Unit | Notes                                  |

|-----------------------------------------------------------------------|------------------------|-----------|------|------|----------------------------------------|

|                                                                       |                        | Min.      | Max. |      |                                        |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub><br>SR | -         | 2000 | V    | Conforming to<br>EIA/JESD22-<br>A114-B |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | $V_{CDM}$ SR           | -         | 500  | V    | Conforming to JESD22-C101-C            |

| Moisture sensitivity level                                            | MSL<br>CC              | -         | 3    | -    | JEDEC<br>J-STD-020C                    |