Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Detalls                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 32MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 11                                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                        |

| Data Converters            | A/D 6x12b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                                    |

| Supplier Device Package    | PG-TSSOP-16-8                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc1100t016f0064aaxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## XMC1100 Data Sheet

## Revision History: V1.4 2014-05

| Previous V | ersion: V1.3                                                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Page       | Subjects                                                                                                                                  |

| Page 10    | ADC channels of Table 2 is updated. Table 3 is added.                                                                                     |

| Page 10    | Description for Chip Identification Number of Section 1.4 is updated.                                                                     |

| Page 17    | The pad type is corrected for P1.6 in Table 6.                                                                                            |

| Page 29    | The $t_{C12}$ , $f_{C12}$ , $t_{C10}$ , $f_{C10}$ , $t_{C8}$ and $f_{C8}$ parameters are updated in Table 12.                             |

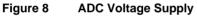

| Page 32    | Figure 8 is added.                                                                                                                        |

| Page 33    | The $t_{SR}$ and $t_{TSAL}$ parameters are updated in Table 13.                                                                           |

| Page 36    | Parameter name for $t_{\rm PSER}$ is updated. The $N_{\rm WSFLASH}$ parameter and test condition for $t_{\rm RET}$ are added to Table 16. |

| Page 39    | The min value for $V_{\rm DDPBO}$ parameter is added to Table 18. Footnote 1 is updated.                                                  |

| Page 41    | The $\Delta f_{LTT}$ parameter is added to Table 19.                                                                                      |

| Page 47    | Figure 13 is added.                                                                                                                       |

## Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

ARM<sup>®</sup>, ARM Powered<sup>®</sup> and AMBA<sup>®</sup> are registered trademarks of ARM, Limited.

Cortex<sup>™</sup>, CoreSight<sup>™</sup>, ETM<sup>™</sup>, Embedded Trace Macrocell<sup>™</sup> and Embedded Trace Buffer<sup>™</sup> are trademarks of ARM, Limited.

## We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

#### About this Document

# About this Document

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC1100 series devices.

The document describes the characteristics of a superset of the XMC1100 series devices. For simplicity, the various device types are referred to by the collective term XMC1100 throughout this document.

## **XMC1000 Family User Documentation**

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

# Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by Users Guides and Application Notes.

Please refer to http://www.infineon.com/xmc1000 to get access to the latest versions of those documents.

## **Summary of Features**

## 1 Summary of Features

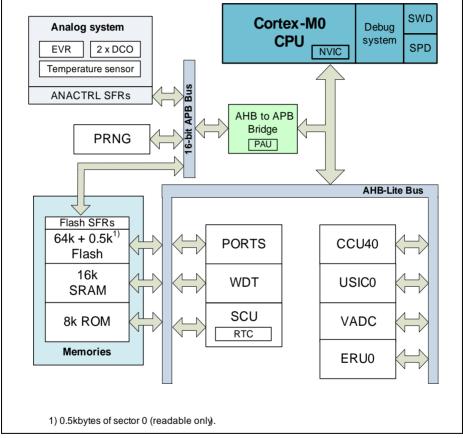

The XMC1100 devices are members of the XMC1000 family of microcontrollers based on the ARM Cortex-M0 processor core. The XMC1100 series devices are designed for general purpose applications.

## **CPU Subsystem**

- CPU Core

- High Performance 32-bit ARM Cortex-M0 CPU

- Most of 16-bit Thumb instruction set

- Subset of 32-bit Thumb2 instruction set

#### Summary of Features

- High code density with 32-bit performance

- Single cycle 32-bit hardware multiplier

- System timer (SysTick) for Operating System support

- Ultra low power consumption

- Nested Vectored Interrupt Controller (NVIC)

- Event Request Unit (ERU) for programmable processing of external and internal service requests

## **On-Chip Memories**

- 8 kbytes on-chip ROM

- 16 kbytes on-chip high-speed SRAM

- up to 64 kbytes on-chip Flash program and data memory

## **On-Chip Peripherals**

- Two Universal Serial Interface Channels (USIC), usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

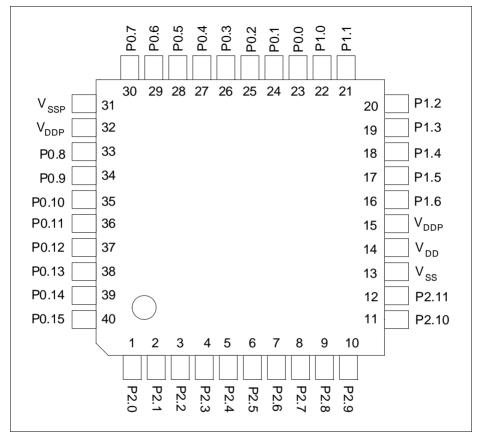

- A/D Converters, up to 12 channels, includes a 12-bit analog to digital converter

- Capture/Compare Units 4 (CCU4) for use as general purpose timers

- Window Watchdog Timer (WDT) for safety sensitive applications

- Real Time Clock module with alarm support (RTC)

- System Control Unit (SCU) for system configuration and control

- Pseudo random number generator (PRNG), provides random data with fast generation times

- Temperature Sensor (TSE)

## Input/Output Lines

- Programmable port driver control module (PORTS)

- Individual bit addressability

- Tri-stated in input mode

- Push/pull or open drain output mode

- Configurable pad hysteresis

## **On-Chip Debug Support**

- Support for debug features: 4 breakpoints, 2 watchpoints

- Various interfaces: ARM serial wire debug (SWD), single pin debug (SPD)

## 1.1 Ordering Information

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. The code "XMC1<DDD>-<Z><PPP><T><FFFF>" identifies:

<DDD> the derivatives function set

## XMC1100 XMC1000 Family

## **General Device Information**

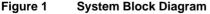

XMC1100 PG-VQFN-40 Pin Configuration (top view)

## Table 8 Port I/O Functions (cont'd)

| Function |                  | Outputs             |                |                       |      |                       | Inputs                |      |      |      |      |       |                 |                    |          |                    |                    |                    |

|----------|------------------|---------------------|----------------|-----------------------|------|-----------------------|-----------------------|------|------|------|------|-------|-----------------|--------------------|----------|--------------------|--------------------|--------------------|

|          | ALT1             | ALT2                | ALT3           | ALT4                  | ALT5 | ALT6                  | ALT7                  | HWO0 | HWO1 | HWIO | HWI1 | Input | Input           | Input              | Input    | Input              | Input              | Input              |

| P1.6     | VADC0.<br>EMUX12 | USIC0_CH1.D<br>OUT0 |                | USIC0_CH0.S<br>CLKOUT |      | USIC0_CH0.S<br>ELO2   | USIC0_CH1.S<br>ELO3   |      |      |      |      |       |                 | USIC0_CH0.D<br>X5F |          |                    |                    |                    |

| P2.0     | ERU0.<br>PDOUT3  | CCU40.OUT0          | ERU0.<br>GOUT3 |                       |      | USIC0_CH0.<br>DOUT0   | USIC0_CH0.<br>SCLKOUT |      |      |      |      |       | VADC0.<br>G0CH5 |                    | ERU0.0B0 | USIC0_CH0.<br>DX0E | USIC0_CH0.<br>DX1E | USIC0_CH1.<br>DX2F |

| P2.1     | ERU0.<br>PDOUT2  | CCU40.OUT1          | ERU0.<br>GOUT2 |                       |      | USIC0_CH0.<br>DOUT0   | USIC0_CH1.<br>SCLKOUT |      |      |      |      |       | VADC0.<br>G0CH6 |                    | ERU0.1B0 | USIC0_CH0.<br>DX0F | USIC0_CH1.<br>DX3A | USIC0_CH1.<br>DX4A |

| P2.2     |                  |                     |                |                       |      |                       |                       |      |      |      |      |       | VADC0.<br>G0CH7 |                    | ERU0.0B1 | USIC0_CH0.<br>DX3A | USIC0_CH0.<br>DX4A | USIC0_CH1.<br>DX5A |

| P2.3     |                  |                     |                |                       |      |                       |                       |      |      |      |      |       | VADC0.<br>G1CH5 |                    | ERU0.1B1 | USIC0_CH0.<br>DX5B | USIC0_CH1.<br>DX3C | USIC0_CH1.<br>DX4C |

| P2.4     |                  |                     |                |                       |      |                       |                       |      |      |      |      |       | VADC0.<br>G1CH6 |                    | ERU0.0A1 | USIC0_CH0.<br>DX3B | USIC0_CH0.<br>DX4B | USIC0_CH1.<br>DX5B |

| P2.5     |                  |                     |                |                       |      |                       |                       |      |      |      |      |       | VADC0.<br>G1CH7 |                    | ERU0.1A1 | USIC0_CH0.<br>DX5D | USIC0_CH1.<br>DX3E | USIC0_CH1.<br>DX4E |

| P2.6     |                  |                     |                |                       |      |                       |                       |      |      |      |      |       | VADC0.<br>G0CH0 |                    | ERU0.2A1 | USIC0_CH0.<br>DX3E | USIC0_CH0.<br>DX4E | USIC0_CH1.<br>DX5D |

| P2.7     |                  |                     |                |                       |      |                       |                       |      |      |      |      |       | VADC0.<br>G1CH1 |                    | ERU0.3A1 | USIC0_CH0.<br>DX5C | USIC0_CH1.<br>DX3D | USIC0_CH1.<br>DX4D |

| P2.8     |                  |                     |                |                       |      |                       |                       |      |      |      |      |       | VADC0.<br>G0CH1 | VADC0.<br>G1CH0    | ERU0.3B1 | USIC0_CH0.<br>DX3D | USIC0_CH0.<br>DX4D | USIC0_CH1.<br>DX5C |

| P2.9     |                  |                     |                |                       |      |                       |                       |      |      |      |      |       | VADC0.<br>G0CH2 | VADC0.<br>G1CH4    | ERU0.3B0 | USIC0_CH0.<br>DX5A | USIC0_CH1.<br>DX3B | USIC0_CH1.<br>DX4B |

| P2.10    | ERU0.<br>PDOUT1  | CCU40.OUT2          | ERU0.<br>GOUT1 |                       |      |                       | USIC0_CH1.<br>DOUT0   |      |      |      |      |       | VADC0.<br>G0CH3 | VADC0.<br>G1CH2    | ERU0.2B0 | USIC0_CH0.<br>DX3C | USIC0_CH0.<br>DX4C | USIC0_CH1.<br>DX0F |

| P2.11    | ERU0.<br>PDOUT0  | CCU40.OUT3          | ERU0.<br>GOUT0 |                       |      | USIC0_CH1.<br>SCLKOUT | USIC0_CH1.<br>DOUT0   |      |      |      |      |       | VADC0.<br>G0CH4 | VADC0.<br>G1CH3    | ERU0.2B1 | USIC0_CH1.<br>DX0E | USIC0_CH1.<br>DX1E |                    |

## 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                          | Sym                  | loc |      | Va   | lues                                | Unit | Note /                |

|--------------------------------------------------------------------|----------------------|-----|------|------|-------------------------------------|------|-----------------------|

|                                                                    |                      |     | Min. | Тур. | Max.                                |      | Test Cond<br>ition    |

| Junction temperature                                               | $T_{J}$              | SR  | -40  | -    | 115                                 | °C   | -                     |

| Storage temperature                                                | Ts                   | SR  | -40  | -    | 125                                 | °C   | -                     |

| Voltage on power supply pin with respect to $V_{\rm SSP}$          | $V_{DDP}$            | SR  | -0.3 | -    | 6                                   | V    | -                     |

| Voltage on any pin with respect to $V_{\rm SSP}$                   | $V_{\sf IN}$         | SR  | -0.5 | -    | $V_{\text{DDP}}$ + 0.5<br>or max. 6 | V    | whichever<br>is lower |

| Voltage on any analog input pin with respect to $V_{\rm SSP}$      | $V_{AIN}$ $V_{AREF}$ | SR  | -0.5 | -    | $V_{\text{DDP}}$ + 0.5<br>or max. 6 | V    | -                     |

| Input current on any pin during overload condition                 | I <sub>IN</sub>      | SR  | -10  | -    | 10                                  | mA   | -                     |

| Absolute sum of all input<br>currents during overload<br>condition | $\Sigma  I_{IN} $    | SR  | _    | -    | 50                                  | mA   | -                     |

| Analog comparator input voltage                                    | $V_{CM}$             | SR  | -0.3 | -    | V <sub>DDP</sub> + 0.3              | V    |                       |

## Table 9 Absolute Maximum Rating Parameters

## 3.1.3 Operating Conditions

The following operating conditions must not be exceeded in order to ensure correct operation and reliability of the XMC1100. All parameters specified in the following tables refer to these operating conditions, unless noted otherwise.

| Parameter                            | Symbol                |      | Values | 3    | Unit | Note /               |  |

|--------------------------------------|-----------------------|------|--------|------|------|----------------------|--|

|                                      |                       | Min. | Тур.   | Max. |      | Test Condition       |  |

| Ambient Temperature                  | $T_{\rm A}{ m SR}$    | -40  | -      | 85   | °C   | Temp. Range F        |  |

|                                      |                       | -40  | -      | 105  | °C   | Temp. Range X        |  |

| Digital supply voltage <sup>1)</sup> | $V_{\rm DDP}{ m SR}$  | 1.8  | -      | 5.5  | V    |                      |  |

| MCLK Frequency                       | $f_{\rm MCLK}{ m CC}$ | _    | -      | 33.2 | MHz  | CPU clock            |  |

| PCLK Frequency                       | $f_{PCLK}CC$          | -    | -      | 66.4 | MHz  | Peripherals<br>clock |  |

Table 10 Operating Conditions Parameters

1) See also the Supply Monitoring thresholds, Chapter 3.3.3.

## 3.2 DC Parameters

## 3.2.1 Input/Output Characteristics

Table 11 provides the characteristics of the input/output pins of the XMC1100.

| Parameter                                                   | Symbol            |    | Limit                      | Values                   | Unit | Test Conditions                                                                    |  |

|-------------------------------------------------------------|-------------------|----|----------------------------|--------------------------|------|------------------------------------------------------------------------------------|--|

|                                                             |                   |    | Min.                       | Max.                     |      |                                                                                    |  |

| Output low voltage on port pins                             | $V_{OLP}$         | СС | -                          | 1.0                      | V    | I <sub>OL</sub> = 11 mA (5 V)<br>I <sub>OL</sub> = 7 mA (3.3 V)                    |  |

| (with standard pads)                                        |                   |    | -                          | 0.4                      | V    | $I_{OL} = 5 \text{ mA} (5 \text{ V})$<br>$I_{OL} = 3.5 \text{ mA} (3.3 \text{ V})$ |  |

| Output low voltage on<br>high current pads                  | $V_{OLP1}$        | CC | -                          | 1.0                      | V    | $I_{\rm OL}$ = 50 mA (5 V)<br>$I_{\rm OL}$ = 25 mA (3.3 V)                         |  |

|                                                             |                   |    | -                          | 0.32                     | V    | I <sub>OL</sub> = 10 mA (5 V)                                                      |  |

|                                                             |                   |    | -                          | 0.4                      | V    | I <sub>OL</sub> = 5 mA (3.3 V)                                                     |  |

| Output high voltage on<br>port pins<br>(with standard pads) | $V_{OHP}$         | СС | V <sub>DDP</sub> - 1.0     | -                        | V    | I <sub>OH</sub> = -10 mA (5 V)<br>I <sub>OH</sub> = -7 mA (3.3 V)                  |  |

|                                                             |                   |    | V <sub>DDP</sub> -<br>0.4  | -                        | V    | $I_{\rm OH}$ = -4.5 mA (5 V)<br>$I_{\rm OH}$ = -2.5 mA (3.3 V)                     |  |

| Output high voltage on high current pads                    | V <sub>OHP1</sub> | CC | V <sub>DDP</sub> -<br>0.32 | -                        | V    | I <sub>OH</sub> = -6 mA (5 V)                                                      |  |

|                                                             |                   |    | V <sub>DDP</sub> -<br>1.0  | -                        | V    | I <sub>OH</sub> = -8 mA (3.3 V)                                                    |  |

|                                                             |                   |    | V <sub>DDP</sub> - 0.4     | -                        | V    | I <sub>OH</sub> = -4 mA (3.3 V)                                                    |  |

| Input low voltage on port<br>pins<br>(Standard Hysteresis)  | V <sub>ILPS</sub> | SR | -                          | $0.19 \times V_{ m DDP}$ | V    | CMOS Mode<br>(5 V, 3.3 V & 2.2 V)                                                  |  |

| Input high voltage on<br>port pins<br>(Standard Hysteresis) | V <sub>IHPS</sub> | SR | $0.7 \times V_{ m DDP}$    | -                        | V    | CMOS Mode<br>(5 V, 3.3 V & 2.2 V)                                                  |  |

| Input low voltage on port<br>pins<br>(Large Hysteresis)     | V <sub>ILPL</sub> | SR | -                          | $0.08 \times V_{ m DDP}$ | V    | CMOS Mode<br>(5 V, 3.3 V & 2.2 V) <sup>3)</sup>                                    |  |

| Table 11 | Input/Output Characteristics (Operating Condition | ons apply) |

|----------|---------------------------------------------------|------------|

|          | input output on a dotten of (operating of and     | ,          |

#### Table 11 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                         | Symbo              |    | Limit | Values | Unit | Test Conditions |  |

|-------------------------------------------------------------------|--------------------|----|-------|--------|------|-----------------|--|

|                                                                   |                    |    | Min.  | Max.   |      |                 |  |

| Maximum current into $V_{\text{DDP}}$ (TSSOP28/16, VQFN24)        | I <sub>MVDD1</sub> | SR | -     | 130    | mA   | 3)              |  |

| Maximum current into<br>V <sub>DDP</sub> (TSSOP38,<br>VQFN40)     | I <sub>MVDD2</sub> | SR | -     | 260    | mA   | 3)              |  |

| Maximum current out of<br>V <sub>SS</sub> (TSSOP28/16,<br>VQFN24) | I <sub>MVSS1</sub> | SR | -     | 130    | mA   | 3)              |  |

| Maximum current out of<br>V <sub>SS</sub> (TSSOP38,<br>VQFN40)    | I <sub>MVSS2</sub> | SR | -     | 260    | mA   | 3)              |  |

Not subject to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

2) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin.

3) Not subject to production test, verified by design/characterization.

4) Not subject to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when V<sub>DDP</sub> is powered off.

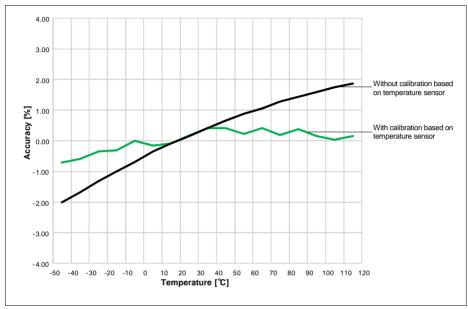

Figure 13 shows the typical curves for the accuracy of DCO1, with and without calibration based on temperature sensor, respectively.

## Figure 13 Typical DCO1 accuracy over temperature

Table 20 provides the characteristics of the 32 kHz clock output from digital controlled oscillators, DCO2 in XMC1100.

| Parameter         | Sym             | Symbol |      | nit Valu | ies  | Unit | Test Conditions                                                                              |

|-------------------|-----------------|--------|------|----------|------|------|----------------------------------------------------------------------------------------------|

|                   |                 |        | Min. | Тур.     | Max. |      |                                                                                              |

| Nominal frequency | $f_{\rm NOM}$   | СС     | 32.5 | 32.75    | 33   | kHz  | under nominal conditions <sup>1)</sup> after trimming                                        |

| Accuracy          | $\Delta f_{LT}$ | CC     | -1.7 | -        | 3.4  | %    | with respect to $f_{\text{NOM}}$ (typ),<br>over temperature<br>(0 °C to 85 °C) <sup>2)</sup> |

|                   |                 |        | -3.9 | -        | 4.0  | %    | with respect to $f_{\rm NOM}$ (typ),<br>over temperature<br>(-40 °C to 105 °C) <sup>2)</sup> |

## Table 20 32 kHz DCO2 Characteristics (Operating Conditions apply)

1) The deviation is relative to the factory trimmed frequency at nominal  $V_{\text{DDC}}$  and  $T_{\text{A}}$  = + 25 °C.

2) Not subject to production test, verified by design/characterisation.

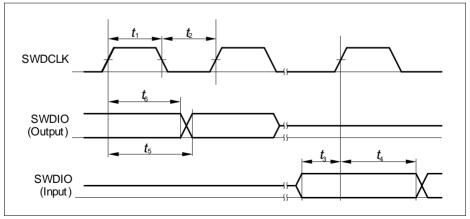

## 3.3.5 Serial Wire Debug Port (SW-DP) Timing

The following parameters are applicable for communication through the SW-DP interface.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                      | Symbol            |      | Values | ;      | Unit | Note /<br>Test Condition |  |

|------------------------------------------------|-------------------|------|--------|--------|------|--------------------------|--|

|                                                |                   | Min. | Тур.   | Max.   |      |                          |  |

| SWDCLK high time                               | t <sub>1</sub> SR | 50   | -      | 500000 | ns   | -                        |  |

| SWDCLK low time                                | t <sub>2</sub> SR | 50   | _      | 500000 | ns   | -                        |  |

| SWDIO input setup to SWDCLK rising edge        | t <sub>3</sub> SR | 10   | -      | -      | ns   | -                        |  |

| SWDIO input hold<br>after SWDCLK rising edge   | t <sub>4</sub> SR | 10   | -      | -      | ns   | -                        |  |

| SWDIO output valid time                        | t <sub>5</sub> CC | -    | -      | 68     | ns   | C <sub>L</sub> = 50 pF   |  |

| after SWDCLK rising edge                       |                   | _    | -      | 62     | ns   | C <sub>L</sub> = 30 pF   |  |

| SWDIO output hold time from SWDCLK rising edge | t <sub>6</sub> CC | 4    | -      | -      | ns   |                          |  |

| Table 21 | SWD Interface Timing | Parameters(Operating | Conditions apply) |

|----------|----------------------|----------------------|-------------------|

|          |                      |                      |                   |

## 3.3.6 SPD Timing Requirements

The optimum SPD decision time between  $0_B$  and  $1_B$  is 0.75 µs. With this value the system has maximum robustness against frequency deviations of the sampling clock on tool and on device side. However it is not always possible to exactly match this value with the given constraints for the sample clock. For instance for a oversampling rate of 4, the sample clock will be 8 MHz and in this case the closest possible effective decision time is 5.5 clock cycles (0.69 µs).

| Sample<br>Freq. | Sampling<br>Factor |        | Sample<br>Clocks 1 <sub>B</sub> | Effective<br>Decision<br>Time <sup>1)</sup> | Remark                                                                                    |

|-----------------|--------------------|--------|---------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------|

| 8 MHz           | 4                  | 1 to 5 | 6 to 12                         | 0.69 µs                                     | The other closest option $(0.81 \ \mu s)$ for the effective decision time is less robust. |

## Table 22 Optimum Number of Sample Clocks for SPD

1) Nominal sample frequency period multiplied with  $0.5 + (max. number of 0_B sample clocks)$

For a balanced distribution of the timing robustness of SPD between tool and device, the timing requirements for the tool are:

- Frequency deviation of the sample clock is +/- 5%

- Effective decision time is between 0.69 µs and 0.75 µs (calculated with nominal sample frequency)

| Parameter                                                                                 | Symbol          |    | Values |      |      | Unit | Note /         |

|-------------------------------------------------------------------------------------------|-----------------|----|--------|------|------|------|----------------|

|                                                                                           |                 |    | Min.   | Тур. | Max. |      | Test Condition |

| Receive data input<br>DX0/DX[5:3] setup time to<br>shift clock receive edge <sup>1)</sup> | t <sub>12</sub> | SR | 10     | -    | _    | ns   |                |

| Data input DX0/DX[5:3] hold<br>time from clock input DX1<br>receive edge <sup>1)</sup>    | t <sub>13</sub> | SR | 10     | -    | _    | ns   |                |

| Data output DOUT[3:0] valid time                                                          | t <sub>14</sub> | CC | -      | -    | 80   | ns   |                |

## Table 24 USIC SSC Slave Mode Timing (cont'd)

1) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

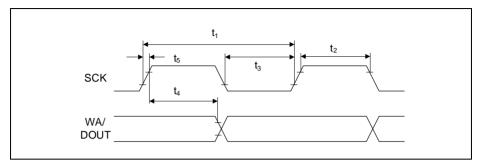

| Figure 17 | USIC IIS Master | Transmitter | Timing |

|-----------|-----------------|-------------|--------|

|-----------|-----------------|-------------|--------|

| Parameter    | Symbol             | Values                      |      |      | Unit | Note /         |

|--------------|--------------------|-----------------------------|------|------|------|----------------|

|              |                    | Min.                        | Тур. | Max. |      | Test Condition |

| Clock period | t <sub>6</sub> SR  | 4/f <sub>MCLK</sub>         | -    | -    | ns   |                |

| Clock HIGH   | t <sub>7</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -    | -    | ns   |                |

| Clock Low    | t <sub>8</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -    | -    | ns   |                |

| Set-up time  | t <sub>9</sub> SR  | 0.2 x<br>t <sub>6min</sub>  | -    | -    | ns   |                |

| Hold time    | t <sub>10</sub> SR | 10                          | -    | -    | ns   |                |

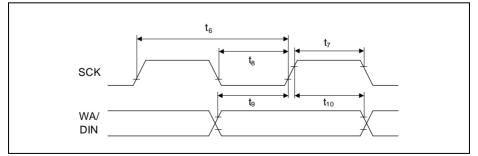

| Table 28 | <b>USIC IIS</b> | Slave | Receiver | Timing |

|----------|-----------------|-------|----------|--------|

|----------|-----------------|-------|----------|--------|

Figure 18 USIC IIS Slave Receiver Timing

Package and Reliability

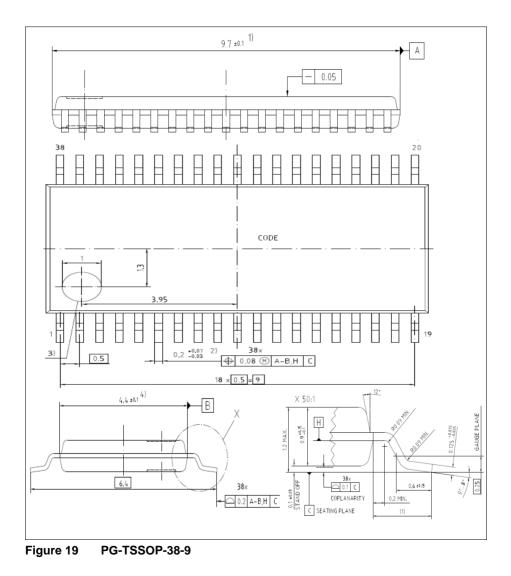

## 4.2 Package Outlines

## XMC1100 XMC1000 Family

## Package and Reliability

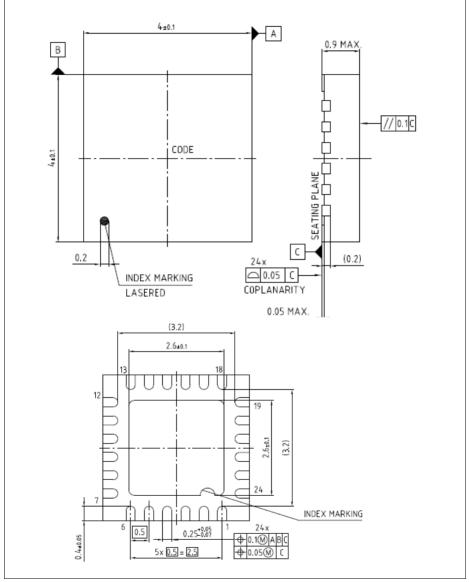

Figure 21 PG-VQFN-24-19

## Package and Reliability

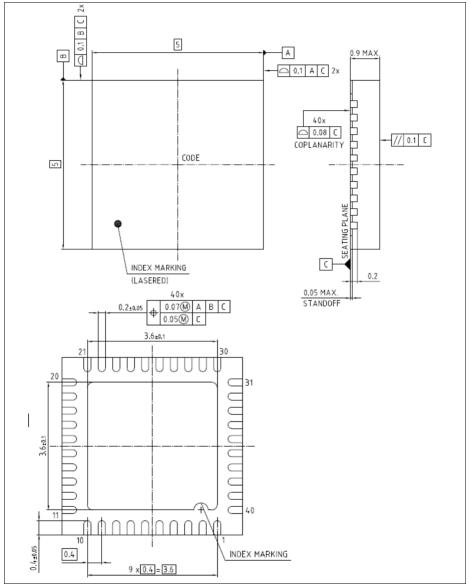

## Figure 22 PG-VQFN-40-13

All dimensions in mm.

www.infineon.com

Published by Infineon Technologies AG