Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 18432                                                                     |

| Number of I/O                  | 71                                                                        |

| Number of Gates                | 60000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 125°C (TA)                                                        |

| Package / Case                 | 100-TQFP                                                                  |

| Supplier Device Package        | 100-VQFP (14x14)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p060-1vqg100t |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

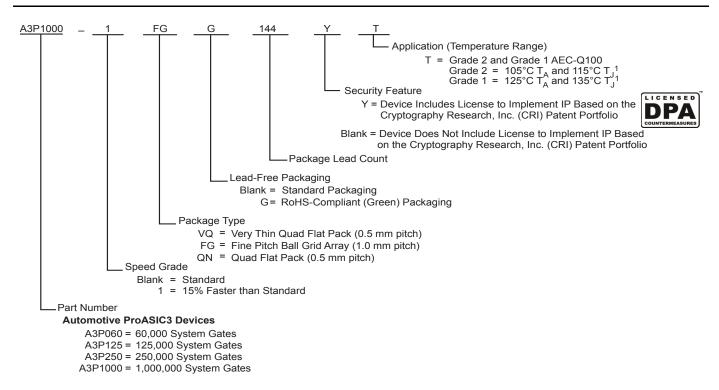

## **Automotive ProASIC3 Ordering Information**

#### Notes:

- 1.  $T_A$  = Ambient temperature and  $T_J$  = Junction temperature.

- 2. Minimum order quantities apply. Contact your local Microsemi SoC Products Group sales office for details.

Revision 5

## **Temperature Grade Offerings**

| Package | A3P060  | A3P125  | A3P250  | A3P1000 |

|---------|---------|---------|---------|---------|

| VQ100   | C, I, T | C, I, T | C, I, T | -       |

| FG144   | C, I, T | C, I, T | C, I, T | C, I, T |

| FG256   | _       | -       | C, I, T | C, I, T |

| FG484   | -       | -       | -       | C, I, T |

| QNG132  | -       | C, I, T | C, I, T | -       |

#### Notes:

- 1. C = Commercial temperature range: 0°C to 70°C

- 2. I = Industrial temperature range: -40°C to 85°C

- T = Automotive temperature range: Grade 2 and Grade 1 AEC-Q100 Grade 2 = 105°C T<sub>A</sub> and 115°C T<sub>J</sub>

Grade 1 = 125°C T<sub>A</sub> and 135°C T<sub>J</sub>

4. Specifications for Commercial and Industrial grade devices can be found in the ProASIC3 Flash Family FPGAs datasheet.

## **Speed Grade and Temperature Grade Matrix**

| Temperature Grade                               | Std. | -1 |

|-------------------------------------------------|------|----|

| T (Grade 1 and Grade 2), Commercial, Industrial | 3    | 3  |

#### Notes:

- 1. T = Automotive temperature range: Grade 2 and Grade 1 AEC-Q100 Grade 2 =  $105^{\circ}$ C  $T_A$  and  $115^{\circ}$ C  $T_J$ Grade 1 =  $125^{\circ}$ C  $T_A$  and  $135^{\circ}$ C  $T_J$

- 2. Specifications for Commercial and Industrial grade devices can be found in the ProASIC3 Flash Family FPGAs datasheet.

Contact your local Microsemi SoC Products Group representative for device availability: http://www.microsemi.com/soc/contact/default.aspx.

Revision 5

#### User Nonvolatile FlashROM

Automotive ProASIC3 devices have 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications:

- · Unique protocol addressing (wireless or fixed)

- System calibration settings

- · Device serialization and/or inventory control

- Subscription-based business models (for example, infotainment systems)

- Secure key storage for secure communications algorithms

- Asset management/tracking

- Date stamping

- Version management

The FlashROM is written using the standard Automotive ProASIC3 IEEE 1532 JTAG programming interface.

The FlashROM can be programmed via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing. Note that the FlashROM can only be programmed from the JTAG interface and cannot be programmed from the internal logic array.

The FlashROM is programmed as 8 banks of 128 bits; however, reading is performed on a byte-by-byte basis using a synchronous interface. A 7-bit address from the FPGA core defines which of the 8 banks and which of the 16 bytes within that bank are being read. The three most significant bits (MSBs) of the FlashROM address determine the bank, and the four least significant bits (LSBs) of the FlashROM address define the byte.

Automotive ProASIC3 development software solutions, Libero<sup>®</sup> System-on-Chip (SoC) and Designer, have extensive support for the FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

#### **SRAM**

Automotive ProASIC3 devices have embedded SRAM blocks along their north and south sides. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be sent through a 4-bit port and read as a single bitstream. The embedded SRAM blocks can be initialized via the device JTAG port (ROM emulation mode) using the UJTAG macro.

#### PLL and CCC

Automotive ProASIC3 devices provide designers with very flexible clock conditioning circuit (CCC) capabilities. Each member of the Automotive ProASIC3 family contains six CCCs. One CCC (center west side) has a PLL.

The six CCC blocks are located at the four corners and the centers of the east and west sides. One CCC (center west side) has a PLL.

All six CCC blocks are usable; the four corner CCCs and the east CCC allow simple clock delay operations as well as clock spine access.

The inputs of the six CCC blocks are accessible from the FPGA core or from one of several inputs located near the CCC that have dedicated connections to the CCC block.

The CCC block has these key features:

- Wide input frequency range (f<sub>IN CCC</sub>) = 1.5 MHz to 350 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz to 350 MHz

- Clock delay adjustment via programmable and fixed delays from -7.56 ns to +11.12 ns

- · 2 programmable delay types for clock skew minimization

- Clock frequency synthesis (for PLL only)

Table 2-10 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings <sup>1</sup>

Applicable to Standard Plus I/O Banks

|                               | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC3 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (μW/MHz) <sup>3</sup> |

|-------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Single-Ended                  |                        |          |                                        |                                              |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 35                     | 3.3      | -                                      | 452.67                                       |

| 2.5 V LVCMOS                  | 35                     | 2.5      | _                                      | 258.32                                       |

| 1.8 V LVCMOS                  | 35                     | 1.8      | _                                      | 133.59                                       |

| 1.5 V LVCMOS<br>(JESD8-11)    | 35                     | 1.5      | -                                      | 92.84                                        |

| 3.3 V PCI                     | 10                     | 3.3      | _                                      | 184.92                                       |

| 3.3 V PCI-X                   | 10                     | 3.3      | _                                      | 184.92                                       |

#### Notes:

- Dynamic power consumption is given for standard load and software default drive strength and output slew.

- 2. PDC3 is the static power (where applicable) measured on VMV.

- 3. PAC10 is the total dynamic power measured on VCCI and VMV.

2-8 Revision 5

#### **Overview of I/O Performance**

# Summary of I/O DC Input and Output Levels – Default I/O Software Settings

Table 2-14 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings

Applicable to Advanced I/O Banks

|                               |                   |                        |           | VIL         | VIH           |           | VOL         | VOH         | I <sub>OL</sub> | I <sub>OH</sub> |

|-------------------------------|-------------------|------------------------|-----------|-------------|---------------|-----------|-------------|-------------|-----------------|-----------------|

| I/O Standard                  | Drive<br>Strength | Slew<br>Rate           | Min.<br>V | Max.<br>V   | Min.<br>V     | Max.<br>V | Max.<br>V   | Min.<br>V   | mA              | mA              |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 12 mA             | High                   | -0.3      | 0.8         | 2             | 3.6       | 0.4         | 2.4         | 12              | 12              |

| 2.5 V LVCMOS                  | 12 mA             | High                   | -0.3      | 0.7         | 1.7           | 3.6       | 0.7         | 1.7         | 12              | 12              |

| 1.8 V LVCMOS                  | 12 mA             | High                   | -0.3      | 0.35 * VCCI | 0.65 * VCCI   | 3.6       | 0.45        | VCCI - 0.45 | 12              | 12              |

| 1.5 V LVCMOS                  | 12 mA             | High                   | -0.3      | 0.30 * VCCI | 0.7 * VCCI    | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 12              | 12              |

| 3.3 V PCI                     |                   | Per PCI specifications |           |             |               |           |             |             |                 |                 |

| 3.3 V PCI-X                   |                   |                        |           | Р           | er PCI-X spec | ification | S           |             |                 |                 |

Note: Currents are measured at 125°C junction temperature.

Table 2-15 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings

Applicable to Standard Plus I/O Banks

|                                  |                   |                        |           | VIL         | VIH                    |           | VOL         | VOH                     | l <sub>OL</sub> | I <sub>OH</sub> |

|----------------------------------|-------------------|------------------------|-----------|-------------|------------------------|-----------|-------------|-------------------------|-----------------|-----------------|

| I/O Standard                     | Drive<br>Strength | Slew<br>Rate           | Min.<br>V | Max.<br>V   | Min.<br>V              | Max.<br>V | Max.<br>V   | Min.<br>V               | mA              | mA              |

| 3.3 V LVTTL /<br>3.3 V<br>LVCMOS | 12 mA             | High                   | -0.3      | 0.8         | 2                      | 3.6       | 0.4         | 2.4                     | 12              | 12              |

| 2.5 V<br>LVCMOS                  | 12 mA             | High                   | -0.3      | 0.7         | 1.7                    | 3.6       | 0.7         | 1.7                     | 12              | 12              |

| 1.8 V<br>LVCMOS                  | 8 mA              | High                   | -0.3      | 0.35 * VCCI | 0.65 * VCCI            | 3.6       | 0.45        | VCCI - 0.45             | 8               | 8               |

| 1.5 V<br>LVCMOS                  | 4 mA              | High                   | -0.3      | 0.30 * VCCI | 0.7 * V <sub>CCI</sub> | 3.6       | 0.25 * VCCI | 0.75 * V <sub>CCI</sub> | 4               | 4               |

| 3.3 V PCI                        |                   | Per PCI specifications |           |             |                        |           |             |                         |                 |                 |

| 3.3 V PCI-X                      |                   |                        |           | Pe          | er PCI-X speci         | fications |             |                         |                 |                 |

Note: Currents are measured at 125°C junction temperature.

2-16 Revision 5

Table 2-16 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings

Applicable to Standard I/O Banks

|                               |                   |              |           | VIL         | VIH         |           | VOL         | VOH         | I <sub>OL</sub> | I <sub>OH</sub> |

|-------------------------------|-------------------|--------------|-----------|-------------|-------------|-----------|-------------|-------------|-----------------|-----------------|

| I/O Standard                  | Drive<br>Strength | Slew<br>Rate | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA              | mA              |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA              | High         | -0.3      | 0.8         | 2           | 3.6       | 0.4         | 2.4         | 8               | 8               |

| 2.5 V LVCMOS                  | 8 mA              | High         | -0.3      | 0.7         | 1.7         | 3.6       | 0.7         | 1.7         | 8               | 8               |

| 1.8 V LVCMOS                  | 4 mA              | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45        | VCCI - 0.45 | 4               | 4               |

| 1.5 V LVCMOS                  | 2 mA              | High         | -0.3      | 0.30 * VCCI | 0.7 * VCCI  | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2               | 2               |

Note: Currents are measured at 125°C junction temperature.

Table 2-17 • Summary of Maximum and Minimum DC Input Levels Applicable to Automotive Grade 1 and Grade 2

|                            | Automotiv | /e Grade 1 <sup>1</sup> | Automotive Grade 2 <sup>2</sup> |     |  |

|----------------------------|-----------|-------------------------|---------------------------------|-----|--|

|                            | IIL       | IIH                     | IIL                             | IIH |  |

| DC I/O Standards           | μΑ        | μΑ                      | μΑ                              | μΑ  |  |

| 3.3 V LVTTL / 3.3 V LVCMOS | 10        | 10                      | 15                              | 15  |  |

| 2.5 V LVCMOS               | 10        | 10                      | 15                              | 15  |  |

| 1.8 V LVCMOS               | 10        | 10                      | 15                              | 15  |  |

| 1.5 V LVCMOS               | 10        | 10                      | 15                              | 15  |  |

| 3.3 V PCI                  | 10        | 10                      | 15                              | 15  |  |

| 3.3 V PCI-X                | 10        | 10                      | 15                              | 15  |  |

#### Notes:

- 1. Automotive range Grade 1 (-40°C <  $T_J$  < 135°C)

- 2. Automotive range Grade 2 ( $-40^{\circ}$ C <  $T_J$  < 115 $^{\circ}$ C)

## Summary of I/O Timing Characteristics – Default I/O Software Settings

Table 2-18 • Summary of AC Measuring Points

| Standard                   | Measuring Trip Point (Vtrip) |

|----------------------------|------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 1.4 V                        |

| 2.5 V LVCMOS               | 1.2 V                        |

| 1.8 V LVCMOS               | 0.90 V                       |

| 1.5 V LVCMOS               | 0.75 V                       |

| 3.3 V PCI                  | 0.285 * VCCI (RR)            |

|                            | 0.615 * VCCI (FF)            |

| 3.3 V PCI-X                | 0.285 * VCCI (RR)            |

|                            | 0.615 * VCCI (FF)            |

Table 2-23 • Summary of I/O Timing Characteristics—Software Default Settings

-1 Speed Grade, Automotive-Case Conditions: T<sub>J</sub> = 115°C, Worst Case VCC = 1.425 V

Worst Case VCCI = 3.0 V

Standard Plus I/O Banks

| I/O Standard                  | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor | t <sub>DOUT</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>pY</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) | Units |

|-------------------------------|---------------------|-----------|----------------------|-------------------|------------------------|----------------------|-----------------------|----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 12 mA               | High      | 35 pF                | -                 | 0.55                   | 3.36                 | 0.04                  | 0.97                 | 0.39                   | 3.42                 | 1.56                 | 3.05                 | 1.94                 | 5.55                  | 2.80                  | ns    |

| 2.5 V LVCMOS                  | 12 mA               | High      | 35 pF                | _                 | 0.55                   | 3.05                 | 0.04                  | 1.23                 | 0.39                   | 3.11                 | 2.99                 | 1.56                 | 1.69                 | 5.23                  | 5.11                  | ns    |

| 1.8 V LVCMOS                  | 8 mA                | High      | 35 pF                | _                 | 0.55                   | 3.73                 | 0.04                  | 1.16                 | 0.39                   | 3.65                 | 3.86                 | 1.62                 | 1.68                 | 5.78                  | 5.99                  | ns    |

| 1.5 V LVCMOS                  | 4 mA                | High      | 35 pF                | _                 | 0.55                   | 4.60                 | 0.04                  | 1.35                 | 0.39                   | 4.61                 | 5.05                 | 2.07                 | 1.85                 | 6.74                  | 7.18                  | ns    |

| 3.3 V PCI                     | Per PCI<br>spec     | High      | 10 pF                | 25 <sup>2</sup>   | 0.55                   | 2.55                 | 0.04                  | 0.82                 | 0.39                   | 1.27                 | 0.94                 | 2.65                 | 3.06                 | 2.49                  | 2.18                  | ns    |

| 3.3 V PCI-X                   | Per PCI-X<br>spec   | High      | 10 pF                | 25 <sup>2</sup>   | 0.55                   | 2.55                 | 0.04                  | 0.79                 | 0.39                   | 1.27                 | 0.94                 | 2.65                 | 3.06                 | 2.49                  | 2.18                  | ns    |

#### Notes:

- 1. For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

- 2. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-11 on page 2-48 for connectivity. This resistor is not required during normal operation.

## **Output Register**

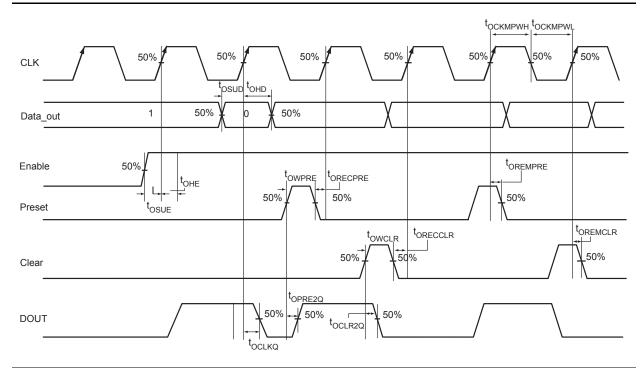

Figure 2-18 • Output Register Timing Diagram

#### **Timing Characteristics**

Table 2-94 • Output Data Register Propagation Delays

Automotive-Case Conditions: T<sub>J</sub> = 135°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | -1   | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 0.72 | 0.84 | ns    |

| t <sub>OSUD</sub>    | Data Setup Time for the Output Data Register                         | 0.38 | 0.45 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | 0.00 | ns    |

| t <sub>OSUE</sub>    | Enable Setup Time for the Output Data Register                       | 0.53 | 0.63 | ns    |

| t <sub>OHE</sub>     | Enable Hold Time for the Output Data Register                        | 0.00 | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 0.98 | 1.15 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 0.98 | 1.15 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        | 0.27 | 0.32 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.27 | 0.32 | ns    |

| t <sub>OWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.25 | 0.30 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.25 | 0.30 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width High for the Output Data Register          | 0.41 | 0.48 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Data Register           | 0.37 | 0.43 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

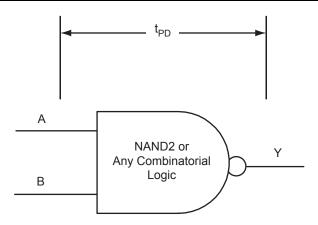

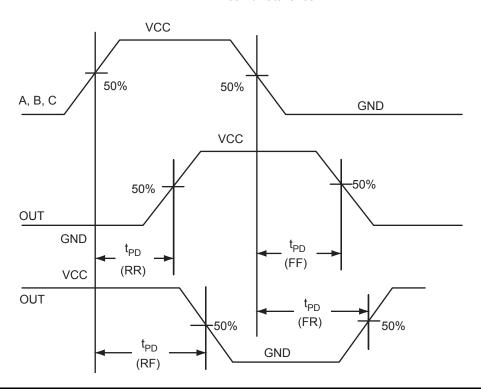

$\begin{aligned} t_{PD} &= \text{MAX}(t_{PD(RR)}, t_{PD(RF)}, t_{PD(FF)}, t_{PD(FR)}) \\ \text{where edges are applicable for the particular} \\ \text{combinatorial cell} \end{aligned}$

Figure 2-25 • Timing Model and Waveforms

2-70 Revision 5

Table 2-107 • Register Delays

Automotive-Case Conditions: T<sub>J</sub> = 115°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | -1   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.66 | 0.77 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.51 | 0.60 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.54 | 0.64 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.48 | 0.56 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.48 | 0.56 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.27 | 0.31 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.27 | 0.31 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.25 | 0.30 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.25 | 0.30 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.41 | 0.48 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.37 | 0.43 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

2-74 Revision 5

Table 2-118 • RAM512X18 Automotive-Case Conditions:  $T_J = 135^{\circ}C$ , Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                        | -1   | Std. | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|-------|

| t <sub>AS</sub>       | Address Setup Time                                                                                                 | 0.30 | 0.35 | ns    |

| t <sub>AH</sub>       | Address Hold Time                                                                                                  | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN Setup Time                                                                                                | 0.11 | 0.13 | ns    |

| t <sub>ENH</sub>      | REN, WEN Hold Time                                                                                                 | 0.07 | 0.08 | ns    |

| t <sub>DS</sub>       | Input data (WD) Setup Time                                                                                         | 0.22 | 0.26 | ns    |

| t <sub>DH</sub>       | Input data (WD) Hold Time                                                                                          | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to New Data Valid on RD (output retained)                                                               | 2.58 | 3.03 | ns    |

| t <sub>CKQ2</sub>     | Clock High to New Data Valid on RD (pipelined)                                                                     | 1.07 | 1.26 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge | 0.43 | 0.50 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address—Applicable to Opening Edge | 0.50 | 0.59 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to Data Out Low on RD (flow-through)                                                                     | 1.10 | 1.29 | ns    |

|                       | RESET Low to Data Out Low on RD (pipelined)                                                                        | 1.10 | 1.29 | ns    |

| t <sub>REMRSTB</sub>  | RESET Removal                                                                                                      | 0.34 | 0.40 | ns    |

| t <sub>RECRSTB</sub>  | RESET Recovery                                                                                                     | 1.79 | 2.10 | ns    |

| t <sub>MPWRSTB</sub>  | RESET Minimum Pulse Width                                                                                          | 0.25 | 0.30 | ns    |

| t <sub>CYC</sub>      | Clock Cycle Time                                                                                                   | 3.85 | 4.53 | ns    |

| F <sub>MAX</sub>      | Maximum Frequency                                                                                                  | 255  | 217  | MHz   |

#### Notes:

<sup>1.</sup> For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

<sup>2.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

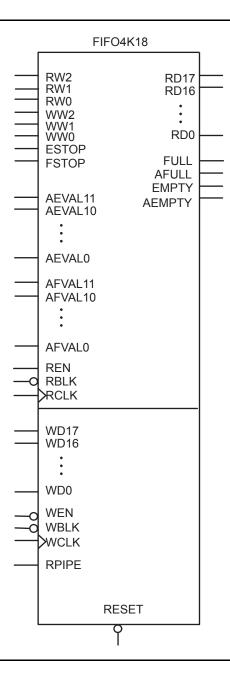

## **FIFO**

Figure 2-36 • FIFO Model

2-90 Revision 5

## **Timing Characteristics**

**Table 2-121 • FIFO**

Worst-Case Automotive Conditions:  $T_J = 135^{\circ}C$ , VCC = 1.425 V

| Parameter            | Description                                       | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 1.97 | 1.67 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.03 | 0.02 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.28 | 0.32 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.26 | 0.22 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 3.37 | 2.86 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 1.28 | 1.09 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 2.45 | 2.09 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 2.33 | 1.98 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 8.85 | 7.53 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 2.42 | 2.06 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 8.76 | 7.45 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 1.32 | 1.12 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 1.32 | 1.12 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.41 | 0.35 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 2.14 | 1.82 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.30 | 0.26 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 4.62 | 3.93 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 217  | 255  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

2-94 Revision 5

## **JTAG 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/O Characteristics" section on page 2-12 for more details.

### **Timing Characteristics**

Table 2-125 • JTAG 1532

Commercial-Case Conditions:  $T_J = 70$ °C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | -2 | -1 | Std. | Units |

|----------------------|-----------------------------|----|----|------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  |    |    |      | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   |    |    |      | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time |    |    |      | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  |    |    |      | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       |    |    |      | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       |    |    |      | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 20 | 20 | 20   | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         |    |    |      | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        |    |    |      | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        |    |    |      | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

## Automotive ProASIC3 Flash Family FPGAs

| VQ100                      |                |  |  |  |

|----------------------------|----------------|--|--|--|

| Pin Number A3P125 Function |                |  |  |  |

| 1                          | GND            |  |  |  |

| 2                          | GAA2/IO67RSB1  |  |  |  |

| 3                          | IO68RSB1       |  |  |  |

| 4                          | GAB2/IO69RSB1  |  |  |  |

| 5                          | IO132RSB1      |  |  |  |

| 6                          | GAC2/IO131RSB1 |  |  |  |

| 7                          | IO130RSB1      |  |  |  |

| 8                          | IO129RSB1      |  |  |  |

| 9                          | GND            |  |  |  |

| 10                         | GFB1/IO124RSB1 |  |  |  |

| 11                         | GFB0/IO123RSB1 |  |  |  |

| 12                         | VCOMPLF        |  |  |  |

| 13                         | GFA0/IO122RSB1 |  |  |  |

| 14                         | VCCPLF         |  |  |  |

| 15                         | GFA1/IO121RSB1 |  |  |  |

| 16                         | GFA2/IO120RSB1 |  |  |  |

| 17                         | VCC            |  |  |  |

| 18                         | VCCIB1         |  |  |  |

| 19                         | GEC0/IO111RSB1 |  |  |  |

| 20                         | GEB1/IO110RSB1 |  |  |  |

| 21                         | GEB0/IO109RSB1 |  |  |  |

| 22                         | GEA1/IO108RSB1 |  |  |  |

| 23                         | GEA0/IO107RSB1 |  |  |  |

| 24                         | VMV1           |  |  |  |

| 25                         | GNDQ           |  |  |  |

| 26                         | GEA2/IO106RSB1 |  |  |  |

| 27                         | GEB2/IO105RSB1 |  |  |  |

| 28                         | GEC2/IO104RSB1 |  |  |  |

| 29                         | IO102RSB1      |  |  |  |

| 30                         | IO100RSB1      |  |  |  |

| 31                         | IO99RSB1       |  |  |  |

| 32                         | IO97RSB1       |  |  |  |

| 33                         | IO96RSB1       |  |  |  |

| 34                         | IO95RSB1       |  |  |  |

| 35                         | IO94RSB1       |  |  |  |

| 36                         | IO93RSB1       |  |  |  |

| VQ100                        |               |  |  |

|------------------------------|---------------|--|--|

| Pin Number   A3P125 Function |               |  |  |

| 37                           | VCC           |  |  |

| 38                           | GND           |  |  |

| 39                           | VCCIB1        |  |  |

| 40                           | IO87RSB1      |  |  |

| 41                           | IO84RSB1      |  |  |

| 42                           | IO81RSB1      |  |  |

| 43                           | IO75RSB1      |  |  |

| 44                           | GDC2/IO72RSB1 |  |  |

| 45                           | GDB2/IO71RSB1 |  |  |

| 46                           | GDA2/IO70RSB1 |  |  |

| 47                           | TCK           |  |  |

| 48                           | TDI           |  |  |

| 49                           | TMS           |  |  |

| 50                           | VMV1          |  |  |

| 51                           | GND           |  |  |

| 52                           | VPUMP         |  |  |

| 53                           | NC NC         |  |  |

| 54                           | TDO           |  |  |

| 55                           | TRST          |  |  |

| 56                           | VJTAG         |  |  |

| 57                           | GDA1/IO65RSB0 |  |  |

| 58                           | GDC0/IO62RSB0 |  |  |

| 59                           | GDC1/IO61RSB0 |  |  |

| 60                           | GCC2/IO59RSB0 |  |  |

| 61                           | GCB2/IO58RSB0 |  |  |

| 62                           | GCA0/IO56RSB0 |  |  |

| 63                           | GCA1/IO55RSB0 |  |  |

| 64                           | GCC0/IO52RSB0 |  |  |

| 65                           | GCC1/IO51RSB0 |  |  |

| 66                           | VCCIB0        |  |  |

| 67                           | GND           |  |  |

| 68                           | VCC           |  |  |

| 69                           | IO47RSB0      |  |  |

| 70                           | GBC2/IO45RSB0 |  |  |

| 71                           | GBB2/IO43RSB0 |  |  |

| 72                           | IO42RSB0      |  |  |

| <u> </u>                     | I             |  |  |

| VQ100      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A3P125 Function |  |  |  |

| 73         | GBA2/IO41RSB0   |  |  |  |

| 74         | VMV0            |  |  |  |

| 75         | GNDQ            |  |  |  |

| 76         | GBA1/IO40RSB0   |  |  |  |

| 77         | GBA0/IO39RSB0   |  |  |  |

| 78         | GBB1/IO38RSB0   |  |  |  |

| 79         | GBB0/IO37RSB0   |  |  |  |

| 80         | GBC1/IO36RSB0   |  |  |  |

| 81         | GBC0/IO35RSB0   |  |  |  |

| 82         | IO32RSB0        |  |  |  |

| 83         | IO28RSB0        |  |  |  |

| 84         | IO25RSB0        |  |  |  |

| 85         | IO22RSB0        |  |  |  |

| 86         | IO19RSB0        |  |  |  |

| 87         | VCCIB0          |  |  |  |

| 88         | GND             |  |  |  |

| 89         | VCC             |  |  |  |

| 90         | IO15RSB0        |  |  |  |

| 91         | IO13RSB0        |  |  |  |

| 92         | IO11RSB0        |  |  |  |

| 93         | IO09RSB0        |  |  |  |

| 94         | IO07RSB0        |  |  |  |

| 95         | GAC1/IO05RSB0   |  |  |  |

| 96         | GAC0/IO04RSB0   |  |  |  |

| 97         | GAB1/IO03RSB0   |  |  |  |

| 98         | GAB0/IO02RSB0   |  |  |  |

| 99         | GAA1/IO01RSB0   |  |  |  |

| 100        | GAA0/IO00RSB0   |  |  |  |

| QN132      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A3P125 Function |  |  |  |

| C17        | IO83RSB1        |  |  |  |

| C18        | VCCIB1          |  |  |  |

| C19        | TCK             |  |  |  |

| C20        | VMV1            |  |  |  |

| C21        | VPUMP           |  |  |  |

| C22        | VJTAG           |  |  |  |

| C23        | VCCIB0          |  |  |  |

| C24        | NC              |  |  |  |

| C25        | NC              |  |  |  |

| C26        | GCA1/IO55RSB0   |  |  |  |

| C27        | GCC0/IO52RSB0   |  |  |  |

| C28        | VCCIB0          |  |  |  |

| C29        | IO42RSB0        |  |  |  |

| C30        | GNDQ            |  |  |  |

| C31        | GBA1/IO40RSB0   |  |  |  |

| C32        | GBB0/IO37RSB0   |  |  |  |

| C33        | VCC             |  |  |  |

| C34        | IO24RSB0        |  |  |  |

| C35        | IO19RSB0        |  |  |  |

| C36        | IO16RSB0        |  |  |  |

| C37        | IO10RSB0        |  |  |  |

| C38        | VCCIB0          |  |  |  |

| C39        | GAB1/IO03RSB0   |  |  |  |

| C40        | VMV0            |  |  |  |

| D1         | GND             |  |  |  |

| D2         | GND             |  |  |  |

| D3         | GND             |  |  |  |

| D4         | GND             |  |  |  |

| FG256      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | A3P1000 Function |  |  |  |

| P9         | IO137RSB2        |  |  |  |

| P10        | IO134RSB2        |  |  |  |

| P11        | IO128RSB2        |  |  |  |

| P12        | VMV1             |  |  |  |

| P13        | TCK              |  |  |  |

| P14        | VPUMP            |  |  |  |

| P15        | TRST             |  |  |  |

| P16        | GDA0/IO113NDB1   |  |  |  |

| R1         | GEA1/IO188PDB3   |  |  |  |

| R2         | GEA0/IO188NDB3   |  |  |  |

| R3         | IO184RSB2        |  |  |  |

| R4         | GEC2/IO185RSB2   |  |  |  |

| R5         | IO168RSB2        |  |  |  |

| R6         | IO163RSB2        |  |  |  |

| R7         | IO157RSB2        |  |  |  |

| R8         | IO149RSB2        |  |  |  |

| R9         | IO143RSB2        |  |  |  |

| R10        | IO138RSB2        |  |  |  |

| R11        | IO131RSB2        |  |  |  |

| R12        | IO125RSB2        |  |  |  |

| R13        | GDB2/IO115RSB2   |  |  |  |

| R14        | TDI              |  |  |  |

| R15        | GNDQ             |  |  |  |

| R16        | TDO              |  |  |  |

| T1         | GND              |  |  |  |

| T2         | IO183RSB2        |  |  |  |

| Т3         | GEB2/IO186RSB2   |  |  |  |

| T4         | IO172RSB2        |  |  |  |

| T5         | IO170RSB2        |  |  |  |

| T6         | IO164RSB2        |  |  |  |

| T7         | IO158RSB2        |  |  |  |

| Т8         | IO153RSB2        |  |  |  |

| Т9         | IO142RSB2        |  |  |  |

| T10        | IO135RSB2        |  |  |  |

| T11        | IO130RSB2        |  |  |  |

| T12        | GDC2/IO116RSB2   |  |  |  |

| FG256      |                  |  |  |

|------------|------------------|--|--|

| Pin Number | A3P1000 Function |  |  |

| T13        | IO120RSB2        |  |  |

| T14        | GDA2/IO114RSB2   |  |  |

| T15        | TMS              |  |  |

| T16        | GND              |  |  |

# 5 - Datasheet Information

# **List of Changes**

The following table lists critical changes that were made in each revision of the Automotive ProASIC3 datasheet.

| Revision                       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page            |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 5<br>(January 2013)   | The "Automotive ProASIC3 Ordering Information" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43222).                                                                                                                                                                                                                                          | 1-III           |

|                                | Added a note to Table 2-2 • Recommended Operating Conditions (SAR 43675): The programming temperature range supported is T <sub>ambient</sub> = 0°C to 85°C.                                                                                                                                                                                                                                                                                                                         | 2-2             |

|                                | The note in Table 2-116 • Automotive ProASIC3 CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42560).                                                                                                                                                                                                                                                                                           | 2-80            |

|                                | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                                                                                                                                                                                                                         | NA              |

| Revision 4                     | The "Specifying I/O States During Programming" section is new (SAR 34691).                                                                                                                                                                                                                                                                                                                                                                                                           | 1-6             |

| (September 2012)               | Table 2-2 • Recommended Operating Conditions was revised to change VPUMP values for programming mode from "3.0 to 3.6" to "3.15 to 3.45" (SAR 34703).                                                                                                                                                                                                                                                                                                                                | 2-2             |

|                                | Maximum values for VIL and VIH were corrected in LVPECL Table 2-86 • Minimum and Maximum DC Input and Output Levels (SAR 37693).                                                                                                                                                                                                                                                                                                                                                     | 2-52            |

|                                | Values were added for F <sub>DDRIMAX</sub> and F <sub>DDOMAX</sub> in the following tables (SAR 34804):                                                                                                                                                                                                                                                                                                                                                                              | 2-64 to         |

|                                | Table 2-99 • Input DDR Propagation Delays (T <sub>J</sub> = 135°C)                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-68            |

|                                | Table 2-100 • Input DDR Propagation Delays (T <sub>J</sub> = 115°C)                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |

|                                | Table 2-102 • Output DDR Propagation Delays (T <sub>J</sub> = 135°C)                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

|                                | Table 2-103 • Output DDR Propagation Delays (T <sub>J</sub> = 115°C)                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

|                                | Added values for minimum pulse width and removed the FRMAX row from Table 2-108 through Table 2-115 in the "Global Tree Timing Characteristics" section. Use the software to determine the FRMAX for the device you are using (SAR 36966).                                                                                                                                                                                                                                           | 2-76            |

|                                | SRAM collision data was added to Table 2-117 $\bullet$ RAM4K9 through Table 2-120 $\bullet$ RAM512X18. Maximum frequency, F <sub>MAX</sub> , was updated in Table 2-118 $\bullet$ RAM512X18 (SAR 40859).                                                                                                                                                                                                                                                                             | 2-86 to<br>2-89 |

|                                | The "VMVx I/O Supply Voltage (quiet)" section was revised. The sentence, "Within the package, the VMV plane is decoupled from the simultaneous switching noise originating from the output buffer VCCI domain" was replaced with, "Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks" (SAR 38323). VMV pins must be connected to the corresponding VCCI pins, as noted in the "VMVx I/O Supply Voltage (quiet)" section, for an ESD enhancement. | 3-1             |

|                                | Libero Integrated Design Environment (IDE) was changed to Libero Systeom-on-Chip (SoC) throughout the document (SAR 40266).                                                                                                                                                                                                                                                                                                                                                          | N/A             |

| Revision 3<br>(September 2012) | The "Security" section was modified to clarify that Microsemi does not support read-back of programmed data.                                                                                                                                                                                                                                                                                                                                                                         | 1-1             |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.