Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 147456                                                                    |

| Number of I/O                  | 97                                                                        |

| Number of Gates                | 1000000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 125°C (TA)                                                        |

| Package / Case                 | 144-LBGA                                                                  |

| Supplier Device Package        | 144-FPBGA (13x13)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p1000-1fg144t |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# I/Os Per Package

| ProASIC3 Devices | A3P060                            | A3P125 | A3F                           | A3P1000                   |                               |                           |   |   |     |    |     |    |

|------------------|-----------------------------------|--------|-------------------------------|---------------------------|-------------------------------|---------------------------|---|---|-----|----|-----|----|

|                  |                                   |        | 1/0 1                         | уре                       |                               |                           |   |   |     |    |     |    |

| Package          | Single-Ended I/O Single-Ended I/O |        | Single-Ended I/O <sup>2</sup> | Differential<br>I/O Pairs | Single-Ended I/O <sup>2</sup> | Differential<br>I/O Pairs |   |   |     |    |     |    |

| VQ100            | 71                                | 71     | 68                            | 13                        | -                             | -                         |   |   |     |    |     |    |

| FG144            | 96                                | 97     | 97 24                         |                           | 97                            | 25                        |   |   |     |    |     |    |

| FG256            | _                                 | _      | _                             | _                         | _                             | -                         | _ | - | 157 | 38 | 177 | 44 |

| FG484            | _                                 | _      | _                             | _                         | 300                           | 74                        |   |   |     |    |     |    |

| QNG132           | _                                 | 84     | 87                            | 19                        | -                             | _                         |   |   |     |    |     |    |

#### Notes:

- 1. When considering migrating your design to a lower- or higher-density device, refer to the ProASIC3 FPGA Fabric User's Guide to ensure complying with design and board migration requirements.

- Each used differential I/O pair reduces the number of available single-ended I/Os by two.

FG256 and FG484 are footprint-compatible packages.

# **Automotive ProASIC3 Device Status**

| Automotive ProASIC3 Devices | Status     |

|-----------------------------|------------|

| A3P060                      | Production |

| A3P125                      | Production |

| A3P250                      | Production |

| A3P1000                     | Production |

Revision 5

# **Calculating Power Dissipation**

### **Quiescent Supply Current**

Table 2-6 • Quiescent Supply Current Characteristics

|                                      | A3P060 | A3P125 | A3P250 | A3P1000 |

|--------------------------------------|--------|--------|--------|---------|

| Typical (25°C)                       | 2 mA   | 2 mA   | 3 mA   | 8 mA    |

| Maximum (Automotive Grade 1) – 135°C | 53 mA  | 53 mA  | 106 mA | 265 mA  |

| Maximum (Automotive Grade 2) – 115°C | 26 mA  | 26 mA  | 53 mA  | 131 mA  |

Note: IDD Includes VCC, VPUMP, VCCI, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-7 and Table 2-10 on page 2-8.

### Power per I/O Pin

Table 2-7 • Summary of I/O Input Buffer Power (per pin) - Default I/O Software Settings 1 Applicable to Advanced I/O Banks

|                            | VMV (V) | Static Power<br>PDC2 (mW) <sup>1</sup> | Dynamic Power PAC9 (µW/MHz) <sup>2</sup> |

|----------------------------|---------|----------------------------------------|------------------------------------------|

| Single-Ended               |         |                                        |                                          |

| 3.3 V LVTTL / 3.3 V LVCMOS | 3.3     | -                                      | 16.69                                    |

| 2.5 V LVCMOS               | 2.5     | -                                      | 5.12                                     |

| 1.8 V LVCMOS               | 1.8     | _                                      | 2.13                                     |

| 1.5 V LVCMOS (JESD8-11)    | 1.5     | _                                      | 1.45                                     |

| 3.3 V PCI                  | 3.3     | -                                      | 18.11                                    |

| 3.3 V PCI-X                | 3.3     | -                                      | 18.11                                    |

| Differential               |         | •                                      |                                          |

| LVDS                       | 2.5     | 2.26                                   | 1.20                                     |

| LVPECL                     | 3.3     | 5.72                                   | 1.87                                     |

2-6 Revision 5

<sup>1.</sup>  $P_{DC2}$  is the static power (where applicable) measured on VMV. 2.  $P_{AC9}$  is the total dynamic power measured on  $V_{CC}$  and VMV.

Table 2-10 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings <sup>1</sup>

Applicable to Standard Plus I/O Banks

|                               | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC3 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (μW/MHz) <sup>3</sup> |

|-------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Single-Ended                  |                        |          |                                        |                                              |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 35                     | 3.3      | -                                      | 452.67                                       |

| 2.5 V LVCMOS                  | 35                     | 2.5      | _                                      | 258.32                                       |

| 1.8 V LVCMOS                  | 35                     | 1.8      | _                                      | 133.59                                       |

| 1.5 V LVCMOS<br>(JESD8-11)    | 35                     | 1.5      | -                                      | 92.84                                        |

| 3.3 V PCI                     | 10                     | 3.3      | _                                      | 184.92                                       |

| 3.3 V PCI-X                   | 10                     | 3.3      | _                                      | 184.92                                       |

#### Notes:

- Dynamic power consumption is given for standard load and software default drive strength and output slew.

- 2. PDC3 is the static power (where applicable) measured on VMV.

- 3. PAC10 is the total dynamic power measured on VCCI and VMV.

2-8 Revision 5

#### I/O Output Buffer Contribution—POUTPUTS

$P_{OUTPUTS} = N_{OUTPUTS} * \alpha_2 / 2 * \beta_1 * PAC10 * F_{CLK}$

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-12.

$\beta_1$  is the I/O buffer enable rate—guidelines are provided in Table 2-13 on page 2-12.

F<sub>CLK</sub> is the global clock signal frequency.

#### RAM Contribution—P<sub>MEMORY</sub>

$P_{MEMORY}$  = PAC11 \*  $N_{BLOCKS}$  \*  $F_{READ-CLOCK}$  \*  $\beta_2$  + PAC12 \*  $N_{BLOCK}$  \*  $F_{WRITE-CLOCK}$  \*  $\beta_3$

N<sub>BLOCKS</sub> is the number of RAM blocks used in the design.

F<sub>READ-CLOCK</sub> is the memory read clock frequency.

$eta_2$  is the RAM enable rate for read operations.

F<sub>WRITE-CLOCK</sub> is the memory write clock frequency.

$\beta_3$  is the RAM enable rate for write operations—guidelines are provided in Table 2-13 on page 2-12.

#### PLL Contribution—P<sub>PLL</sub>

$P_{PLL}$  = PAC13 + PAC14 \*  $F_{CLKOUT}$

F<sub>CLKIN</sub> is the input clock frequency.

F<sub>CLKOUT</sub> is the output clock frequency. 1

#### Guidelines

#### **Toggle Rate Definition**

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that this net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100% because all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ..

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + . . . + 0.78125%) / 8

#### **Enable Rate Definition**

Output enable rate is the average percentage of time during which tristate outputs are enabled. When nontristate output buffers are used, the enable rate should be 100%.

Table 2-12 • Toggle Rate Guidelines Recommended for Power Calculation

| Component  | Definition                       | Guideline |

|------------|----------------------------------|-----------|

| $\alpha_1$ | Toggle rate of VersaTile outputs | 10%       |

| $\alpha_2$ | I/O buffer toggle rate           | 10%       |

The PLL dynamic contribution depends on the input clock frequency, the number of output clock signals generated by the PLL, and the frequency of each output clock. If a PLL is used to generate more than one output clock, include each output clock in the formula by adding its corresponding contribution (P<sub>AC14</sub> \* F<sub>CLKOUT</sub> product) to the total PLL contribution.

Table 2-29 • I/O Short Currents IOSH/IOSL

Applicable to Standard Plus I/O Banks

|                            | Drive Strength              | I <sub>OSL</sub> (mA)* | I <sub>OSH</sub> (mA)* |

|----------------------------|-----------------------------|------------------------|------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA                        | 27                     | 25                     |

|                            | 4 mA                        | 27                     | 25                     |

|                            | 6 mA                        | 54                     | 51                     |

|                            | 8 mA                        | 54                     | 51                     |

|                            | 12 mA                       | 109                    | 103                    |

|                            | 16 mA                       | 109                    | 103                    |

| 2.5 V LVCMOS               | 2 mA                        | 18                     | 16                     |

|                            | 6 mA                        | 37                     | 32                     |

|                            | 12 mA                       | 74                     | 65                     |

| 1.8 V LVCMOS               | 2 mA                        | 11                     | 9                      |

|                            | 4 mA                        | 22                     | 17                     |

|                            | 6 mA                        | 44                     | 35                     |

|                            | 8 mA                        | 44                     | 35                     |

| 1.5 V LVCMOS               | 2 mA                        | 16                     | 13                     |

|                            | 4 mA                        | 33                     | 25                     |

| 3.3 V PCI/PCI-X            | Per PCI/PCI-X specification | 109                    | 103                    |

Note:  $*T_J = 100$ °C

The length of time an I/O can withstand  $I_{OSH}/I_{OSL}$  events depends on the junction temperature. The reliability data below is based on a 3.3 V, 12 mA I/O setting, which is the worst case for this type of analysis.

For example, at 110°C, the short current condition would have to be sustained for more than three months to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

Table 2-30 • Duration of Short Circuit Event before Failure

| Temperature | Time before Failure |

|-------------|---------------------|

| -40°C       | > 20 years          |

| 0°C         | > 20 years          |

| 25°C        | > 20 years          |

| 70°C        | 5 years             |

| 85°C        | 2 years             |

| 100°C       | 6 months            |

| 110°C       | 3 months            |

| 125°C       | 25 days             |

| 135°        | 12 days             |

#### **Timing Characteristics**

Table 2-46 • 2.5 V LVCMOS High Slew

Automotive-Case Conditions: T<sub>J</sub> = 135°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

Applicable to Advanced I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | STD            | 0.64              | 9.69            | 0.05             | 1.45            | 0.46              | 8.76            | 9.69            | 1.48            | 1.25            | 11.26            | 12.187           | ns    |

|                   | -1             | 0.55              | 8.24            | 0.04             | 1.23            | 0.39              | 7.45            | 8.24            | 1.48            | 1.25            | 9.58             | 10.367           | ns    |

| 6 mA              | STD            | 0.64              | 5.78            | 0.05             | 1.45            | 0.46              | 5.63            | 5.78            | 1.68            | 1.62            | 8.13             | 8.277            | ns    |

|                   | -1             | 0.55              | 4.91            | 0.04             | 1.23            | 0.39              | 4.79            | 4.91            | 1.69            | 1.63            | 6.92             | 7.04             | ns    |

| 12 mA             | STD            | 0.64              | 3.98            | 0.05             | 1.45            | 0.46              | 4.05            | 3.84            | 1.82            | 1.86            | 6.55             | 6.338            | ns    |

|                   | -1             | 0.55              | 3.39            | 0.04             | 1.23            | 0.39              | 3.45            | 3.27            | 1.83            | 1.86            | 5.58             | 5.392            | ns    |

| 16 mA             | STD            | 0.64              | 3.75            | 0.05             | 1.45            | 0.46              | 1.85            | 1.69            | 3.76            | 3.97            | 3.06             | 2.926            | ns    |

|                   | -1             | 0.55              | 3.19            | 0.04             | 1.23            | 0.39              | 1.85            | 1.69            | 3.20            | 3.38            | 3.06             | 2.929            | ns    |

| 24 mA             | STD            | 0.64              | 3.45            | 0.05             | 1.45            | 0.46              | 1.70            | 1.35            | 3.84            | 4.47            | 2.92             | 2.585            | ns    |

|                   | -1             | 0.55              | 2.94            | 0.04             | 1.23            | 0.39              | 1.71            | 1.35            | 3.27            | 3.80            | 2.92             | 2.586            | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

Table 2-47 • 2.5 V LVCMOS Low Slew

Automotive-Case Conditions: T<sub>J</sub> = 135°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

Applicable to Advanced I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | STD            | 0.64              | 12.12           | 0.05             | 1.45            | 0.46              | 12.54           | 12.74           | 1.48            | 1.19            | 15.04            | 15.243           | ns    |

|                   | -1             | 0.55              | 10.31           | 0.04             | 1.23            | 0.39              | 10.67           | 10.84           | 1.48            | 1.20            | 12.80            | 12.966           | ns    |

| 6 mA              | STD            | 0.64              | 8.24            | 0.05             | 1.45            | 0.46              | 9.07            | 8.74            | 1.68            | 1.57            | 11.57            | 11.237           | ns    |

|                   | -1             | 0.55              | 7.01            | 0.04             | 1.23            | 0.39              | 7.71            | 7.43            | 1.69            | 1.57            | 9.84             | 9.559            | ns    |

| 12 mA             | STD            | 0.64              | 6.91            | 0.05             | 1.45            | 0.46              | 7.04            | 6.62            | 1.82            | 1.80            | 9.54             | 9.117            | ns    |

|                   | -1             | 0.55              | 5.88            | 0.04             | 1.23            | 0.39              | 5.99            | 5.63            | 1.83            | 1.80            | 8.11             | 7.756            | ns    |

| 16 mA             | STD            | 0.64              | 6.44            | 0.05             | 1.45            | 0.46              | 6.56            | 6.18            | 1.86            | 1.86            | 9.06             | 8.678            | ns    |

|                   | -1             | 0.55              | 5.48            | 0.04             | 1.23            | 0.39              | 5.58            | 5.26            | 1.86            | 1.86            | 7.71             | 7.382            | ns    |

| 24 mA             | STD            | 0.64              | 6.16            | 0.05             | 1.45            | 0.46              | 6.15            | 6.16            | 1.90            | 2.10            | 8.65             | 8.657            | ns    |

|                   | -1             | 0.55              | 5.24            | 0.04             | 1.23            | 0.39              | 5.23            | 5.24            | 1.90            | 2.10            | 7.36             | 7.364            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

2-34 Revision 5

Table 2-50 • 2.5 V LVCMOS High Slew

Automotive-Case Conditions: T<sub>J</sub> = 115°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

Applicable to Advanced I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | STD            | 0.63              | 9.37            | 0.05             | 1.40            | 0.45              | 8.47            | 9.37            | 1.43            | 1.21            | 10.89            | 11.79            | ns    |

|                   | -1             | 0.53              | 7.97            | 0.04             | 1.19            | 0.38              | 7.21            | 7.97            | 1.43            | 1.21            | 9.27             | 10.03            | ns    |

| 6 mA              | STD            | 0.63              | 5.59            | 0.05             | 1.40            | 0.45              | 5.45            | 5.59            | 1.63            | 1.57            | 7.87             | 8.01             | ns    |

|                   | -1             | 0.53              | 4.75            | 0.04             | 1.19            | 0.38              | 4.63            | 4.75            | 1.63            | 1.57            | 6.69             | 6.81             | ns    |

| 12 mA             | STD            | 0.63              | 3.85            | 0.05             | 1.40            | 0.45              | 3.92            | 3.71            | 1.77            | 1.80            | 6.34             | 6.13             | ns    |

|                   | -1             | 0.53              | 3.28            | 0.04             | 1.19            | 0.38              | 3.34            | 3.16            | 1.77            | 1.80            | 5.39             | 5.22             | ns    |

| 16 mA             | STD            | 0.63              | 3.63            | 0.05             | 1.40            | 0.45              | 1.79            | 1.64            | 3.64            | 3.84            | 2.96             | 2.83             | ns    |

|                   | -1             | 0.53              | 3.08            | 0.04             | 1.19            | 0.38              | 1.79            | 1.64            | 3.09            | 3.27            | 2.96             | 2.83             | ns    |

| 24 mA             | STD            | 0.63              | 3.34            | 0.05             | 1.40            | 0.45              | 1.65            | 1.31            | 3.72            | 4.32            | 2.82             | 2.50             | ns    |

|                   | -1             | 0.53              | 2.84            | 0.04             | 1.19            | 0.38              | 1.65            | 1.31            | 3.16            | 3.68            | 2.82             | 2.50             | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

Table 2-51 • 2.5 V LVCMOS Low Slew

Automotive-Case Conditions: TJ = 115°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

Applicable to Advanced I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | STD            | 0.63              | 11.73           | 0.05             | 1.40            | 0.45              | 12.14           | 12.33           | 1.43            | 1.16            | 14.55            | 14.75            | ns    |

|                   | -1             | 0.53              | 9.98            | 0.04             | 1.19            | 0.38              | 10.32           | 10.49           | 1.43            | 1.16            | 12.38            | 12.55            | ns    |

| 6 mA              | STD            | 0.63              | 7.97            | 0.05             | 1.40            | 0.45              | 8.77            | 8.45            | 1.63            | 1.51            | 11.19            | 10.87            | ns    |

|                   | -1             | 0.53              | 6.78            | 0.04             | 1.19            | 0.38              | 7.46            | 7.19            | 1.63            | 1.52            | 9.52             | 9.25             | ns    |

| 12 mA             | STD            | 0.63              | 6.68            | 0.05             | 1.40            | 0.45              | 6.81            | 6.40            | 1.77            | 1.74            | 9.23             | 8.82             | ns    |

|                   | -1             | 0.53              | 5.69            | 0.04             | 1.19            | 0.38              | 5.79            | 5.45            | 1.77            | 1.74            | 7.85             | 7.50             | ns    |

| 16 mA             | STD            | 0.63              | 6.24            | 0.05             | 1.40            | 0.45              | 6.35            | 5.98            | 1.80            | 1.80            | 8.77             | 8.40             | ns    |

|                   | -1             | 0.53              | 5.30            | 0.04             | 1.19            | 0.38              | 5.40            | 5.08            | 1.80            | 1.80            | 7.46             | 7.14             | ns    |

| 24 mA             | STD            | 0.63              | 5.96            | 0.05             | 1.40            | 0.45              | 5.95            | 5.96            | 1.84            | 2.03            | 8.37             | 8.38             | ns    |

|                   | -1             | 0.53              | 5.07            | 0.04             | 1.19            | 0.38              | 5.06            | 5.07            | 1.84            | 2.03            | 7.12             | 7.12             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

2-36 Revision 5

#### 1.8 V LVCMOS

Low-voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 1.8 V input buffer and a push-pull output buffer.

Table 2-54 • Minimum and Maximum DC Input and Output Levels

Applicable to Advanced I/O Banks

| 1.8 V<br>LVCMOS   |           | VIL         | VIH                     |           | VOL       | VOH         | I <sub>OL</sub> | I <sub>OH</sub> | I <sub>OSL</sub>        | I <sub>osh</sub>        | I <sub>IL</sub> | I <sub>IH</sub> |

|-------------------|-----------|-------------|-------------------------|-----------|-----------|-------------|-----------------|-----------------|-------------------------|-------------------------|-----------------|-----------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V               | Max.<br>V | Max.<br>V | Min.<br>V   | mA              | mΑ              | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA <sup>2</sup> | μ <b>Α</b> 2    |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI             | 3.6       | 0.45      | VCCI - 0.45 | 2               | 2               | 11                      | 9                       | 10              | 10              |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI             | 3.6       | 0.45      | VCCI - 0.45 | 4               | 4               | 22                      | 17                      | 10              | 10              |

| 6 mA              | -0.3      | 0.35 * VCCI | 0.65 * V <sub>CCI</sub> | 3.6       | 0.45      | VCCI - 0.45 | 6               | 6               | 44                      | 35                      | 10              | 10              |

| 8 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI             | 3.6       | 0.45      | VCCI - 0.45 | 8               | 8               | 51                      | 45                      | 10              | 10              |

| 12 mA             | -0.3      | 0.35 * VCCI | 0.65 * VCCI             | 3.6       | 0.45      | VCCI - 0.45 | 12              | 12              | 74                      | 91                      | 10              | 10              |

| 16 mA             | -0.3      | 0.35 * VCCI | 0.65 * VCCI             | 3.6       | 0.45      | VCCI - 0.45 | 16              | 16              | 74                      | 91                      | 10              | 10              |

#### Notes:

- 1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 2. Currents are measured at 125°C junction temperature.

- 3. Software default selection highlighted in gray.

Table 2-55 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O I/O Banks

| 1.8 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL       | VOH         | l <sub>OL</sub> | I <sub>OH</sub> | I <sub>OSL</sub>        | I <sub>osh</sub>        | Ι <sub>ΙL</sub> | Ι <sub>ΙΗ</sub> |

|-------------------|-----------|-------------|-------------|-----------|-----------|-------------|-----------------|-----------------|-------------------------|-------------------------|-----------------|-----------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V   | mA              | mA              | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μ <b>Α</b> 2    | μA <sup>2</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 2               | 2               | 11                      | 9                       | 10              | 10              |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 4               | 4               | 22                      | 17                      | 10              | 10              |

| 6 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 6               | 6               | 44                      | 35                      | 10              | 10              |

| 8 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 8               | 8               | 44                      | 35                      | 10              | 10              |

#### Notes:

- 1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 2. Currents are measured at 125°C junction temperature.

- 3. Software default selection highlighted in gray.

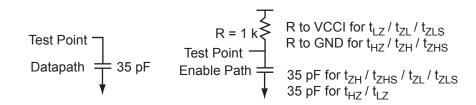

Figure 2-9 • AC Loading

Table 2-56 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.8            | 0.9                  | 35                     |

Note: \*Measuring point =  $V_{trip.}$  See Table 2-18 on page 2-17 for a complete table of trip points.

2-38 Revision 5

Table 2-97 • Output Enable Register Propagation Delays

Automotive-Case Conditions: T<sub>J</sub> = 115°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | -1   | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.53 | 0.62 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.37 | 0.44 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.52 | 0.61 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.79 | 0.93 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 0.79 | 0.93 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.27 | 0.31 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.27 | 0.31 | ns    |

| t <sub>OEWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.25 | 0.30 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.25 | 0.30 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.41 | 0.48 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.37 | 0.43 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

2-62 Revision 5

Automotive ProASIC3 Flash Family FPGAs

Table 2-100 • Input DDR Propagation Delays Automotive-Case Conditions:  $T_J$  = 115°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                          | -1   | Std. | Units |

|-------------------------|------------------------------------------------------|------|------|-------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR for Input DDR                    | 0.33 | 0.38 | ns    |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF for Input DDR                    | 0.46 | 0.54 | ns    |

| t <sub>DDRISUD</sub>    | Data Setup for Input DDR                             | 0.34 | 0.40 | ns    |

| t <sub>DDRIHD</sub>     | Data Hold for Input DDR                              | 0.00 | 0.00 | ns    |

| t <sub>DDRICLR2Q1</sub> | Asynchronous Clear-to-Out Out_QR for Input DDR       | 0.55 | 0.65 | ns    |

| t <sub>DDRICLR2Q2</sub> | Asynchronous Clear-to-Out Out_QF for Input DDR       | 0.68 | 0.80 | ns    |

| t <sub>DDRIREMCLR</sub> | Asynchronous Clear Removal Time for Input DDR        | 0.00 | 0.00 | ns    |

| t <sub>DDRIRECCLR</sub> | Asynchronous Clear Recovery Time for Input DDR       | 0.27 | 0.31 | ns    |

| t <sub>DDRIWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for Input DDR | 0.25 | 0.30 | ns    |

| t <sub>DDRICKMPWH</sub> | Clock Minimum Pulse Width High for Input DDR         | 0.41 | 0.48 | ns    |

| t <sub>DDRICKMPWL</sub> | Clock Minimum Pulse Width Low for Input DDR          | 0.37 | 0.43 | ns    |

| F <sub>DDRIMAX</sub>    | Maximum Frequency for Input DDR                      | 309  | 263  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

Table 2-110 • A3P125 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 135°C, VCC = 1.425 V

|                      |                                           | _                 | -1 St             |                   | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.93              | 1.22              | 1.09              | 1.43              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.92              | 1.26              | 1.08              | 1.49              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.80              |                   | 0.94              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.98              |                   | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.35              |                   | 0.41              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

Table 2-111 • A3P125 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 115°C, VCC = 1.425 V

|                      |                                           | -1 S              |                   | td.               |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.90              | 1.19              | 1.06              | 1.40              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.90              | 1.23              | 1.05              | 1.45              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.80              |                   | 0.94              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.98              |                   | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.34              |                   | 0.40              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

Table 2-112 • A3P250 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 135°C, VCC = 1.425 V

|                      |                                           | -                 | -1                |                   | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.96              | 1.25              | 1.13              | 1.47              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.94              | 1.28              | 1.10              | 1.51              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.80              |                   | 0.94              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.98              |                   | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.35              |                   | 0.41              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

Table 2-113 • A3P250 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 115°C, VCC = 1.425 V

|                      |                                           | <b>-1</b>         |                   | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.94              | 1.22              | 1.10              | 1.44              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.92              | 1.25              | 1.08              | 1.47              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.80              |                   | 0.94              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.98              |                   | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.34              |                   | 0.40              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

2-78 Revision 5

### **JTAG 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/O Characteristics" section on page 2-12 for more details.

### **Timing Characteristics**

Table 2-125 • JTAG 1532

Commercial-Case Conditions:  $T_J = 70$ °C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | -2 | -1 | Std. | Units |

|----------------------|-----------------------------|----|----|------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  |    |    |      | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   |    |    |      | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time |    |    |      | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  |    |    |      | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       |    |    |      | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       |    |    |      | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 20 | 20 | 20   | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         |    |    |      | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        |    |    |      | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        |    |    |      | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-5 on page 2-5 for derating values.

# 3 - Pin Descriptions and Packaging

## **Supply Pins**

#### GND Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

#### GNDQ Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ must always be connected to GND on the board.

#### VCC Core Supply Voltage

Supply voltage to the FPGA core, nominally 1.5 V. VCC is required for powering the JTAG state machine in addition to VJTAG. Even when a device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the device.

#### VCCIBx I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are up to four I/O banks on Automotive ProASIC3 devices, plus a dedicated VJTAG bank. Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCI pins tied to GND.

#### VMVx I/O Supply Voltage (quiet)

Quiet supply voltage to the input buffers of each I/O bank. *x* is the bank number. Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks. This minimizes the noise transfer within the package and improves input signal integrity. Each bank must have at least one VMV connection, and no VMV should be left unconnected. All I/Os in a bank run off the same VMVx supply. VMV is used to provide a quiet supply voltage to the input buffers of each I/O bank. VMVx can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VMV pins tied to GND. VMV and VCCI should be at the same voltage within a given I/O bank. Used VMV pins must be connected to the corresponding VCCI pins of the same bank (i.e., VMV0 to VCCIB0, VMV1 to VCCIB1, etc.).

#### VCCPLA/B/C/D/E/F PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V.

When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Microsemi recommends tying VCCPLx to VCC and using proper filtering circuits to decouple VCC noise from the PLLs. Refer to the PLL Power Supply Decoupling section of the "Clock Conditioning Circuits in IGLOO and ProASIC3 Devices" chapter of the *Automotive ProASIC3 FPGA Fabric User's Guide* for a complete board solution for the PLL analog power supply and ground.

There is one VCCPLF pin on Automotive ProASIC3 devices.

#### VCOMPLA/B/C/D/E/F PLL Ground

Ground to analog PLL power supplies. When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground.

There is one VCOMPLF pin on Automotive ProASIC3 devices.

#### VJTAG JTAG Supply Voltage

Automotive ProASIC3 devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is

Pin Descriptions and Packaging

## **Special Function Pins**

NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

DC Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

## **Packaging**

Semiconductor technology is constantly shrinking in size while growing in capability and functional integration. To enable next-generation silicon technologies, semiconductor packages have also evolved to provide improved performance and flexibility.

Microsemi consistently delivers packages that provide the necessary mechanical and environmental protection to ensure consistent reliability and performance. Microsemi IC packaging technology efficiently supports high-density FPGAs with large-pin-count Ball Grid Arrays (BGAs), but is also flexible enough to accommodate stringent form factor requirements for Chip Scale Packaging (CSP). In addition, Actel offers a variety of packages designed to meet your most demanding application and economic requirements for today's embedded and mobile systems.

### **Related Documents**

#### **User's Guides**

Automotive ProASIC FPGA Fabric User's Guide

http://www.microsemi.com/soc/documents/PA3 Auto UG.pdf

### **Packaging**

The following documents provide packaging information and device selection for low power flash devices.

#### Product Catalog

http://www.microsmei.com/soc/documents/ProdCat PIB.pdf

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

### Package Mechanical Drawings

http://www.microsemi.com/soc/documents/PckgMechDrwngs.pdf

This document contains the package mechanical drawings for all packages currently or previously supplied by Actel. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials: http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

3-4 Revision 5

### Package Pin Assignments

| FG144      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A3P060 Function |  |  |  |

| K1         | GEB0/IO74RSB1   |  |  |  |

| K2         | GEA1/IO73RSB1   |  |  |  |

| K3         | GEA0/IO72RSB1   |  |  |  |

| K4         | GEA2/IO71RSB1   |  |  |  |

| K5         | IO65RSB1        |  |  |  |

| K6         | IO64RSB1        |  |  |  |

| K7         | GND             |  |  |  |

| K8         | IO57RSB1        |  |  |  |

| K9         | GDC2/IO56RSB1   |  |  |  |

| K10        | GND             |  |  |  |

| K11        | GDA0/IO50RSB0   |  |  |  |

| K12        | GDB0/IO48RSB0   |  |  |  |

| L1         | GND             |  |  |  |

| L2         | VMV1            |  |  |  |

| L3         | GEB2/IO70RSB1   |  |  |  |

| L4         | IO67RSB1        |  |  |  |

| L5         | VCCIB1          |  |  |  |

| L6         | IO62RSB1        |  |  |  |

| L7         | IO59RSB1        |  |  |  |

| L8         | IO58RSB1        |  |  |  |

| L9         | TMS             |  |  |  |

| L10        | VJTAG           |  |  |  |

| L11        | VMV1            |  |  |  |

| L12        | TRST            |  |  |  |

| M1         | GNDQ            |  |  |  |

| M2         | GEC2/IO69RSB1   |  |  |  |

| M3         | IO68RSB1        |  |  |  |

| M4         | IO66RSB1        |  |  |  |

| M5         | IO63RSB1        |  |  |  |

| M6         | IO61RSB1        |  |  |  |

| M7         | IO60RSB1        |  |  |  |

| M8         | NC              |  |  |  |

| M9         | TDI             |  |  |  |

| M10        | VCCIB1          |  |  |  |

| M11        | VPUMP           |  |  |  |

| M12        | GNDQ            |  |  |  |

4-12 Revision 5

Package Pin Assignments

| FG256      |                  | FG256      |                  |            | FG256            |  |

|------------|------------------|------------|------------------|------------|------------------|--|

| Pin Number | A3P1000 Function | Pin Number | A3P1000 Function | Pin Number | A3P1000 Function |  |

| G13        | GCC1/IO91PPB1    | K1         | GFC2/IO204PDB3   | M5         | VMV3             |  |

| G14        | IO90NPB1         | K2         | IO204NDB3        | M6         | VCCIB2           |  |

| G15        | IO88PDB1         | K3         | IO203NDB3        | M7         | VCCIB2           |  |

| G16        | IO88NDB1         | K4         | IO203PDB3        | M8         | IO147RSB2        |  |

| H1         | GFB0/IO208NPB3   | K5         | VCCIB3           | M9         | IO136RSB2        |  |

| H2         | GFA0/IO207NDB3   | K6         | VCC              | M10        | VCCIB2           |  |

| НЗ         | GFB1/IO208PPB3   | K7         | GND              | M11        | VCCIB2           |  |

| H4         | VCOMPLF          | K8         | GND              | M12        | VMV2             |  |

| H5         | GFC0/IO209NPB3   | K9         | GND              | M13        | IO110NDB1        |  |

| H6         | VCC              | K10        | GND              | M14        | GDB1/IO112PPB1   |  |

| H7         | GND              | K11        | VCC              | M15        | GDC1/IO111PDB1   |  |

| H8         | GND              | K12        | VCCIB1           | M16        | IO107NDB1        |  |

| H9         | GND              | K13        | IO95NPB1         | N1         | IO194PSB3        |  |

| H10        | GND              | K14        | IO100NPB1        | N2         | IO192PPB3        |  |

| H11        | VCC              | K15        | IO102NDB1        | N3         | GEC1/IO190PPB3   |  |

| H12        | GCC0/IO91NPB1    | K16        | IO102PDB1        | N4         | IO192NPB3        |  |

| H13        | GCB1/IO92PPB1    | L1         | IO202NDB3        | N5         | GNDQ             |  |

| H14        | GCA0/IO93NPB1    | L2         | IO202PDB3        | N6         | GEA2/IO187RSB2   |  |

| H15        | IO96NPB1         | L3         | IO196PPB3        | N7         | IO161RSB2        |  |

| H16        | GCB0/IO92NPB1    | L4         | IO193PPB3        | N8         | IO155RSB2        |  |

| J1         | GFA2/IO206PSB3   | L5         | VCCIB3           | N9         | IO141RSB2        |  |

| J2         | GFA1/IO207PDB3   | L6         | GND              | N10        | IO129RSB2        |  |

| J3         | VCCPLF           | L7         | VCC              | N11        | IO124RSB2        |  |

| J4         | IO205NDB3        | L8         | VCC              | N12        | GNDQ             |  |

| J5         | GFB2/IO205PDB3   | L9         | VCC              | N13        | IO110PDB1        |  |

| J6         | VCC              | L10        | VCC              | N14        | VJTAG            |  |

| J7         | GND              | L11        | GND              | N15        | GDC0/IO111NDB1   |  |

| J8         | GND              | L12        | VCCIB1           | N16        | GDA1/IO113PDB1   |  |

| J9         | GND              | L13        | GDB0/IO112NPB1   | P1         | GEB1/IO189PDB3   |  |

| J10        | GND              | L14        | IO106NDB1        | P2         | GEB0/IO189NDB3   |  |

| J11        | VCC              | L15        | IO106PDB1        | P3         | VMV2             |  |

| J12        | GCB2/IO95PPB1    | L16        | IO107PDB1        | P4         | IO179RSB2        |  |

| J13        | GCA1/IO93PPB1    | M1         | IO197NSB3        | P5         | IO171RSB2        |  |

| J14        | GCC2/IO96PPB1    | M2         | IO196NPB3        | P6         | IO165RSB2        |  |

| J15        | IO100PPB1        | M3         | IO193NPB3        | P7         | IO159RSB2        |  |

| J16        | GCA2/IO94PSB1    | M4         | GEC0/IO190NPB3   | P8         | IO151RSB2        |  |

4-24 Revision 5

| FG256      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | A3P1000 Function |  |  |  |

| P9         | IO137RSB2        |  |  |  |

| P10        | IO134RSB2        |  |  |  |

| P11        | IO128RSB2        |  |  |  |

| P12        | VMV1             |  |  |  |

| P13        | TCK              |  |  |  |

| P14        | VPUMP            |  |  |  |

| P15        | TRST             |  |  |  |

| P16        | GDA0/IO113NDB1   |  |  |  |

| R1         | GEA1/IO188PDB3   |  |  |  |

| R2         | GEA0/IO188NDB3   |  |  |  |

| R3         | IO184RSB2        |  |  |  |

| R4         | GEC2/IO185RSB2   |  |  |  |

| R5         | IO168RSB2        |  |  |  |

| R6         | IO163RSB2        |  |  |  |

| R7         | IO157RSB2        |  |  |  |

| R8         | IO149RSB2        |  |  |  |

| R9         | IO143RSB2        |  |  |  |

| R10        | IO138RSB2        |  |  |  |

| R11        | IO131RSB2        |  |  |  |

| R12        | IO125RSB2        |  |  |  |

| R13        | GDB2/IO115RSB2   |  |  |  |

| R14        | TDI              |  |  |  |

| R15        | GNDQ             |  |  |  |

| R16        | TDO              |  |  |  |

| T1         | GND              |  |  |  |

| T2         | IO183RSB2        |  |  |  |

| Т3         | GEB2/IO186RSB2   |  |  |  |

| T4         | IO172RSB2        |  |  |  |

| T5         | IO170RSB2        |  |  |  |

| T6         | IO164RSB2        |  |  |  |

| T7         | IO158RSB2        |  |  |  |

| Т8         | IO153RSB2        |  |  |  |

| Т9         | IO142RSB2        |  |  |  |

| T10        | IO135RSB2        |  |  |  |

| T11        | IO130RSB2        |  |  |  |

| T12        | GDC2/IO116RSB2   |  |  |  |

| FG256      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | A3P1000 Function |  |  |  |

| T13        | IO120RSB2        |  |  |  |

| T14        | GDA2/IO114RSB2   |  |  |  |

| T15        | TMS              |  |  |  |

| T16        | GND              |  |  |  |