Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Active                                                                       |

| Number of LABs/CLBs            | 1484                                                                         |

| Number of Logic Elements/Cells | 5936                                                                         |

| Total RAM Bits                 | 184320                                                                       |

| Number of I/O                  | 37                                                                           |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 125°C (TJ)                                                           |

| Package / Case                 | 81-VFBGA                                                                     |

| Supplier Device Package        | 81-CSFBGA (4.5x4.5)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lia-md6000-6mg81e |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Contents**

| Acronym        | ns in This Document                                                                                                       | 5  |

|----------------|---------------------------------------------------------------------------------------------------------------------------|----|

| 1. Ger         | neral Description                                                                                                         | 6  |

| 1.1.           | Features                                                                                                                  | 6  |

| 2. App         | plication Examples                                                                                                        | 7  |

| 2.1.           | 2:1 MIPI CSI-2 Image Sensor Aggregator Bridge                                                                             | 7  |

| 2.2.           | 1:2 MIPI DSI Display Interface Bridge                                                                                     | 8  |

| 2.3.           | FPD-Link/OpenLDI LVDS to MIPI DSI Display Interface Bridge                                                                | 9  |

| 2.4.           | MIPI DSI to FPD-Link/OpenLDI LVDS Display Interface Bridge                                                                |    |

| 2.5.           | CMOS to MIPI DSI Display Interface Bridge                                                                                 | 11 |

| 2.6.           | CMOS to MIPI CSI-2 Image Sensor Interface Bridge                                                                          |    |

| 2.7.           | MIPI DSI to CMOS Display Interface Bridge                                                                                 |    |

| 2.8.           | MIPI CSI-2 to CMOS Image Sensor Interface Bridge                                                                          |    |

| 2.9.           | SubLVDS to MIPI CSI-2 Image Sensor Interface Bridge                                                                       |    |

|                | duct Feature Summary                                                                                                      |    |

| 4. Arc         | hitecture Overview                                                                                                        |    |

| 4.1.           | MIPI D-PHY Blocks                                                                                                         |    |

| 4.2.           | Programmable I/O Banks                                                                                                    |    |

| 4.3.           | Programmable FPGA Fabric                                                                                                  |    |

| 4.3.           |                                                                                                                           |    |

| 4.3.           | · · · · · · · · · · · · · · · · · · ·                                                                                     |    |

| 4.3.           |                                                                                                                           |    |

| 4.4.           | System Resources                                                                                                          |    |

| 4.4.           |                                                                                                                           |    |

| 4.4.           |                                                                                                                           |    |

| 4.4.           |                                                                                                                           |    |

| 4.4.           |                                                                                                                           |    |

|                | and Switching Characteristics                                                                                             |    |

| 5.1.           | Absolute Maximum Ratings                                                                                                  |    |

| 5.2.           | Recommended Operating Conditions                                                                                          |    |

| 5.3.           | Preliminary Power Supply Ramp Rates                                                                                       |    |

| 5.4.           | Preliminary Power-On-Reset Voltage Levels                                                                                 |    |

| 5.5.           | ESD Performance                                                                                                           |    |

| 5.6.           | Preliminary DC Electrical Characteristics                                                                                 |    |

| 5.7.           | Preliminary CrossLink Supply Current                                                                                      |    |

| 5.8.           | Preliminary Power Management Unit (PMU) Timing                                                                            |    |

| 5.9.           | sysI/O Recommended Operating Conditions                                                                                   |    |

| 5.10.          | Preliminary sysI/O Single-Ended DC Electrical Characteristics  Preliminary sysI/O Differential Electrical Characteristics |    |

| 5.11.          |                                                                                                                           |    |

| 5.1            |                                                                                                                           |    |

| 5.1:<br>5.12.  | 1.2. Preliminary Hardened MIPI D-PHY I/OsPreliminary CrossLink Maximum General Purpose I/O Buffer Speed                   |    |

| 5.12.<br>5.13. | Preliminary CrossLink Maximum General Purpose 1/O Burier Speed  Preliminary CrossLink External Switching Characteristics  |    |

|                |                                                                                                                           |    |

| 5.14.<br>5.15. | Preliminary sysCLOCK PLL Timing Hardened MIPI D-PHY Performance                                                           |    |

| 5.15.<br>5.16. | Preliminary Internal Oscillators (HFOSC, LFOSC)                                                                           |    |

| 5.16.<br>5.17. | Preliminary Internal Oscillators (HFOSC, LFOSC)                                                                           |    |

| 5.17.<br>5.18. | CrossLink sysCONFIG Port Timing Specifications                                                                            |    |

| 5.16.<br>5.19. | Preliminary SRAM Configuration Time from NVCM                                                                             |    |

| 5.19.<br>5.20. | Switching Test Conditions                                                                                                 |    |

| 5.20.          | Switching rest conditions                                                                                                 | 39 |

### 2.4. MIPI DSI to FPD-Link/OpenLDI LVDS Display Interface Bridge

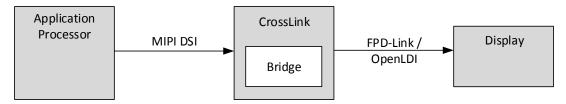

Figure 2.4 shows the block diagram for the MIPI DSI to FPD-Link/OpenLDI LVDS Display Interface Bridge. This solution bridges the MIPI DSI output from the application processor to a single or dual channel FPD-Link/OpenLDI LVDS display input.

Table 2.4 provides additional details on the application example, including input and output descriptions and device resource usage. The interface bridge is fully programmable, supporting both RGB666 and RGB888, variable number of LVDS data lanes, and data rates up to 1.2 Gb/s per lane input or 1.5 Gb/s per lane output. For details, refer to FPGA-IPUG-02003, MIPI DSI to OpenLDI/FPD-Link/LVDS Interface Bridge Soft IP User Guide.

Figure 2.4. MIPI DSI to FPD-Link/OpenLDI LVDS Display Interface Bridge

Table 2.4. MIPI DSI to FPD-Link/OpenLDI LVDS Display Interface Bridge Overview

| Application Example Details      |                                                                              |  |  |

|----------------------------------|------------------------------------------------------------------------------|--|--|

| January Trans                    | 1080p60, 24-bit RGB                                                          |  |  |

| Input Type                       | 4-Lane MIPI D-PHY @ ~900 Mb/s per lane                                       |  |  |

| Programmable Fabric Operation(s) | Bridge                                                                       |  |  |

| Outrout Tura                     | 1080p60, 24-bit RGB                                                          |  |  |

| Output Type                      | 2 Channels (2 x 4 Data Lanes and 2 x 1 Clock Lane) @ 74.25MHz FPD-Link Clock |  |  |

|                                  | Display Configuration                                                        |  |  |

| Additional System Functions      | Power and Reset Sequencing of Display                                        |  |  |

|                                  | Backlight PWM Control                                                        |  |  |

|                                  | Preliminary Example Device Resource Usage*                                   |  |  |

| Typical Power Consumption        | TBD mW                                                                       |  |  |

| Device I/O Used                  | 20 Programmable I/O; 1 x Hard D-PHY Quads                                    |  |  |

| Fabric Resources Used            | ~30% of LUT4; ~30% of EBR                                                    |  |  |

<sup>\*</sup>Note: For reference only – exact usage and power consumption depends on specific application parameters. Additional system functions are not included in resource usage. The typical power consumption estimate is based on nominal supply voltages at  $T_1 = 25$  °C.

© 2015-2017 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

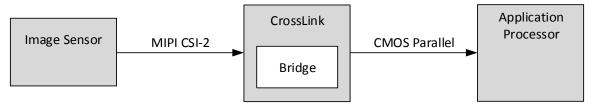

### 2.8. MIPI CSI-2 to CMOS Image Sensor Interface Bridge

Figure 2.8 shows the block diagram for the MIPI DSI to CMOS display interface bridge. This solution bridges the MIPI DSI output from the application processor to CMOS parallel display input.

Table 2.8 provides additional details on the application example, including input and output descriptions and device resource usage. The interface bridge is fully programmable, supporting multiple pixel formats and data rates up to 1.5 Gb/s per lane input and up to 150 MHz CMOS parallel output. For details, refer to FPGA-IPUG-02004, MIPI D-PHY to CMOS Interface Bridge Soft IP User Guide.

Figure 2.8. MIPI CSI-2 to CMOS Image Sensor Interface Bridge

Table 2.8. MIPI CSI-2 to CMOS Image Sensor Interface Bridge Overview

| Table 2.6. Wiff C31-2 to Civios image sensor interface bridge overview |                                            |  |  |  |

|------------------------------------------------------------------------|--------------------------------------------|--|--|--|

| Application Example Details                                            |                                            |  |  |  |

| Input Tuno                                                             | 1080p60, RAW12                             |  |  |  |

| Input Type                                                             | 4-Lane MIPI D-PHY @ ~445 Mb/s per lane     |  |  |  |

| Programmable Fabric Operation(s)                                       | Interface Bridge                           |  |  |  |

| Output Tupo                                                            | 1080p60, RAW12                             |  |  |  |

| Output Type                                                            | CMOS Parallel @ 74.25 MHz                  |  |  |  |

| Additional Custom Functions                                            | I <sup>2</sup> C for Camera Configuration  |  |  |  |

| Additional System Functions                                            | GPIO for image sensor reset/power control  |  |  |  |

|                                                                        | Preliminary Example Device Resource Usage* |  |  |  |

| Typical Power Consumption                                              | 60 mW                                      |  |  |  |

| Device I/O Used                                                        | 16 Programmable I/O; 1 x Hard D-PHY Quads  |  |  |  |

| Fabric Resources Used                                                  | 15% of LUT4; ~15% of EBR                   |  |  |  |

<sup>\*</sup>Note: For reference only – exact usage and power consumption depends on specific application parameters. Additional system functions are not included in resource usage. The typical power consumption estimate is based on nominal supply voltages at  $T_J = 25$  °C.

© 2015-2017 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 3. Product Feature Summary

Table 3.1 lists CrossLink device information and packages.

**Table 3.1. CrossLink Feature Summary**

| Device                                                         | CrossLink |

|----------------------------------------------------------------|-----------|

| LUTs                                                           | 5936      |

| sysMEM Blocks (9 kb)                                           | 20        |

| Embedded Memory (kb)                                           | 180       |

| Distributed RAM Bits (kb)                                      | 47        |

| General Purpose PLL                                            | 1         |

| NVCM                                                           | Yes       |

| Embedded I <sup>2</sup> C                                      | 2         |

| Oscillator (10 KHz)                                            | 1         |

| Oscillator (48 MHz)                                            | 1         |

| Hardened MIPI D-PHY                                            | 21, 2     |

| Packages                                                       | 1/0       |

| 36 WLCSP <sup>2</sup> (2.535 × 2.583 mm <sup>2</sup> , 0.6 mm) | 17        |

| 64 ucfBGA (3.5 × 3.5 mm², 1 mm)                                | 29        |

| 80 ctfBGA (6.5 x 6.5 mm <sup>2</sup> , 1 mm)                   | 36        |

| 81 csfBGA (4.5 × 4.5 mm², 1 mm)                                | 37        |

#### Notes:

- 1. Additional D-PHY Rx interfaces are available using programmable I/O.

- 2. Only one Hardened D-PHY is available in 36 WLCSP package.

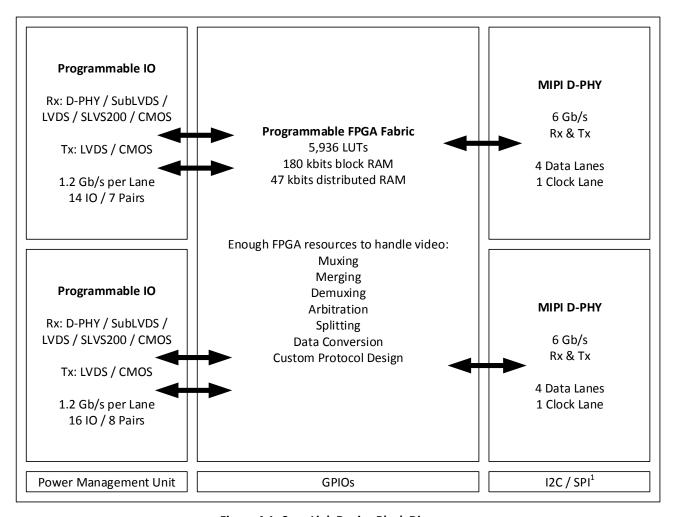

### 4. Architecture Overview

CrossLink is designed as a flexible, chip-to-chip bridging solution which supports a wide variety of applications, including those described in Application Examples section on page 7.

CrossLink provides three key building blocks for these bridging applications:

- Up to two embedded Hard D-PHY blocks

- Two banks of flexible programmable I/O supporting a variety of standards including D-PHY Rx, subLVDS, SLVS, LVDS, and CMOS

- A programmable logic core providing the LUTs, memory, and system resources to implement a wide range of bridging operations

In addition to these blocks, CrossLink also provides key system resources including a Power Management Unit, flexible configuration interface, additional CMOS GPIO, and user I<sup>2</sup>C blocks.

The block diagram for the device is shown in Figure 4.1.

Figure 4.1. CrossLink Device Block Diagram

Note: I<sup>2</sup>C and SPI configuration modes are supported. User mode hardened I<sup>2</sup>C is also supported.

#### 4.1. MIPI D-PHY Blocks

The top side of the device includes two hard MIPI D-PHY quads. The D-PHY can be configured to support both camera interface (CSI-2) and display interface (DSI) applications. Below is a summary of the features supported by the hard D-PHY quads. Refer to FPGA-TN-02012, CrossLink High-Speed I/O Interface for more information on the Hard D-PHY quads.

- Transmit and Receive compliant to D-PHY Revision 1.1

- High-Speed (HS) and Low-Power (LP) mode support (including built-in contention detect)

- Up to 6 Gb/s per quad (1500 Mb/s data rate per lane)

- Dedicated PLL for Transmit Frequency Synthesis

- Dedicated Serializer and De-Serializer blocks for fabric interfacing

- Supports continuous clock mode or low power clock mode

Lattice Semiconductor provides a set of pre-engineered IP modules which include the full implementation and control of the hard D-PHY blocks for the examples in Application Examples section on page 7, enabling designers to focus on unique aspects of their design.

### 4.2. Programmable I/O Banks

CrossLink devices provide programmable I/O which can be used to interface to a variety of external standards. The I/O features are summarized below, and described in detail in FPGA-TN-02012, CrossLink High-Speed I/O Interface and FPGA-TN-02016, CrossLink sysI/O Usage Guide. The programmable LVDS/CMOS I/O (Banks 1 and 2) are described below, while the CMOS GPIO (bank 0) and hard D-PHY quads are described separately. Programmable LVDS/CMOS I/O (Bank 1 and 2) features:

- Built-in support for the following differential standards

- LVDS Tx and Rx

- SLVS Rx

- SubLVDS Rx

- MIPI Rx (both LP and HS receive on a single differential pair)

- Support for the following single ended standards (ratioed to VCCIO)

- LVCMOS33

- LVCMOS25

- LVCMOS18

- LVCMOS12 (Outputs)

- LVTTL33

- Independent voltage levels per bank based on VCCIO supply

- Input/output gearboxes per LVDS pair supporting several ratios for video interface applications

- DDRX1, DDRX2, DDRX4, DDRX8 and DDRX71, DDRX141

- Programmable delay cells to support edge-aligned and center-aligned interfaces

- Programmable differential termination ( $\sim 100 \Omega$ ) with dynamic enable control

- Tri-state control for output

- Input/output register blocks

- Single-ended standards support open-drain and programmable input hysteresis

- Optional weak pull-up resistors

To ensure the MIPI Rx interface implemented in FPGA fabric using Programmable I/Os runs in an optimal environment, follow this guideline of assigning I/Os to the bank for the MIPI Rx inputs:

• When an SLVS/MIPI Rx interface is placed in Bank 1 or 2, do not place both Banks 1 and 2 with LVCMOS outputs in these 2 banks.

© 2015-2017 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

- Four Edge Clocks for high-speed DDR interfaces

- 2 per Programmable I/O bank

- Source from PCLK pins, PLL or DLL blocks

- Programmable Clock divider per Edge Clock

- Delay primitives for 90 degree phase shifting of clock/data (DDRDLL, DLLDEL)

- Dynamic Clock Control

- Fabric control to disable clock nets for power savings

- Dynamic Clock Select

- Smart clock multiplexer with two independent inputs and glitchless output support

- Two On-Chip Oscillators

- Always-on Low Frequency (LFCLKOUT) with nominal frequency of 10 kHz

- High-Frequency (HFCLKOUT) with nominal frequency of 48 MHz, programmable output dividers, and dynamic enable control

#### 4.3.3. Embedded Block RAM Overview

CrossLink devices also contain sysMEM Embedded Block RAM (EBR). The EBR consists of a 9 kB RAM with memory core, dedicated input registers and output registers with separate clock and clock enable. Supported modes and other general information on the EBR are listed below. For details, refer to FPGA-TN-02017, CrossLink Memory Usage Guide.

- Support for different memory configurations

- Single Port

- True Dual Port

- Pseudo Dual Port

- ROM

- FIFO (logic wrapper added automatically by design tools)

- Flexible customization features

- Initialization of RAM/ROM

- Memory cascading (handled automatically by design tools)

- Optional parity bit support

- Byte-enable

- Multiple block size options

- RAM modes support optional Write Through or Read-Before-Write modes

### 4.4. System Resources

#### 4.4.1. CMOS GPIO (Bank 0)

CrossLink provides dedicated CMOS GPIO on Bank 0 of the device. These GPIO do not include differential signaling support. A summary of the features associated with these GPIOs is listed below:

- Support for the following single ended standards (ratioed to VCCIO)

- LVCMOS33

- LVCMOS25

- LVCMOS18

- LVCMOS12 (Outputs)

- LVTTL33

- Tri-state control for output

- Input/output register blocks

- Open-drain option and programmable input hysteresis

- Internal pull-up resistors with configurable values of 3.3 k $\Omega$ , 6.8 k $\Omega$ , 10 k $\Omega$

© 2015-2017 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 5. DC and Switching Characteristics

### 5.1. Absolute Maximum Ratings

Table 5.1. Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Symbol                                                                        | Parameter                                       | Min         | Max  | Unit |

|-------------------------------------------------------------------------------|-------------------------------------------------|-------------|------|------|

| V <sub>cc</sub>                                                               | Core Supply Voltage                             | -0.5        | 1.32 | V    |

| V <sub>CCPLL</sub>                                                            | PLL Supply Voltage                              | -0.5        | 1.32 | V    |

| V <sub>CCAUX</sub>                                                            | Auxiliary Supply Voltage for Bank 1, 2 and NVCM | -0.5        | 2.75 | V    |

| V <sub>ccio</sub>                                                             | I/O Driver Supply Voltage for Banks 0, 1, 2     | -0.5        | 3.63 | V    |

| _                                                                             | Input or I/O Transient Voltage Applied          | -0.5        | 3.63 | V    |

| V <sub>CC_DPHY</sub> V <sub>CCA_DPHY</sub> V <sub>CCPLL_DPHY</sub> VCCMU_DPHY | MIPI D-PHY Supply Voltages                      | -0.5        | 1.32 | V    |

| _                                                                             | Voltage Applied on MIPI D-PHY Pins              | -0.5        | 1.32 | V    |

| T <sub>A</sub>                                                                | Storage Temperature (Ambient)                   | <b>–</b> 65 | 150  | °C   |

| T <sub>J</sub>                                                                | Junction Temperature (TJ)                       | _           | +125 | °C   |

#### Notes:

- 1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 2. Compliance with the Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

### 5.2. Recommended Operating Conditions

Table 5.2. Recommended Operating Conditions 1, 2

| Symbol                   | Parameter                                                                                             | Min   | Max   | Unit |

|--------------------------|-------------------------------------------------------------------------------------------------------|-------|-------|------|

| V <sub>cc</sub>          | Core Supply Voltage                                                                                   | 1.14  | 1.26  | V    |

| V <sub>CCPLL</sub>       | PLL Supply Voltage                                                                                    | 1.14  | 1.26  | V    |

| V <sub>CCAUX</sub>       | Auxiliary Supply Voltage for Bank 1, 2 and NVCM                                                       | 2.375 | 2.625 | V    |

| V <sub>ccio</sub>        | I/O Driver Supply Voltage for Bank 0, 1, 2                                                            | 1.14  | 3.465 | V    |

| T <sub>JIND</sub>        | Junction Temperature, Industrial Operation                                                            | -40   | 100   | °C   |

| D-PHY External           | Power Supply                                                                                          |       |       |      |

| V <sub>CC_DPHYx</sub>    | Supply Voltage for D-PHY                                                                              | 1.14  | 1.26  | V    |

| V <sub>CCA_DPHYx</sub>   | Analog Supply Voltage for D-PHY                                                                       | 1.14  | 1.26  | V    |

| V <sub>CCPLL_DPHYx</sub> | PLL Supply voltage for D-PHY                                                                          | 1.14  | 1.26  | V    |

| V <sub>CCMU_DPHY</sub>   | Supply for V <sub>CC_DPHY1</sub> , V <sub>CCA_DPHY1</sub> and V <sub>CCPLL_DPHY1</sub> on the WLCSP36 | 1.14  | 1.26  | V    |

#### Notes:

- 1. For Correct Operation, all supplies must be held in their valid operation range.

- 2. Like power supplies, must be tied together if they are at the same supply voltage. Follow the noise filtering recommendations in FPGA-TN-02013, CrossLink Hardware Checklist.

### 5.3. Preliminary Power Supply Ramp Rates

#### Table 5.3. Preliminary Power Supply Ramp Rates<sup>1</sup>

| Symbol            | Parameter                                                                | Min | Max | Unit |

|-------------------|--------------------------------------------------------------------------|-----|-----|------|

| t <sub>RAMP</sub> | Power supply ramp rates for all power supplies except V <sub>CCAUX</sub> | 0.6 | 10  | V/ms |

#### Note:

### 5.4. Preliminary Power-On-Reset Voltage Levels

Table 5.4. Preliminary Power-On-Reset Voltage Levels<sup>1, 3, 4</sup>

| Symbol                                                                                         | Parameter                                                                                                       |                                 | Min  | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|------|

| V <sub>PORUP</sub> Power-On-Reset ramp up (Monitoring V <sub>CC</sub> , V <sub>CC100</sub> , a |                                                                                                                 | V <sub>cc</sub>                 | 0.62 | 0.68 | 0.93 | V    |

|                                                                                                | Power-On-Reset ramp up trip point (Monitoring Ves. Vescos, and Vescos)                                          | V <sub>CCIOO</sub> <sup>2</sup> | 0.87 | 1.08 | 1.50 | V    |

|                                                                                                | V <sub>CCAUX</sub>                                                                                              | V <sub>CCAUX</sub>              | 0.90 | _    | 1.53 | V    |

|                                                                                                | Power-On-Reset ramp down trip point (Monitoring V <sub>CC</sub> , V <sub>CCIOO</sub> , and V <sub>CCAUX</sub> ) | V <sub>cc</sub>                 | _    | _    | 0.79 | V    |

| V <sub>PORDN</sub>                                                                             |                                                                                                                 | V <sub>CCIOO</sub> <sup>2</sup> | _    | _    | 1.50 | V    |

|                                                                                                |                                                                                                                 | V <sub>CCAUX</sub>              | _    | _    | 1.53 | V    |

#### Notes:

- 1. These POR ramp up trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

- 2. Only V<sub>CCIOO</sub> (Config Bank) has a Power-On-Reset ramp up trip point. All other VCCIOs do not have Power-On-Reset ramp up detection.

- 3. V<sub>CCIO</sub> supplies should be powered-up before or together with the V<sub>CC</sub> and V<sub>CCAUX</sub> supplies.

- 4. Configuration starts after V<sub>CC</sub>, V<sub>CCI00</sub> and V<sub>CCAUX</sub> reach V<sub>PORUP</sub>. For details, see t<sub>REFRESH</sub> time in Table 5.21 on page 38.

#### 5.5. ESD Performance

Refer to the LIFMD Product Family Qualification Summary for complete qualification data, including ESD performance.

Assume monotonic ramp rates.

### 5.7. Preliminary CrossLink Supply Current

Over recommended operating conditions.

**Table 5.6. Preliminary CrossLink Supply Current**

| Symbol                        | Parameter                                                                                | Тур  | Unit |

|-------------------------------|------------------------------------------------------------------------------------------|------|------|

| Normal Operat                 | ion <sup>1</sup>                                                                         |      |      |

| I <sub>cc</sub>               | Core Power Supply Current                                                                | 7.17 | mA   |

| I <sub>CCPLL</sub>            | PLL Power Supply Current                                                                 | 0.05 | mA   |

| I <sub>CCAUX25VPP</sub>       | Auxiliary Power Supply Current for Bank 1, 2 and NVCM Programming Supply Current         | 2.65 | mA   |

| I <sub>CCIOx</sub>            | Bank x Power Supply Current (per Bank)                                                   | 0.06 | mA   |

| I <sub>CCA_DPHYx</sub>        | V <sub>CCA_DPHYx</sub> Power Supply Current                                              | 8.33 | mA   |

| I <sub>CCPLL_DPHYx</sub>      | V <sub>CCPLL_DPHYx</sub> Power Supply Current                                            | 1.31 | mA   |

| Standby Currer                | tt <sup>2</sup>                                                                          |      |      |

| I <sub>CCSTDBY</sub>          | Core Power Supply Standby Current                                                        | 2.73 | mA   |

| I <sub>CCPLLSTDBY</sub>       | PLL Power Supply Standby Current                                                         |      | mA   |

| I <sub>CCAUX25VPPSTDBY</sub>  | Auxiliary Power Supply Current for Bank 1, 2 and NVCM Programming Supply Standby Current | 0.46 | mA   |

| I <sub>CCIOSTDBY</sub>        | Bank Power Supply Standby Current (per Bank)                                             | 0    | mA   |

| I <sub>CCA_DPHYxSTDBY</sub>   | V <sub>CCA_DPHYx</sub> Power Supply Standby Current                                      | 0.01 | mA   |

| I <sub>CCPLL_DPHYxSTDBY</sub> | V <sub>CCPLL_DPHYx</sub> Power Supply Standby Current                                    | 0.01 | mA   |

| Sleep/Power D                 | own Mode Current <sup>3</sup>                                                            |      |      |

| I <sub>CC_SLEEP</sub>         | Core Power Supply Sleep Current                                                          | 0.48 | mA   |

| I <sub>CCGPLL_SLEEP</sub>     | PLL Power Supply Current                                                                 | 0.05 | mA   |

| I <sub>CCAUX_SLEEP</sub>      | Auxiliary Power Supply Current for Bank 1, 2 and NVCM Programming Supply Current         | 0.03 | mA   |

| I <sub>CCIOx_SLEEP</sub>      | Bank Power Supply Current (per Bank)                                                     | 0.06 | mA   |

| I <sub>CCPLL_DPHY_SLEEP</sub> | V <sub>CCPLL_DPHY</sub> Power Supply Sleep Current                                       | 0.01 | mA   |

| I <sub>CCA_DPHY_SLEEP</sub>   | V <sub>CCA_DPHY</sub> Power Supply Sleep Current                                         | 0.05 | mA   |

#### Notes:

#### 1. Normal Operation

Typical design as defined in 2:1 MIPI CSI-2 Image Sensor Aggregator Bridge section, under the following conditions:

- a.  $T_J = 25$  °C, all power supplies at nominal voltages.

- b. Typical processed device in csfBGA81 package.

- c. To determine power for all other applications and operating conditions, use Power Calculator in Lattice Diamond design software

#### 2. Standby Operation

A typically processed device in csfBGA81 package with blank pattern programmed, under the following conditions:

- a. All outputs are tri-stated, all inputs are held at either V<sub>CCIO</sub>, or GND.

- b. All clock inputs are at 0 MHz.

- c.  $T_J = 25$  °C, all power supplies at nominal voltages.

- d. No pull-ups on I/O.

#### Sleep/Power Down Mode

Typical design as defined in 2:1 MIPI CSI-2 Image Sensor Aggregator Bridge section, under following conditions:

- a. Design is put into Sleep/Power Down Mode with user logic powers down D-PHY, and enters into Sleep Mode in PMU.

- b.  $T_J = 25$  °C, all power supplies at nominal voltages.

- Typical processed device in csfBGA81 package.

#### 4. For ucfBGA64 package

- a.  $V_{CCA\ DPHY0}$  and  $V_{CCA\ DPHY1}$  are tied together as  $V_{CC\ DPHYX}$ .

- b.  $V_{CCPLL\_DPHY0}$  and  $V_{CCPLL\_DPHY1}$  are tied together as  $V_{CC\_DPHYX}$ .

#### 5. For WLCS36 package

- a. V<sub>CCGPLL</sub> and V<sub>CCIO1</sub> (Bank 1) are tied together to V<sub>CC</sub>.

- b.  $V_{CCPLL\_DPHY}$  and  $V_{CCA\_DPHY}$  are tied together as  $V_{CCMU\_DPHY}$ .

- 5. To determine the CrossLink start-up peak current, use the Power Calculator tool in the Lattice Diamond design software.

### 5.8. Preliminary Power Management Unit (PMU) Timing

Table 5.7. Preliminary PMU Timing<sup>1</sup>

| Symbol               | Parameter                            | Device      | Max | Unit |

|----------------------|--------------------------------------|-------------|-----|------|

| t <sub>PMUWAKE</sub> | Time for PMU to wake from Sleep mode | All Devices | 1   | ms   |

#### Note:

### 5.9. sysI/O Recommended Operating Conditions

Table 5.8. sysI/O Recommended Operating Conditions<sup>1</sup>

| Chandand                       | V <sub>CCIO</sub> |      |       |  |

|--------------------------------|-------------------|------|-------|--|

| Standard                       | Min               | Тур  | Max   |  |

| LVCMOS33/LVTTL33               | 3.135             | 3.30 | 3.465 |  |

| LVCMOS25                       | 2.375             | 2.50 | 2.625 |  |

| LVCMOS18                       | 1.710             | 1.80 | 1.890 |  |

| LVCMOS12 (Output only)         | 1.140             | 1.20 | 1.260 |  |

| subLDVS (Input only)           | 2.375             | 2.50 | 2.625 |  |

| SLVS (Input only) <sup>2</sup> | 2.375             | 2.50 | 2.625 |  |

| LVDS                           | 2.375             | 2.50 | 2.625 |  |

| MIPI (Input only)              | 1.140             | 1.20 | 1.260 |  |

#### Note:

- 1. For input voltage compatibility, refer to FPGA-TN-02016, CrossLink sysI/O Usage Guide.

- 2. For SLVS/MIPI interface I/O placement, see the Programmable I/O Banks section.

### 5.10. Preliminary sysI/O Single-Ended DC Electrical Characteristics

Table 5.9. Preliminary syst/O Single-Ended DC Electrical Characteristics

| Input/Output  | V <sub>IL</sub>                             |                        | V <sub>IH</sub>         |                        | V <sub>OL</sub> Max     | V <sub>он Min</sub> (V) | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) |

|---------------|---------------------------------------------|------------------------|-------------------------|------------------------|-------------------------|-------------------------|----------------------|----------------------|

| Standard      | Min (V)                                     | Max (V)                | Min (V)                 | Max (V)                | (V)                     | VOH IVIIN (V)           | IOL (IIIA)           | IOH (IIIA)           |

| LVCMOS33/     | -0.3                                        | 0.8                    | 2.0                     | V 10.2                 | 0.40                    | V <sub>CCIO</sub> - 0.4 | 8                    | -8                   |

| LVTTL33       | 33 -0.3 0.8 2.0 V <sub>CCIO</sub> +0.2 0.20 | 0.20                   | V <sub>CCIO</sub> – 0.2 | 0.1                    | -0.1                    |                         |                      |                      |

| LVCMOS2E      | -0.3 0.7                                    | 0.7                    | 0.7                     |                        | 0.40                    | V <sub>CCIO</sub> – 0.4 | 6                    | <b>-</b> 6           |

| LVCMOS25      |                                             | 1.7                    | V <sub>CCIO</sub> +0.2  | 0.20                   | V <sub>CCIO</sub> – 0.2 | 0.1                     | -0.1                 |                      |

| 11/61/106/10  | 0.2                                         | 0.35.1/                | 0.65.17                 |                        | 0.40                    | V <sub>CCIO</sub> – 0.4 | 4                    | -4                   |

| LVCMOS18      | -0.3                                        | 0.35 V <sub>CCIO</sub> | 0.65 V <sub>CCIO</sub>  | V <sub>CCIO</sub> +0.2 | 0.20                    | V <sub>CCIO</sub> – 0.2 | 0.1                  | -0.1                 |

| LVCMOS12      |                                             |                        |                         |                        | 0.40                    | V <sub>CCIO</sub> - 0.4 | 2                    | -2                   |

| (Output only) | 1                                           | _                      | _                       | _                      | 0.20                    | V <sub>CCIO</sub> – 0.2 | 0.1                  | -0.1                 |

<sup>1.</sup> For details on PMU usage, refer to FPGA-TN-02018, Power Management and Calculation for CrossLink Devices.

### 5.11.2. Preliminary Hardened MIPI D-PHY I/Os

### Table 5.11. Preliminary MIPI D-PHY

|                      | Description                                      | Min | Тур | Max  | Unit |

|----------------------|--------------------------------------------------|-----|-----|------|------|

|                      | Receiver                                         |     |     |      |      |

| High Speed           |                                                  |     |     |      |      |

| V <sub>CMRX</sub>    | Common-Mode Voltage HS Receive Mode              | 70  | _   | 330  | mV   |

| V <sub>IDTH</sub>    | Differential Input High Threshold                | _   | _   | 70   | mV   |

| V <sub>IDTL</sub>    | Differential Input Low Threshold                 | -70 | _   | _    | mV   |

| V <sub>IHHS</sub>    | Single-ended Input High Voltage                  | _   | _   | 460  | mV   |

| V <sub>ILHS</sub>    | Single-ended Input Low Voltage                   | -40 | _   | _    | mV   |

| V <sub>TERM-EN</sub> | Single-ended Threshold for HS Termination Enable | _   | _   | 450  | mV   |

| Z <sub>ID</sub>      | Differential Input Impedance                     | 80  | 100 | 125  | Ω    |

| Low Power            | •                                                |     |     |      |      |

| V <sub>IH</sub>      | Logic 1 Input Voltage                            | 880 | _   | _    | mV   |

| V <sub>IL</sub>      | Logic 0 Input Voltage, not in ULP State          | _   | _   | 550  | mV   |

| V <sub>IL-ULPS</sub> | Logic 0 Input Voltage, in ULP State              | _   | _   | 300  | mV   |

| V <sub>HYST</sub>    | Input Hysteresis                                 | 25  | _   | _    | mV   |

|                      | Transmitter                                      |     |     |      |      |

| High Speed           |                                                  |     |     |      |      |

| V <sub>CMTX</sub>    | HS Transmit Static Common Mode Voltage           | 150 | 200 | 250  | mV   |

| V <sub>OD</sub>      | HS Transmit Differential Voltage                 | 140 | 200 | 270  | mV   |

| V <sub>OHHS</sub>    | HS Output High Voltage                           | _   | _   | 360  | mV   |

| Zos                  | Single-ended Output Impedance                    | 40  | 50  | 62.5 | Ω    |

| $\Delta Z_{OS}$      | Single-ended Output Impedance Mismatch           | _   | _   | 10   | %    |

| Low Power            |                                                  |     |     |      |      |

| V <sub>OH</sub>      | Output High Level                                | 1.1 | 1.2 | 1.3  | V    |

| V <sub>OL</sub>      | Output Low Level                                 | -50 | _   | 50   | mV   |

| Z <sub>OLP</sub>     | Output Impedance of LP Transmitter               | 110 | _   | _    | Ω    |

### 5.12. Preliminary CrossLink Maximum General Purpose I/O Buffer Speed

Over recommended operating conditions.

Table 5.12. Preliminary CrossLink Maximum I/O Buffer Speed

| Buffer                            | Description                                                               | Max | Unit |

|-----------------------------------|---------------------------------------------------------------------------|-----|------|

| Maximum Input Frequency           |                                                                           |     | •    |

| LVDS25                            | LVDS, V <sub>CCIO</sub> = 2.5 V, csfBGA81, ctfBGA80, ucfBGA64 packages    | 600 | MHz  |

|                                   | LVDS, V <sub>CCIO</sub> = 2.5 V, WLCSP36 package                          | 500 | MHz  |

| subLVDS                           | subLVDS, V <sub>CCIO</sub> = 2.5 V, csfBGA81, ctfBGA80, ucfBGA64 packages | TBD | MHz  |

|                                   | subLVDS, V <sub>CCIO</sub> = 2.5 V, WLCSP36 package                       | TBD | MHz  |

| MAIDLD DILLY (LIC MA - 4-16       | MIPI D-PHY, csfBGA81, ctfBGA80, ucfBGA64 packages                         | 600 | MHz  |

| MIPI D-PHY (HS Mode) <sup>6</sup> | MIPI D-PHY, WLCSP36 package                                               | 500 | MHz  |

| SLVS                              | SLVS, VCCIO=2.5 V, csfBGA81, ctfBGA80, ucfBGA64 packages                  | TBD | MHz  |

|                                   | SLVS, VCCIO=2.5 V, WLCSP36 package                                        | TBD | MHz  |

| LVTTL33                           | LVTTL, V <sub>CCIO</sub> = 3.3 V                                          | 300 | MHz  |

| LVCMOS33                          | LVCMOS, V <sub>CCIO</sub> = 3.3 V                                         | 300 | MHz  |

| LVCMOS25D                         | Differential LVCMOS, V <sub>CCIO</sub> = 2.5 V                            | 300 | MHz  |

| LVCMOS25                          | LVCMOS, V <sub>CCIO</sub> = 2.5 V                                         | 300 | MHz  |

| LVCMOS18                          | LVCMOS, V <sub>CCIO</sub> = 1.8 V                                         | 155 | MHz  |

| <b>Maximum Output Frequency</b>   |                                                                           |     |      |

| LVDS25                            | LVDS, V <sub>CCIO</sub> = 2.5 V, csfBGA81, ctfBGA80, ucfBGA64 packages    | 600 | MHz  |

|                                   | LVDS, V <sub>CCIO</sub> = 2.5 V, WLCSP36 package                          | 500 | MHz  |

| LVTTL33                           | LVTTL, V <sub>CCIO</sub> = 3.3 V                                          | 300 | MHz  |

| LVTTL33D                          | Differential LVTTL, V <sub>CCIO</sub> = 3.3 V                             | 300 | MHz  |

| LVCMOS33                          | LVCMOS, 3.3 V                                                             | 300 | MHz  |

| LVCMOS33D                         | Differential LVCMOS, 3.3 V                                                | 300 | MHz  |

| LVCMOS25                          | LVCMOS, 2.5 V                                                             | 300 | MHz  |

| LVCMOS25D                         | Differential LVCMOS, 2.5 V                                                | 300 | MHz  |

| LVCMOS18                          | LVCMOS, 1.8 V                                                             | 155 | MHz  |

| LVCMOS12                          | LVCMOS, V <sub>CCIO</sub> = 1.2 V                                         | 70  | MHz  |

#### Notes:

- 1. These maximum speeds are characterized but not tested on every device.

- 2. Maximum I/O speed for differential output standards emulated with resistors depends on the layout.

- 3. LVCMOS timing is measured with the load specified in Table 5.22.

- 4. Actual system operation may vary depending on user logic implementation.

- 5. Maximum data rate equals two times the clock rate when utilizing DDR.

- 6. This is the maximum MIPI D-PHY input rate on the programmable I/O banks 1 and 2. The hardened MIPI D-PHY input and output rates are described in Hardened MIPI D-PHY Performance section. For SLVS/MIPI interface I/O placement, see the Programmable I/O Banks section.

© 2015-2017 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 5.13. Preliminary CrossLink External Switching Characteristics

Over recommended commercial operating conditions.

Table 5.13. Preliminary CrossLink External Switching Characteristics<sup>4, 5</sup>

| Damanat - ::              | Description                                                                           | Canalistana                     | -6       |             | l lm:4      |

|---------------------------|---------------------------------------------------------------------------------------|---------------------------------|----------|-------------|-------------|

| Parameter                 | Description                                                                           | Conditions                      | Min      | Max         | Unit        |

| Clocks                    |                                                                                       |                                 |          |             |             |

| Primary Clock             |                                                                                       |                                 |          |             |             |

| f <sub>MAX_PRI</sub>      | Frequency for Primary Clock Tree                                                      | _                               | 1        | 150         | MHz         |

| tw_PRI                    | Clock Pulse Width for Primary Clock                                                   | _                               | 0.8      | _           | ns          |

| t <sub>ISKEW_PRI</sub>    | Primary Clock Skew Within a Clock                                                     | _                               | _        | 450         | ps          |

| Edge Clock                |                                                                                       |                                 |          |             |             |

| f <sub>MAX_EDGE</sub>     | Frequency for Edge Clock Tree                                                         | _                               | _        | 600         | MHz         |

| t <sub>W_EDGE</sub>       | Clock Pulse Width for Edge Clock                                                      | _                               | 0.783    | _           | ns          |

| t <sub>ISKEW_EDGE</sub>   | Edge Clock Skew Within a Bank                                                         | _                               | _        | 120         | ps          |

| Generic SDR Inte          | erface <sup>1</sup>                                                                   |                                 |          |             |             |

| General Purpose           | I/O Pin Parameters Using Clock Tree Without                                           | t PLL                           |          |             |             |

| t <sub>co</sub>           | Clock to Output – PIO Input Register                                                  | _                               | _        | 6.0         | ns          |

| t <sub>su</sub>           | Clock to Data Setup – PIO Input<br>Register                                           | _                               | -0.90    | _           | ns          |

| t <sub>HD</sub>           | Clock to Data Hold – PIO Input Register                                               | _                               | 1.82     | _           | ns          |

| t <sub>su_delay</sub>     | Clock to Data Setup – PIO Input<br>Register with Input Delay for zero t <sub>HD</sub> | _                               | 1.02     | _           | ns          |

| t <sub>HD_DELAY</sub>     | Clock to Data Hold – PIO Input Register with Input Delay for zero t <sub>HD</sub>     | _                               | 0        | _           | ns          |

| General Purpose           | I/O Pin Parameters Using Clock Tree With PL                                           | L                               |          |             |             |

| t <sub>co</sub>           | Clock to Output – PIO Input Register                                                  | _                               | _        | 5.2         | ns          |

| t <sub>SU</sub>           | Clock to Data Setup – PIO Input<br>Register                                           | _                               | 0.17     | 1           | ns          |

| t <sub>HD</sub>           | Clock to Data Hold – PIO Input Register                                               | _                               | 1.01     | _           | ns          |

| t <sub>su_delay</sub>     | Clock to Data Setup – PIO Input<br>Register with Input Delay for zero t <sub>HD</sub> | _                               | 1.70     | _           | ns          |

| t <sub>HD_DELAY</sub>     | Clock to Data Hold – PIO Input Register with Input Delay for zero t <sub>HD</sub>     | _                               | 0        | _           | ns          |

| Generic DDR Inte          | erfaces <sup>2</sup>                                                                  | •                               |          |             |             |

| Generic DDRX8 o           | or DDRX4 I/O with Clock and Data Centered at ECLK.Centered)                           | General Purpose Pins (          | GDDRX8_R | X/TX.ECLK.C | Centered or |

| t <sub>SU_GDDRX4_8</sub>  | Input Data Set-Up Before CLK Rising and Falling edges                                 | _                               | 0.167    | _           | ns          |

| t <sub>HO_GDDRX4_8</sub>  | Input Data Hold After CLK Rising and Falling edges                                    | _                               | 0.167    | _           | ns          |

|                           | Output Data Valid Before CLK Output                                                   | Data Rate = 1.2 Gb/s            | 0.297    | 1           | ns          |

| t <sub>DVB_GDDRX4_8</sub> | Rising and Falling edges                                                              | Other Data Rates                | -0.120   | _           | ns+1/2UI    |

| +                         | Output Data Valid After CLK Output                                                    | Data Rate = 1.2 Gb/s            | 0.297    | _           | ns          |

| t <sub>DVA_GDDRX4_8</sub> | Rising and Falling edges                                                              | Other Data Rates                | -0.120   | _           | ns+1/2UI    |

| f <sub>MAX GDDRX4 8</sub> | Frequency for ECLK <sup>3</sup>                                                       | csfBGA81, ctfBGA80,<br>ucfBGA64 | _        | 600         | MHz         |

| -IWAX_GDDRX4_6            | , , -                                                                                 | WLCSP36                         | _        | 500         | MHz         |

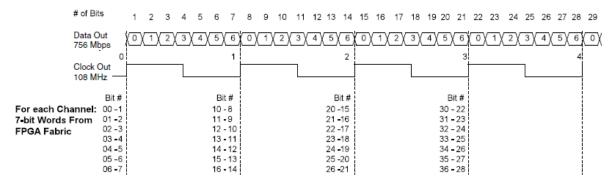

45 - 27

46 - 28

#### # of Bits 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 Data In 3 \ 4 \ 5 \ 6 \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 0 \ 0 \ 756 Mbps 2 Clock In 108 MHz Bit# Bit # Bit # Bit # 40 - 22 For each Channel: 10 - 1 20 - 8 30 - 15 0x 41 - 23 42 - 24 0x 0x 11 - 2 12 - 3 21 **-** 9 22 **-** 10 31 - 16 7-bit Output Words 32 - 17 to FPGA Fabric 0x 23 - 11 43 - 25 13 - 4 33 - 18 0x 24 - 12 34 - 19 44 - 26

25 - 13

26 - 14

35 - 20

36 - 21

15 - 6

16 - 7

#### Transmitter - Shown for one LVDS Channel

0x

0x

Receiver - Shown for one LVDS Channel

Figure 5.5. DDRX71, DDRX141 Video Timing Waveforms

### 6.2. ucfBGA64 Pinout

| Pin Number | Pin Function | Bank   | <b>Dual Function</b> | Differential      |

|------------|--------------|--------|----------------------|-------------------|

| A1         | DPHY1_CKP    | DPHY1  | _                    | True_OF_DPHY1_CKN |

| A2         | DPHY1_CKN    | DPHY1  | _                    | Comp_OF_DPHY1_CKP |

| A3         | DPHY1_DP3    | DPHY1  | -                    | True_OF_DPHY1_DN3 |

| A4         | DPHY1_DN3    | DPHY1  | _                    | Comp_OF_DPHY1_DP3 |

| A5         | DPHY0_DN2    | DPHY0  |                      | Comp_OF_DPHY0_DP2 |

| A6         | DPHY0_DP0    | DPHY0  | _                    | True_OF_DPHY0_DN0 |

| A7         | DPHY0_CKP    | DPHY0  | -                    | True_OF_DPHY0_CKN |

| A8         | DPHY0_CKN    | DPHY0  | -                    | Comp_OF_DPHY0_CKP |

| B1         | DPHY1_DP2    | DPHY1  | -                    | True_OF_DPHY1_DN2 |

| B2         | DPHY1_DN2    | DPHY1  |                      | Comp_OF_DPHY1_DP2 |

| В3         | DPHY1_DP1    | DPHY1  | -                    | True_OF_DPHY1_DN1 |

| B4         | DPHY1_DN1    | DPHY1  | -                    | Comp_OF_DPHY1_DP1 |

| B5         | DPHY0_DP2    | DPHY0  | -                    | True_OF_DPHY0_DN2 |

| В6         | DPHY0_DN0    | DPHY0  | -                    | Comp_OF_DPHY0_DP0 |

| В7         | DPHY0_DP3    | DPHY0  | -                    | True_OF_DPHY0_DN3 |

| В8         | DPHY0_DN3    | DPHY0  | -                    | Comp_OF_DPHY0_DP3 |

| C1         | DPHY1_DP0    | DPHY1  | -                    | True_OF_DPHY1_DN0 |

| C2         | DPHY1_DN0    | DPHY1  | _                    | Comp_OF_DPHY1_DP0 |

| C3         | PB47         | 0      | PCLKTO_0/USER_SDA    |                   |

| C4         | VCCPLL_DPHYX | DPHY   |                      | _                 |

| C5         | VCCA_DPHYX   | DPHY   | _                    | _                 |

| C6         | GNDA_DPHYX   | GND    | _                    | _                 |

| C7         | DPHY0_DP1    | DPHY0  | _                    | True_OF_DPHY0_DN1 |

| C8         | DPHY0_DN1    | DPHY0  | _                    | Comp_OF_DPHY0_DP1 |

| D1         | PB34B        | 1      | -                    | Comp_OF_PB34A     |

| D2         | PB34A        | 1      | GR_PCLK1_0           | True_OF_PB34B     |

| D3         | PB52         | 0      | SPI_SS/CSN/SCL       |                   |

| D4         | GND          | GND    |                      | _                 |

| D5         | VCC          | VCC    | _                    | _                 |

| D6         | VCCAUX       | VCCAUX | -                    | _                 |

| D7         | PB16A        | 2      | PCLKT2_0             | True_OF_PB16B     |

| D8         | PB12A        | 2      | GPLLT2_0             | True OF PB12B     |

| E1         | PB51         | 0      | MISO                 |                   |

| E2         | CRESET_B     | 0      | _                    | _                 |

| E3         | PB48         | 0      | PCLKTO_1/USER_SCL    | _                 |

| E4         | VCC          | VCC    |                      | _                 |

| E5         | GND          | GND    | _                    | _                 |

| E6         | VCCIO2       | 2      | _                    | _                 |

| E7         | PB16B        | 2      | PCLKC2 0             | Comp_OF_PB16A     |

| E8         | PB12B        | 2      | GPLLC2_0             | Comp_OF_PB12A     |

| F1         | PB53         | 0      | SPI_SCK/MCK/SDA      |                   |

| F2         | PB50         | 0      | MOSI                 | _                 |

|            | . 550        | 1      | 111001               |                   |

### ctfBGA80 Pinout (Continued)

| Pin Number | Pin Function | Bank    | Dual Function     | Differential  |

|------------|--------------|---------|-------------------|---------------|

| F4         | VCCIO0       | 0       | _                 | _             |

| F5         | VCCIO1       | 1       | _                 | _             |

| F6         | VCCIO2       | 2       | _                 | _             |

| F7         | VCCIO2       | 2       | _                 | _             |

| F9         | PB6A         | 2       | GR_PCLK2_0        | True_OF_PB6B  |

| F10        | PB6B         | 2       | _                 | Comp_OF_PB6A  |

| G1         | PB50         | 0       | MOSI              | _             |

| G2         | VSS          | GND     | _                 | _             |

| G4         | VCCIO1       | 1       | _                 | _             |

| G5         | VSS          | GND     | _                 | _             |

| G6         | VCCGPLL      | VCCGPLL | _                 | _             |

| G7         | VSSGPLL      | GND     | _                 | _             |

| G9         | PB2A         | 2       | _                 | True_OF_PB2B  |

| G10        | PB2B         | 2       | _                 | Comp_OF_PB2A  |

| H1         | PB52         | 0       | SPI_SS/CSN/SCL    | _             |

| H2         | CRESET_B     | 0       | _                 | _             |

| Н9         | PB2D         | 2       | MIPI_CLKC2_0      | Comp_OF_PB2C  |

| H10        | PB2C         | 2       | MIPI_CLKT2_0      | True_OF_PB2D  |

| J1         | PB53         | 0       | SPI_SCK/MCK/SDA   | _             |

| J2         | PB49         | 0       | PMU_WKUPN/CDONE   | _             |

| J3         | PB43D        | 1       | _                 | Comp_OF_PB43C |

| J4         | PB38D        | 1       | _                 | Comp_OF_PB38C |

| J5         | PB34D        | 1       | MIPI_CLKC1_0      | Comp_OF_PB34C |

| J6         | PB29D        | 1       | PCLKC1_1          | Comp_OF_PB29C |

| J7         | PB29A        | 1       | PCLKT1_0          | True_OF_PB29B |

| 18         | PB16D        | 2       | PCLKC2_1          | Comp_OF_PB16C |

| J9         | PB6D         | 2       | _                 | Comp_OF_PB6C  |

| J10        | PB6C         | 2       | _                 | True_OF_PB6D  |

| K1         | PB51         | 0       | MISO              | _             |

| K2         | PB47         | 0       | PCLKTO_0/USER_SDA | _             |

| К3         | PB43C        | 1       | _                 | True_OF_PB43D |

| K4         | PB38C        | 1       | _                 | True_OF_PB38D |

| K5         | PB34C        | 1       | MIPI_CLKT1_0      | True_OF_PB34D |

| К6         | PB29C        | 1       | PCLKT1_1          | True_OF_PB29D |

| K7         | PB29B        | 1       | PCLKC1_0          | Comp_OF_PB29A |

| К8         | PB16C        | 2       | PCLKT2_1          | True_OF_PB16D |

| К9         | PB12D        | 2       |                   | Comp_OF_PB12C |

| K10        | PB12C        | 2       | _                 | True_OF_PB12D |

### 6.4. csfBGA81 Pinout

| Pin Number | Pin Function | Bank   | Dual Function | Differential                           |  |

|------------|--------------|--------|---------------|----------------------------------------|--|

| A1         | DPHY1_CKP    | DPHY1  | _             | True_OF_DPHY1_CKN                      |  |

| A2         | DPHY1_CKN    | DPHY1  | _             | Comp_OF_DPHY1_CKP                      |  |

| А3         | DPHY1_DP1    | DPHY1  | _             | True_OF_DPHY1_DN1                      |  |

| A4         | DPHY1_DP3    | DPHY1  | _             | True_OF_DPHY1_DN3                      |  |

| A5         | VCCA_DPHY1   | DPHY1  | _             | _                                      |  |

| A6         | DPHY0_DN2    | DPHY0  | _             | Comp_OF_DPHY0_DP2                      |  |

| A7         | DPHY0_DN0    | DPHY0  | _             | Comp_OF_DPHY0_DP0                      |  |

| A8         | DPHY0_CKP    | DPHY0  | _             | True_OF_DPHY0_CKN                      |  |

| A9         | DPHY0_CKN    | DPHY0  | _             | Comp_OF_DPHY0_CKP                      |  |

| B1         | DPHY1_DP0    | DPHY1  | _             | True_OF_DPHY1_DN0                      |  |

| B2         | DPHY1_DN0    | DPHY1  | _             | Comp_OF_DPHY1_DP0                      |  |

| В3         | DPHY1_DN1    | DPHY1  | _             | Comp_OF_DPHY1_DP1                      |  |

| B4         | DPHY1_DN3    | DPHY1  | _             | Comp_OF_DPHY1_DP3                      |  |

| B5         | GNDPLL_DPHYX | GND    | _             | _                                      |  |

| В6         | DPHY0_DP2    | DPHY0  | _             | True_OF_DPHY0_DN2                      |  |

| В7         | DPHY0_DP0    | DPHY0  | _             | True_OF_DPHY0_DN0                      |  |

| В8         | DPHY0_DP1    | DPHY0  | _             | True_OF_DPHY0_DN1                      |  |

| В9         | DPHY0_DN1    | DPHY0  | _             | Comp_OF_DPHY0_DP1                      |  |

| C1         | DPHY1_DP2    | DPHY1  | _             | True_OF_DPHY1_DN2                      |  |

| C2         | DPHY1_DN2    | DPHY1  | _             | Comp_OF_DPHY1_DP2                      |  |

| C3         | GNDA_DPHY1   | DPHY1  | _             | _                                      |  |

| C4         | VCCPLL_DPHY1 | DPHY1  | _             | _                                      |  |

| C5         | GND          | GND    | _             | _                                      |  |

| C6         | VCCPLL_DPHY0 | DPHY0  | _             | _                                      |  |

| C7         | GNDA DPHY0   | DPHY0  | _             | _                                      |  |

| C8         | DPHY0 DP3    | DPHY0  | _             | True_OF_DPHY0_DN3                      |  |

| C9         | DPHY0_DN3    | DPHY0  | _             | Comp_OF_DPHY0_DP3                      |  |

| D1         | PB34A        | 1      | GR_PCLK1_0    | True_OF_PB34B                          |  |

| D2         | PB34B        | 1      |               | Comp_OF_PB34A                          |  |

| D3         | VCCA_DPHY1   | DPHY1  | _             |                                        |  |

| D4         | GND          | GND    | _             | _                                      |  |

| D5         | VCCAUX       | VCCAUX | _             | _                                      |  |

| D6         | GND          | GND    | _             | _                                      |  |

| D7         | VCCA_DPHY0   | DPHY0  | _             | _                                      |  |

| D8         | PB16B        | 2      | PCLKC2_0      | Comp_OF_PB16A                          |  |

| D9         | PB16A        | 2      | PCLKT2_0      | True_OF_PB16B                          |  |

| E1         | PB38A        | 1      |               | True_OF_PB38B                          |  |

| E2         | PB38B        | 1      | _             | Comp OF PB38A                          |  |

| E3         | VCC          | VCC    | _             | —————————————————————————————————————— |  |

| E4         | VCC          | VCC    | _             | _                                      |  |

| E5         | GND          | GND    | _             | _                                      |  |

| E6         | VCCIO2       | 2      |               | _                                      |  |

### 6.7. Pin Information Summary

| Die Tone                                     | CrossLink |          |          |          |  |  |

|----------------------------------------------|-----------|----------|----------|----------|--|--|

| Pin Type                                     | WLCSP36   | ucfBGA64 | ctfBGA80 | csfBGA81 |  |  |

| General Purpose I/O per Bank                 |           |          |          | •        |  |  |

| Bank 0                                       | 7         | 6        | 7        | 7        |  |  |

| Bank 1                                       | 0         | 10       | 14       | 14       |  |  |

| Bank 2                                       | 10        | 12       | 16       | 16       |  |  |

| Total General Purpose Single Ended IO        | 17        | 28       | 37       | 37       |  |  |

| Differential I/O pairs per Bank              |           |          |          |          |  |  |

| Bank 0                                       | 0         | 0        | 0        | 0        |  |  |

| Bank 1                                       | 0         | 5        | 7        | 7        |  |  |

| Bank 2                                       | 5         | 6        | 8        | 8        |  |  |

| Total General Purpose Differential I/O pairs | 5         | 11       | 15       | 15       |  |  |

| D-PHY                                        | 1         | 2        | 2        | 2        |  |  |

| D-PHY Clock/Data                             | 10        | 20       | 20       | 20       |  |  |

| D-PHY VCC                                    | 1         | 2        | 4        | 4        |  |  |

| D-PHY GND                                    | 1         | 1        | 3        | 3        |  |  |

| VCC/VCCIOx/VCCAUX/VCCGPLL                    | 4         | 8        | 9        | 10       |  |  |

| GND                                          | 3         | 4        | 9        | 9        |  |  |

| CRESETB                                      | 1         | 1        | 1        | 1        |  |  |

| Total Balls                                  | 36        | 64       | 80       | 81       |  |  |

7<sup>TH</sup> Floor, 111 SW 5<sup>th</sup> Avenue Portland, OR 97204, USA T 503.268.8000 www.latticesemi.com