Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Obsolete                                                        |

| Core Processor             | F <sup>2</sup> MC-8FX                                           |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 16MHz                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                         |

| Number of I/O              | 52                                                              |

| Program Memory Size        | 60KB (60K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2K x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                     |

| Data Converters            | A/D 8x8/10b                                                     |

| Oscillator Type            | External                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-LQFP                                                         |

| Supplier Device Package    | 64-LQFP (12x12)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/fujitsu/mb95f168japmc1-ge1 |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8-bit Microcontrollers

CMOS

# F<sup>2</sup>MC-8FX MB95160MA Series

## MB95168MA/F168MA/F168NA/F168JA/ MB95FV100D-103

### DESCRIPTION

The MB95160MA series is general-purpose, single-chip microcontrollers. In addition to a compact instruction set, the microcontrollers contain a variety of peripheral functions.

Note : F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

### ■ FEATURE

• F<sup>2</sup>MC-8FX CPU core

Instruction set optimized for controllers

- Multiplication and division instructions

- 16-bit arithmetic operations

- Bit test branch instruction

- Bit manipulation instructions etc.

- Clock

- Main clock

- Main PLL clock

- Sub clock

- Sub PLL clock

(Continued)

For the information for microcontroller supports, see the following web site.

This web site includes the **"Customer Design Review Supplement"** which provides the latest cautions on system development and the minimal requirements to be checked to prevent problems before the system development.

http://edevice.fujitsu.com/micom/en-support/

- Timer

- 8/16-bit compound timer  $\times\,2$  channels

- Can be used to interval timer, PWC timer, PWM timer and input capture.

- 8/16-bit PPG × 2 channels

- 16-bit PPG  $\times$  1 channel

- Time-base timer  $\times$  1 channel

- Watch prescaler  $\times$  1 channel

- LIN-UART  $\times$  1 channel

- LIN function, clock asynchronous (UART) or clock synchronous (SIO) serial data transfer capable

- Full duplex double buffer

- $\bullet$  UART/SIO  $\times$  1 channel

- Clock asynchronous (UART) or clock synchronous (SIO) serial data transfer capable

- Full duplex double buffer

- $I^2C \times 1$  channel

- Built-in wake-up function

- $\bullet$  External interrupt  $\times\,8$  channels

- Interrupt by edge detection (rising, falling, or both edges can be selected)

- Can be used to recover from low-power consumption (standby) modes.

- $\bullet$  8/10-bit A/D converter  $\times$  8 channels

- 8-bit or 10-bit resolution can be selected.

- LCD controller (LCDC)

- 32 SEG  $\times\,4$  COM (Max 128 pixels)

- With blinking function

- Low-power consumption (standby) mode

- Stop mode

- Sleep mode

- Watch mode

- Time-base timer mode

- I/O port

- The number of maximum ports : Max 52

- Port configuration

- General-purpose I/O ports (N-ch open drain) : 2 ports

- General-purpose I/O ports (CMOS) : 50 ports

- Programmable input voltage levels of port

- Automotive input level / CMOS input level / hysteresis input level

- Flash memory security function (Flash memory product only)

- Protects the content of Flash memory

### ■ PRODUCT LINEUP

| Par                  | Part number<br>rameter                 | MB95168MA                                                                                                                                                                                                                                                                                                                     | MB95F168MA            | MB95F168NA                                                       | MB95F168JA               |  |  |  |

|----------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------|--------------------------|--|--|--|

| Тур                  | Type Mask ROM Flash memory product     |                                                                                                                                                                                                                                                                                                                               |                       |                                                                  |                          |  |  |  |

| RO                   | M capacity                             |                                                                                                                                                                                                                                                                                                                               | 60 Kbytes             |                                                                  |                          |  |  |  |

| RAI                  | RAM capacity 2 Kbytes                  |                                                                                                                                                                                                                                                                                                                               |                       |                                                                  |                          |  |  |  |

| Res                  | set output                             | Yes/No<br>selectable                                                                                                                                                                                                                                                                                                          | Y                     | es                                                               | No                       |  |  |  |

|                      | Clock system                           |                                                                                                                                                                                                                                                                                                                               | Dual                  | clock                                                            |                          |  |  |  |

| Option*              | Low voltage<br>detection reset         | Yes/No<br>selectable                                                                                                                                                                                                                                                                                                          | No                    | Ye                                                               | es                       |  |  |  |

| 0                    | Clock supervisor                       | Yes/No<br>selectable                                                                                                                                                                                                                                                                                                          | Ν                     | lo                                                               | Yes                      |  |  |  |

| CPI                  | U functions                            | Number of basic instructions: 136Instruction bit length: 8 bitsInstruction length: 1 to 3 bytesData bit length: 1, 8, and 16 bitsMinimum instruction execution time: 61.5 ns (at machine clock frequency<br>16.25 MHz)Interrupt processing time: 0.6 µs (at machine clock frequency<br>16.25 MHz)                             |                       |                                                                  |                          |  |  |  |

|                      | Ports (Max 52 ports)                   | General-purpose I/O port (N-ch open drain) : 2 ports<br>General-purpose I/O port (CMOS) : 50 ports<br>Programmable input voltage levels of port :<br>Automotive input level / CMOS input level / hysteresis input level                                                                                                       |                       |                                                                  |                          |  |  |  |

|                      | Time-base timer<br>(1 channel)         | Interrupt cycle : 0.5                                                                                                                                                                                                                                                                                                         | ms, 2.1 ms, 8.2 ms, 3 | 32.8 ms (at main osci                                            | llation clock 4 MHz)     |  |  |  |

|                      | Watchdog timer                         | Reset generated cy<br>At main oscillation of<br>At sub oscillation clo                                                                                                                                                                                                                                                        | lock 10 MHz           | :<br>dual clock product) :                                       | Min 105 ms<br>Min 250 ms |  |  |  |

|                      | Wild register                          | Capable of replacing                                                                                                                                                                                                                                                                                                          | g 3 bytes of ROM da   | ıta                                                              |                          |  |  |  |

| Peripheral functions | l <sup>2</sup> C<br>(1 channel)        | Master/slave sending and receiving<br>Bus error function and arbitration function<br>Detecting transmitting direction function<br>Start condition repeated generation and detection functions<br>Built-in wake-up function                                                                                                    |                       |                                                                  |                          |  |  |  |

| Periph               | UART/SIO<br>(1 channel)                | Data transfer capable in UART/SIO<br>Full duplex double buffer,<br>variable data length (5/6/7/8-bit), built-in baud rate generator<br>NRZ type transfer format, error detected function<br>LSB-first or MSB-first can be selected.<br>Clock synchronous (SIO) or clock asynchronous (UART) serial data transfer ca-<br>pable |                       |                                                                  |                          |  |  |  |

|                      | LIN-UART<br>(1 channel)                | Full duplex double b<br>Capable of serial da                                                                                                                                                                                                                                                                                  | ouffer.               | ange of communication<br>ous or asynchronous<br>or or LIN slave. |                          |  |  |  |

|                      | 8/10-bit A/D converter<br>(8 channels) | 8-bit or 10-bit resolu                                                                                                                                                                                                                                                                                                        | ition can be selected | l.                                                               |                          |  |  |  |

### ■ OSCILLATION STABILIZATION WAIT TIME

The initial value of the main clock oscillation stabilization wait time is fixed to the maximum value. The maximum value is shown as follows.

| Oscillation stabilization wait time | Remarks                                           |

|-------------------------------------|---------------------------------------------------|

| (2 <sup>14</sup> -2) / <b>F</b> сн  | Approx. 4.10 ms (at main oscillation clock 4 MHz) |

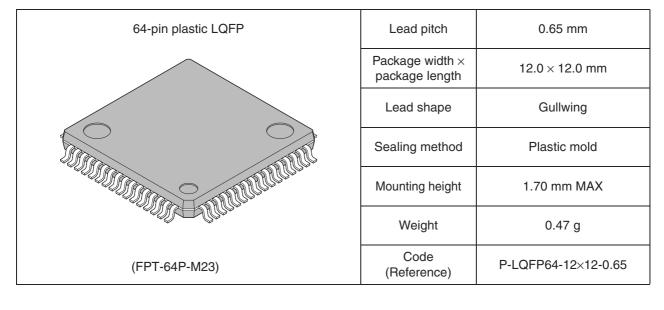

### ■ PACKAGES AND CORRESPONDING PRODUCTS

| Part number<br>Package | MB95168MA | MB95F168MA/<br>F168NA/F168JA | MB95FV100D-103 |

|------------------------|-----------|------------------------------|----------------|

| FPT-64P-M23            | 0         | 0                            | ×              |

| FPT-64P-M24            | 0         | 0                            | ×              |

| BGA-224P-M08           | ×         | ×                            | 0              |

$\bigcirc$ : Available

$\times$  : Unavailable

### (Continued)

| Pin no. | Pin name                 | I/O circuit<br>type*1 | Function                                                                                                       |   |                                                                                                   |

|---------|--------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------------------------|

| 55      | P67/SEG23/<br>SIN        | N                     | General-purpose I/O port.<br>The pin is shared with LCDC SEG output (SEG23) and LIN-UART<br>data input (SIN) . |   |                                                                                                   |

| 56      | P07/INT07/<br>AN07/SEG24 |                       |                                                                                                                |   |                                                                                                   |

| 57      | P06/INT06/<br>AN06/SEG25 |                       |                                                                                                                |   |                                                                                                   |

| 58      | P05/INT05/<br>AN05/SEG26 |                       |                                                                                                                |   |                                                                                                   |

| 59      | P04/INT04/<br>AN04/SEG27 | _                     | F                                                                                                              | F | General-purpose I/O ports.<br>The pins are shared with external interrupt input (INT00 to INT07), |

| 60      | P03/INT03/<br>AN03/SEG28 |                       | A/D analog input (AN00 to AN07) and LCDC SEG output (SEG31 to SEG24) .                                         |   |                                                                                                   |

| 61      | P02/INT02/<br>AN02/SEG29 |                       |                                                                                                                |   |                                                                                                   |

| 62      | P01/INT01/<br>AN01/SEG30 |                       |                                                                                                                |   |                                                                                                   |

| 63      | P00/INT00/<br>AN00/SEG31 |                       |                                                                                                                |   |                                                                                                   |

| 64      | AVss                     |                       | Power supply pin (GND) of A/D converter                                                                        |   |                                                                                                   |

\*1 : Refer to "

I/O CIRCUIT TYPE" for details on the I/O circuit types.

\*2 : When using P07 for segment output (SEG24) of LCDC, P95 can not be used as an output port. It can be used only as an input port.

#### • Mode Pin (MOD)

Connect the MOD pin directly to  $V\mbox{cc}$  or  $V\mbox{ss}.$

To prevent the device unintentionally entering test mode due to noise, lay out the printed circuit board so as to minimize the distance from the MOD pin to  $V_{CC}$  or  $V_{SS}$  and to provide a low-impedance connection.

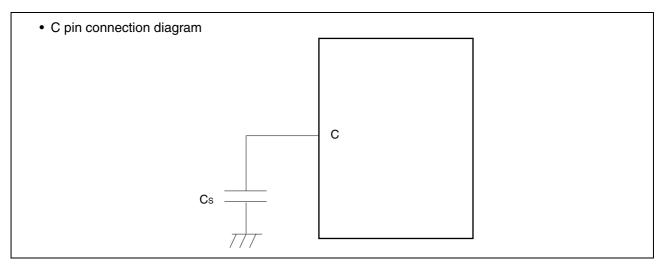

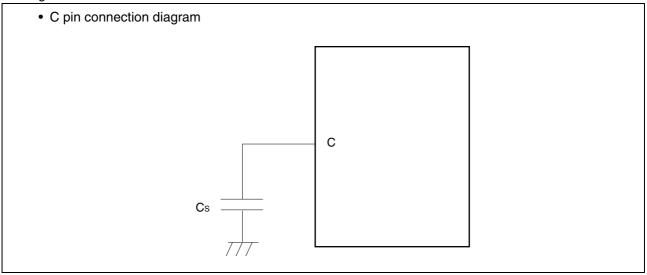

• C Pin

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. A bypass capacitor of  $V_{\rm CC}$  pin must have a capacitance value higher than Cs. For connection of smoothing capacitor Cs, refer to the diagram below.

#### • Analog Power Supply

Always set the same potential to  $AV_{CC}$  and  $V_{CC}$  pins. When  $V_{CC} > AV_{CC}$ , the current may flow through the AN00 to AN07 pins.

• Treatment of Power Supply Pins on A/D Converter

Connect to be  $AV_{CC} = V_{CC}$  and  $AV_{SS} = AVR = V_{SS}$  even if the A/D converter is not in use.

Noise riding on the AV<sub>cc</sub> pin may cause accuracy degradation. So, connect approx. 0.1  $\mu$ F ceramic capacitor as a bypass capacitor between AV<sub>cc</sub> and AV<sub>ss</sub> pins in the vicinity of this device.

### ■ I/O MAP

| Address              | Register<br>abbreviation | Register name                                        | R/W | Initial value |

|----------------------|--------------------------|------------------------------------------------------|-----|---------------|

| 0000н                | PDR0                     | Port 0 data register                                 | R/W | 0000000в      |

| <b>0001</b> н        | DDR0                     | Port 0 direction register                            | R/W | 0000000в      |

| 0002н                | PDR1                     | Port 1 data register                                 | R/W | 0000000в      |

| 0003н                | DDR1                     | Port 1 direction register                            | R/W | 0000000в      |

| 0004н                |                          | (Disabled)                                           | —   |               |

| 0005н                | WATR                     | Oscillation stabilization wait time setting register | R/W | 11111111в     |

| 0006н                | PLLC                     | PLL control register                                 | R/W | 0000000в      |

| 0007н                | SYCC                     | System clock control register                        | R/W | 1010Х011в     |

| 0008н                | STBC                     | Standby control register                             | R/W | 0000000в      |

| 0009н                | RSRR                     | Reset factor register                                | R/W | XXXXXXXX      |

| 000Ан                | TBTC                     | Time-base timer control register                     | R/W | 0000000в      |

| 000Вн                | WPCR                     | Watch prescaler control register                     | R/W | 0000000в      |

| 000Сн                | WDTC                     | Watchdog timer control register                      | R/W | 0000000в      |

| 000Dн                |                          | (Disabled)                                           | —   | —             |

| 000Eн                | PDR2                     | Port 2 data register                                 | R/W | 0000000в      |

| 000Fн                | DDR2                     | Port 2 direction register                            | R/W | 0000000в      |

| 0010⊦<br>to<br>0015⊦ | _                        | (Disabled)                                           | _   | _             |

| <b>0016</b> H        | PDR6                     | Port 6 data register                                 | R/W | 0000000в      |

| <b>0017</b> н        | DDR6                     | Port 6 direction register                            | R/W | 0000000в      |

| 0018⊦<br>to<br>001B⊦ |                          | (Disabled)                                           | _   | _             |

| <b>001С</b> н        | PDR9                     | Port 9 data register                                 | R/W | 0000000в      |

| <b>001D</b> н        | DDR9                     | Port 9 direction register                            | R/W | 0000000в      |

| <b>001Е</b> н        | PDRA                     | Port A data register                                 | R/W | 0000000в      |

| 001Fн                | DDRA                     | Port A direction register                            | R/W | 0000000в      |

| 0020н                | PDRB                     | Port B data register                                 | R/W | 0000000в      |

| <b>0021</b> н        | DDRB                     | Port B direction register                            | R/W | 0000000в      |

| 0022н                | PDRC                     | Port C data register                                 | R/W | 0000000в      |

| 0023н                | DDRC                     | Port C direction register                            | R/W | 0000000в      |

| 0024н<br>to<br>002Сн | _                        | (Disabled)                                           | _   | _             |

| Address              | Register<br>abbreviation | Register name                                                     | R/W | Initial value |

|----------------------|--------------------------|-------------------------------------------------------------------|-----|---------------|

| <b>0059</b> н        | TDR0                     | UART/SIO serial output data register ch.0                         | R/W | 0000000в      |

| 005 <b>А</b> н       | RDR0                     | UART/SIO serial input data register ch.0                          | R   | 0000000в      |

| 005Вн<br>to<br>005Fн |                          | (Disabled)                                                        |     | _             |

| 0060н                | IBCR00                   | I <sup>2</sup> C bus control register 0 ch.0                      | R/W | 0000000в      |

| <b>0061</b> н        | IBCR10                   | I <sup>2</sup> C bus control register 1 ch.0                      | R/W | 0000000в      |

| 0062н                | IBSR0                    | I <sup>2</sup> C bus status register ch.0                         | R   | 0000000в      |

| 0063н                | IDDR0                    | l <sup>2</sup> C data register ch.0                               | R/W | 0000000в      |

| 0064н                | IAAR0                    | I <sup>2</sup> C address register ch.0                            | R/W | 0000000в      |

| 0065н                | ICCR0                    | I <sup>2</sup> C clock control register ch.0                      | R/W | 0000000в      |

| 0066н<br>to<br>006Вн |                          | (Disabled)                                                        |     | _             |

| 006Сн                | ADC1                     | 8/10-bit A/D converter control register 1                         | R/W | 0000000в      |

| 006Dн                | ADC2                     | 8/10-bit A/D converter control register 2                         | R/W | 0000000в      |

| 006Eн                | ADDH                     | 8/10-bit A/D converter data register (upper byte)                 | R/W | 0000000в      |

| 006Fн                | ADDL                     | 8/10-bit A/D converter data register (lower byte)                 | R/W | 0000000в      |

| 0070н                | WCSR                     | Watch counter status register                                     | R/W | 0000000в      |

| <b>0071</b> н        |                          | (Disabled)                                                        |     |               |

| 0072н                | FSR                      | Flash memory status register                                      | R/W | 000Х000в      |

| 0073н                | SWRE0                    | Flash memory sector writing control register 0                    | R/W | 0000000в      |

| 0074н                | SWRE1                    | Flash memory sector writing control register 1                    | R/W | 0000000в      |

| 0075н                |                          | (Disabled)                                                        |     |               |

| 0076н                | WREN                     | Wild register address compare enable register                     | R/W | 0000000в      |

| 0077н                | WROR                     | Wild register data test setting register                          | R/W | 0000000в      |

| 0078н                |                          | Register bank pointer (RP),<br>Mirror of direct bank pointer (DP) |     |               |

| 0079н                | ILR0                     | Interrupt level setting register 0                                | R/W | 11111111в     |

| 007Ан                | ILR1                     | Interrupt level setting register 1                                | R/W | 11111111в     |

| 007Bн                | ILR2                     | Interrupt level setting register 2                                | R/W | 11111111в     |

| 007Сн                | ILR3                     | Interrupt level setting register 3                                | R/W | 11111111      |

| 007Dн                | ILR4                     | Interrupt level setting register 4                                | R/W | 11111111в     |

| <b>007Е</b> н        | ILR5                     | Interrupt level setting register 5                                | R/W | 11111111в     |

| <b>007F</b> н        |                          | (Disabled)                                                        | _   |               |

| 0F80н                | WRARH0                   | Wild register address setting register (upper byte) ch.0          | R/W | 0000000в      |

|                      | •                        |                                                                   |     | (Continued    |

### (Continued)

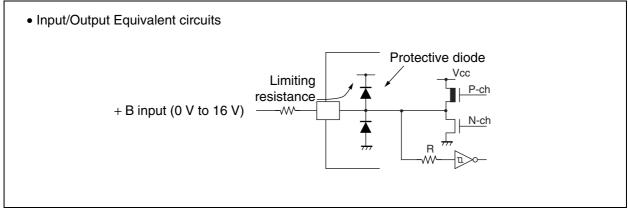

- \*1 : The parameter is based on  $V_{\mbox{\scriptsize SS}}=0.0$  V.

- \*2 : Apply equal potential to AVcc and Vcc. AVR should not exceed AVcc + 0.3 V.

- \*3 : V0 to V3 should not exceed Vcc + 0.3 V.

- \*4 : V<sub>I</sub> and Vo should not exceed V<sub>CC</sub> + 0.3 V. V<sub>I</sub> must not exceed the rating voltage. However, if the maximum current to/from an input is limited by some means with external components, the I<sub>CLAMP</sub> rating supersedes the V<sub>I</sub> rating.

- \*5 : Applicable to pins :

- P00 to P07, P10 to P14, P20 to P22,P60 to P67, P90 to P95, PA0 to PA3, PB0 to PB7, PC0 to PC7

- Use within recommended operating conditions.

- Use at DC voltage (current).

- + B signal is an input signal that exceeds  $V_{CC}$  voltage. The + B signal should always be applied a limiting resistance placed between the + B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the + B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this affects other devices.

- Note that if the + B signal is inputted when the microcontroller power supply is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the + B input is applied during power-on, the power supply is provided from the pins and the resulting power supply voltage may not be sufficient to operate the power-on reset.

- Care must be taken not to leave the + B input pin open.

- •Note that analog system input/output pins other than the A/D input pins (LCD drive pins, etc.) cannot accept + B signal input.

- Sample recommended circuits :

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

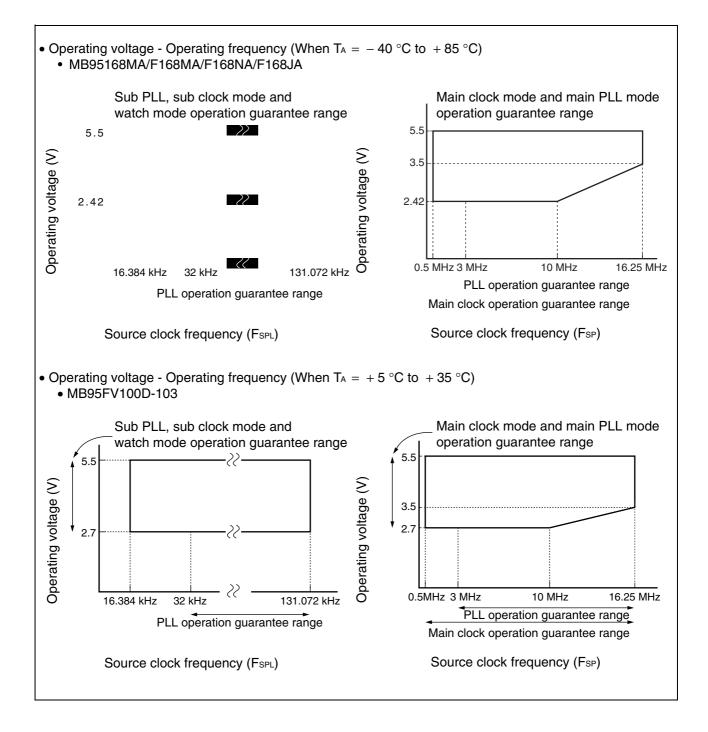

### 2. Recommended Operating Conditions

(Vss = 0.0 V)

| Parameter                                | Symbol Condi- Value |       | Unit      | Remarks           |      |                                                                                                                     |                    |  |

|------------------------------------------|---------------------|-------|-----------|-------------------|------|---------------------------------------------------------------------------------------------------------------------|--------------------|--|

| Falametei                                | Symbol              | tions | Min       | Max               | Unit | neman                                                                                                               | <b>N</b> 5         |  |

|                                          |                     |       | 2.42*1,*2 | 5.5* <sup>1</sup> |      | In normal operating                                                                                                 | Other than         |  |

| Power supply                             | Vcc,                |       | 2.3       | 5.5               | v    | Hold condition in STOP mode                                                                                         | MB95FV100D-<br>103 |  |

| voltage                                  | AVcc                |       | 2.7       | 5.5               | v    | In normal operating                                                                                                 | MB95FV100D-        |  |

|                                          |                     |       | 2.3       | 5.5               |      | Hold condition in STOP mode                                                                                         | 103                |  |

| Power supply<br>voltage for LCD          | V0<br>to<br>V3      | —     | Vss       | Vcc               | v    | The range of liquid crystal power supply<br>(The optimal value depends on liquid<br>crystal display elements used.) |                    |  |

| A/D converter<br>reference input voltage | AVR                 |       | 4.0       | AVcc              | V    |                                                                                                                     |                    |  |

| Smoothing capacitor                      | Cs                  |       | 0.1       | 1.0               | μF   | *3                                                                                                                  |                    |  |

|                                          | Ta                  |       | - 40      | + 85              | °C   | Other than MB95FV10                                                                                                 | 0D-103             |  |

| Operating temperature                    | IA                  |       | + 5       | +35               | °C   | MB95FV100D-103                                                                                                      |                    |  |

\*1 : The values vary with the operating frequency, machine clock or analog guarantee range.

\*2 : When the low voltage detection reset is used, reset occurs while the low voltage is detected. For details on Low voltage detection, see "(9) Low Voltage Detection" in "4. AC Characteristics ".

\*3 : Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. A bypass capacitor of V<sub>cc</sub> pin must have a capacitor value higher than C<sub>s</sub>. For connection of smoothing capacitor C<sub>s</sub>, refer to the diagram below.

# WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

### 3. DC Characteristics

|                             | Sym-  |                                                                                                                     |                   | = 5.0 V ± 10%, Vss = 0.0 V<br>Value |   |           |      |                                                             |  |

|-----------------------------|-------|---------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------|---|-----------|------|-------------------------------------------------------------|--|

| Parameter                   | bol   | Pin name                                                                                                            | Conditions        | Min Ty                              |   | Max       | Unit | Remarks                                                     |  |

| "H" level input<br>voltage  | VIH1  | P10, P67                                                                                                            | *1                | 0.7 Vcc                             | _ | Vcc + 0.3 | V    | When selecting<br>CMOS input level                          |  |

|                             | VIH2  | P23, P24                                                                                                            | *1                | 0.7 Vcc                             |   | Vss + 5.5 | V    |                                                             |  |

|                             | VIHA  | P00 to P07,<br>P10 to P14,<br>P20 to P22,<br>P60 to P67,<br>P90 to P95,<br>PA0 to PA3,<br>PB0 to PB7,<br>PC0 to PC7 |                   | 0.8 Vcc                             |   | Vcc + 0.3 | V    | Port inputs if Auto-<br>motive input levels<br>are selected |  |

|                             | VIHS1 | P00 to P07,<br>P10 to P14,<br>P20 to P22,<br>P60 to P67,<br>P90 to P95,<br>PA0 to PA3,<br>PB0 to PB7,<br>PC0 to PC7 | *1                | 0.8 Vcc                             |   | Vcc + 0.3 | v    | Hysteresis input                                            |  |

|                             | VIHS2 | P23, P24                                                                                                            | *1                | 0.8 Vcc                             | _ | Vss + 5.5 | V    |                                                             |  |

|                             | VIHM  | RST, MOD                                                                                                            |                   | 0.8 Vcc                             | _ | Vcc + 0.3 | V    |                                                             |  |

|                             | VIL   | P10,P23,<br>P24,P67                                                                                                 | *1                | Vss - 0.3                           | _ | 0.3 Vcc   | V    | Hysteresis input<br>(When selecting<br>CMOS input level)    |  |

| "L" level input<br>voltage  | Vila  | P00 to P07,<br>P10 to P14,<br>P20 to P24,<br>P60 to P67,<br>P90 to P95,<br>PA0 to PA3,<br>PB0 to PB7,<br>PC0 to PC7 |                   | Vss - 0.3                           |   | 0.5 Vcc   | V    | Port inputs if<br>Automotive input<br>levels are selected   |  |

| voltage                     | Vils  | P00 to P07,<br>P10 to P14,<br>P20 to P24,<br>P60 to P67,<br>P90 to P95,<br>PA0 to PA3,<br>PB0 to PB7,<br>PC0 to PC7 | *1                | Vss - 0.3                           |   | 0.2 Vcc   | v    | Hysteresis input                                            |  |

|                             | VILM  | RST, MOD                                                                                                            |                   | Vss - 0.3                           |   | 0.3 Vcc   | V    | Hysteresis input                                            |  |

| "H" level<br>output voltage | Vон   | All output pins                                                                                                     | Іон =<br>– 4.0 mA | $V_{\text{cc}}-0.5$                 |   |           | V    |                                                             |  |

| "L" level output voltage    | Vol   | RST* <sup>2</sup> ,<br>All output pins                                                                              | lo∟ = 4.0 mA      |                                     |   | 0.4       | ۷    |                                                             |  |

$(Vcc = 5.0 V \pm 10\%, Vss = 0.0 V, T_A = -40 \circ C to + 85 \circ C)$

|                                                              | Sym-  |                                            | (Vcc = 5.0 V ± 10%, Vss = 0.0 V<br>Value                                                                                                              |             |      |            |                                                               |                                                                                     |      |      |    |

|--------------------------------------------------------------|-------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|----|

| Parameter                                                    | bol   | Pin name                                   | Conditions                                                                                                                                            | Min Typ Max |      | Unit       | Remarks                                                       |                                                                                     |      |      |    |

| Input leakage<br>current (Hi-Z<br>output leakage<br>current) | Iu    | Ports other than<br>P23, P24               | 0.0 V < Vı < Vcc                                                                                                                                      | - 5         | _    | + 5        | μA                                                            | When the pull-up prohibition setting                                                |      |      |    |

| Open drain<br>output leakage<br>current                      |       | P23, P24                                   | 0.0 V < VI < Vss<br>+ 5.5 V                                                                                                                           |             |      | 5          | μA                                                            |                                                                                     |      |      |    |

| Pull-up<br>resistor                                          | RPULL | P10 to P14,<br>P20 to P22                  | $V_{I} = 0.0 V$                                                                                                                                       | 25          | 50   | 100        | kΩ                                                            | When the pull-up permission setting                                                 |      |      |    |

| Pull-down<br>resistor                                        | Rмор  | MOD                                        | VI = Vcc                                                                                                                                              | 50          | 100  | 200        | kΩ                                                            | Mask ROM<br>product only                                                            |      |      |    |

| Input<br>capacitance                                         | CIN   | Other than AVcc,<br>AVss, AVR, Vcc,<br>Vss | f = 1 MHz                                                                                                                                             |             | 5    | 15         | pF                                                            |                                                                                     |      |      |    |

|                                                              |       |                                            | Fсн = 20 MHz                                                                                                                                          |             | 9.5  | 12.5       | mA                                                            | Flash memory<br>product<br>(At other than<br>Flash memory writ-<br>ing and erasing) |      |      |    |

|                                                              |       |                                            | $F_{MP} = 10 \text{ MHz}$<br>Main clock mode<br>(divided by 2)                                                                                        | _           | 30.0 | 35.0       | mA                                                            | Flash memory<br>product<br>(At Flash memory<br>writing and eras-<br>ing)            |      |      |    |

|                                                              | 1     |                                            |                                                                                                                                                       | _           | 7.2  | 9.5        | mA                                                            | Mask ROM<br>product                                                                 |      |      |    |

| Power supply current*3                                       | Icc   | Vcc<br>(External clock<br>operation)       | Fсн = 32 MHz                                                                                                                                          |             | 15.2 | 20.0       | mA                                                            | Flash memory<br>product<br>(At other than<br>Flash memory writ-<br>ing and erasing) |      |      |    |

|                                                              |       |                                            |                                                                                                                                                       |             |      | opolation) | F <sub>MP</sub> = 16 MHz<br>Main clock mode<br>(divided by 2) |                                                                                     | 35.7 | 42.5 | mA |

|                                                              |       |                                            |                                                                                                                                                       |             | 11.6 | 15.2       | mA                                                            | Mask ROM<br>product                                                                 |      |      |    |

|                                                              | 1000  |                                            | $\label{eq:Fch} \begin{split} F_{CH} &= 20 \text{ MHz} \\ F_{MP} &= 10 \text{ MHz} \\ \text{Main Sleep mode} \\ (\text{divided by 2}) \end{split}$    |             | 4.5  | 7.5        | mA                                                            |                                                                                     |      |      |    |

|                                                              | Iccs  |                                            | $\label{eq:Fch} \begin{array}{l} F_{CH} = 32 \mbox{ MHz} \\ F_{MP} = 16 \mbox{ MHz} \\ Main \mbox{ Sleep mode} \\ (divided \mbox{ by 2}) \end{array}$ |             | 7.2  | 12.0       | mA                                                            |                                                                                     |      |      |    |

(Vcc = 5.0 V  $\pm$  10%, Vss = 0.0 V, T\_A = - 40 °C to + 85 °C)

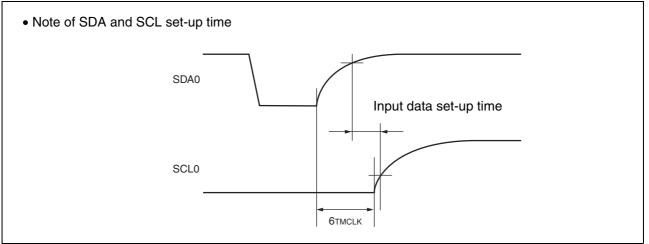

#### (8) I<sup>2</sup>C Timing

|                                                                                  |         | (Vcc = 5     | 5.0 V ± 10%, A           | Vss = Vss | s = 0.0 V, <sup>·</sup> | $T_{A} = -40$ | °C to +           | 85 °C) |

|----------------------------------------------------------------------------------|---------|--------------|--------------------------|-----------|-------------------------|---------------|-------------------|--------|

|                                                                                  |         |              |                          | Val       | ue                      |               |                   |        |

| Parameter                                                                        | Symbol  | Pin<br>name  | Conditions               | Standar   | d-mode                  | Fast-         | mode              | Unit   |

|                                                                                  |         |              |                          | Min       | Max                     | Min           | Max               |        |

| SCL clock frequency                                                              | fsc∟    | SCL0         |                          | 0         | 100                     | 0             | 400               | kHz    |

| (Repeat) Start condition hold time SDA $\downarrow \rightarrow$ SCL $\downarrow$ | thd;sta | SCL0<br>SDA0 |                          | 4.0       | —                       | 0.6           |                   | μs     |

| SCL clock "L" width                                                              | t∟ow    | SCL0         |                          | 4.7       |                         | 1.3           |                   | μs     |

| SCL clock "H" width                                                              | tніgн   | SCL0         |                          | 4.0       | —                       | 0.6           |                   | μs     |

| (Repeat) Start condition setup time SCL $\uparrow \rightarrow$ SDA $\downarrow$  | tsu;sta | SCL0<br>SDA0 | R = 1.7 kΩ,              | 4.7       | —                       | 0.6           |                   | μs     |

| Data hold time SCL $\downarrow \rightarrow$ SDA $\downarrow \uparrow$            | thd;dat | SCL0<br>SDA0 | $C = 50 \text{ pF}^{*1}$ | 0         | 3.45* <sup>2</sup>      | 0             | 0.9* <sup>3</sup> | μs     |

| Data setup time SDA $\downarrow \uparrow \rightarrow$ SCL $\uparrow$             | tsu;dat | SCL0<br>SDA0 |                          | 0.25*4    |                         | 0.1*4         | _                 | μs     |

| Stop condition setup time SCL $\uparrow \rightarrow$ SDA $\uparrow$              | tsu;sto | SCL0<br>SDA0 |                          | 4.0       |                         | 0.6           |                   | μs     |

| Bus free time between stop condition and start condition                         | tbur    | SCL0<br>SDA0 |                          | 4.7       |                         | 1.3           | _                 | μs     |

\*1 : R, C : Pull-up resistor and load capacitor of the SCL and SDA lines.

\*2 : The maximum thd;DAT have only to be met if the device dose not stretch the "L" width (tLOW) of the SCL signal.

\*3 : A fast-mode I<sup>2</sup>C-bus device can be used in a standard-mode I<sup>2</sup>C-bus system, but the requirement  $t_{SU;DAT} \ge 250$  ns must then be met.

\*4 : Refer to " • Note of SDA and SCL set-up time".

The rating of the input data set-up time in the device connected to the bus cannot be satisfied depending on the load capacitance or pull-up resistor.

Be sure to adjust the pull-up resistor of SDA and SCL if the rating of the input data set-up time cannot be satisfied.

| _                                                                 | Sym-             | Pin          | Condi-                          | -                                       | 0, AVSS = VSS = 0.0 V                   |                                   |                                                                                                                                                                                                 |    |  |

|-------------------------------------------------------------------|------------------|--------------|---------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| Parameter                                                         | bol              | name         | tions                           | Min                                     | Мах                                     | Unit                              | Remarks                                                                                                                                                                                         |    |  |

| SCL clock<br>"L" width                                            | tLOW             | SCL0         |                                 | (2 + nm / 2) tмськ –<br>20              |                                         | ns                                | Master mode                                                                                                                                                                                     |    |  |

| SCL clock<br>"H" width                                            | <b>t</b> HIGH    | SCL0         |                                 | (nm / 2) t <sub>MCLK</sub> – 20         | (nm / 2 ) t <sub>MCLK</sub> + 20        | ns                                | Master mode                                                                                                                                                                                     |    |  |

| Start condition hold time                                         | thd;sta          | SCL0<br>SDA0 |                                 | (–1 + nm / 2) tмськ –<br>20             | (–1 + nm) t <sub>мськ</sub> + 20        | ns                                | Master mode<br>Maximum value is<br>applied when m,<br>n = 1, 8.<br>Otherwise, the<br>minimum value is<br>applied.                                                                               |    |  |

| Stop condition setup time                                         | tsu;sto          | SCL0<br>SDA0 |                                 | (1 + nm / 2) tмськ –<br>20              | (1 + nm / 2) tмськ + 20                 | ns                                | Master mode                                                                                                                                                                                     |    |  |

| Start condition setup time                                        | tsu;sta          | SCL0<br>SDA0 |                                 | (1 + nm / 2) tмськ -<br>20              | (1 + nm / 2) tмськ + 20                 | ns                                | Master mode                                                                                                                                                                                     |    |  |

| Bus free time<br>between stop<br>condition and<br>start condition | t <sub>BUF</sub> | SCL0<br>SDA0 |                                 |                                         |                                         | (2 nm + 4) t <sub>MCLK</sub> – 20 |                                                                                                                                                                                                 | ns |  |

| Data hold time                                                    | thd;dat          | SCL0<br>SDA0 |                                 | 3 tмськ – 20                            | _                                       | ns                                | Master mode                                                                                                                                                                                     |    |  |

| Data setup<br>time                                                | tsu;dat          | SCL0<br>SDA0 | R = 1.7 kΩ,<br>$C = 50 pF^{*1}$ | (—2 + nm / 2) t <sub>MCLK</sub> —<br>20 | (-1 + nm / 2) t <sub>MCLK</sub> +<br>20 | ns                                | Master mode<br>When assuming<br>that "L" of SCL is<br>not extended, the<br>minimum value is<br>applied to first bit<br>of continuous<br>data.<br>Otherwise,<br>the maximum<br>value is applied. |    |  |

| Setup time<br>between<br>clearing<br>interrupt and<br>SCL rising  | tsu;int          | SCL0         |                                 | (nm / 2) t <sub>мськ</sub> – 20         | (1 + nm / 2) tмськ + 20                 | ns                                | Minimum value is<br>applied to interrupt<br>at 9th SCL $\downarrow$ .<br>Maximum value is<br>applied to interrupt<br>at 8th SCL $\downarrow$ .                                                  |    |  |

| SCL clock "L" width                                               | t∟ow             | SCL0         |                                 | 4 tмськ – 20                            |                                         | ns                                | At reception                                                                                                                                                                                    |    |  |

| SCL clock "H" width                                               | tніgн            | SCL0         |                                 | 4 tмськ – 20                            |                                         | ns                                | At reception                                                                                                                                                                                    |    |  |

| Start condition detection                                         | thd;sta          | SCL0<br>SDA0 |                                 | 2 t <sub>MCLK</sub> – 20                |                                         | ns                                | Undetected when<br>1 tMCLK is used at<br>reception                                                                                                                                              |    |  |

(Vcc = 5.0 V  $\pm$  10%, AVss = Vss = 0.0 V, T\_A = -40  $^\circ C$  to ~+ 85  $^\circ C)$

(Continued)

$(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ AV}_{SS} = V_{SS} = 0.0 \text{ V}, \text{ T}_{A} = -40 \text{ }^{\circ}\text{C} \text{ to } + 85 \text{ }^{\circ}\text{C})$

| Parameter                             | Sym-<br>bol     | Pin<br>name  | Condi-<br>tions                 | Value* <sup>2</sup>                                         |     | Unit | Remarks                                            |

|---------------------------------------|-----------------|--------------|---------------------------------|-------------------------------------------------------------|-----|------|----------------------------------------------------|

| Farameter                             |                 |              |                                 | Min                                                         | Max | Unit | neillaiks                                          |

| Stop condition<br>detection           | <b>t</b> su;sто | SCL0<br>SDA0 | R = 1.7 kΩ,<br>$C = 50 pF^{*1}$ | 2 tмськ – 20                                                |     | ns   | Undetected when 1<br>tмс∟к is used at<br>reception |

| Restart condition detection condition | tsu;sta         | SCL0<br>SDA0 |                                 | 2 tмськ – 20                                                |     | ns   | Undetected when 1<br>tмс∟к is used at<br>reception |

| Bus free time                         | tBUF            | SCL0<br>SDA0 |                                 | 2 тмськ – 20                                                |     | ns   | At reception                                       |

| Data hold time                        | <b>t</b> hd;dat | SCL0<br>SDA0 |                                 | 2 тмськ – 20                                                | _   | ns   | At slave transmission mode                         |

| Data setup time                       | tsu;dat         | SCL0<br>SDA0 |                                 | t∟ow – 3 tмс∟к –<br>20                                      | _   | ns   | At slave transmission mode                         |

| Data hold time                        | thd;dat         | SCL0<br>SDA0 |                                 | 0                                                           |     | ns   | At reception                                       |

| Data setup time                       | tsu;dat         | SCL0<br>SDA0 |                                 | tмськ — 20                                                  | _   | ns   | At reception                                       |

| SDA↓→SCL↑<br>(at wakeup function)     | twake-<br>UP    | SCL0<br>SDA0 |                                 | Oscillation<br>stabilization<br>wait time +<br>2 tmclk – 20 |     | ns   |                                                    |

\*1 : R, C : Pull-up resistor and load capacitor of the SCL and SDA lines.

\*2 : •Refer to " (2) Source Clock/Machine Clock" for tmcLK.

- m is CS4 bit and CS3 bit (bit 4 and bit 3) of I<sup>2</sup>C clock control register (ICCR) .

- n is CS2 bit to CS0 bit (bit 2 to bit 0) of I<sup>2</sup>C clock control register (ICCR) .

- Actual timing of I<sup>2</sup>C is determined by m and n values set by the machine clock ( $t_{MCLK}$ ) and CS4 to CS0 of ICCR0 register.

FUITSU

Standard-mode : m and n can be set at the range : 0.9 MHz < t<sub>MCLK</sub> (machine clock) < 10 MHz.</li>

Setting of m and n determines the machine clock that can be used below.

$(m, n) = (1, 8) : 0.9 \text{ MHz} < t_{MCLK} \le 1 \text{ MHz}$

$$(m,\,n) \;=\; (1,\,22)\;,\;\; (5,\,4)\;,\;\; (6,\,4)\;,\;\; (7,\,4)\;,\;\; (8,\,4)\;\; : 0.9\;MHz < t_{\text{MCLK}} \leq 2\;MHz$$

- $(m,\,n) \;=\; (1,\,38)\;,\;\; (5,\,8)\;,\;\; (6,\,8)\;,\;\; (7,\,8)\;,\;\; (8,\,8)\;\; : 0.9\;MHz < t_{\text{MCLK}} \leq 4\;MHz$

- $(m, n) = (1, 98) : 0.9 \text{ MHz} < t_{MCLK} \le 10 \text{ MHz}$

- Fast-mode :

m and n can be set at the range : 3.3 MHz <  $t_{MCLK}$  (machine clock) < 10 MHz. Setting of m and n determines the machine clock that can be used below.

$(m, n) = (1, 8) : 3.3 \text{ MHz} < t_{MCLK} \le 4 \text{ MHz}$

$(m,\,n) \;=\; (1,\,22)\;,\;\; (5,\,4): 3.3\;MHz < t_{\text{MCLK}} \leq 8\;MHz$

$(m, n) = (6, 4) : 3.3 \text{ MHz} < t_{MCLK} \le 10 \text{ MHz}$

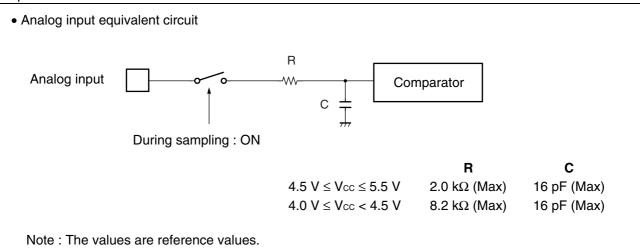

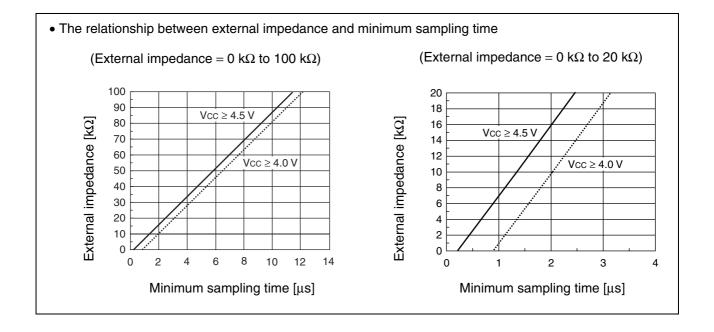

### (2) Notes on Using A/D Converter

#### About the external impedance of analog input and its sampling time

A/D converter with sample and hold circuit. If the external impedance is too high to keep sufficient sampling time, the analog voltage charged to the internal sample and hold capacitor is insufficient, adversely affecting A/D conversion precision. Therefore, to satisfy the A/D conversion precision standard, consider the relationship between the external impedance and minimum sampling time and either adjust the register value and operating frequency or decrease the external impedance so that the sampling time is longer than the minimum value. Also, if the sampling time cannot be sufficient, connect a capacitor of about 0.1  $\mu$ F to the analog input pin.

#### About errors

As  $|V_{\text{CC}} - V_{\text{SS}}|$  becomes smaller, values of relative errors grow larger.

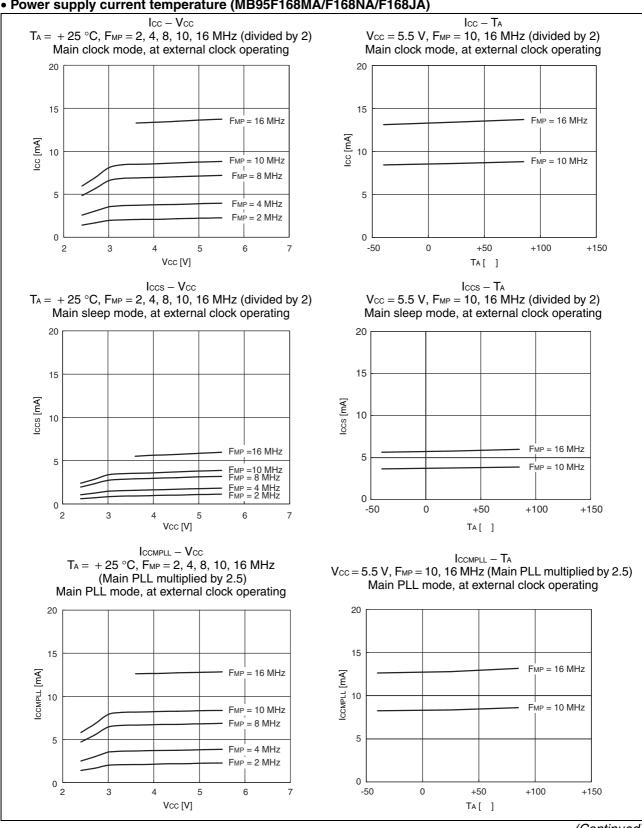

### EXAMPLE CHARACTERISTICS

#### • Power supply current temperature (MB95F168MA/F168NA/F168JA)

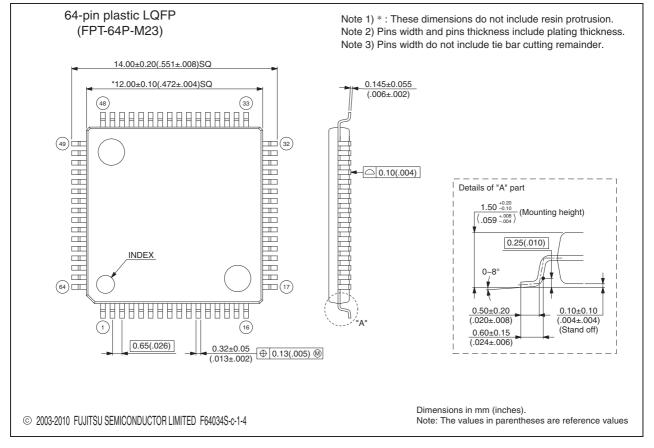

### ■ PACKAGE DIMENSIONS

FUITSU

### ■ MAJOR CHANGES IN THIS EDITION

| Page | Section                                                                       | Change Results                                                                                                                                                                                                                                                                                                                                            |

|------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35   | <ul> <li>ELECTRICAL CHARACTERISTICS</li> <li>3. DC Characteristics</li> </ul> | Corrected note *1 below the table.<br>(The value is 2.88 V when the low voltage detection reset is<br>used.<br>$\rightarrow$ The input level of P10, P23, P24 and P67 can be<br>switched to either the "CMOS input level" or "Hysteresis in-<br>put level". The switching of the input level can be set by the<br>input level selection register (ILSR).) |

The vertical lines marked in the left side of the page show the changes.