Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 180MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, SD, SPI, SSI, SSP, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 83                                                                                |

| Program Memory Size        | -                                                                                 |

| Program Memory Type        | ROMIess                                                                           |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 136K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                              |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

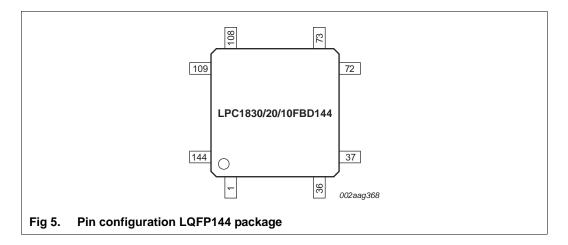

| Package / Case             | 144-LQFP                                                                          |

| Supplier Device Package    | 144-LQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1810fbd144-551         |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M3 microcontroller

## 6.2 Pin description

On the LPC1850/30/20/10, digital pins are grouped into 16 ports, named P0 to P9 and PA to PF, with up to 20 pins used per port. Each digital pin can support up to eight different digital functions, including General-Purpose I/O (GPIO), selectable through the System Configuration Unit (SCU) registers. The pin name is not indicative of the GPIO port assigned to it.

Not all functions listed in <u>Table 3</u> are available on all packages. See <u>Table 2</u> for availability of USB0, USB1, Ethernet, and LCD functions.

The parts contain two 10-bit ADCs (ADC0 and ADC1). The input channels of ADC0 and ADC1 on dedicated pins and multiplexed pins are combined in such a way that all channel 0 inputs (named ADC0\_0 and ADC1\_0) are tied together and connected to both, channel 0 on ADC0 and channel 0 on ADC1, channel 1 inputs (named ADC0\_1 and ADC1\_1) are tied together and connected to channel 1 on ADC0 and ADC1, and so forth. There are eight ADC channels total for the two ADCs.

LPC1850\_30\_20\_10

7 of 153

## 32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144                |     | Reset state<br>[1] | Type | Description                                                                                                                                                                                        |

|--------|---------|----------|----------|------------------------|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1_5   | R5      | N3       | J4       | 48                     | [2] | N; PU              | I/O  | GPIO1[8] — General purpose digital input/output pin.                                                                                                                                               |

|        |         |          |          |                        |     |                    | 0    | <b>CTOUT_10</b> — SCTimer/PWM output 10. Match output 3 of timer 3.                                                                                                                                |

|        |         |          |          |                        |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |                        |     |                    | 0    | EMC_CS0 — LOW active Chip Select 0 signal.                                                                                                                                                         |

|        |         |          |          |                        |     |                    | I    | <b>USB0_PWR_FAULT</b> — Port power fault signal indicating overcurrent condition; this signal monitors over-current on the USB bus (external circuitry required to detect over-current condition). |

|        |         |          |          |                        |     |                    | I/O  | SSP1_SSEL — Slave Select for SSP1.                                                                                                                                                                 |

|        |         |          | -        | R — Function reserved. |     |                    |      |                                                                                                                                                                                                    |

|        |         |          |          |                        |     |                    | 0    | <b>SD_POW</b> — SD/MMC card power monitor output.                                                                                                                                                  |

| P1_6   | T4      | P3       | K4       | 49 <u>[2]</u>          |     | N; PU              | I/O  | GPIO1[9] — General purpose digital input/output pin.                                                                                                                                               |

|        |         |          |          |                        |     |                    | I    | <b>CTIN_5</b> — SCTimer/PWM input 5. Capture input 2 of timer 2.                                                                                                                                   |

|        |         |          |          |                        |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |                        |     |                    | 0    | <b>EMC_WE</b> — LOW active Write Enable signal.                                                                                                                                                    |

|        |         |          |          |                        |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |                        |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |                        |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |                        |     |                    | I/O  | <b>SD_CMD</b> — SD/MMC command signal.                                                                                                                                                             |

| P1_7   | T5      | N4       | G4       | 50                     | [2] | N; PU              | I/O  | <b>GPIO1[0]</b> — General purpose digital input/output pin.                                                                                                                                        |

|        |         |          |          |                        |     |                    | I    | <b>U1_DSR</b> — Data Set Ready input for UART1.                                                                                                                                                    |

|        |         |          |          |                        |     |                    | 0    | <b>CTOUT_13</b> — SCTimer/PWM output 13. Match output 3 of timer 3.                                                                                                                                |

|        |         |          |          |                        |     |                    | I/O  | <b>EMC_D0</b> — External memory data line 0.                                                                                                                                                       |

|        |         |          |          |                        |     |                    | 0    | <b>USB0_PPWR</b> — VBUS drive signal (towards external charge pump or power management unit); indicates that VBUS must be driven (active HIGH).                                                    |

|        |         |          |          |                        |     |                    |      | Add a pull-down resistor to disable the power switch at reset.<br>This signal has opposite polarity compared to the USB_PPWR<br>used on other NXP LPC parts.                                       |

|        |         |          |          |                        |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |                        |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |                        |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256  | TFBGA180 | TFBGA100 | LQFP144                                        |     | Reset state<br>[1] | Type | Description                                                                                                                                                                                        |

|--------|----------|----------|----------|------------------------------------------------|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1_20  | M10      | J10      | K10      | 70                                             | [2] | N; PU              | I/O  | GPIO0[15] — General purpose digital input/output pin.                                                                                                                                              |

|        |          |          |          |                                                |     |                    | I/O  | SSP1_SSEL — Slave Select for SSP1.                                                                                                                                                                 |

|        |          |          |          |                                                |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |          |          |          |                                                |     |                    | 0    | <b>ENET_TXD1</b> — Ethernet transmit data 1 (RMII/MII interface).                                                                                                                                  |

|        |          |          |          |                                                |     |                    | I    | T0_CAP2 — Capture input 2 of timer 0.                                                                                                                                                              |

|        |          |          |          |                                                |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |          |          |          |                                                |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |          |          |          |                                                |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

| P2_0   | T16      | N14      | G10      | 75                                             | [2] | N; PU              | -    | R — Function reserved.                                                                                                                                                                             |

|        | 0<br>1/C |          | 0        | <b>U0_TXD</b> — Transmitter output for USART0. |     |                    |      |                                                                                                                                                                                                    |

|        |          |          | I/O      | EMC_A13 — External memory address line 13.     |     |                    |      |                                                                                                                                                                                                    |

|        |          |          |          |                                                |     |                    | 0    | <b>USB0_PPWR</b> — VBUS drive signal (towards external charge pump or power management unit); indicates that VBUS must be driven (active high).                                                    |

|        |          |          |          |                                                |     |                    |      | Add a pull-down resistor to disable the power switch at reset.<br>This signal has opposite polarity compared to the USB_PPWR<br>used on other NXP LPC parts.                                       |

|        |          |          |          |                                                |     |                    | I/O  | GPIO5[0] — General purpose digital input/output pin.                                                                                                                                               |

|        |          |          |          |                                                |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |          |          |          |                                                |     |                    | I    | T3_CAP0 — Capture input 0 of timer 3.                                                                                                                                                              |

|        |          |          |          |                                                |     |                    | 0    | ENET_MDC — Ethernet MIIM clock.                                                                                                                                                                    |

| P2_1   | N15      | M13      | G7       | 81                                             | [2] | N; PU              | -    | R — Function reserved.                                                                                                                                                                             |

|        |          |          |          |                                                |     |                    | I    | U0_RXD — Receiver input for USART0.                                                                                                                                                                |

|        |          |          |          |                                                |     |                    | I/O  | EMC_A12 — External memory address line 12.                                                                                                                                                         |

|        |          |          |          |                                                |     |                    | I    | <b>USB0_PWR_FAULT</b> — Port power fault signal indicating overcurrent condition; this signal monitors over-current on the USB bus (external circuitry required to detect over-current condition). |

|        |          |          |          |                                                |     |                    | I/O  | GPIO5[1] — General purpose digital input/output pin.                                                                                                                                               |

|        |          |          |          |                                                |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |          |          |          |                                                |     |                    | I    | T3_CAP1 — Capture input 1 of timer 3.                                                                                                                                                              |

|        |          |          |          |                                                |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                          |

|--------|---------|----------|----------|---------|-----|--------------------|------|----------------------------------------------------------------------|

| P6_10  | H15     | G13      | -        | 100     | [2] | N; PU              | I/O  | GPIO3[6] — General purpose digital input/output pin.                 |

|        |         |          |          |         |     |                    | 0    | <b>MCABORT</b> — Motor control PWM, LOW-active fast abort.           |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | 0    | <b>EMC_DQMOUT1</b> — Data mask 1 used with SDRAM and static devices. |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

| P6_11  | H12     | F11      | C9       | 101     | [2] | N; PU              | I/O  | GPIO3[7] — General purpose digital input/output pin.                 |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | 0    | EMC_CKEOUT0 — SDRAM clock enable 0.                                  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | 0    | T2_MAT3 — Match output 3 of timer 2.                                 |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

| P6_12  | G15     | F13      | -        | 103     | [2] | N; PU              | I/O  | GPIO2[8] — General purpose digital input/output pin.                 |

|        |         |          |          |         |     |                    | 0    | <b>CTOUT_7</b> — SCTimer/PWM output 7. Match output 3 of timer 1.    |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | 0    | <b>EMC_DQMOUT0</b> — Data mask 0 used with SDRAM and static devices. |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

| P7_0   | B16     | B14      | -        | 110     | [2] | N; PU              | I/O  | GPIO3[8] — General purpose digital input/output pin.                 |

|        |         |          |          |         |     |                    | 0    | <b>CTOUT_14</b> — SCTimer/PWM output 14. Match output 2 of timer 3.  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | 0    | LCD_LE — Line end signal.                                            |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                               |

#### Table 3. Pin description ... continued

ilahla a ~ // ~ Saa Tabla 2

32-bit ARM Cortex-M3 microcontroller

| Symbol |         |          | -        |         | are | 1                  |      | on all parts. See <u>Table 2</u> . Description                                                                                                                                                  |

|--------|---------|----------|----------|---------|-----|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type |                                                                                                                                                                                                 |

| P7_1   | C14     | C13      | -        | 113     | [2] | N; PU              | I/O  | GPIO3[9] — General purpose digital input/output pin.                                                                                                                                            |

|        |         |          |          |         |     |                    | 0    | <b>CTOUT_15</b> — SCTimer/PWM output 15. Match output 3 of timer 3.                                                                                                                             |

|        |         |          |          |         |     |                    | I/O  | <b>I2S0_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>I</i> <sup>2</sup> <i>S</i> - <i>bus specification</i> . |

|        |         |          |          |         |     |                    | 0    | LCD_VD19 — LCD data.                                                                                                                                                                            |

|        |         |          |          |         |     |                    | 0    | LCD_VD7 — LCD data.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                          |

|        |         |          |          |         |     |                    | 0    | <b>U2_TXD</b> — Transmitter output for USART2.                                                                                                                                                  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                          |

| P7_2   | A16     | A14      | -        | 115     | [2] | N; PU              | I/O  | GPIO3[10] — General purpose digital input/output pin.                                                                                                                                           |

|        |         |          |          |         |     |                    | I    | CTIN_4 — SCTimer/PWM input 4. Capture input 2 of timer 1.                                                                                                                                       |

|        |         |          |          |         |     |                    | I/O  | <b>I2S0_TX_SDA</b> — $I^2S$ transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> <i>S</i> -bus specification.     |

|        |         |          |          |         |     |                    | 0    | LCD_VD18 — LCD data.                                                                                                                                                                            |

|        |         |          |          |         |     |                    | 0    | LCD_VD6 — LCD data.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                          |

|        |         |          |          |         |     |                    | I    | U2_RXD — Receiver input for USART2.                                                                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                          |

| P7_3   | C13     | C12      | -        | 117     | [2] | N; PU              | I/O  | GPIO3[11] — General purpose digital input/output pin.                                                                                                                                           |

|        |         |          |          |         |     |                    | I    | CTIN_3 — SCTimer/PWM input 3. Capture input 1 of timer 1.                                                                                                                                       |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                          |

|        |         |          |          |         |     |                    | 0    | LCD_VD17 — LCD data.                                                                                                                                                                            |

|        |         |          |          |         |     |                    | 0    | LCD_VD5 — LCD data.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                          |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                          |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                          |

Table 3.

Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

## 32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state            | Type | Description                                                                                                                                                                                               |  |  |  |

|--------|---------|----------|----------|---------|-----|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P9_6   | <br>L11 | M9       | -        | 72      | [2] | N; PU                  | I/O  | GPIO4[11] — General purpose digital input/output pin.                                                                                                                                                     |  |  |  |

|        |         |          |          |         |     |                        | 0    | MCOB1 — Motor control PWM channel 1, output B.                                                                                                                                                            |  |  |  |

|        |         |          |          |         |     |                        | I    | <b>USB1_PWR_FAULT</b> — USB1 Port power fault signal indicating over-current condition; this signal monitors over-current on the USB1 bus (external circuitry required to detect over-current condition). |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | I    | ENET_COL — Ethernet Collision detect (MII interface).                                                                                                                                                     |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | I    | U0_RXD — Receiver input for USART0.                                                                                                                                                                       |  |  |  |

| PA_0   | L12     | L10      | -        | -       | [2] | N; PU                  | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         | -   | R — Function reserved. |      |                                                                                                                                                                                                           |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | 0    | I2S1_RX_MCLK — I <sup>2</sup> S1 receive master clock.                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | 0    | CGU_OUT1 — CGU spare clock output 1.                                                                                                                                                                      |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

| PA_1   | J14     | H12      | -        | -       | [3] | N; PU                  | I/O  | GPIO4[8] — General purpose digital input/output pin.                                                                                                                                                      |  |  |  |

|        |         |          |          |         |     |                        | I    | QEI_IDX — Quadrature Encoder Interface INDEX input.                                                                                                                                                       |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | 0    | U2_TXD — Transmitter output for USART2.                                                                                                                                                                   |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

| PA_2   | K15     | J13      | -        | -       | [3] | N; PU                  | I/O  | GPIO4[9] — General purpose digital input/output pin.                                                                                                                                                      |  |  |  |

|        |         |          |          |         |     |                        | I    | <b>QEI_PHB</b> — Quadrature Encoder Interface PHB input.                                                                                                                                                  |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | I    | U2_RXD — Receiver input for USART2.                                                                                                                                                                       |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         |     |                        | -    | R — Function reserved.                                                                                                                                                                                    |  |  |  |

|        |         |          |          |         | -   | R — Function reserved. |      |                                                                                                                                                                                                           |  |  |  |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144                                             |     | Reset state<br>[1] | Type | Description                                                                                     |  |  |  |  |

|--------|---------|----------|----------|-----------------------------------------------------|-----|--------------------|------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| PC_7   | G5      | -        | -        | -                                                   | [2] | N; PU              | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I/O  | USB1_ULPI_D1 — ULPI link bidirectional data line 1.                                             |  |  |  |  |

|        |         |          |          |                                                     |     |                    | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I    | ENET_RXD3 — Ethernet receive data 3 (MII interface).                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I/O  | GPIO6[6] — General purpose digital input/output pin.                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | 0    | T3_MAT0 — Match output 0 of timer 3.                                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I/O  | SD_DAT3 — SD/MMC data bus line 3.                                                               |  |  |  |  |

| PC_8   | N4      | -        | -        | -                                                   | [2] | N; PU              | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          | I/O      | USB1_ULPI_D0 — ULPI link bidirectional data line 0. |     |                    |      |                                                                                                 |  |  |  |  |

|        |         |          |          |                                                     |     |                    | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I    | <b>ENET_RX_DV</b> — Ethernet Receive Data Valid (RMII/MII interface).                           |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I/O  | GPIO6[7] — General purpose digital input/output pin.                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | 0    | T3_MAT1 — Match output 1 of timer 3.                                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I    | SD_CD — SD/MMC card detect input.                                                               |  |  |  |  |

| PC_9   | K2      | -        | -        | -                                                   | [2] | N; PU              | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I    | <b>USB1_ULPI_NXT</b> — ULPI link NXT signal. Data flow control signal from the PHY.             |  |  |  |  |

|        |         |          |          |                                                     |     |                    | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I    | ENET_RX_ER — Ethernet receive error (MII interface).                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I/O  | GPIO6[8] — General purpose digital input/output pin.                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | 0    | T3_MAT2 — Match output 2 of timer 3.                                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | 0    | <b>SD_POW</b> — SD/MMC power monitor output.                                                    |  |  |  |  |

| PC_10  | M5      | -        | -        | -                                                   | [2] | N; PU              | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | 0    | <b>USB1_ULPI_STP</b> — ULPI link STP signal. Asserted to end or interrupt transfers to the PHY. |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I    | U1_DSR — Data Set Ready input for UART1.                                                        |  |  |  |  |

|        |         |          |          |                                                     |     |                    | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I/O  | GPIO6[9] — General purpose digital input/output pin.                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | -    | R — Function reserved.                                                                          |  |  |  |  |

|        |         |          |          |                                                     |     |                    | 0    | T3_MAT3 — Match output 3 of timer 3.                                                            |  |  |  |  |

|        |         |          |          |                                                     |     |                    | I/O  | SD_CMD — SD/MMC command signal.                                                                 |  |  |  |  |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |            | Reset state<br>[1] | Type     | Description                                                                                                                                                                           |

|--------|---------|----------|----------|---------|------------|--------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PF_6   | E7      | -        | -        | -       | <u>[5]</u> | N; PU              | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | I/O      | <b>U3_DIR</b> — RS-485/EIA-485 output enable/direction control for USART3.                                                                                                            |

|        |         |          |          |         |            |                    | I/O      | SSP1_MISO — Master In Slave Out for SSP1.                                                                                                                                             |

|        |         |          |          |         |            |                    | 0        | TRACEDATA[1] — Trace data, bit 1.                                                                                                                                                     |

|        |         |          |          |         |            |                    | I/O      | GPI07[20] — General purpose digital input/output pin.                                                                                                                                 |

|        |         |          |          |         |            |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | I/O      | <b>I2S1_TX_SDA</b> — $I^2$ S1 transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> S-bus specification. |

|        |         |          |          |         |            |                    | AI       | <b>ADC1_3</b> — ADC1 and ADC0, input channel 3. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.                                |

| PF_7   | B7      | -        | -        | -       | [5]        | N; PU              | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | I/O      | U3_BAUD — Baud pin USART3.                                                                                                                                                            |

|        |         |          |          |         |            |                    | I/O      | SSP1_MOSI — Master Out Slave in for SSP1.                                                                                                                                             |

|        |         |          |          |         |            |                    | 0        | TRACEDATA[2] — Trace data, bit 2.                                                                                                                                                     |

|        |         |          |          |         |            |                    | I/O      | GPI07[21] — General purpose digital input/output pin.                                                                                                                                 |

|        |         |          |          |         |            |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | I/O      | <b>I2S1_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification.                        |

|        |         |          |          |         |            |                    | Al/<br>O | <b>ADC1_7</b> — ADC1 and ADC0, input channel 7 or band gap output. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.             |

| PF_8   | E6      | -        | -        | -       | [5]        | N; PU              | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | I/O      | <b>U0_UCLK</b> — Serial clock input/output for USART0 in synchronous mode.                                                                                                            |

|        |         |          |          |         |            |                    | I        | CTIN_2 — SCTimer/PWM input 2. Capture input 2 of timer 0.                                                                                                                             |

|        |         |          |          |         |            |                    | 0        | TRACEDATA[3] — Trace data, bit 3.                                                                                                                                                     |

|        |         |          |          |         |            |                    | I/O      | GPI07[22] — General purpose digital input/output pin.                                                                                                                                 |

|        |         |          |          |         |            |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |            |                    | AI       | <b>ADC0_2</b> — ADC0 and ADC1, input channel 2. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.                                |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

32-bit ARM Cortex-M3 microcontroller

|                           | ,0 <u>0</u> 0, a |          | וערים    |         | are         |                    | iable | on all parts. See <u>Table 2</u> .                                                                                                                                                                                                                                                                                                                       |

|---------------------------|------------------|----------|----------|---------|-------------|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                    | LBGA256          | TFBGA180 | TFBGA100 | LQFP144 |             | Reset state<br>[1] | Type  | Description                                                                                                                                                                                                                                                                                                                                              |

| Debug pins                |                  |          |          |         |             |                    |       |                                                                                                                                                                                                                                                                                                                                                          |

| DBGEN                     | L4               | K4       | A6       | 28      | [2]         | I; PU              | I     | <ul> <li>JTAG interface control signal. Also used for boundary scan. To use the part in functional mode, connect this pin in one of the following ways:</li> <li>Leave DBGEN open. The DBGEN pin is pulled up internally by a 50 kΩ resistor.</li> <li>Tie DBGEN to VDDIO.</li> <li>Pull DBGEN up to VDDIO with an external pull-up resistor.</li> </ul> |

| TCK/SWDCLK                | J5               | G5       | H2       | 27      | [2]         | I; F               | I     | Test Clock for JTAG interface (default) or Serial Wire (SW) clock.                                                                                                                                                                                                                                                                                       |

| TRST                      | M4               | L4       | B4       | 29      | [2]         | I; PU              | I     | Test Reset for JTAG interface.                                                                                                                                                                                                                                                                                                                           |

| TMS/SWDIO                 | K6               | K5       | C4       | 30      | [2]         | I; PU              | I     | Test Mode Select for JTAG interface (default) or SW debug data input/output.                                                                                                                                                                                                                                                                             |

| TDO/SWO                   | K5               | J5       | H3       | 31      | [2]         | 0                  | 0     | Test Data Out for JTAG interface (default) or SW trace output.                                                                                                                                                                                                                                                                                           |

| TDI                       | J4               | H4       | G3       | 26      | [2]         | I; PU              | I     | Test Data In for JTAG interface.                                                                                                                                                                                                                                                                                                                         |

| USB0 pins                 |                  |          |          |         |             |                    |       |                                                                                                                                                                                                                                                                                                                                                          |

| USB0_DP                   | F2               | E2       | E1       | 18      | [6]         | -                  | I/O   | USB0 bidirectional D+ line. Do not add an external series resistor.                                                                                                                                                                                                                                                                                      |

| USB0_DM                   | G2               | F2       | E2       | 20      | [6]         | -                  | I/O   | USB0 bidirectional D- line. Do not add an external series resistor.                                                                                                                                                                                                                                                                                      |

| USB0_VBUS                 | F1               | E1       | E3       | 21      | [6]<br>[7]  | -                  | I/O   | VBUS pin (power on USB cable). This pin includes an internal pull-down resistor of 64 k $\Omega$ (typical) $\pm$ 16 k $\Omega$ .                                                                                                                                                                                                                         |

| USB0_ID                   | H2               | G2       | F1       | 22      | <u>[8]</u>  | -                  | I     | Indicates to the transceiver whether connected as an A-device (USB0_ID LOW) or B-device (USB0_ID HIGH). For use with OTG, this pin has an internal pull-up resistor.                                                                                                                                                                                     |

| USB0_RREF                 | H1               | G1       | F3       | 24      | <u>[8]</u>  | -                  |       | 12.0 k $\Omega$ (accuracy 1 %) on-board resistor to ground for current reference.                                                                                                                                                                                                                                                                        |

| USB1 pins                 |                  |          |          |         |             |                    |       |                                                                                                                                                                                                                                                                                                                                                          |

| USB1_DP                   | F12              | D11      | E9       | 89      | [9]         | -                  | I/O   | USB1 bidirectional D+ line. Add an external series resistor of 33 $\Omega$ +/- 2 %.                                                                                                                                                                                                                                                                      |

| USB1_DM                   | G12              | E11      | E10      | 90      | [9]         | -                  | I/O   | USB1 bidirectional D– line. Add an external series resistor of 33 $\Omega$ +/- 2 %.                                                                                                                                                                                                                                                                      |

| I <sup>2</sup> C-bus pins |                  |          |          |         |             |                    |       |                                                                                                                                                                                                                                                                                                                                                          |

| I2C0_SCL                  | L15              | K13      | D6       | 92      | <u>[10]</u> | I; F               | I/O   | I <sup>2</sup> C clock input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                                                                                                                                                            |

| I2C0_SDA                  | L16              | K14      | E6       | 93      | <u>[10]</u> | I; F               | I/O   | I <sup>2</sup> C data input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                                                                                                                                                             |

| Reset and wak             | e-up pi          | ins      |          | •       |             | •                  |       | •                                                                                                                                                                                                                                                                                                                                                        |

| RESET                     | D9               | C7       | B6       | 128     | [11]        | I; IA              | I     | External reset input: A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. This pin does not have an internal pull-up.                                                                                                   |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

## 32-bit ARM Cortex-M3 microcontroller

- Two AHB bus masters for transferring data. These interfaces transfer data when a DMA request goes active. Master 1 can access memories and peripherals, master 0 can access memories only.

- 32-bit AHB master bus width.

- Incrementing or non-incrementing addressing for source and destination.

- Programmable DMA burst size. The DMA burst size can be programmed to more efficiently transfer data.

- Internal four-word FIFO per channel.

- Supports 8, 16, and 32-bit wide transactions.

- Big-endian and little-endian support. The DMA Controller defaults to little-endian mode on reset.

- An interrupt to the processor can be generated on a DMA completion or when a DMA error has occurred.

- Raw interrupt status. The DMA error and DMA count raw interrupt status can be read prior to masking.

## 7.13.3 SPI Flash Interface (SPIFI)

The SPI Flash Interface allows low-cost serial flash memories to be connected to the ARM Cortex-M3 processor with little performance penalty compared to parallel flash devices with higher pin count.

After a few commands configure the interface at startup, the entire flash content is accessible as normal memory using byte, halfword, and word accesses by the processor and/or DMA channels. Simple sequences of commands handle erasing and programming.

Many serial flash devices use a half-duplex command-driven SPI protocol for device setup and initialization and then move to a half-duplex, command-driven 4-bit protocol for normal operation. Different serial flash vendors and devices accept or require different commands and command formats. SPIFI provides sufficient flexibility to be compatible with common flash devices and includes extensions to help insure compatibility with future devices.

## 7.13.3.1 Features

- Interfaces to serial flash memory in the main memory map.

- Supports classic and 4-bit bidirectional serial protocols.

- Half-duplex protocol compatible with various vendors and devices.

- Quad SPI Flash Interface (SPIFI) with 1-, 2-, or 4-bit data at rates of up to 52 MB per second.

- Supports DMA access.

## 7.13.4 SD/MMC card interface

The SD/MMC card interface supports the following modes:

- Secure Digital memory (SD version 3.0)

- Secure Digital I/O (SDIO version 2.0)

- Consumer Electronics Advanced Transport Architecture (CE-ATA version 1.1)

© NXP Semiconductors N.V. 2016. All rights reserved.

## 32-bit ARM Cortex-M3 microcontroller

• Smart card mode conforming to ISO7816 specification

## 7.14.3 SSP serial I/O controller

Remark: The LPC1850/30/20/10 contain two SSP controllers.

The SSP controller can operate on a SPI, 4-wire SSI, or Microwire bus. It can interact with multiple masters and slaves on the bus. Only a single master and a single slave can communicate on the bus during a given data transfer. The SSP supports full-duplex transfers, with frames of 4 bit to 16 bit of data flowing from the master to the slave and from the slave to the master. In practice, often only one of these data flows carries meaningful data.

## 7.14.3.1 Features

- Maximum SSP speed in full-duplex mode of 25 Mbit/s; for transmit only 50 Mbit/s (master) and 15 Mbit/s (slave).

- Compatible with Motorola SPI, 4-wire Texas Instruments SSI, and National Semiconductor Microwire buses.

- Synchronous serial communication.

- Master or slave operation.

- Eight-frame FIFOs for both transmit and receive.

- 4-bit to 16-bit frame.

- Connected to the GPDMA.

## 7.14.4 I<sup>2</sup>C-bus interface

**Remark:** The LPC1850/30/20/10 contain two I<sup>2</sup>C-bus interfaces.

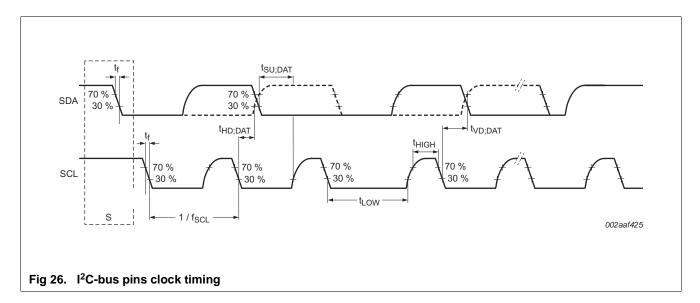

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock line (SCL) and a Serial Data line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (for example an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

## 7.14.4.1 Features

- I<sup>2</sup>C0 is a standard I<sup>2</sup>C-compliant bus interface with open-drain pins. I<sup>2</sup>C0 also supports Fast mode plus with bit rates up to 1 Mbit/s.

- I<sup>2</sup>C1 uses standard I/O pins with bit rates of up to 400 kbit/s (Fast I<sup>2</sup>C-bus).

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).