Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | ARM® Cortex®-M3                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 150MHz                                                                          |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT |

| Number of I/O              | 64                                                                              |

| Program Memory Size        | -                                                                               |

| Program Memory Type        | ROMIess                                                                         |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 136К х 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x10b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C                                                                    |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TFBGA                                                                       |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1810fet100-551       |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M3 microcontroller

### 4. Ordering information

#### Table 1.Ordering information

| Type number   | Package  |                                                                                             |          |

|---------------|----------|---------------------------------------------------------------------------------------------|----------|

|               | Name     | Description                                                                                 | Version  |

| LPC1850FET256 | LBGA256  | Plastic low profile ball grid array package; 256 balls; body $17 \times 17 \times 1$ mm     | SOT740-2 |

| LPC1850FET180 | TFBGA180 | Thin fine-pitch ball grid array package; 180 balls                                          | SOT570-3 |

| LPC1830FET256 | LBGA256  | Plastic low profile ball grid array package; 256 balls; body $17 \times 17 \times 1$ mm     | SOT740-2 |

| LPC1830FET180 | TFBGA180 | Thin fine-pitch ball grid array package; 180 balls                                          | SOT570-3 |

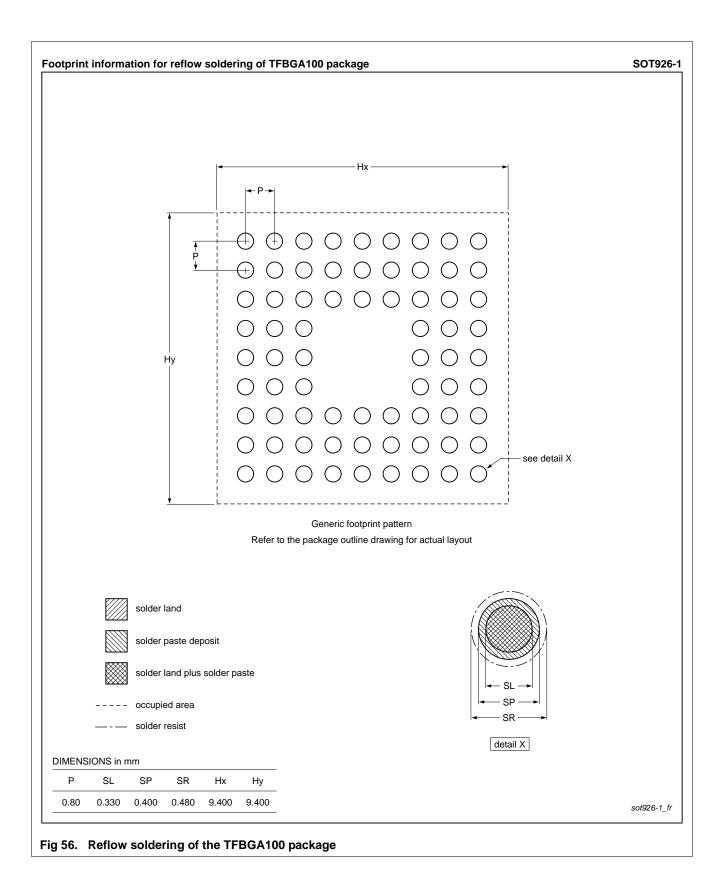

| LPC1830FET100 | TFBGA100 | Plastic thin fine-pitch ball grid array package; 100 balls; body $9 \times 9 \times 0.7$ mm | SOT926-1 |

| LPC1830FBD144 | LQFP144  | Plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm         | SOT486-1 |

| LPC1820FET100 | TFBGA100 | Plastic thin fine-pitch ball grid array package; 100 balls; body $9 \times 9 \times 0.7$ mm | SOT926-1 |

| LPC1820FBD144 | LQFP144  | Plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm         | SOT486-1 |

| LPC1810FET100 | TFBGA100 | Plastic thin fine-pitch ball grid array package; 100 balls; body $9 \times 9 \times 0.7$ mm | SOT926-1 |

| LPC1810FBD144 | LQFP144  | Plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm         | SOT486-1 |

### 4.1 Ordering options

#### Table 2. Ordering options

| Type number   | Total<br>SRAM | LCD | Ethernet | USB0<br>(Host,<br>Device,<br>OTG) | USB1<br>(Host,<br>Device)/<br>ULPI<br>interface | ADC<br>channels | Motor<br>control<br>PWM | QEI | GPIO | Package  |

|---------------|---------------|-----|----------|-----------------------------------|-------------------------------------------------|-----------------|-------------------------|-----|------|----------|

| LPC1850FET256 | 200 kB        | yes | yes      | yes                               | yes/yes                                         | 8               | yes                     | yes | 164  | LBGA256  |

| LPC1850FET180 | 200 kB        | yes | yes      | yes                               | yes/yes                                         | 8               | yes                     | yes | 118  | TFBGA180 |

| LPC1830FET256 | 200 kB        | no  | yes      | yes                               | yes/yes                                         | 8               | yes                     | yes | 164  | LBGA256  |

| LPC1830FET180 | 200 kB        | no  | yes      | yes                               | yes/yes                                         | 8               | yes                     | yes | 118  | TFBGA180 |

| LPC1830FET100 | 200 kB        | no  | yes      | yes                               | yes/no                                          | 4               | no                      | no  | 49   | TFBGA100 |

| LPC1830FBD144 | 200 kB        | no  | yes      | yes                               | yes/no                                          | 8               | yes                     | no  | 83   | LQFP144  |

| LPC1820FET100 | 168 kB        | no  | no       | yes                               | no                                              | 4               | no                      | no  | 49   | TFBGA100 |

| LPC1820FBD144 | 168 kB        | no  | no       | yes                               | no                                              | 8               | yes                     | no  | 83   | LQFP144  |

| LPC1810FET100 | 136 kB        | no  | no       | no                                | no                                              | 4               | no                      | no  | 49   | TFBGA100 |

| LPC1810FBD144 | 136 kB        | no  | no       | no                                | no                                              | 8               | yes                     | no  | 83   | LQFP144  |

32-bit ARM Cortex-M3 microcontroller

|        | , USB0, a | and US   | SB1 fur  | nctions | are |             | ilable | on all parts. See <u>Table 2</u> .                          |

|--------|-----------|----------|----------|---------|-----|-------------|--------|-------------------------------------------------------------|

| Symbol | LBGA256   | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type   | Description                                                 |

| P1_12  | R9        | P7       | K7       | 56      | [2] | N; PU       | I/O    | GPIO1[5] — General purpose digital input/output pin.        |

|        |           |          |          |         |     |             | I      | <b>U1_DCD</b> — Data Carrier Detect input for UART1.        |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | I/O    | <b>EMC_D5</b> — External memory data line 5.                |

|        |           |          |          |         |     |             | I      | <b>T0_CAP1</b> — Capture input 1 of timer 0.                |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | I/O    | <b>SD_DAT3</b> — SD/MMC data bus line 3.                    |

| P1_13  | R10       | L8       | H8       | 60      | [2] | N; PU       | I/O    | <b>GPIO1[6]</b> — General purpose digital input/output pin. |

|        |           |          |          |         |     |             | 0      | <b>U1_TXD</b> — Transmitter output for UART1.               |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | I/O    | EMC_D6 — External memory data line 6.                       |

|        |           |          |          |         |     |             | I      | <b>T0_CAP0</b> — Capture input 0 of timer 0.                |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | I      | <b>SD_CD</b> — SD/MMC card detect input.                    |

| P1_14  | R11       | K7       | J8       | 61      | [2] | N; PU       | I/O    | GPIO1[7] — General purpose digital input/output pin.        |

|        |           |          |          |         |     |             | I      | U1_RXD — Receiver input for UART1.                          |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | I/O    | EMC_D7 — External memory data line 7.                       |

|        |           |          |          |         |     |             | 0      | T0_MAT2 — Match output 2 of timer 0.                        |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

| P1_15  | T12       | P11      | K8       | 62      | [2] | N; PU       | I/O    | GPIO0[2] — General purpose digital input/output pin.        |

|        |           |          |          |         |     |             | 0      | U2_TXD — Transmitter output for USART2.                     |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | I      | ENET_RXD0 — Ethernet receive data 0 (RMII/MII interface).   |

|        |           |          |          |         |     |             | 0      | T0_MAT1 — Match output 1 of timer 0.                        |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

|        |           |          |          |         |     |             | -      | R — Function reserved.                                      |

#### Table 3. Pin description ... continued

Jahla ~*II •* Saa Tahla 2

32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                                                                        |

|--------|---------|----------|----------|---------|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1_20  | M10     | J10      | K10      | 70      | [2] | N; PU              | I/O  | GPIO0[15] — General purpose digital input/output pin.                                                                                                                                              |

|        |         |          |          |         |     |                    | I/O  | SSP1_SSEL — Slave Select for SSP1.                                                                                                                                                                 |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | 0    | <b>ENET_TXD1</b> — Ethernet transmit data 1 (RMII/MII interface).                                                                                                                                  |

|        |         |          |          |         |     |                    | I    | T0_CAP2 — Capture input 2 of timer 0.                                                                                                                                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

| P2_0   | T16     | N14      | G10      | 75      | [2] | N; PU              | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | 0    | U0_TXD — Transmitter output for USART0.                                                                                                                                                            |

|        |         |          |          |         |     |                    | I/O  | EMC_A13 — External memory address line 13.                                                                                                                                                         |

|        |         |          |          |         |     |                    | 0    | <b>USB0_PPWR</b> — VBUS drive signal (towards external charge pump or power management unit); indicates that VBUS must be driven (active high).                                                    |

|        |         |          |          |         |     |                    |      | Add a pull-down resistor to disable the power switch at reset.<br>This signal has opposite polarity compared to the USB_PPWR<br>used on other NXP LPC parts.                                       |

|        |         |          |          |         |     |                    | I/O  | GPIO5[0] — General purpose digital input/output pin.                                                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | I    | T3_CAP0 — Capture input 0 of timer 3.                                                                                                                                                              |

|        |         |          |          |         |     |                    | 0    | ENET_MDC — Ethernet MIIM clock.                                                                                                                                                                    |

| P2_1   | N15     | M13      | G7       | 81      | [2] | N; PU              | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | I    | U0_RXD — Receiver input for USART0.                                                                                                                                                                |

|        |         |          |          |         |     |                    | I/O  | EMC_A12 — External memory address line 12.                                                                                                                                                         |

|        |         |          |          |         |     |                    | I    | <b>USB0_PWR_FAULT</b> — Port power fault signal indicating overcurrent condition; this signal monitors over-current on the USB bus (external circuitry required to detect over-current condition). |

|        |         |          |          |         |     |                    | I/O  | GPIO5[1] — General purpose digital input/output pin.                                                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |         |     |                    | I    | T3_CAP1 — Capture input 1 of timer 3.                                                                                                                                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                                             |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                         |

|--------|---------|----------|----------|---------|-----|--------------------|------|---------------------------------------------------------------------|

| PD_16  | R14     | P12      | -        | -       | [2] | N; PU              | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | I/O  | EMC_A16 — External memory address line 16.                          |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | I/O  | GPIO6[30] — General purpose digital input/output pin.               |

|        |         |          |          |         |     |                    | 0    | <b>SD_VOLT2</b> — SD/MMC bus voltage select output 2.               |

|        |         |          |          |         |     |                    | 0    | <b>CTOUT_12</b> — SCTimer/PWM output 12. Match output 3 of timer 3. |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

| PE_0   | P14     | N12      | -        | -       | [2] | N; PU              | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | I/O  | EMC_A18 — External memory address line 18.                          |

|        |         |          |          |         |     |                    | I/O  | GPI07[0] — General purpose digital input/output pin.                |

|        |         |          |          |         |     |                    | 0    | CAN1_TD — CAN1 transmitter output.                                  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

| PE_1   | N14     | M12      | -        | -       | [2] | N; PU              | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | I/O  | <b>EMC_A19</b> — External memory address line 19.                   |

|        |         |          |          |         |     |                    | I/O  | <b>GPIO7[1]</b> — General purpose digital input/output pin.         |

|        |         |          |          |         |     |                    | I    | CAN1_RD — CAN1 receiver input.                                      |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

| PE_2   | M14     | L12      | -        | -       | [2] | N; PU              | I    | ADCTRIG0 — ADC trigger input 0.                                     |

|        |         |          |          |         |     |                    | I    | CAN0_RD — CAN receiver input.                                       |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | I/O  | EMC_A20 — External memory address line 20.                          |

|        |         |          |          |         |     |                    | I/O  | <b>GPI07[2]</b> — General purpose digital input/output pin.         |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                              |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                          |

|--------|---------|----------|----------|---------|-----|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| PE_7   | F15     | -        | -        | -       | [2] | N; PU              | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | 0    | <b>CTOUT_5</b> — SCTimer/PWM output 5. Match output 3 of timer 3.                                                                    |

|        |         |          |          |         |     |                    | I    | U1_CTS — Clear to Send input for UART1.                                                                                              |

|        |         |          |          |         |     |                    | I/O  | EMC_D26 — External memory data line 26.                                                                                              |

|        |         |          |          |         |     |                    | I/O  | GPI07[7] — General purpose digital input/output pin.                                                                                 |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

| PE_8   | F14     | -        | -        | -       | [2] | N; PU              | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | 0    | <b>CTOUT_4</b> — SCTimer/PWM output 4. Match output 3 of timer 3.                                                                    |

|        |         |          |          |         |     |                    | I    | U1_DSR — Data Set Ready input for UART1.                                                                                             |

|        |         |          |          |         |     |                    | I/O  | EMC_D27 — External memory data line 27.                                                                                              |

|        |         |          |          |         |     |                    | I/O  | GPI07[8] — General purpose digital input/output pin.                                                                                 |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

| PE_9   | E16     | -        | -        | -       | [2] | N; PU              | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | I    | CTIN_4 — SCTimer/PWM input 4. Capture input 2 of timer 1.                                                                            |

|        |         |          |          |         |     |                    | I    | U1_DCD — Data Carrier Detect input for UART1.                                                                                        |

|        |         |          |          |         |     |                    | I/O  | EMC_D28 — External memory data line 28.                                                                                              |

|        |         |          |          |         |     |                    | I/O  | GPI07[9] — General purpose digital input/output pin.                                                                                 |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

| PE_10  | E14     | -        | -        | -       | [2] | N; PU              | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | I    | CTIN_3 — SCTimer/PWM input 3. Capture input 1 of timer 1.                                                                            |

|        |         |          |          |         |     |                    | 0    | <b>U1_DTR</b> — Data Terminal Ready output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1. |

|        |         |          |          |         |     |                    | I/O  | EMC_D29 — External memory data line 29.                                                                                              |

|        |         |          |          |         |     |                    | I/O  | GPI07[10] — General purpose digital input/output pin.                                                                                |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                               |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

© NXP Semiconductors N.V. 2016. All rights reserved.

#### 32-bit ARM Cortex-M3 microcontroller

#### Symbol Description state **FBGA180** FBGA100 -BGA256 **.QFP144** Reset : [1] Type Power and ground pins USB0 VDDA F3 F3 D1 16 Separate analog 3.3 V power supply for driver. 3V3 DRIVER USB0 G3 F3 USB 3.3 V separate power supply voltage. D2 17 \_ \_VDDA3V3 USB0 VSSA H3 D3 Dedicated analog ground for clean reference for termination G3 19 TERM resistors. USB0 VSSA G1 F1 F2 23 Dedicated clean analog ground for generation of reference REF currents and voltages. VDDA B4 A6 B2 137 Analog power supply and ADC reference voltage. VBAT B10 Β9 C5 RTC power supply: 3.3 V on this pin supplies power to the 127 RTC. Main regulator power supply. Tie the VDDREG and VDDIO VDDREG F10, D8, E4, 94, F9, E8 E5, 131, pins to a common power supply to ensure the same ramp-up L8, F4 59, time for both supply voltages. L7 25 VPP [12] E8 OTP programming voltage. [12] I/O power supply. Tie the VDDREG and VDDIO pins to a VDDIO D7. H5. F10. 5, E12. H10. K5 common power supply to ensure the same ramp-up time for 36 F7, K8. 41. both supply voltages. F8. 71, G10 G10. 77. H10. 107. J6, 111. J7, 141 K7, L9, L10, N7, N13 [13] VSS G9. F10, C8, Ground. H7, D7, D4, J10, E6, D5, J11, E7, G8, K8 E9, J3, K6, J6 K9

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

LPC1850\_30\_20\_10

#### 32-bit ARM Cortex-M3 microcontroller

- Clock selection

- Inputs

- Events

- Outputs

- Interrupts

#### 7.13.1.1 Features

- Two 16-bit counters or one 32-bit counter.

- Counters clocked by bus clock or selected input.

- Counters can be configured as up counters or up-down counters.

- State variable allows sequencing across multiple counter cycles.

- Event combines input or output condition and/or counter match in a specified state.

- Events control outputs and interrupts.

- Selected events can limit, halt, start, or stop a counter.

- Supports:

- up to 8 inputs

- up to 16 outputs

- 16 match/capture registers

- 16 events

- 32 states

#### 7.13.2 General-purpose DMA

The DMA controller allows peripheral-to memory, memory-to-peripheral, peripheral-to-peripheral, and memory-to-memory transactions. Each DMA stream provides unidirectional serial DMA transfers for a single source and destination. For example, a bidirectional port requires one stream for transmit and one for receives. The source and destination areas can each be either a memory region or a peripheral for master 1, but only memory for master 0.

#### 7.13.2.1 Features

- Eight DMA channels. Each channel can support a unidirectional transfer.

- 16 DMA request lines.

- Single DMA and burst DMA request signals. Each peripheral connected to the DMA Controller can assert either a burst DMA request or a single DMA request. The DMA burst size is set by programming the DMA Controller.

- Memory-to-memory, memory-to-peripheral, peripheral-to-memory, and peripheral-to-peripheral transfers are supported.

- Scatter or gather DMA is supported through the use of linked lists. This means that the source and destination areas do not have to occupy contiguous areas of memory.

- Hardware DMA channel priority.

- AHB slave DMA programming interface. The DMA Controller is programmed by writing to the DMA control registers over the AHB slave interface.

#### 32-bit ARM Cortex-M3 microcontroller

#### 7.18.3 Clock Generation Unit (CGU)

The Clock Generator Unit (CGU) generates several base clocks. The base clocks can be unrelated in frequency and phase and can have different clock sources within the CGU. One CGU base clock is routed to the CLKOUT pins. The base clock that generates the CPU clock is referred to as CCLK.

Multiple branch clocks are derived from each base clock. The branch clocks offer flexible control for power-management purposes. All branch clocks are outputs of one of two Clock Control Units (CCUs) and can be controlled independently. Branch clocks derived from the same base clock are synchronous in frequency and phase.

#### 7.18.4 Internal RC oscillator (IRC)

The IRC is used as the clock source for the WWDT and/or as the clock that drives the PLLs and the CPU. The nominal IRC frequency is 12 MHz. The IRC is trimmed to 1.5 % accuracy over the entire voltage and temperature range.

Upon power-up or any chip reset, the LPC1850/30/20/10 use the IRC as the clock source. The boot loader then configures the PLL1 to provide a 96 MHz clock for the core and the PLL0USB or PLL0AUDIO as needed if an external boot source is selected.

#### 7.18.5 PLL0USB (for USB0)

PLL0 is a dedicated PLL for the USB0 High-speed controller.

PLL0 accepts an input clock frequency from an external oscillator in the range of 14 kHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The CCO operates in the range of 4.3 MHz to 550 MHz.

#### 7.18.6 PLL0AUDIO (for audio)

The audio PLL PLL0AUDIO is a general-purpose PLL with a small step size. This PLL accepts an input clock frequency derived from an external oscillator or internal IRC. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). A sigma-delta converter modulates the PLL divider ratios to obtain the desired output frequency. The output frequency can be set as a multiple of the sampling frequency  $f_s$  to  $32 \times f_s$ ,  $64 \times f_s$ ,  $128 \times f_s$ ,  $256 \times f_s$ ,  $384 \times f_s$ ,  $512 \times f_s$  and the sampling frequency  $f_s$  can range from 16 kHz to 192 kHz (16, 22.05, 32, 44.1, 48, 96,192) kHz. Many other frequencies are possible as well using the integrated fractional divider.

#### 7.18.7 System PLL1

The PLL1 accepts an input clock frequency from an external oscillator in the range of 1 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The multiplier can be an integer value from 1 to 32. The CCO operates in the range of 156 MHz to 320 MHz. This range is possible through an additional divider in the loop to keep the CCO within its frequency range while the PLL is providing the desired output frequency. The output divider can be set to divide by 2, 4, 8, or 16 to produce the output clock. Since the minimum output divider value is 2, it is insured that the PLL output has a 50 % duty cycle. The PLL is turned off and bypassed following a chip reset. After reset, software can enable the PLL. The program must configure and activate the PLL, wait for the PLL to lock, and then connect to the PLL as a clock source. The PLL settling time is 100  $\mu$ s.

#### **NXP Semiconductors**

# LPC1850/30/20/10

#### 32-bit ARM Cortex-M3 microcontroller

- [5] PLL1 disabled; IRC running; CCLK = 12 MHz.

- [6] V<sub>BAT</sub> = 3.6 V.

- [7]  $V_{DD(IO)} = V_{DDA} = 3.6$  V; over entire frequency range CCLK = 12 MHz to 180 MHz.

- [8]  $V_{DD(REG)(3V3)} = 3.3 \text{ V}; V_{DD(IO)} = 3.3 \text{ V}.$  Input leakage increases when  $V_{DD(IO)}$  is floating or grounded. It is recommended to keep  $V_{DD(REG)(3V3)}$  and  $V_{DD(IO)}$  powered in deep power-down mode.

- [9] On pin VBAT;  $T_{amb} = 25 \ ^{\circ}C$ .

- [10] V<sub>ps</sub> corresponds to the output of the power switch (see Figure 9) which is determined by the greater of V<sub>BAT</sub> and V<sub>DD(Reg)(3V3)</sub>.

- [11]  $V_{DDA(3V3)} = 3.3 \text{ V}; T_{amb} = 25 \text{ °C}.$

- [12] Allowed as long as the current limit does not exceed the maximum current allowed by the device.

- [13] To  $V_{\text{SS}}.$

- [14] The values specified are simulated and absolute values.

- [15] The weak pull-up resistor is connected to the  $V_{DD(IO)}$  rail and pulls up the I/O pin to the  $V_{DD(IO)}$  level.

- [16] The input cell disables the weak pull-up resistor when the applied input voltage exceeds  $V_{DD(IO)}$ .

- [17] The parameter value specified is a simulated value excluding bond capacitance.

- [18] For USB operation 3.0 V  $\leq$  V\_{DD((IO)}  $\leq$  3.6 V. Guaranteed by design.

- [19] V<sub>DD(IO)</sub> present.

- [20] Includes external resistors of 33  $\Omega\pm$  1 % on D+ and D–.

32-bit ARM Cortex-M3 microcontroller

### **11. Dynamic characteristics**

#### 11.1 Wake-up times

### Table 13. Dynamic characteristic: Wake-up from Deep-sleep, Power-down, and Deep power-down modes

$T_{amb} = -40 \ ^{\circ}\text{C} \text{ to } +85 \ ^{\circ}\text{C}$

| Symbol            | Parameter    | Conditions                             |     | Min                    | Typ <u>[1]</u>        | Max | Unit |

|-------------------|--------------|----------------------------------------|-----|------------------------|-----------------------|-----|------|

| t <sub>wake</sub> | wake-up time | from Sleep mode                        | [2] | $3 \times T_{cy(clk)}$ | $5 	imes T_{cy(clk)}$ | -   | ns   |

|                   |              | from Deep-sleep and<br>Power-down mode |     | 12                     | 51                    | -   | μs   |

|                   |              | from Deep power-down mode              |     | -                      | 250                   | -   | μs   |

|                   |              | after reset                            |     | -                      | 250                   | -   | μS   |

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2]  $T_{cy(clk)} = 1/CCLK$  with CCLK = CPU clock frequency.

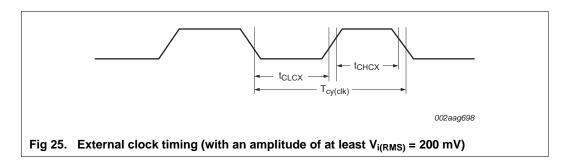

### 11.2 External clock for oscillator in slave mode

**Remark:** The input voltage on the XTAL1/2 pins must be  $\leq 1.2$  V (see <u>Table 10</u>). For connecting the oscillator to the XTAL pins, also see <u>Section 13.2</u> and <u>Section 13.4</u>.

#### Table 14. Dynamic characteristic: external clock

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; V_{DD(IO)} \text{ over specified ranges}.$

| Symbol               | Parameter            | Min                             | Max                      | Unit |

|----------------------|----------------------|---------------------------------|--------------------------|------|

| f <sub>osc</sub>     | oscillator frequency | 1                               | 25                       | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time     | 40                              | 1000                     | ns   |

| t <sub>CHCX</sub>    | clock HIGH time      | $T_{\text{cy(clk)}} \times 0.4$ | $T_{cy(clk)} \times 0.6$ | ns   |

| t <sub>CLCX</sub>    | clock LOW time       | $T_{cy(clk)} 	imes 0.4$         | $T_{cy(clk)} \times 0.6$ | ns   |

[1] Parameters are valid over operating temperature range unless otherwise specified.

#### 32-bit ARM Cortex-M3 microcontroller

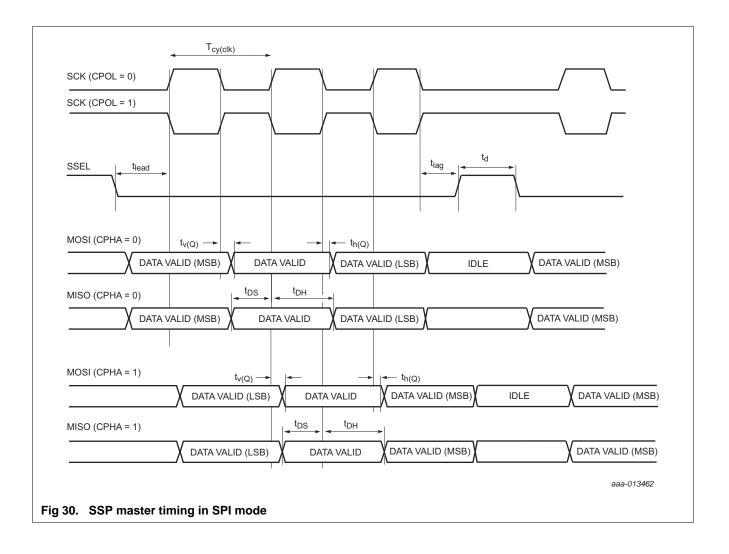

#### Table 23. Dynamic characteristics: SSP pins in SPI mode

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; 2.2 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V}; 2.7 \text{ V} \le V_{DD(IO)} \le 3.6 \text{ V}; C_L = 20 \text{ pF. Sampled at } 10 \text{ \% and } 90 \text{ \% of the signal level; EHS} = 1 \text{ for all pins. Simulated values.}$

| Symbol           | Parameter  | Conditions                        | Min                             | Тур                            | Max | Unit |

|------------------|------------|-----------------------------------|---------------------------------|--------------------------------|-----|------|

| t <sub>lag</sub> | lag time   | continuous transfer mode          | $0.5T_{cy(clk)} + 0.2$          | -                              | -   | ns   |

|                  |            | SPI mode; CPOL = 0;<br>CPHA = 0   |                                 |                                |     |      |

|                  |            | SPI mode; CPOL = 0;<br>CPHA = 1   | $T_{cy(clk)}$ + 0.2             | -                              | -   | ns   |

|                  |            | SPI mode; CPOL = 1;<br>CPHA = 0   | $0.5 	imes T_{cy(clk)} + 0.2$   | -                              | -   | ns   |

|                  |            | SPI mode; CPOL = 1;<br>CPHA = 1   | $T_{cy(clk)} + 0.2$             | -                              | -   | ns   |

|                  |            | synchronous serial frame mode     | $T_{cy(clk)} + 0.2$             | -                              | -   | ns   |

|                  |            | microwire frame format            | format $0.5 \times T_{cy(clk)}$ | ns                             |     |      |

| t <sub>d</sub>   | delay time | continuous transfer mode          | -                               | $0.5\times T_{\text{cy(clk)}}$ | -   | ns   |

|                  |            | SPI mode; CPOL = 0;<br>CPHA = $0$ |                                 |                                |     |      |

|                  |            | SPI mode; CPOL = 0;<br>CPHA = 1   | -                               | n/a                            | -   | ns   |

|                  |            | SPI mode; CPOL = 1;<br>CPHA = 0   | -                               | $0.5 \times T_{cy(clk)}$       | -   | ns   |

|                  |            | SPI mode; CPOL = 1;<br>CPHA = 1   | -                               | n/a                            | -   | ns   |

|                  |            | synchronous serial frame mode     | -                               | T <sub>cy(clk)</sub>           | -   | ns   |

|                  |            | microwire frame format            | -                               | n/a                            | -   | ns   |

[1]  $T_{cy(clk)} = (SSPCLKDIV \times (1 + SCR) \times CPSDVSR) / f_{main}$ . The clock cycle time derived from the SPI bit rate  $T_{cy(clk)}$  is a function of the main clock frequency  $f_{main}$ , the SSP peripheral clock divider (SSPCLKDIV), the SSP SCR parameter (specified in the SSP0CR0 register), and the SSP CPSDVSR parameter (specified in the SSP clock prescale register).

32-bit ARM Cortex-M3 microcontroller

#### 32-bit ARM Cortex-M3 microcontroller

| Symbol                | Parameter                     | Conditions                     |     | Min | Тур | Max      | Unit |

|-----------------------|-------------------------------|--------------------------------|-----|-----|-----|----------|------|

| High-spe              | ed mode                       |                                |     |     |     |          |      |

| P <sub>cons</sub>     | power consumption             |                                | [2] | -   | 68  | -        | mW   |

| I <sub>DDA(3V3)</sub> | analog supply current (3.3 V) | on pin USB0_VDDA3V3_DRIVER;    | [3] |     |     |          |      |

|                       |                               | total supply current           |     | -   | 18  | -        | mA   |

|                       |                               | during transmit                |     | -   | 31  | -        | mA   |

|                       |                               | during receive                 |     | -   | 14  | -        | mA   |

|                       |                               | with driver tri-stated         |     | -   | 14  | -        | mA   |

| IDDD                  | digital supply current        |                                |     | -   | 7   | -        | mA   |

| Full-spee             | ed/low-speed mode             |                                | Į   |     | -   | <b>I</b> | -    |

| P <sub>cons</sub>     | power consumption             |                                | [2] | -   | 15  | -        | mW   |

| DDA(3V3)              | analog supply current (3.3 V) | on pin USB0_VDDA3V3_DRIVER;    |     |     |     |          |      |

|                       |                               | total supply current           |     | -   | 3.5 | -        | mA   |

|                       |                               | during transmit                |     | -   | 5   | -        | mA   |

|                       |                               | during receive                 |     | -   | 3   | -        | mA   |

|                       |                               | with driver tri-stated         |     | -   | 3   | -        | mA   |

| I <sub>DDD</sub>      | digital supply current        |                                |     | -   | 3   | -        | mA   |

| Suspend               | mode                          |                                |     |     | 1   |          | 1    |

| I <sub>DDA(3V3)</sub> | analog supply current (3.3 V) |                                |     | -   | 24  | -        | μA   |

|                       |                               | with driver tri-stated         |     | -   | 24  | -        | μA   |

|                       |                               | with OTG functionality enabled |     | -   | 3   | -        | mA   |

| I <sub>DDD</sub>      | digital supply current        |                                |     | -   | 30  | -        | μA   |

| VBUS de               | tector outputs                |                                | L   |     |     | - I-     |      |

| V <sub>th</sub>       | threshold voltage             | for VBUS valid                 |     | 4.4 | -   | -        | V    |

|                       |                               | for session end                |     | 0.2 | -   | 0.8      | V    |

|                       |                               | for A valid                    |     | 0.8 | -   | 2        | V    |

|                       |                               | for B valid                    |     | 2   | -   | 4        | V    |

| V <sub>hys</sub>      | hysteresis voltage            | for session end                |     | -   | 150 | 10       | mV   |

|                       |                               | A valid                        |     | -   | 200 | 10       | mV   |

|                       |                               | B valid                        |     | -   | 200 | 10       | mV   |

#### Table 28. Static characteristics: USB0 PHY pins<sup>[1]</sup>

[1] Characterized but not implemented as production test.

[2] Total average power consumption.

[3] The driver is active only 20 % of the time.

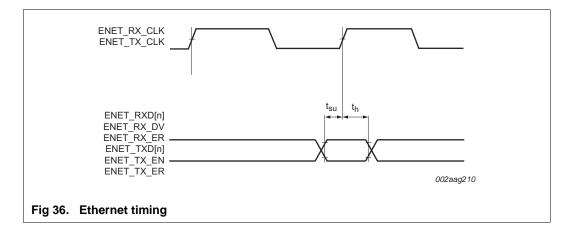

#### 11.14 Ethernet

**Remark:** The timing characteristics of the ENET\_MDC and ENET\_MDIO signals comply with the *IEEE standard 802.3*.

LPC1850\_30\_20\_10

#### 32-bit ARM Cortex-M3 microcontroller

#### Table 29. Dynamic characteristics: Ethernet

$T_{amb} = -40 \ ^{\circ}C$  to 85  $\ ^{\circ}C$ ; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6 \ V$ ; 2.7 V  $\leq V_{DD(IO)} \leq 3.6 \ V$ . Values guaranteed by design.

| Symbol                | Parameter        | Conditions                                                         |            | Min | Max      | Unit |

|-----------------------|------------------|--------------------------------------------------------------------|------------|-----|----------|------|

| RMII mo               | de               |                                                                    | I          |     | <b>I</b> |      |

| f <sub>clk</sub>      | clock frequency  | for ENET_RX_CLK                                                    | <u>[1]</u> | -   | 50       | MHz  |

| $\delta_{\text{clk}}$ | clock duty cycle |                                                                    | <u>[1]</u> | 50  | 50       | %    |

| t <sub>su</sub>       | set-up time      | for ENET_TXDn, ENET_TX_EN,<br>ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV | [1][2]     | 4   | -        | ns   |

| t <sub>h</sub>        | hold time        | for ENET_TXDn, ENET_TX_EN,<br>ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV | [1][2]     | 2   | -        | ns   |

| MII mode              | 9                |                                                                    |            |     |          |      |

| f <sub>clk</sub>      | clock frequency  | for ENET_TX_CLK                                                    | <u>[1]</u> | -   | 25       | MHz  |

| $\delta_{\text{clk}}$ | clock duty cycle |                                                                    | <u>[1]</u> | 50  | 50       | %    |

| t <sub>su</sub>       | set-up time      | for ENET_TXDn, ENET_TX_EN,<br>ENET_TX_ER                           | [1][2]     | 4   | -        | ns   |

| t <sub>h</sub>        | hold time        | for ENET_TXDn, ENET_TX_EN,<br>ENET_TX_ER                           | [1][2]     | 2   | -        | ns   |

| f <sub>clk</sub>      | clock frequency  | for ENET_RX_CLK                                                    | [1]        | -   | 25       | MHz  |

| $\delta_{\text{clk}}$ | clock duty cycle |                                                                    | [1]        | 50  | 50       | %    |

| t <sub>su</sub>       | set-up time      | for ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV                           | [1][2]     | 4   | -        | ns   |

| t <sub>h</sub>        | hold time        | for ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV                           | [1][2]     | 2   | -        | ns   |

[1] Output drivers can drive a load ≥ 25 pF accommodating over 12 inch of PCB trace and the input capacitance of the receiving device.

[2] Timing values are given from the point at which the clock signal waveform crosses 1.4 V to the valid input or output level.

LPC1850\_30\_20\_10

### **NXP Semiconductors**

### LPC1850/30/20/10

32-bit ARM Cortex-M3 microcontroller

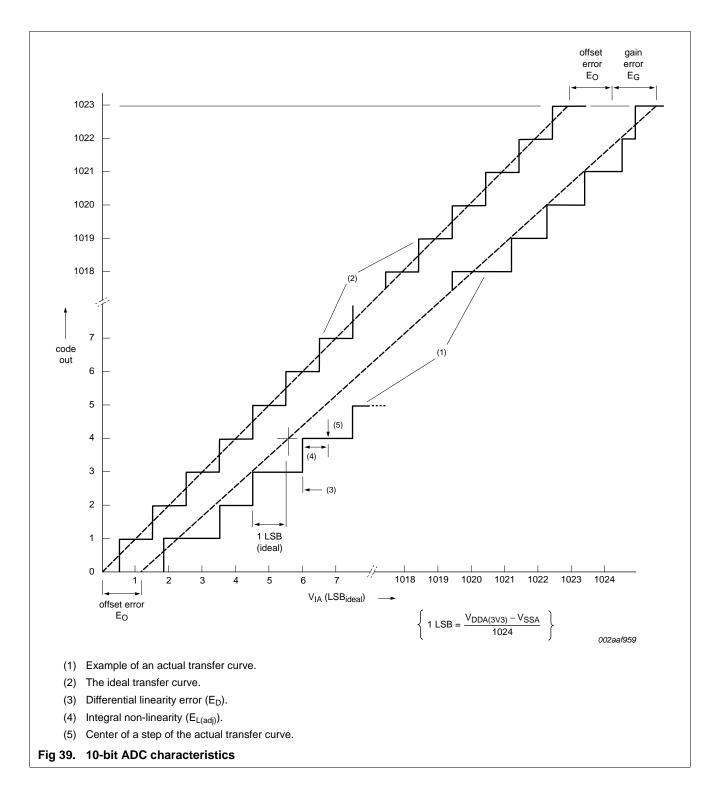

#### 32-bit ARM Cortex-M3 microcontroller

#### Table 34. DAC characteristics

$V_{DDA(3V3)}$  over specified ranges;  $T_{amb} = -40$  °C to +85 °C; unless otherwise specified

| Symbol              | Parameter                    | Conditions                                                              |     | Min | Тур  | Max | Unit |

|---------------------|------------------------------|-------------------------------------------------------------------------|-----|-----|------|-----|------|

| E <sub>D</sub>      | differential linearity error | $2.7~\text{V} \leq \text{V}_{\text{DDA}(3\text{V3})} \leq 3.6~\text{V}$ | [1] | -   | ±0.8 | -   | LSB  |

|                     |                              | $2.2 \text{ V} \le \text{V}_{\text{DDA}(3\text{V}3)}$ < 2.7 V           |     | -   | ±1.0 | -   | LSB  |

| E <sub>L(adj)</sub> | integral non-linearity       | code = 0 to 975                                                         | [1] | -   | ±1.0 | -   | LSB  |

|                     |                              | $2.7~\text{V} \leq \text{V}_{\text{DDA}(3\text{V3})} \leq 3.6~\text{V}$ |     |     |      |     |      |

|                     |                              | $2.2 \text{ V} \le \text{V}_{\text{DDA}(3\text{V3})} < 2.7 \text{ V}$   |     | -   | ±1.5 | -   | LSB  |

| Eo                  | offset error                 | $2.7~\text{V} \leq \text{V}_{\text{DDA}(3\text{V3})} \leq 3.6~\text{V}$ | [1] | -   | ±0.8 | -   | LSB  |

|                     |                              | $2.2 \text{ V} \le \text{V}_{\text{DDA}(3\text{V}3)}$ < 2.7 V           |     | -   | ±1.0 | -   | LSB  |

| E <sub>G</sub>      | gain error                   | $2.7~\text{V} \leq \text{V}_{\text{DDA}(3\text{V3})} \leq 3.6~\text{V}$ | [1] | -   | ±0.3 | -   | %    |

|                     |                              | $2.2 \text{ V} \le \text{V}_{\text{DDA}(3\text{V}3)}$ < 2.7 V           |     | -   | ±1.0 | -   | %    |

| CL                  | load capacitance             |                                                                         |     | -   | -    | 200 | pF   |

| R <sub>L</sub>      | load resistance              |                                                                         |     | 1   | -    | -   | kΩ   |

| t <sub>s</sub>      | settling time                |                                                                         | [1] |     | 0.4  |     | μσ   |

[1] In the DAC CR register, bit BIAS = 0 (see the *LPC18xx user manual*).

[2] Settling time is calculated within 1/2 LSB of the final value.

32-bit ARM Cortex-M3 microcontroller

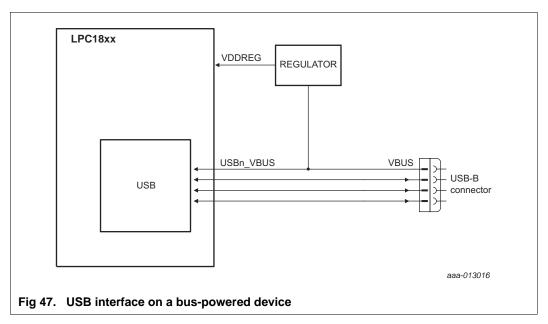

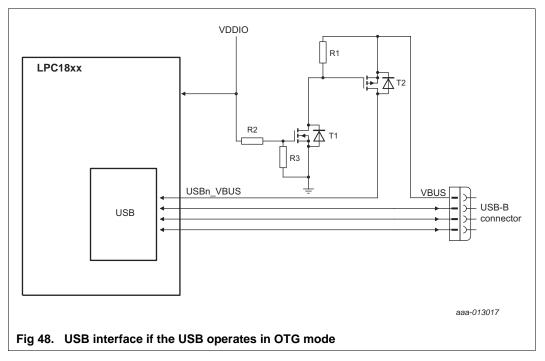

**Remark:** If the VBUS function of the USB1 interface is not connected, configure the pin function for GPIO using the function control bits in the SYSCON block.

**Remark:** In OTG mode, it is important to be able to detect the VBUS level and to charge and discharge VBUS. This requires adding active devices that disconnect the link when VDDIO is not present.

#### **NXP Semiconductors**

## LPC1850/30/20/10

32-bit ARM Cortex-M3 microcontroller

#### 32-bit ARM Cortex-M3 microcontroller

Table 40. Abbreviations ... continued

| Acronym | Description                                             |

|---------|---------------------------------------------------------|

| USART   | Universal Synchronous Asynchronous Receiver/Transmitter |

| USB     | Universal Serial Bus                                    |

| UTMI    | USB 2.0 Transceiver Macrocell Interface                 |

### 17. References

- [1] LPC18xx User manual UM10430: http://www.nxp.com/documents/user\_manual/UM10430.pdf

- [2] LPC18X0 Errata sheet: http://www.nxp.com/documents/errata\_sheet/ES\_LPC18X0.pdf

32-bit ARM Cortex-M3 microcontroller

### 18. Revision history

#### Table 41. Revision history

| Document ID            | Release date                                                                                                                                                           | Data sheet status                                                                                                                                                                                                                                                        | Change notice | Supersedes             |  |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------|--|--|--|--|

| LPC1850_30_20_10 v.6.7 | 20160314                                                                                                                                                               | Product data sheet                                                                                                                                                                                                                                                       | -             | LPC1850_30_20_10 v.6.6 |  |  |  |  |

|                        |                                                                                                                                                                        | <ul> <li>Updated Table 25 "Dynamic characteristics: Dynamic external memory interface":<br/>Read cycle parameters t<sub>h(D)</sub> min value is 2.2 ns and max value is "-".</li> </ul>                                                                                  |               |                        |  |  |  |  |

| LPC1850_30_20_10 v.6.6 | 20151116                                                                                                                                                               | Product data sheet                                                                                                                                                                                                                                                       | 2015110031    | LPC1850_30_20_10 v.6.5 |  |  |  |  |

| Modifications:         | Updated SSP slave and SSP master values in Table 23 "Dynamic characteristics: SSP pins in SPI mode". Updated footnote 2 to: $T_{cy(clk)} \ge 12 \times T_{cy(PCLK)}$ . |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | <ul> <li>removed t<sub>v(Q)</sub>, data output valid time in SPI mode, minimum value of 3 ´ (1/PCLK) from SSP slave mode.</li> </ul>                                   |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | <ul> <li>added units to t<sub>d</sub>, delay time, for SSP slave and master mode.</li> </ul>                                                                           |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | Added GPCLKIN section and table. See Section 11.6 "GPCLKIN" and Table 18 "Dynamic characteristic: GPCLKIN".                                                            |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

| LPC1850_30_20_10 v.6.5 | 20150430                                                                                                                                                               | Product data sheet                                                                                                                                                                                                                                                       | -             | LPC1850_30_20_10 v.6.4 |  |  |  |  |

| Modifications:         | 3 "Pin des                                                                                                                                                             | • For WAKEUP pin description: Changed external pull-up to internal pull-up. See Table 3 "Pin description".                                                                                                                                                               |               |                        |  |  |  |  |

|                        | Table note 2 corrected in Table 10.                                                                                                                                    |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | Updated USART dynamic characteristics table. See Table 22.                                                                                                             |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | Added SSP slave timing data. See Table 22.                                                                                                                             |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | Added USART timing diagram. See Figure 29.                                                                                                                             |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | <ul> <li>Updated SD/MMC dynamic characteristics table. See Table 30.</li> </ul>                                                                                        |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | <ul> <li>Updated S</li> </ul>                                                                                                                                          | <ul> <li>Updated SPIFI dynamic characteristics table. See Table 32.</li> <li>Updated Dynamic characteristics: USB0 and USB1 pins (full-speed). See Table 27.</li> <li>Updated Table 2: Motor control PWM instead of PWM.</li> <li>Added a remark to Table 27.</li> </ul> |               |                        |  |  |  |  |

|                        | <ul> <li>Updated E</li> </ul>                                                                                                                                          |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | <ul> <li>Updated T</li> </ul>                                                                                                                                          |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

|                        | <ul> <li>Added a relation</li> </ul>                                                                                                                                   |                                                                                                                                                                                                                                                                          |               |                        |  |  |  |  |

| LPC1850_30_20_10 v.6.4 | 20140818                                                                                                                                                               | Product data sheet                                                                                                                                                                                                                                                       | 201408013F01  | LPC1850_30_20_10 v.6.3 |  |  |  |  |