Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 4K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-VFBGA                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1142af1-an1-a |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

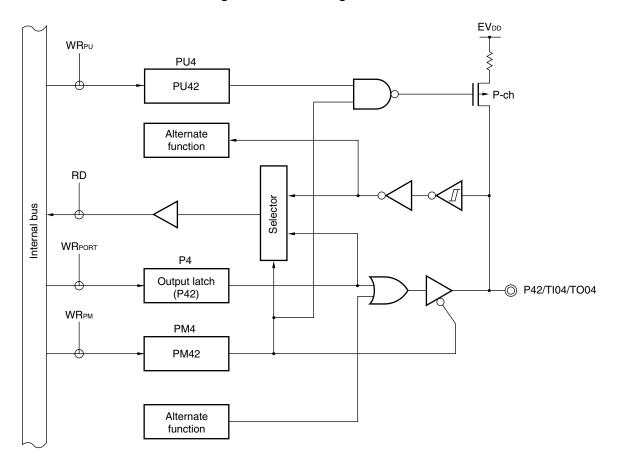

Figure 4-16. Block Diagram of P42

- P4: Port register 4

- PU4: Pull-up resistor option register 4

- PM4: Port mode register 4

- RD: Read signal

- WR××: Write signal

# (3) Pull-up resistor option registers (PU0, PU1, PU3 to PU5, PU7, PU12, PU14)

These registers specify whether the on-chip pull-up resistors of P00 to P06, P10 to P17, P30, P31, P40 to P43, P50 to P55, P70 to P77, P120, P140, or P141 are to be used or not. On-chip pull-up resistors can be used in 1bit units only for the bits set to input mode of the pins to which the use of an on-chip pull-up resistor has been specified in PU0, PU1, PU3 to PU5, PU7, PU12, and PU14. On-chip pull-up resistors cannot be connected to bits set to output mode and bits used as alternate-function output pins, regardless of the settings of PU0, PU1, PU3 to PU5, PU7, PU12, and PU14.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears these registers to 00H.

| Symbol | 7    | 6       | 5           | 4            | 3        | 2            | 1            | 0            | Address | After reset | R/W |  |

|--------|------|---------|-------------|--------------|----------|--------------|--------------|--------------|---------|-------------|-----|--|

| PU0    | 0    | PU06    | PU05        | PU04         | PU03     | PU02         | PU01         | PU00         | F0030H  | 00H         | R/W |  |

|        |      |         |             |              |          |              |              |              |         |             |     |  |

| PU1    | PU17 | PU16    | PU15        | PU14         | PU13     | PU12         | PU11         | PU10         | F0031H  | 00H         | R/W |  |

|        |      |         |             |              |          |              |              |              |         |             |     |  |

| PU3    | 0    | 0       | 0           | 0            | 0        | 0            | PU31         | PU30         | F0033H  | 00H         | R/W |  |

|        |      |         |             |              |          |              |              |              |         |             |     |  |

| PU4    | 0    | 0       | 0           | 0            | PU43     | PU42         | PU41         | PU40         | F0034H  | 00H         | R/W |  |

|        |      |         |             |              |          |              |              |              |         |             |     |  |

| PU5    | 0    | 0       | PU55        | PU54         | PU53     | PU52         | PU51         | PU50         | F0035H  | 00H         | R/W |  |

|        |      |         |             |              |          |              |              |              |         |             |     |  |

| PU7    | PU77 | PU76    | PU75        | PU74         | PU73     | PU72         | PU71         | PU70         | F0037H  | 00H         | R/W |  |

|        |      |         |             |              |          |              |              |              |         |             |     |  |

| PU12   | 0    | 0       | 0           | 0            | 0        | 0            | 0            | PU120        | F003CH  | 00H         | R/W |  |

|        |      |         |             |              |          |              |              |              |         |             |     |  |

| PU14   | 0    | 0       | 0           | 0            | 0        | 0            | PU141        | PU140        | F003EH  | 00H         | R/W |  |

|        |      |         |             |              |          |              |              |              |         |             |     |  |

|        | PUmn |         |             |              | •        | •            | pull-up res  |              |         |             |     |  |

|        |      |         |             |              | (m =     | 0, 1, 3 to 5 | 5, 7, 12, 14 | ; n = 0 to 1 | 7)      |             |     |  |

|        | 0    | On-chip | pull-up res | istor not co | onnected |              |              |              |         |             |     |  |

|        | 1    | On-chip | pull-up res | istor conne  | ected    |              |              |              |         |             |     |  |

## Figure 4-30. Format of Pull-up Resistor Option Register

### (4) Port input mode registers (PIM0)

This register sets the input buffer of P03 or P04 in 1-bit units.

TTL input buffer can be selected during serial communication with an external device of the different potential.

This register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

## Figure 4-31. Format of Port Input Mode Register

| Address: | F0040H | After reset: 00H | R/W |       |       |   |   |   |

|----------|--------|------------------|-----|-------|-------|---|---|---|

| Symbol   | 7      | 6                | 5   | 4     | 3     | 2 | 1 | 0 |

| PIM0     | 0      | 0                | 0   | PIM04 | PIM03 | 0 | 0 | 0 |

| -        |        |                  |     |       |       |   |   |   |

| PIM0n | P0n pin input buffer selection $(n = 3, 4)$ |

|-------|---------------------------------------------|

| 0     | Normal input buffer                         |

| 1     | TTL input buffer                            |

## (5) Port output mode registers (POM0)

This register sets the output mode of P02 to P04 in 1-bit units.

N-ch open drain output (V<sub>DD</sub> tolerance) mode can be selected during serial communication with an external device of the different potential, and for the SDA10 and SDA20 pins during simplified  $I^2C$  communication with an external device of the same potential.

This register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

## Figure 4-32. Format of Port Input Mode Register

| Address: | F0050H | After reset: 00H | R/W |       |       |       |   |   |

|----------|--------|------------------|-----|-------|-------|-------|---|---|

| Symbol   | 7      | 6                | 5   | 4     | 3     | 2     | 1 | 0 |

| POM0     | 0      | 0                | 0   | POM04 | POM03 | POM02 | 0 | 0 |

| PO | OMmn | Pmn pin output mode selection<br>(n = 2 to 4) |  |  |  |  |

|----|------|-----------------------------------------------|--|--|--|--|

|    | 0    | Normal output mode                            |  |  |  |  |

|    | 1    | N-ch open-drain output (V₀₀ tolerance) mode   |  |  |  |  |

| Pin Name                   | Alternate Function           | PM××   | P×× |   |

|----------------------------|------------------------------|--------|-----|---|

|                            | Function Name                | I/O    |     |   |

| P20 to P27 <sup>Note</sup> | ANI0 to ANI7 <sup>Note</sup> | Input  | 1   | × |

| P30                        | RTC1HZ                       | Output | 0   | 0 |

|                            | INTP3                        | Input  | 1   | × |

| P31                        | ТІ03                         | Input  | 1   | × |

|                            | ТО03                         | Output | 0   | 0 |

|                            | INTP4                        | Input  | 1   | × |

| P40                        | TOOL0                        | I/O    | ×   | × |

| P41                        | TOOL1                        | Output | ×   | × |

| P42                        | TI04                         | Input  | 1   | × |

|                            | TO04                         | Output | 0   | 0 |

| P50                        | INTP1                        | Input  | 1   | × |

| P51                        | INTP2                        | Input  | 1   | × |

| P60                        | SCL0                         | I/O    | 0   | 0 |

| P61                        | SDA0                         | I/O    | 0   | 0 |

| P70 to P73                 | KR0 to KR3                   | Input  | 1   | × |

| P74 to P77                 | INTP8 to INTP11              | Input  | 1   | × |

|                            | KR4 to KR7                   | Input  | 1   | × |

| P120                       | INTP0                        | Input  | 1   | × |

|                            | EXLVI                        | Input  | 1   | × |

| P140                       | PCLBUZ0                      | Output | 0   | 0 |

|                            | INTP6                        | Input  | 1   | × |

| P141                       | PCLBUZ1                      | Output | 0   | 0 |

|                            | INTP7                        | Input  | 1   | × |

Table 4-5. Settings of Port Mode Register and Output Latch When Using Alternate Function (2/2)

Remark ×: don't care

PM××: Port mode register

P××: Port output latch

**Note** The function of the ANI0/P20 to ANI7/P27 pins can be selected by using the A/D port configuration register (ADPC), the analog input channel specification register (ADS), and PM2.

Table 4-6. Setting Functions of ANI0/P20 to ANI7/P27 Pins

| ADPC                   | PM2         | ADS                  | ANI0/P20 to ANI7/P27 Pins          |

|------------------------|-------------|----------------------|------------------------------------|

| Digital I/O selection  | Input mode  | -                    | Digital input                      |

|                        | Output mode | -                    | Digital output                     |

| Analog input selection | Input mode  | Selects ANI.         | Analog input (to be converted)     |

|                        |             | Does not select ANI. | Analog input (not to be converted) |

|                        | Output mode | Selects ANI.         | Setting prohibited                 |

|                        |             | Does not select ANI. |                                    |

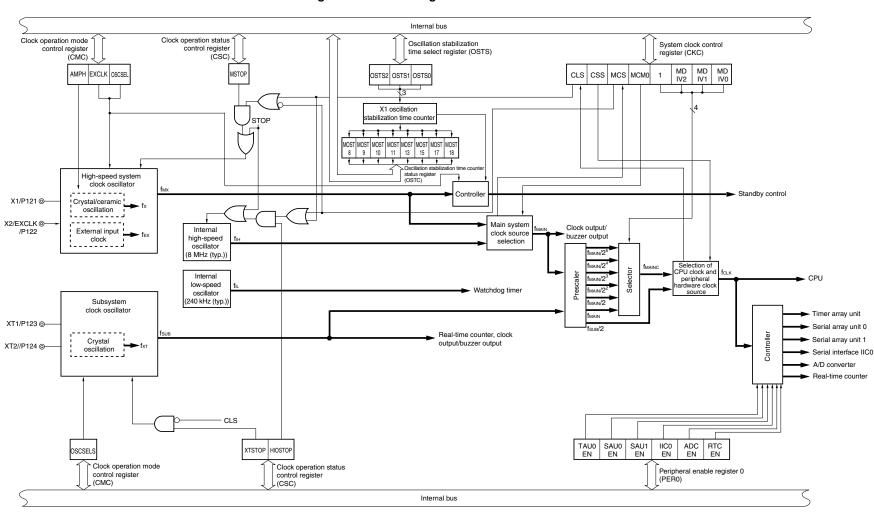

CHAPTER 5 CLOCK GENERATOR

## <R> Figure 5-1. Block Diagram of Clock Generator

#### (2) Example of setting procedure when using the external main system clock

<1> Setting P121/X1 and P122/X2/EXCLK pins (CMC register)

| EXCLK | OSCSEL | 0 | OSCSELS | 0 | 0 | 0 | AMPH |

|-------|--------|---|---------|---|---|---|------|

| 1     | 1      | 0 | 0/1     | 0 | 0 | 0 | ×    |

#### **Remarks 1.** ×: don't care

- 2. For setting of the P123/XT1 and P124/XT2 pins, see 5.6.3 (1) Example of setting procedure when oscillating the subsystem clock.

- <2> Controlling external main system clock input (CSC register) When MSTOP is cleared to 0, the input of the external main system clock is enabled.

- Cautions 1. The CMC register can be written only once after reset release, by an 8-bit memory manipulation instruction.

Therefore, it is necessary to also set the value of the OSCSELS bits at the same time. For OSCSELS bits, see 5.6.3 Example of controlling subsystem clock.

- 2. Set the external main system clock after the supply voltage has reached the operable voltage of the clock to be used (see CHAPTER 27 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS) and CHAPTER 28 ELECTRICAL SPECIFICATIONS ((A) GRADE PRODUCTS)).

- (3) Example of setting procedure when using high-speed system clock as CPU/peripheral hardware clock

- <1> Setting high-speed system clock oscillation<sup>Note</sup>

(See 5.6.1 (1) Example of setting procedure when oscillating the X1 clock and (2) Example of setting procedure when using the external main system clock.)

Note The setting of <1> is not necessary when high-speed system clock is already operating.

<2> Setting the high-speed system clock as the source clock of the CPU/peripheral hardware clock and setting the division ratio of the set clock (CKC register)

| MCM0 | MDIV2 | MDIV1 | MDIV0 | Selection of CPU/Peripheral<br>Hardware Clock (fclk) |

|------|-------|-------|-------|------------------------------------------------------|

| 1    | 0     | 0     | 0     | fмx                                                  |

|      | 0     | 0     | 1     | fmx/2                                                |

|      | 0     | 1     | 0     | fmx/2 <sup>2</sup>                                   |

|      | 0     | 1     | 1     | fmx/2 <sup>3</sup>                                   |

|      | 1     | 0     | 0     | fmx/2 <sup>4</sup>                                   |

|      | 1     | 0     | 1     | fmx/2 <sup>5 Note</sup>                              |

**Note** Setting is prohibited when f<sub>MX</sub> < 4 MHz.

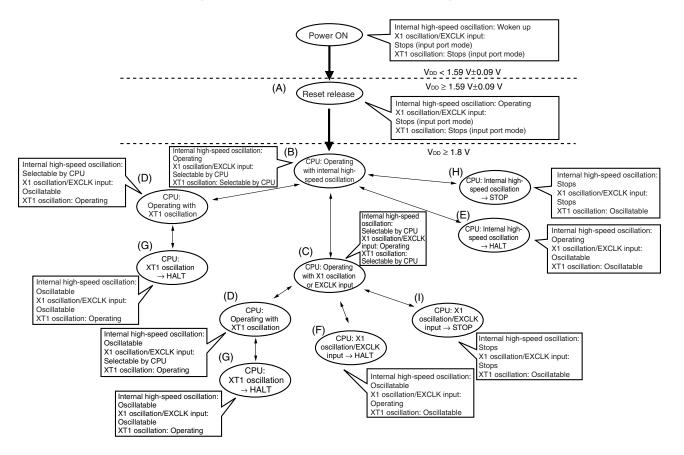

## 5.6.5 CPU clock status transition diagram

Figure 5-15 shows the CPU clock status transition diagram of this product.

Figure 5-15. CPU Clock Status Transition Diagram

**Remark** If the low-power-supply detector (LVI) is set to ON by default by the option bytes, the reset will not be released until the power supply voltage (V<sub>DD</sub>) exceeds 2.07 V±0.2 V. After the reset operation, the status will shift to (B) in the above figure.

Table 5-4 shows transition of the CPU clock and examples of setting the SFR registers.

## Table 5-4. CPU Clock Transition and SFR Register Setting Examples (1/4)

#### (1) CPU operating with internal high-speed oscillation clock (B) after reset release (A)

| Status Transition     | SFR Register Setting                                                      |

|-----------------------|---------------------------------------------------------------------------|

| $(A) \rightarrow (B)$ | SFR registers do not have to be set (default status after reset release). |

#### (2) CPU operating with high-speed system clock (C) after reset release (A)

(The CPU operates with the internal high-speed oscillation clock immediately after a reset release (B).)

| (Setting sequence of SFR registers)                                                                                |                     |        |      |                 |                     |                           |                 |

|--------------------------------------------------------------------------------------------------------------------|---------------------|--------|------|-----------------|---------------------|---------------------------|-----------------|

| Setting Flag of SFR Register                                                                                       | CMC Register Note 1 |        |      | CSC<br>Register | OSMC<br>Register    | OSTC<br>Register          | CKC<br>Register |

| Status Transition                                                                                                  | EXCLK               | OSCSEL | AMPH | MSTOP           | FSEL                |                           | MCM0            |

| $\begin{array}{l} (A) \rightarrow (B) \rightarrow (C) \\ (X1 \ clock:  2 \ MHz \leq fx \leq 10 \ MHz) \end{array}$ | 0                   | 1      | 0    | 0               | 0                   | Must be checked           | 1               |

| $(A) \rightarrow (B) \rightarrow (C)$<br>(X1 clock: 10 MHz < fx $\leq$ 20 MHz)                                     | 0                   | 1      | 1    | 0               | 1 <sup>Note 2</sup> | Must be checked           | 1               |

| $(A) \rightarrow (B) \rightarrow (C)$<br>(external main clock)                                                     | 1                   | 1      | ×    | 0               | 0/1                 | Must<br>not be<br>checked | 1               |

- **Notes 1.** The CMC and OSMC registers can be written only once by an 8-bit memory manipulation instruction after reset release.

- 2. FSEL = 1 when  $f_{CLK} > 10 \text{ MHz}$ If a divided clock is selected and  $f_{CLK} \le 10 \text{ MHz}$ , use with FSEL = 0 is possible even if  $f_X > 10 \text{ MHz}$ .

# Caution Set the clock after the supply voltage has reached the operable voltage of the clock to be set (see CHAPTER 27 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS) and CHAPTER 28 ELECTRICAL SPECIFICATIONS ((A) GRADE PRODUCTS)).

#### Remark ×: don't care

### (3) CPU operating with subsystem clock (D) after reset release (A)

(The CPU operates with the internal high-speed oscillation clock immediately after a reset release (B).)

| (Sett                 | ing sequence of SFR registers) |                              |              |                              | <u> </u>     |

|-----------------------|--------------------------------|------------------------------|--------------|------------------------------|--------------|

|                       | Setting Flag of SFR Register   | CMC Register <sup>Note</sup> | CSC Register | Waiting for                  | CKC Register |

| Status Transition     |                                | OSCSELS                      | XTSTOP       | Oscillation<br>Stabilization | CSS          |

| $(A) \to (B) \to (D)$ |                                | 1                            | 0            | Necessary                    | 1            |

Note The CMC register can be written only once by an 8-bit memory manipulation instruction after reset release.

**Remark** (A) to (I) in Table 5-4 correspond to (A) to (I) in Figure 5-15.

<R>

<R>

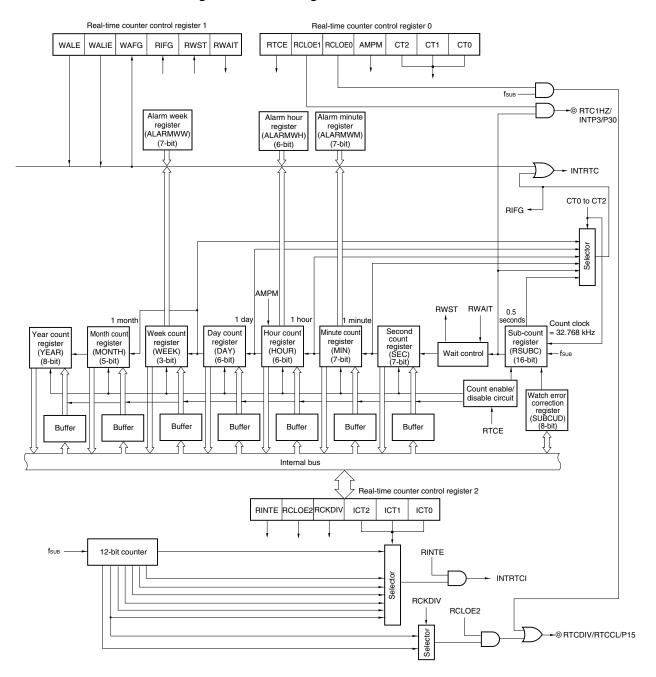

## (11) Month count register (MONTH)

The MONTH register is an 8-bit register that takes a value of 1 to 12 (decimal) and indicates the count value of months.

It counts up when the day counter overflows.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (32.768 kHz) later. Even if the day count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 01 to 12 to this register in BCD code. If a value outside the range is set, the register value returns to the normal value after 1 period.

MONTH can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 01H.

### Figure 7-12. Format of Month Count Register (MONTH)

Address: FFF97H After reset: 01H R/W

| Symbol | 7 | 6 | 5 | 4       | 3      | 2      | 1      | 0      |

|--------|---|---|---|---------|--------|--------|--------|--------|

| MONTH  | 0 | 0 | 0 | MONTH10 | MONTH8 | MONTH4 | MONTH2 | MONTH1 |

### (12) Year count register (YEAR)

The YEAR register is an 8-bit register that takes a value of 0 to 99 (decimal) and indicates the count value of years.

It counts up when the month counter overflows.

Values 00, 04, 08, ..., 92, and 96 indicate a leap year.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (32.768 kHz) later. Even if the month count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 00 to 99 to this register in BCD code. If a value outside the range is set, the register value returns to the normal value after 1 period.

YEAR can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

### Figure 7-13. Format of Year Count Register (YEAR)

Address: FFF98H After reset: 00H R/W

| Symbol | 7      | 6      | 5      | 4      | 3     | 2     | 1     | 0     |

|--------|--------|--------|--------|--------|-------|-------|-------|-------|

| YEAR   | YEAR80 | YEAR40 | YEAR20 | YEAR10 | YEAR8 | YEAR4 | YEAR2 | YEAR1 |

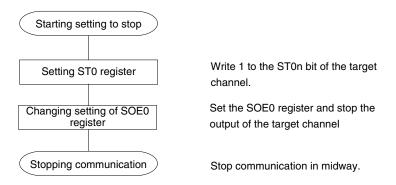

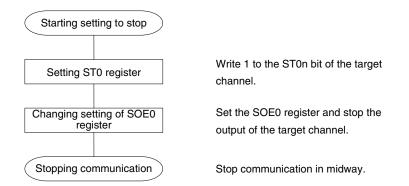

- Remarks 1. Even after communication is stopped, the pin level is retained. To resume the operation, re-set the SO0 register (see Figure 11-27 Procedure for Resuming Master Transmission).

- **2.** p: CSI number (p = 00, 10)

## Figure 11-64. Procedure for Stopping Slave Transmission/Reception

**Remark** Even after communication is stopped, the pin level is retained. To resume the operation, re-set the SO0 register (see Figure 11-65 Procedure for Resuming Slave Transmission/Reception).

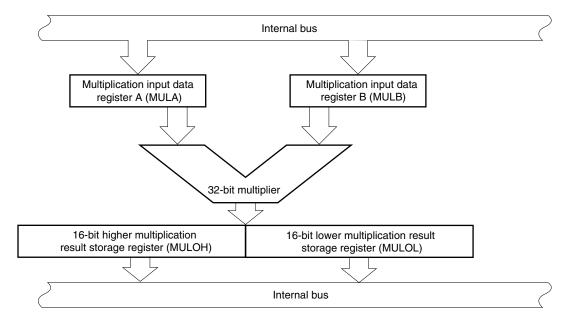

# **CHAPTER 13 MULTIPLIER**

# **13.1 Functions of Multiplier**

The multiplier has the following functions.

• Can execute calculation of 16 bits  $\times$  16 bits = 32 bits.

Figure 13-1 shows the block diagram of the multiplier.

Figure 13-1. Block Diagram of Multiplier

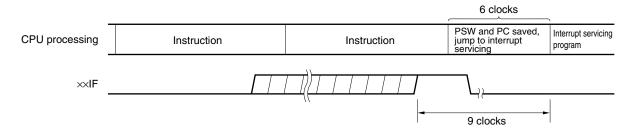

## Figure 15-8. Interrupt Request Acknowledgment Timing (Minimum Time)

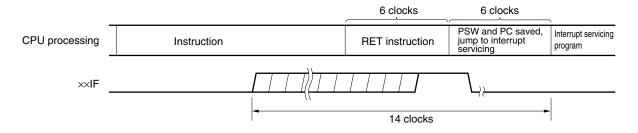

### Figure 15-9. Interrupt Request Acknowledgment Timing (Maximum Time)

### 15.4.2 Software interrupt request acknowledgment

A software interrupt acknowledge is acknowledged by BRK instruction execution. Software interrupts cannot be disabled.

If a software interrupt request is acknowledged, the contents are saved into the stacks in the order of the program status word (PSW), then program counter (PC), the IE flag is reset (0), and the contents of the vector table (0007EH, 0007FH) are loaded into the PC and branched.

Restoring from a software interrupt is possible by using the RETB instruction.

## Caution Do not use the RETI instruction for restoring from the software interrupt.

Remark 1 clock: 1/fclk (fclk: CPU clock)

# **CHAPTER 17 STANDBY FUNCTION**

# 17.1 Standby Function and Configuration

### 17.1.1 Standby function

The standby function reduces the operating current of the system, and the following two modes are available.

## (1) HALT mode

HALT instruction execution sets the HALT mode. In the HALT mode, the CPU operation clock is stopped. If the high-speed system clock oscillator, internal high-speed oscillator, or subsystem clock oscillator is operating before the HALT mode is set, oscillation of each clock continues. In this mode, the operating current is not decreased as much as in the STOP mode, but the HALT mode is effective for restarting operation immediately upon interrupt request generation and carrying out intermittent operations frequently.

## (2) STOP mode

STOP instruction execution sets the STOP mode. In the STOP mode, the high-speed system clock oscillator and internal high-speed oscillator stop, stopping the whole system, thereby considerably reducing the CPU operating current.

Because this mode can be cleared by an interrupt request, it enables intermittent operations to be carried out. However, because a wait time is required to secure the oscillation stabilization time after the STOP mode is released when the X1 clock is selected, select the HALT mode if it is necessary to start processing immediately upon interrupt request generation.

In either of these two modes, all the contents of registers, flags and data memory just before the standby mode is set are held. The I/O port output latches and output buffer statuses are also held.

- Cautions 1. The STOP mode can be used only when the CPU is operating on the main system clock. The STOP mode cannot be set while the CPU operates with the subsystem clock. The HALT mode can be used when the CPU is operating on either the main system clock or the subsystem clock.

- 2. When shifting to the STOP mode, be sure to stop the peripheral hardware operation operating with main system clock before executing STOP instruction.

- 3. The following sequence is recommended for operating current reduction of the A/D converter when the standby function is used: First clear bit 7 (ADCS) and bit 0 (ADCE) of the A/D converter mode register (ADM) to 0 to stop the A/D conversion operation, and then execute the STOP instruction.

- 4. It can be selected by the option byte whether the internal low-speed oscillator continues oscillating or stops in the HALT or STOP mode. For details, see CHAPTER 22 OPTION BYTE.

## 17.1.2 Registers controlling standby function

The standby function is controlled by the following two registers.

- Oscillation stabilization time counter status register (OSTC)

- Oscillation stabilization time select register (OSTS)

Remark For the registers that start, stop, or select the clock, see CHAPTER 5 CLOCK GENERATOR.

| Instruction | Mnemonic | emonic Operands       |   | Clo                   | ocks   | Operation                                                                      |   | =lag |

|-------------|----------|-----------------------|---|-----------------------|--------|--------------------------------------------------------------------------------|---|------|

| Group       |          |                       |   | Note 1                | Note 2 |                                                                                | Z | AC C |

| Condition   | BF       | saddr.bit, \$addr20   | 4 | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 4 + jdisp8$ if (saddr).bit = 0                             |   |      |

| al branch   |          | sfr.bit, \$addr20     | 4 | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 4 + jdisp8$ if sfr.bit = 0                                 |   |      |

|             |          | A.bit, \$addr20       | 3 | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 3 + jdisp8$ if A.bit = 0                                   |   |      |

|             |          | PSW.bit, \$addr20     | 4 | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 4 + jdisp8$ if PSW.bit = 0                                 |   |      |

|             |          | [HL].bit, \$addr20    | 3 | 3/5 <sup>Note 3</sup> | 6/7    | $PC \leftarrow PC + 3 + jdisp8$ if (HL).bit = 0                                |   |      |

|             |          | ES:[HL].bit, \$addr20 | 4 | 4/6 <sup>Note 3</sup> | 7/8    | $PC \leftarrow PC + 4 + jdisp8$ if (ES, HL).bit = 0                            |   |      |

|             | BTCLR    | saddr.bit, \$addr20   | 4 | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 4 + jdisp8$ if (saddr).bit = 1<br>then reset (saddr).bit   | - |      |

|             |          | sfr.bit, \$addr20     | 4 | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 4 + jdisp8$ if sfr.bit = 1 then reset sfr.bit              | - |      |

|             |          | A.bit, \$addr20       | 3 | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 3 + jdisp8$ if A.bit = 1<br>then reset A.bit               |   |      |

|             |          | PSW.bit, \$addr20     | 4 | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 4 + jdisp8$ if PSW.bit = 1<br>then reset PSW.bit           | × | ×    |

|             |          | [HL].bit, \$addr20    | 3 | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 3 + jdisp8$ if (HL).bit = 1<br>then reset (HL).bit         | _ |      |

|             |          | ES:[HL].bit, \$addr20 | 4 | 4/6 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 4 + jdisp8$ if (ES, HL).bit = 1<br>then reset (ES, HL).bit |   |      |

| Conditional | SKC      | -                     | 2 | 1                     | -      | Next instruction skip if CY = 1                                                |   |      |

| skip        | SKNC     | -                     | 2 | 1                     | -      | Next instruction skip if CY = 0                                                |   |      |

|             | SKZ      | -                     | 2 | 1                     | -      | Next instruction skip if Z = 1                                                 |   |      |

|             | SKNZ     | -                     | 2 | 1                     | -      | Next instruction skip if $Z = 0$                                               |   |      |

|             | SKH      | -                     | 2 | 1                     | -      | Next instruction skip if $(Z \lor CY) = 0$                                     | 1 |      |

|             | SKNH     | -                     | 2 | 1                     | -      | Next instruction skip if $(Z \lor CY) = 1$                                     |   |      |

| CPU         | SEL      | RBn                   | 2 | 1                     | -      | RBS[1:0] ← n                                                                   |   |      |

| control     | NOP      | _                     | 1 | 1                     | _      | No Operation                                                                   |   |      |

|             | EI       | _                     | 3 | 4                     | _      | $IE \leftarrow 1(Enable Interrupt)$                                            |   |      |

|             | DI       | _                     | 3 | 4                     | -      | $IE \leftarrow O(Disable Interrupt)$                                           |   |      |

|             | HALT     | -                     | 2 | 3                     | -      | Set HALT Mode                                                                  |   |      |

|             | STOP     | -                     | 2 | 3                     | -      | Set STOP Mode                                                                  |   |      |

|  | Table 26-5. | <b>Operation List</b> | (17/17) |

|--|-------------|-----------------------|---------|

|--|-------------|-----------------------|---------|

**Notes 1.** When the internal RAM area, SFR area, or extended SFR area is accessed, or for an instruction with no data access.

2. When the program memory area is accessed.

3. This indicates the number of clocks "when condition is not met/when condition is met".

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcLK) selected by the system clock control register (CKC).

**2.** This number of clocks is for when the program is in the internal ROM (flash memory) area. When fetching an instruction from the internal RAM area, the number of clocks is twice the number of clocks plus 3, maximum.

**3.** n indicates the number of register banks (n = 0 to 3)

(A) Grade Products

## DC Characteristics (7/10)

## $(TA = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{Vdd} = \text{EVdd} \le 5.5 \text{ V}, 1.8 \text{ V} \le \text{AVREF} \le \text{Vdd}, \text{Vss} = \text{EVss} = \text{AVss} = 0 \text{ V})$

| Parameter | Symbol     |           | (                                             | Conditions                          |                                 | MIN. | TYP. | MAX. | Unit |

|-----------|------------|-----------|-----------------------------------------------|-------------------------------------|---------------------------------|------|------|------|------|

| Supply    | DD1 Note 1 | Operating | $f_{MX} = 20 \text{ MHz}^{Note 2},$           |                                     | Square wave input               |      | 7.0  | 12.2 | mA   |

| current   |            | mode      | $V_{DD} = 5.0 V$                              |                                     | Resonator connection            |      | 7.3  | 12.5 | mA   |

|           |            |           | $f_{MX} = 20 \text{ MHz}^{Note 2},$           |                                     | Square wave input               |      | 7.0  | 12.2 | mA   |

|           |            |           | $V_{DD} = 3.0 V$                              |                                     | Resonator connection            |      | 7.3  | 12.5 | mA   |

|           |            |           | $f_{MX} = 10 \text{ MHz}^{Notes 2, 3},$       | ,                                   | Square wave input               |      | 3.8  | 6.2  | mA   |

|           |            |           | $V_{DD} = 5.0 V$                              |                                     | Resonator connection            |      | 3.9  | 6.3  | mA   |

|           |            |           | $f_{MX} = 10 \text{ MHz}^{Notes 2, 3},$       | ,                                   | Square wave input               |      | 3.8  | 6.2  | mA   |

|           |            |           | $V_{DD} = 3.0 V$                              |                                     | Resonator connection            |      | 3.9  | 6.3  | mA   |

|           |            |           | $f_{MX} = 5 \text{ MHz}^{\text{Notes 2, 3}},$ | Normal current                      | Square wave input               |      | 2.1  | 3.0  | mA   |

|           |            |           | $V_{DD} = 3.0 V$                              | mode                                | Resonator connection            |      | 2.2  | 3.1  | mA   |

|           |            |           |                                               | Low consumption current mode Note 4 | Square wave input               |      | 1.5  | 2.1  | mA   |

|           |            |           |                                               |                                     | Resonator connection            |      | 1.5  | 2.1  | mA   |

|           |            |           | $f_{MX} = 5 \text{ MHz}^{\text{Notes 2, 3}},$ | Normal current                      | Square wave input               |      | 1.4  | 2.1  | mA   |

|           |            |           | $V_{DD} = 2.0 V$                              | mode                                | Resonator connection            |      | 1.4  | 2.1  | mA   |

|           |            |           |                                               | Low consumption                     | Square wave input               |      | 1.4  | 2.0  | mA   |

|           |            |           |                                               | current mode <sup>Note 4</sup>      | Resonator connection            |      | 1.4  | 2.0  | mA   |

|           |            |           | $f_{IH} = 8 \text{ MHz}^{Note 5}$             |                                     | $V_{DD} = 5.0 V$                |      | 3.1  | 5.0  | mA   |

|           |            |           |                                               |                                     | $V_{DD} = 3.0 V$                |      | 3.1  | 5.0  | mA   |

|           |            |           | fsub = 32.768 kHz <sup>Note</sup>             | e 6<br>,                            | $V_{DD} = 5.0 V$                |      | 6.4  | 24.0 | μA   |

|           |            |           | $T_A = -40 \text{ to } +70 \text{ °C}$        | ;                                   | $V_{DD} = 3.0 V$                |      | 6.4  | 24.0 | μA   |

|           |            |           |                                               |                                     | V <sub>DD</sub> = 2.0 V         |      | 6.3  | 21.0 | μA   |

|           |            |           | fsuв = 32.768 kHz <sup>Note</sup>             |                                     | $V_{DD} = 5.0 V$                |      | 6.4  | 31.0 | μA   |

|           |            |           | $T_A = -40 \text{ to } +85 \circ C$           | ;                                   | $V_{\text{DD}} = 3.0 \text{ V}$ |      | 6.4  | 31.0 | μA   |

|           |            |           |                                               |                                     | V <sub>DD</sub> = 2.0 V         |      | 6.3  | 28.0 | μA   |

**Notes 1.** Total current flowing into VDD, EVDD, and AVREF, including the input leakage current flowing when the level of the input pin is fixed to VDD or VSS. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, LVI circuit, I/O port, and on-chip pull-up/pull-down resistors.

- 2. When internal high-speed oscillator and subsystem clock are stopped.

- When AMPH (bit 0 of clock operation mode control register (CMC)) = 0 and FSEL (bit 0 of operation speed mode control register (OSMC)) = 0.

- 4. When the RMC register is set to 5AH.

- 5. When high-speed system clock and subsystem clock are stopped. When FSEL (bit 0 of operation speed mode control register (OSMC)) = 0 is set.

- 6. When internal high-speed oscillator and high-speed system clock are stopped. When watchdog timer is stopped.

- fin: Internal high-speed oscillation clock frequency

- fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- 2. For details on the normal current mode and low consumption current mode according to the regulator output voltage, refer to CHAPTER 21 REGULATOR.

- **3.** Temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

<R>

Remarks 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

# (2) Serial interface: Serial array unit (5/18)

(TA = -40 to +85°C, 1.8 V  $\leq$  VDD = EVDD  $\leq$  5.5 V, Vss = EVss = AVss = 0 V)

|   | Parameter                     | Symbol  | Conditions                                                                                                                                                           | MIN.         | MAX.                | Unit |

|---|-------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------|

| > | SCL10 clock frequency         | fscl    | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} = 100 \ p\text{F}, \ R_{\text{b}} = 3 \ k\Omega \end{array} \end{array} \label{eq:bound}$ |              | 400 <sup>Note</sup> | kHz  |

|   |                               |         | $\label{eq:VDD} \begin{split} 1.8 \ V &\leq V_{\text{DD}} < 2.7 \ V \\ C_{\text{b}} &= 100 \ pF, \ R_{\text{b}} = 5 \ k\Omega \end{split}$                           |              | 300 <sup>Note</sup> | kHz  |

|   | Hold time when SCL10 = "L"    | t∟ow    | $\label{eq:VDD} \begin{split} 2.7 \; V \leq V_{\text{DD}} \leq 5.5 \; V, \\ C_{\text{b}} = 100 \; pF, \; R_{\text{b}} = 3 \; k\Omega \end{split}$                    | 995          |                     | ns   |

|   |                               |         | $\label{eq:VDD} \begin{array}{l} 1.8 \ V \leq V_{\text{DD}} < 2.7 \ V \\ C_{\text{b}} = 100 \ pF, \ R_{\text{b}} = 5 \ k\Omega \end{array}$                          | 1500         |                     | ns   |

|   | Hold time when SCL10 = "H"    | tнıgн   | $\label{eq:VDD} \begin{array}{l} 2.7 \; V \leq V_{\text{DD}} \leq 5.5 \; V, \\ C_{\text{b}} = 100 \; pF, \; R_{\text{b}} = 3 \; k\Omega \end{array}$                 | 995          |                     | ns   |

|   |                               |         | $\label{eq:VDD} \begin{array}{l} 1.8 \ V \leq V_{\text{DD}} < 2.7 \ V \\ C_{\text{b}} = 100 \ pF, \ R_{\text{b}} = 5 \ k\Omega \end{array}$                          | 1500         |                     | ns   |

|   | Data setup time (reception)   | tsu:dat | $\label{eq:VDD} \begin{array}{l} 2.7 \; V \leq V_{\text{DD}} \leq 5.5 \; V, \\ C_{\text{b}} = 100 \; pF, \; R_{\text{b}} = 3 \; k\Omega \end{array}$                 | 1/fмск + 120 |                     | ns   |

|   |                               |         | $\label{eq:VDD} \begin{array}{l} 1.8 \ V \leq V_{\text{DD}} < 2.7 \ V \\ C_{\text{b}} = 100 \ p\text{F}, \ R_{\text{b}} = 5 \ k\Omega \end{array}$                   | 1/fмск + 230 |                     | ns   |

|   | Data hold time (transmission) | thd:dat | $\label{eq:VDD} \begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} = 100 \ p\text{F}, \ R_{\text{b}} = 3 \ k\Omega \end{array}$               | 0            | 160                 | ns   |

|   |                               |         | $\label{eq:VDD} \begin{array}{l} 1.8 \ V \leq V_{\text{DD}} < 2.7 \ V \\ C_{b} = 100 \ pF, \ R_{b} = 5 \ k\Omega \end{array}$                                        | 0            | 210                 | ns   |

# (d) During communication at same potential (simplified I<sup>2</sup>C mode)

<R> Note The value must also be fmck/4 or less.

(Remarks are given on the next page.)

# A.1 Software Package

| SP78K0R                       | Development tools (software) common to the 78K0R microcontrollers are combined in |

|-------------------------------|-----------------------------------------------------------------------------------|

| 78K0R Series software package | this package.                                                                     |

|                               | Part number: $\mu$ S××××SP78K0R                                                   |

Remark xxxx in the part number differs depending on the host machine and OS used.

# $\mu S \times \times \times S P78 K0 R$

| ×××× | Host Machine          | OS                         | Supply Medium |

|------|-----------------------|----------------------------|---------------|

| AB17 | PC-9800 series,       | Windows (Japanese version) | CD-ROM        |

| BB17 | IBM PC/AT compatibles | Windows (English version)  |               |

# A.2 Language Processing Software

| RA78K0R<br>Assembler package            | This assembler converts programs written in mnemonics into object codes executable with a microcontroller.<br>This assembler is also provided with functions capable of automatically creating symbol tables and branch instruction optimization.<br>This assembler should be used in combination with a device file (DF781188).<br><precaution environment="" in="" pc="" ra78kor="" using="" when=""><br/>This assembler package is a DOS-based application. It can also be used in Windows, however, by using the Project Manager (included in assembler package) on Windows.</precaution> |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CC78K0R<br>C compiler package           | Part number: μS××××RA78K0R   This compiler converts programs written in C language into object codes executable with a microcontroller.   This compiler should be used in combination with an assembler package and device file (both sold separately). <precaution cc78k0r="" environment="" in="" pc="" using="" when="">   This C compiler package is a DOS-based application. It can also be used in Windows, however, by using the Project Manager (included in assembler package) on Windows.</precaution>                                                                              |

| DF781188 <sup>Note</sup><br>Device file | Part number: μS××××CC78K0R   This file contains information peculiar to the device.   This device file should be used in combination with a tool (RA78K0R, CC78K0R, SM+ for 78K0R, and ID78K0R-QB) (all sold separately).   The corresponding OS and host machine differ depending on the tool to be used.   Part number: μS××××DF781188                                                                                                                                                                                                                                                      |

Note The DF781188 can be used in common with the RA78K0R, CC78K0R, SM+ for 78K0R, and ID78K0R-QB. Download the DF781188 from the download site for development tools (http://www.necel.com/micro/ods/eng/index.html).

| <b></b>    |                |                                                        |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (29               | /33) |

|------------|----------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|

| Chapter    | Classification | Function                                               | Details of<br>Function                                                                                                              | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pag               | e    |

| Chapter 27 | Hard           | Electrical<br>specifications<br>(standard<br>products) | Recommended<br>oscillator<br>constants                                                                                              | The oscillator constants shown above are reference values based on evaluation in a specific environment by the resonator manufacturer. If it is necessary to optimize the oscillator characteristics in the actual application, apply to the resonator manufacturer for evaluation on the implementation circuit. When doing so, check the conditions for using the RMC register, and whether to enter or exit the STOP mode. The oscillation voltage and oscillation frequency only indicate the oscillator characteristic. Use the 78K0R/KE3 so that the internal operation conditions are within the specifications of the DC and AC characteristics. | p.714             |      |

|            |                |                                                        | DC                                                                                                                                  | P02 to P04 do not output high level in N-ch open-drain mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | p.715             |      |

|            |                |                                                        | characteristics                                                                                                                     | The maximum value of V <sub>IH</sub> of pins P02 to P04 is V <sub>DD</sub> , even in the N-ch open-drain mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                 |      |

|            |                |                                                        |                                                                                                                                     | For P122/EXCLK, the value of V <sub>IH</sub> and V <sub>IL</sub> differs according to the input port mode or external clock mode.<br>Make sure to satisfy the DC characteristics of EXCLK in external clock input mode.                                                                                                                                                                                                                                                                                                                                                                                                                                  | p.717             |      |

|            | Soft           |                                                        | During<br>communication<br>at same potential<br>(UART mode)<br>(dedicated baud<br>rate generator<br>output)                         | When using UART1, select the normal input buffer for RxD1 and the normal output mode for TxD1 by using the PIM0 and POM0 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p.731             |      |

|            |                |                                                        | During<br>communication<br>at same potential<br>(CSI mode)<br>(master mode,<br>SCKp internal<br>clock output)                       | When using CSI10, select the normal input buffer for SI10 and the normal output mode for SO10 and SCK10 by using the PIM0 and POM0 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | p.732             |      |

|            |                |                                                        | During<br>communication<br>at same potential<br>(CSI mode)<br>(slave mode,<br>SCKp external<br>clock input)                         | When using CSI10, select the normal input buffer for SI10 and SCK10 and the normal output mode for SO10 by using the PIM0 and POM0 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | p.733             |      |

|            |                |                                                        | During<br>communication<br>at same potential<br>(simplified I <sup>2</sup> C<br>mode)                                               | Select the normal input buffer and the N-ch open drain output (V <sub>DD</sub> tolerance) mode for SDA10 and the normal output mode for SCL10 by using the PIM0 and POM0 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p.736             |      |

|            |                |                                                        | During<br>communication<br>at different<br>potential (2.5 V,<br>3 V) (UART<br>mode)<br>(dedicated baud<br>rate generator<br>output) | Select the TTL input buffer for RxD1 and the N-ch open drain output ( $V_{DD}$ tolerance) mode for TxD1 by using the PIM0 and POM0 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | pp.737<br>738, 74 |      |