Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 50                                                                                    |

| Program Memory Size        | 96KB (96K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 6K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-TQFP                                                                               |

| Supplier Device Package    | ·                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1143aga-hab-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (b) TI03

This is a pin for inputting an external count clock/capture trigger to 16-bit timer 03.

## (c) TO03

This is a timer output pin from 16-bit timer 03.

# (d) RTC1HZ

This is a real-time counter correction clock (1 Hz) output pin.

# 2.2.5 P40 to P43 (port 4)

P40 to P43 function as a 4-bit I/O port. These pins also function as data I/O for a flash memory programmer/debugger, clock output, and timer I/O.

The following operation modes can be specified in 1-bit units.

## (1) Port mode

P40 to P43 function as an 4-bit I/O port. P40 to P43 can be set to input or output port in 1-bit units using port mode register 4 (PM4). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 4 (PU4).

Be sure to connect an external pull-up resistor to P40 when on-chip debugging is enabled (by using an option byte).

## (2) Control mode

P40 to P42 function as data I/O for a flash memory programmer/debugger, clock output, and timer I/O.

# (a) TOOL0

This is a data I/O pin for a flash memory programmer/debugger. Be sure to pull up this pin externally when on-chip debugging is enabled (pulling it down is prohibited).

# (b) TOOL1

This is a clock output pin for a debugger.

When the on-chip debug function is used, P41/TOOL1 pin can be used as follows by the mode setting on the debugger.

1-line mode: can be used as a port (P41).

2-line mode: used as a TOOL1 pin and cannot be used as a port (P41).

# (c) TI04

This is a pin for inputting an external count clock/capture trigger to 16-bit timers 04.

## (d) TO04

This is a timer output pin from 16-bit timers 04.

# Caution The function of the P40/TOOL0 pin varies as described in (a) to (c) below. In the case of (b) or (c), make the specified connection.

- (a) In normal operation mode and when on-chip debugging is disabled (OCDENSET = 0) by an option byte (000C3H)

- => Use this pin as a port pin (P40).

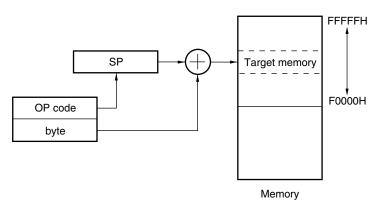

## 3.4.7 Based addressing

# [Function]

Based addressing uses the contents of a register pair specified with the instruction word as a base address, and 8-bit immediate data or 16-bit immediate data as offset data. The sum of these values is used to specify the target address.

# [Operand format]

| Identifier | Description                                                                                 |

|------------|---------------------------------------------------------------------------------------------|

| -          | [HL + byte], [DE + byte], [SP + byte] (only the space from F0000H to FFFFFH is specifiable) |

| _          | word[B], word[C] (only the space from F0000H to FFFFFH is specifiable)                      |

| _          | word[BC] (only the space from F0000H to FFFFH is specifiable)                               |

| _          | ES:[HL + byte], ES:[DE + byte] (higher 4-bit addresses are specified by the ES register)    |

| _          | ES:word[B], ES:word[C] (higher 4-bit addresses are specified by the ES register)            |

| _          | ES:word[BC] (higher 4-bit addresses are specified by the ES register)                       |

# Figure 3-31. Example of [SP+byte]

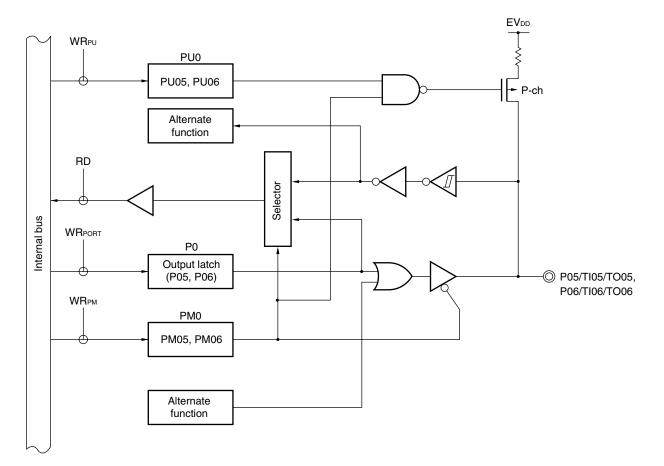

Figure 4-6. Block Diagram of P05 and P06

- P0: Port register 0

- PU0: Pull-up resistor option register 0

- PM0: Port mode register 0

- RD: Read signal

- WR××: Write signal

# (5) Timer channel enable status register 0 (TE0)

TE0 is used to enable or stop the timer operation of each channel.

When a bit of timer channel start register 0 (TS0) is set to 1, the corresponding bit of this register is set to 1. When a bit of timer channel stop register 0 (TT0) is set to 1, the corresponding bit of this register is cleared to 0.

TE0 can be read by a 16-bit memory manipulation instruction.

The lower 8 bits of TE0 can be set with a 1-bit or 8-bit memory manipulation instruction with TE0L. Reset signal generation clears this register to 0000H.

## Figure 6-8. Format of Timer Channel Enable Status Register 0 (TE0)

| Address: F01B0H, F01B1H |    |    | After reset: 0000H |    |    | R  |   |   |      |      |      |      |      |      |      |      |

|-------------------------|----|----|--------------------|----|----|----|---|---|------|------|------|------|------|------|------|------|

| Symbol                  | 15 | 14 | 13                 | 12 | 11 | 10 | 9 | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| TE0                     | 0  | 0  | 0                  | 0  | 0  | 0  | 0 | 0 | TE07 | TE06 | TE05 | TE04 | TE03 | TE02 | TE01 | TE00 |

|                         |    |    |                    |    |    |    |   |   |      |      |      |      |      |      |      |      |

| TE0n | Indication of operation enable/stop status of channel n |

|------|---------------------------------------------------------|

| 0    | Operation is stopped.                                   |

| 1    | Operation is enabled.                                   |

# Caution When TOE0n = 1, even if the output by timer interrupt of each timer (INTTM0n) contends with writing to TO0n, output is normally done to TO0n pin.

**Remark** n = 0 to 6

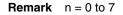

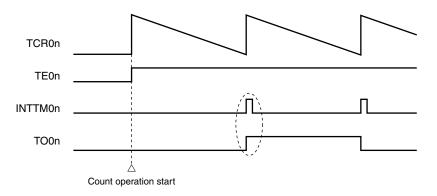

#### 6.4.5 Timer Interrupt and TO0n Pin Output at Operation Start

In the interval timer mode or capture mode, the MD0n0 bit in the TMR0n register sets whether or not to generate a timer interrupt at count start.

When MD0n0 is set to 1, the count operation start timing can be known by the timer interrupt (INTTM0n) generation.

In the other modes, neither timer interrupt at count operation start nor TO0n output is controlled.

Figures 6-32 and 6-33 show operation examples when the interval timer mode (TOE0n = 1, TOM0n = 0) is set.

Figure 6-32. When MD0n0 is set to 1

When MD0n0 is set to 1, a timer interrupt (INTTM0n) is output at count operation start, and TO0n performs a toggle operation.

## Figure 6-33. When MD0n0 is set to 0

When MD0n0 is set to 0, a timer interrupt (INTTM0n) is not output at count operation start, and TO0n does not change either. After counting one cycle, INTTM0n is output and TO0n performs a toggle operation.

**Remark** n = 0 to 6

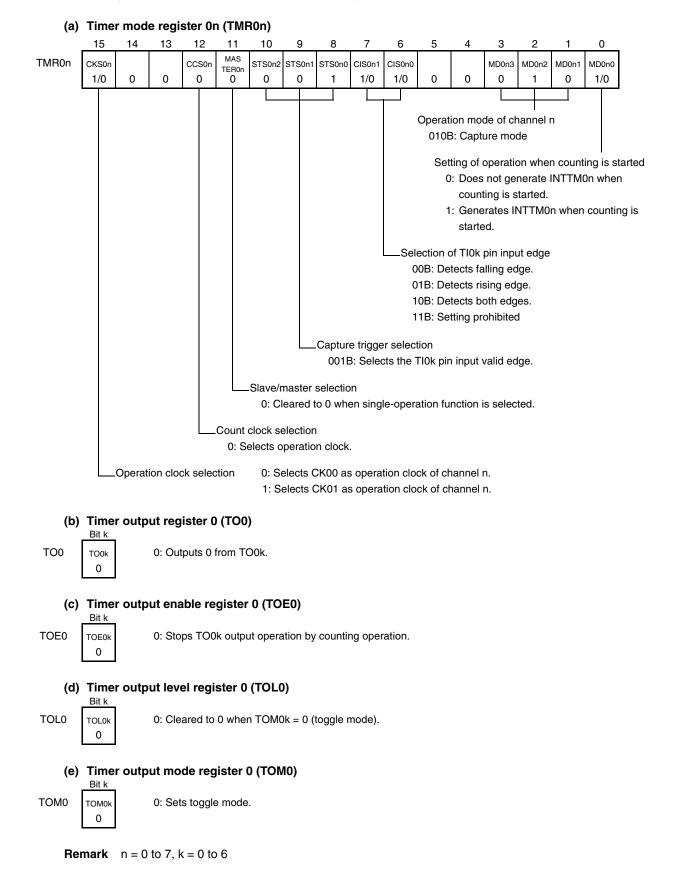

#### Figure 6-49. Example of Set Contents of Registers to Measure Input Pulse Interval

# Figure 7-3. Format of Real-Time Counter Control Register 0 (RTCC0)

| Address: FFF | 9DH After re | set: 00H | R/W    |        |      |     |     |     |

|--------------|--------------|----------|--------|--------|------|-----|-----|-----|

| Symbol       | <7>          | 6        | <5>    | <4>    | 3    | 2   | 1   | 0   |

| RTCC0        | RTCE         | 0        | RCLOE1 | RCLOE0 | AMPM | CT2 | CT1 | CT0 |

| RTCE | Real-time counter operation control |  |  |  |  |  |  |

|------|-------------------------------------|--|--|--|--|--|--|

| 0    | Stops counter operation.            |  |  |  |  |  |  |

| 1    | Starts counter operation.           |  |  |  |  |  |  |

| RCLOE1 | RTC1HZ pin output control            |  |  |  |  |  |  |

|--------|--------------------------------------|--|--|--|--|--|--|

| 0      | isables output of RTC1HZ pin (1 Hz). |  |  |  |  |  |  |

| 1      | Enables output of RTC1HZ pin (1 Hz). |  |  |  |  |  |  |

| RCLOE0 <sup>Note</sup> | RTCCL pin output control                    |  |  |  |  |  |  |  |

|------------------------|---------------------------------------------|--|--|--|--|--|--|--|

| 0                      | isables output of RTCCL pin (32.768 kHz).   |  |  |  |  |  |  |  |

| 1                      | 1 Enables output of RTCCL pin (32.768 kHz). |  |  |  |  |  |  |  |

| AMPM                                                                          | Selection of 12-/24-hour system                                                                               |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 0                                                                             | 12-hour system (a.m. and p.m. are displayed.)                                                                 |  |  |  |  |  |  |  |  |

| 1                                                                             | 24-hour system                                                                                                |  |  |  |  |  |  |  |  |

| Rewrite the A                                                                 | Rewrite the AMPM value after setting RWAIT (bit 0 of RTCC1) to 1. If the AMPM value is changed, the values of |  |  |  |  |  |  |  |  |

| the hour count register (HOUR) change according to the specified time system. |                                                                                                               |  |  |  |  |  |  |  |  |

| Table 7-2 shows the displayed time digits.                                    |                                                                                                               |  |  |  |  |  |  |  |  |

| CT2                                                                                                                                                                                                                                                                                                                             | CT1 | CT0 | Constant-period interrupt (INTRTC) selection                                    |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0                                                                                                                                                                                                                                                                                                                               | 0   | 0   | Does not use constant-period interrupt function.                                |  |  |  |  |  |  |  |

| 0                                                                                                                                                                                                                                                                                                                               | 0   | 1   | Once per 0.5 s (synchronized with second count up)                              |  |  |  |  |  |  |  |

| 0                                                                                                                                                                                                                                                                                                                               | 1   | 0   | Once per 1 s (same time as second count up)                                     |  |  |  |  |  |  |  |

| 0                                                                                                                                                                                                                                                                                                                               | 1   | 1   | Once per 1 m (second 00 of every minute)                                        |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                               | 0   | 0   | Once per 1 hour (minute 00 and second 00 of every hour)                         |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                               | 0   | 1   | Once per 1 day (hour 00, minute 00, and second 00 of every day)                 |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                               | 1   | ×   | Once per 1 month (Day 1, hour 00 a.m., minute 00, and second 00 of every month) |  |  |  |  |  |  |  |

| When changing the values of CT2 to CT0 while the counter operates (RTCE = 1), rewrite the values of CT2 to CT0 after disabling interrupt servicing INTRTC by using the interrupt mask flag register. Furthermore, after rewriting the values of CT2 to CT0, enable interrupt servicing after clearing the RIFG and RTCIF flags. |     |     |                                                                                 |  |  |  |  |  |  |  |

Note RCLOE0 and RCLOE2 must not be enabled at the same time.

# Caution If RCLOE0 and RCLOE1 are changed when RTCE = 1, glitches may occur in the 32.768 kHz and 1 Hz output signals.

Remark ×: don't care

<R>

## (7) Serial flag clear trigger register mn (SIRmn)

SIRmn is a trigger register that is used to clear each error flag of channel n.

When each bit (FECTmn, PECTmn, OVCTmn) of this register is set to 1, the corresponding bit (FEFmn, PEFmn, OVFmn) of serial status register mn is cleared to 0. Because SIRmn is a trigger register, it is cleared immediately when the corresponding bit of SSRmn is cleared.

SIRmn can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of SIRmn can be set with an 8-bit memory manipulation instruction with SIRmnL.

Reset signal generation clears this register to 0000H.

# Figure 11-10. Format of Serial Flag Clear Trigger Register mn (SIRmn)

| Address: F01 | 08H, F0 | 0109H ( | SIR00)  | to F010  | DEH, FC | 10FH ( | SIR03), | Afte | r reset: | 0000H | R/W |   |   |     |     |     |

|--------------|---------|---------|---------|----------|---------|--------|---------|------|----------|-------|-----|---|---|-----|-----|-----|

| F01          | 4CH, F  | 014DH   | (SIR12) | ), F014l | EH, F01 | 4FH (S | SIR13)  |      |          |       |     |   |   |     |     |     |

| Symbol       | 15      | 14      | 13      | 12       | 11      | 10     | 9       | 8    | 7        | 6     | 5   | 4 | 3 | 2   | 1   | 0   |

| SIRmn        | 0       | 0       | 0       | 0        | 0       | 0      | 0       | 0    | 0        | 0     | 0   | 0 | 0 | FEC | PEC | OVC |

|              |         |         |         |          |         |        |         |      |          |       |     |   |   | Tmn | Tmn | Tmn |

| FEC | Clear trigger of framing error of channel n      |  |  |  |  |  |

|-----|--------------------------------------------------|--|--|--|--|--|

| Tmn |                                                  |  |  |  |  |  |

| 0   | No trigger operation                             |  |  |  |  |  |

| 1   | Clears the FEFmn bit of the SSRmn register to 0. |  |  |  |  |  |

| PEC<br>Tmn | Clear trigger of parity error flag of channel n  |  |  |  |  |

|------------|--------------------------------------------------|--|--|--|--|

| 0          | No trigger operation                             |  |  |  |  |

| 1          | Clears the PEFmn bit of the SSRmn register to 0. |  |  |  |  |

| OVC | Clear trigger of overrun error flag of channel n |  |  |  |  |

|-----|--------------------------------------------------|--|--|--|--|

| Tmn |                                                  |  |  |  |  |

| 0   | No trigger operation                             |  |  |  |  |

| 1   | Clears the OVFmn bit of the SSRmn register to 0. |  |  |  |  |

## Caution Be sure to clear bits 15 to 3 to "0".

- **Remarks 1.** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), mn = 00 to 03, 12, 13

- 2. When the SIRmn register is read, 0000H is always read.

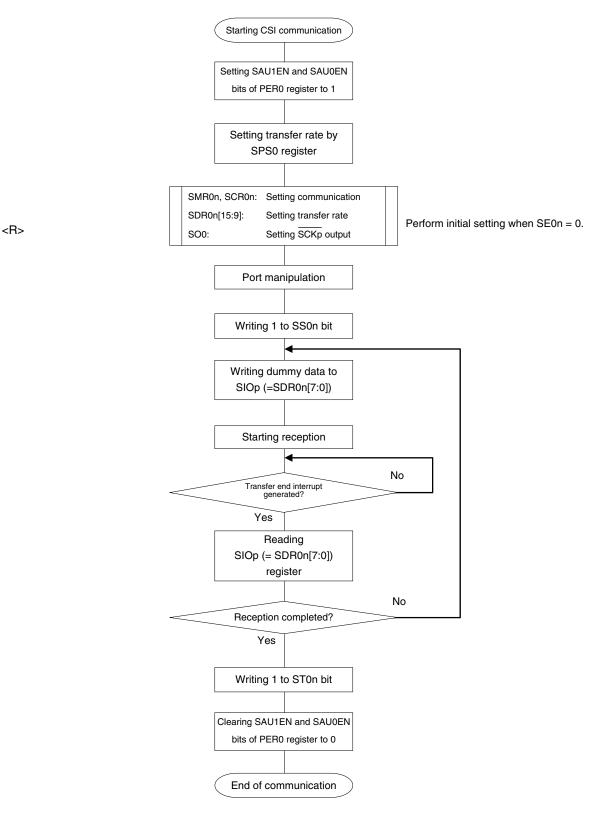

Figure 11-37. Flowchart of Master Reception (in Single-Reception Mode)

Caution After setting the PER0 register to 1, be sure to set the SPS0 register after 4 or more clocks have elapsed.

| SE01 <sup>Note1</sup> | MD012 | MD011 | TXE01 | RXE01 | PM11 <sup>Note2</sup> | P11 <sup>Note2</sup> | Operation mode                         | Pin Function                   |

|-----------------------|-------|-------|-------|-------|-----------------------|----------------------|----------------------------------------|--------------------------------|

|                       |       |       |       |       |                       |                      |                                        | SI00/RxD0/P11 <sup>Note2</sup> |

|                       |       |       |       |       |                       |                      |                                        |                                |

| 0                     | 0     | 1     | 0     | 0     | Note3<br>×            | × <sup>Note3</sup>   | Operation stop<br>mode                 | SI00/P11                       |

| 1                     | 0     | 1     | 0     | 1     | 1                     | ×                    | UART0<br>reception <sup>Note4, 5</sup> | RxD0                           |

Table 11-6. Relationship between register settings and pins (Channel 1 of unit 0: UART0 reception)

Notes 1. The SE0 register is a read-only status register which is set using the SS0 and ST0 registers.

- 2. When channel 1 of unit 0 is set to UART0 reception, this pin becomes an RxD0 function pin. In this case, set channel 0 of unit 0 to operation stop mode or UART0 transmission (refer to **Table 11-5**). When channel 0 of unit 0 is set to CSI00, this pin cannot be used as an RxD0 function pin. In this case, set channel 1 of unit 0 to operation stop mode.

- **3.** This pin can be set as a port function pin.

- 4. When using UART0 transmission and reception in a pair, set channel 0 of unit 0 to UART0 transmission (refer to **Table 11-5**).

- The SMR00 register of channel 0 of unit 0 must also be set during UART0 reception. For details, refer to 11.6.2 (1) Register setting.

Remark X: Don't care

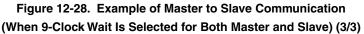

condition

condition

IIC0 ← FFH Note 2

Note 2

(When SPIE0 = 1)

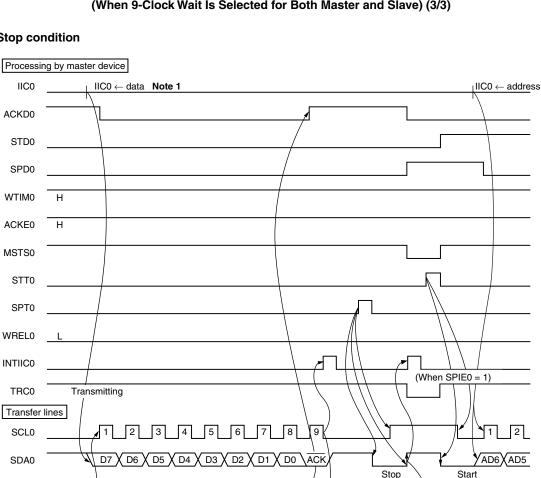

## (3) Stop condition

Processing by slave device

Н

н

Т

L Receiving

Note 2

/IIC0  $\leftarrow$  FFH Note 2

IIC0

ACKD0

STD0

SPD0

WTIMO

ACKE0

MSTS0

STT0

SPT0

WREL0

**INTIIC0**

TRC0

| HALT Mode               | e Setting | When HALT Instruction Is                                                                                                                                            | s Executed While CPU Is Operat            | ing on Main System Clock                                                     |  |  |  |

|-------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| Item                    |           | When CPU Is Operating on<br>Internal High-Speed<br>Oscillation Clock (f⊮)                                                                                           | When CPU Is Operating on<br>X1 Clock (fx) | When CPU Is Operating on<br>External Main System Clock<br>(f <sub>EX</sub> ) |  |  |  |

| System clock            |           | Clock supply to the CPU is stop                                                                                                                                     | oped                                      |                                                                              |  |  |  |

| Main system clock       | fін       | Operation continues (cannot Status before HALT mode was set is retained be stopped)                                                                                 |                                           |                                                                              |  |  |  |

|                         | fx        | Status before HALT mode<br>was set is retained                                                                                                                      | Operation continues (cannot be stopped)   | Cannot operate                                                               |  |  |  |

|                         | fex       |                                                                                                                                                                     | Cannot operate                            | Operation continues (cannot be stopped)                                      |  |  |  |

| Subsystem clock         | fхт       | Status before HALT mode was                                                                                                                                         | set is retained                           |                                                                              |  |  |  |

| fiL.                    |           | Set by bits 0 (WDSTBYON) and 4 (WTON) of option byte (000C0H)<br>• WTON = 0: Stops<br>• WTON = 1 and WDSTBYON = 1: Oscillates<br>• WTON = 1 and WDSTBYON = 0: Stops |                                           |                                                                              |  |  |  |

| CPU                     |           | Operation stopped                                                                                                                                                   |                                           |                                                                              |  |  |  |

| Flash memory            |           | Operable in low-current consumption mode                                                                                                                            |                                           |                                                                              |  |  |  |

| RAM                     |           | Operation stopped. However, status before HALT mode was set is retained at voltage higher than POC detection voltage.                                               |                                           |                                                                              |  |  |  |

| Port (latch)            |           | Status before HALT mode was set is retained                                                                                                                         |                                           |                                                                              |  |  |  |

| Timer array unit (TAU)  |           | Operable                                                                                                                                                            |                                           |                                                                              |  |  |  |

| Real-time counter (RTC  | ;)        |                                                                                                                                                                     |                                           |                                                                              |  |  |  |

| Watchdog timer          |           | Set by bits 0 (WDSTBYON) and 4 (WTON) of option byte (000C0H)<br>• WTON = 0: Stops<br>• WTON = 1 and WDSTBYON = 1: Operates<br>• WTON = 1 and WDSTBYON = 0: Stops   |                                           |                                                                              |  |  |  |

| Clock output/buzzer out | tput      | Operable                                                                                                                                                            |                                           |                                                                              |  |  |  |

| A/D converter           |           |                                                                                                                                                                     |                                           |                                                                              |  |  |  |

| Serial array unit (SAU) |           | ]]                                                                                                                                                                  |                                           |                                                                              |  |  |  |

| Serial interface (IIC0) |           |                                                                                                                                                                     |                                           |                                                                              |  |  |  |

| Multiplier              |           | Operation stopped                                                                                                                                                   |                                           |                                                                              |  |  |  |

| DMA controller          |           | Operable                                                                                                                                                            |                                           |                                                                              |  |  |  |

| Power-on-clear function | ı         |                                                                                                                                                                     |                                           |                                                                              |  |  |  |

| Low-voltage detection f | unction   |                                                                                                                                                                     |                                           |                                                                              |  |  |  |

| External interrupt      |           |                                                                                                                                                                     |                                           |                                                                              |  |  |  |

| Key interrupt function  |           |                                                                                                                                                                     |                                           |                                                                              |  |  |  |

| Table 17-1. | Operating | Statuses | in HALT | Mode | (1/2) |

|-------------|-----------|----------|---------|------|-------|

|             | - p       |          |         |      | ···-/ |

Remark fin: Internal high-speed oscillation clock

- fx: X1 clock

- fex: External main system clock

- fxT: XT1 clock

- fı∟: Internal low-speed oscillation clock

- (2) When detecting level of input voltage from external input pin (EXLVI)

- When starting operation

- <1> Mask the LVI interrupt (LVIMK = 1).

- <2> Set bit 2 (LVISEL) of the low-voltage detection register (LVIM) to 1 (detects level of input voltage from external input pin (EXLVI)).

- <3> Set bit 7 (LVION) of LVIM to 1 (enables LVI operation).

- <4> Use software to wait for the following periods of time (Total 410  $\mu$ s).

- Operation stabilization time (10 μs (MAX.))

- Minimum pulse width (200 µs (MIN.))

- Detection delay time (200 µs (MAX.))

- <5> Wait until it is checked that (input voltage from external input pin (EXLVI) ≥ detection voltage (VEXLVI = 1.21 V (TYP.))) by bit 0 (LVIF) of LVIM.

- <6> Set bit 1 (LVIMD) of LVIM to 1 (generates reset signal when the level is detected).

Figure 20-7 shows the timing of the internal reset signal generated by the low-voltage detector. The numbers in this timing chart correspond to <1> to <6> above.

- Cautions 1. <1> must always be executed. When LVIMK = 0, an interrupt may occur immediately after the processing in <3>.

- 2. If input voltage from external input pin (EXLVI) ≥ detection voltage (V<sub>EXLVI</sub> = 1.21 V (TYP.)) when LVIMD is set to 1, an internal reset signal is not generated.

- 3. Input voltage from external input pin (EXLVI) must be EXLVI < VDD.

- When stopping operation

Either of the following procedures must be executed.

- When using 8-bit memory manipulation instruction: Write 00H to LVIM.

- When using 1-bit memory manipulation instruction: Clear LVIMD to 0 and then LVION to 0.

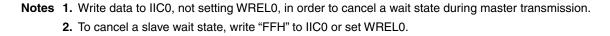

Examples of the recommended connection when using the adapter for flash memory writing are shown below.

- Notes 1. This pin is not required to be connected when using PG-FP5 or FL-PR5.

- 2. Connect SI/RxD or SO/TxD when using QB-MINI2.

WRITER INTERFACE

## 23.7 Security Settings

The 78K0R/KE3 supports a security function that prohibits rewriting the user program written to the internal flash memory, so that the program cannot be changed by an unauthorized person.

The operations shown below can be performed using the Security Set command. The security setting is valid when the programming mode is set next.

• Disabling batch erase (chip erase)

Execution of the block erase and batch erase (chip erase) commands for entire blocks in the flash memory is prohibited by this setting during on-board/off-board programming. Once execution of the batch erase (chip erase) command is prohibited, all of the prohibition settings (including prohibition of batch erase (chip erase)) can no longer be cancelled.

# Caution After the security setting for the batch erase is set, erasure cannot be performed for the device. In addition, even if a write command is executed, data different from that which has already been written to the flash memory cannot be written, because the erase command is disabled.

• Disabling block erase

Execution of the block erase command for a specific block in the flash memory is prohibited during on-board/offboard programming. However, blocks can be erased by means of self programming.

• Disabling write

Execution of the write and block erase commands for entire blocks in the flash memory is prohibited during onboard/off-board programming. However, blocks can be written by means of self programming.

• Disabling rewriting boot cluster 0

Execution of the write command, block erase command, and batch erase (chip erase) command for boot cluster 0 (00000H to 00FFFH) in the flash memory is prohibited by this setting.

The batch erase (chip erase), block erase, write commands, and rewriting boot cluster 0 are enabled by the default setting when the flash memory is shipped. Security can be set by on-board/off-board programming and self programming. Each security setting can be used in combination.

All the security settings are cleared by executing the batch erase (chip erase) command.

Table 23-7 shows the relationship between the erase and write commands when the 78K0R/KE3 security function is enabled.

**Remark** To prohibit writing and erasing during self-programming, use the flash sealed window function (see **23.9.2** for detail).

## 23.9.2 Flash shield window function

The flash shield window function is provided as one of the security functions for self programming. It disables writing to and erasing areas outside the range specified as a window only during self programming.

The window range can be set by specifying the start and end blocks. The window range can be set or changed during both on-board/off-board programming and self programming.

Writing to and erasing areas outside the window range are disabled during self programming. During on-board/offboard programming, however, areas outside the range specified as a window can be written and erased.

# Figure 23-13. Flash Shield Window Setting Example (Target Devices: μPD78F1142, 78F1142A, Start Block: 04H, End Block: 06H)

# Caution If the rewrite-prohibited area of the boot cluster 0 overlaps with the flash shield window range, prohibition to rewrite the boot cluster 0 takes priority.

Table 23-11. Relationship Between Flash Shield Window Function Setting/Change Methods and Commands

| Programming Conditions            | Window Range                                                                                      | Execution Commands                                            |                                                                 |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------|--|

|                                   | Setting/Change Methods                                                                            | Block Erase                                                   | Write                                                           |  |

| Self-programming                  | brogramming Specify the starting and<br>ending blocks by the set<br>information library.          |                                                               | Writing is enabled only<br>within the range of<br>window range. |  |

| On-board/off-board<br>programming | Specify the starting and<br>ending blocks on GUI of<br>dedicated flash memory<br>programmer, etc. | Block erasing is enabled<br>also outside the window<br>range. | Writing is enabled also<br>outside the window<br>range.         |  |

Remark See 23.7 Security Settings to prohibit writing/erasing during on-board/off-board programming.

| Instruction | Mnemonic | Operands             | Bytes | Clo    | cks    | Operation                           |   | Flag  |

|-------------|----------|----------------------|-------|--------|--------|-------------------------------------|---|-------|

| Group       |          |                      |       | Note 1 | Note 2 |                                     | z | AC CY |

| 8-bit data  | MOV      | A, [HL + byte]       | 2     | 1      | 4      | $A \leftarrow (HL + byte)$          |   |       |

| transfer    |          | [HL + byte], A       | 2     | 1      | -      | (HL + byte) ← A                     |   |       |

|             |          | A, [HL + B]          | 2     | 1      | 4      | $A \leftarrow (HL + B)$             |   |       |

|             |          | [HL + B], A          | 2     | 1      | -      | (HL + B) ← A                        |   |       |

|             |          | A, [HL + C]          | 2     | 1      | 4      | $A \leftarrow (HL + C)$             |   |       |

|             |          | [HL + C], A          | 2     | 1      | -      | $(HL + C) \leftarrow A$             |   |       |

|             |          | word[B], #byte       | 4     | 1      | -      | $(B + word) \leftarrow byte$        |   |       |

|             |          | A, word[B]           | 3     | 1      | 4      | $A \leftarrow (B + word)$           |   |       |

|             |          | word[B], A           | 3     | 1      | _      | $(B + word) \leftarrow A$           |   |       |

|             |          | word[C], #byte       | 4     | 1      | -      | $(C + word) \leftarrow byte$        |   |       |

|             |          | A, word[C]           | 3     | 1      | 4      | $A \leftarrow (C + word)$           |   |       |

|             |          | word[C], A           | 3     | 1      | -      | $(C + word) \leftarrow A$           |   |       |

|             |          | word[BC], #byte      | 4     | 1      | -      | (BC + word) ← byte                  |   |       |

|             |          | A, word[BC]          | 3     | 1      | 4      | $A \leftarrow (BC + word)$          |   |       |

|             |          | word[BC], A          | 3     | 1      | -      | $(BC + word) \leftarrow A$          |   |       |

|             |          | [SP + byte], #byte   | 3     | 1      | -      | (SP + byte) ← byte                  |   |       |

|             |          | A, [SP + byte]       | 2     | 1      | -      | $A \leftarrow (SP + byte)$          |   |       |

|             |          | [SP + byte], A       | 2     | 1      | -      | (SP + byte) ← A                     |   |       |

|             |          | B, saddr             | 2     | 1      | -      | $B \leftarrow (saddr)$              |   |       |

|             |          | B, !addr16           | 3     | 1      | 4      | $B \leftarrow (addr16)$             |   |       |

|             |          | C, saddr             | 2     | 1      | -      | $C \leftarrow (saddr)$              |   |       |

|             |          | C, laddr16           | 3     | 1      | 4      | $C \leftarrow (addr16)$             |   |       |

|             |          | X, saddr             | 2     | 1      | -      | $X \leftarrow (saddr)$              |   |       |

|             |          | X, !addr16           | 3     | 1      | 4      | X ← (addr16)                        |   |       |

|             |          | ES:!addr16, #byte    | 5     | 2      | -      | (ES, addr16) $\leftarrow$ byte      |   |       |

|             |          | A, ES:!addr16        | 4     | 2      | 5      | $A \leftarrow (ES, addr16)$         |   |       |

|             |          | ES:!addr16, A        | 4     | 2      | -      | (ES, addr16) $\leftarrow$ A         |   |       |

|             |          | A, ES:[DE]           | 2     | 2      | 5      | $A \leftarrow (ES, DE)$             |   |       |

|             |          | ES:[DE], A           | 2     | 2      | -      | $(ES,DE) \gets A$                   |   |       |

|             |          | ES:[DE + byte],#byte | 4     | 2      | -      | $((ES, DE) + byte) \leftarrow byte$ |   |       |

|             |          | A, ES:[DE + byte]    | 3     | 2      | 5      | $A \leftarrow ((ES, DE) + byte)$    |   |       |

|             |          | ES:[DE + byte], A    | 3     | 2      | -      | $((ES, DE) + byte) \leftarrow A$    |   |       |

Table 26-5. Operation List (2/17)

**Notes 1.** When the internal RAM area, SFR area, or extended SFR area is accessed, or for an instruction with no data access.

- 2. When the program memory area is accessed.

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcLK) selected by the system clock control register (CKC).

- **2.** This number of clocks is for when the program is in the internal ROM (flash memory) area. When fetching an instruction from the internal RAM area, the number of clocks is twice the number of clocks plus 3, maximum.

## Standard Products

## (2) Serial interface: Serial array unit (17/18)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

| Parameter                     | Symbol  | Conditions                                                  | MIN.       | MAX.                | Unit |

|-------------------------------|---------|-------------------------------------------------------------|------------|---------------------|------|

| SCL10 clock frequency         | fscL    | $4.0 V \le V_{DD} \le 5.5 V$ ,                              |            | 400 <sup>Note</sup> | kHz  |

|                               |         | $2.7 \text{ V} \le V_b \le 4.0 \text{ V},$                  |            | 400                 |      |

|                               |         | $C_b = 100 \text{ pF}, R_b = 1.4 \text{ k}\Omega$           |            |                     |      |

|                               |         | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 4.0 \text{ V},$ |            | 400 <sup>Note</sup> | kHz  |

|                               |         | $2.3 V \le V_b \le 2.7 V$ ,                                 |            |                     |      |

|                               |         | $C_b = 100 \text{ pF}, \text{ R}_b = 2.7 \text{ k}\Omega$   |            |                     |      |

| Hold time when SCL10 = "L"    | tLOW    | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                      | 1065       |                     | ns   |

|                               |         | $2.7~V \leq V_b \leq 4.0~V,$                                |            |                     |      |

|                               |         | $C_b = 100 \text{ pF}, \text{ R}_b = 1.4 \text{ k}\Omega$   |            |                     |      |

|                               |         | $2.7~V \leq V_{\text{DD}} \leq 4.0~V,$                      | 1065       |                     | ns   |

|                               |         | $2.3~V \le V_b \le 2.7~V,$                                  |            |                     |      |

|                               |         | $C_b$ = 100 pF, $R_b$ = 2.7 k $\Omega$                      |            |                     |      |

| Hold time when SCL10 = "H"    | tніgн   | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                      | 445        |                     | ns   |

|                               |         | $2.7~V \leq V_b \leq 4.0~V,$                                |            |                     |      |

|                               |         | $C_b$ = 100 pF, $R_b$ = 1.4 k $\Omega$                      |            |                     |      |

|                               |         | $2.7~V \leq V_{\text{DD}} \leq 4.0~V,$                      | 445        |                     | ns   |

|                               |         | $2.3~V \leq V_b \leq 2.7~V,$                                |            |                     |      |

|                               |         | $C_b$ = 100 pF, $R_b$ = 2.7 k $\Omega$                      |            |                     |      |

| Data setup time (reception)   | tsu:dat | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                      | 1/fмск+190 |                     | ns   |

|                               |         | $2.7~V \leq V_b \leq 4.0~V,$                                |            |                     |      |

|                               |         | $C_b$ = 100 pF, $R_b$ = 1.4 k $\Omega$                      |            |                     |      |

|                               |         | $2.7~V \leq V_{\text{DD}} \leq 4.0~V,$                      | 1/fмск+190 |                     | ns   |

|                               |         | $2.3~V \leq V_b \leq 2.7~V,$                                |            |                     |      |

|                               |         | $C_b$ = 100 pF, $R_b$ = 2.7 k $\Omega$                      |            |                     |      |

| Data hold time (transmission) | thd:dat | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                      | 0          | 160                 | ns   |

|                               |         | $2.7~V \leq V_b \leq 4.0~V,$                                |            |                     |      |

|                               |         | $C_{\rm b}=100~pF,~R_{\rm b}=1.4~k\Omega$                   |            |                     |      |

|                               |         | $2.7~V \leq V_{\text{DD}} \leq 4.0~V,$                      | 0          | 160                 | ns   |

|                               |         | $2.3~V \le V_b \le 2.7~V,$                                  |            |                     |      |

|                               |         | $C_b = 100 \text{ pF}, \text{ R}_b = 2.7 \text{ k}\Omega$   |            |                     |      |

## (h) During Communication at different potential (2.5 V, 3 V) (simplified I<sup>2</sup>C mode)

<R>

<R>

**Note** The value must also be fMCK/4 or less.

# Caution Select the TTL input buffer and the N-ch open drain output (VDD tolerance) mode for SDA10 and the N-ch open drain output (VDD tolerance) mode for SCL10 by using the PIM0 and POM0 registers.

**Remarks 1.**  $R_b[\Omega]$ :Communication line (SDA10, SCL10) pull-up resistance,

Cb[F]: Communication line (SDA10, SCL10) load capacitance, Vb[V]: Communication line voltage **2.** fмск: Serial array unit operation clock frequency

(Operation clock to be set by the CKS02 bit of the SMR02 register.)

3. V<sub>IH</sub> and V<sub>IL</sub> below are observation points for the AC characteristics of the serial array unit when communicating at different potentials in simplified I<sup>2</sup>C mode mode.

$4.0~V \leq V_{\text{DD}} \leq 5.5~V,~2.7~V \leq V_{\text{b}} \leq 4.0~V;~V_{\text{IH}} = 2.2~V,~V_{\text{IL}} = 0.8~V$

$2.7~V \leq V_{\text{DD}} \leq 4.0~V,~2.3~V \leq V_{\text{b}} \leq 2.7~V;~V_{\text{IH}} = 2.0~V,~V_{\text{IL}} = 0.5~V$

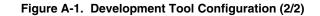

(2) When using the on-chip debug emulator with programming function QB-MINI2

- **Notes 1.** Download the device file for 78K0R/KE3 (DF781188) and the integrated debugger (ID78K0R-QB) from the download site for development tools (http://www.necel.com/micro/ods/eng/index.html).

- 2. The project manager PM+ is included in the assembler package. The PM+ is only used for Windows.

- 3. On-chip debug emulator QB-MINI2 is supplied with USB interface cable, connection cables (10-pin cable and 16-pin cable), and 78K0-OCD board. Any other products are sold separately. In addition, download the software for operating the QB-MINI2 from the download site for MINICUBE2 (http://www.necel.com/micro/en/development/asia/minicube2/minicube2.html).

|            |                |                                                         |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (30/                | 33) |

|------------|----------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|

| Chapter    | Classification | Function                                                | Details of<br>Function                                                                                                               | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                | 1   |

| Chapter 27 | Soft           | Electrical<br>specifications<br>(standard<br>products)  | During<br>communication<br>at different<br>potential (2.5 V,<br>3 V) (CSI mode)<br>(master mode,<br>SCK10 internal<br>clock output)  | Select the TTL input buffer for SI10 and the N-ch open-drain output (VDD tolerance) mode for SO10 and SCK10 by using the PIM0 and POM0 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | pp.741,<br>742, 743 |     |

|            |                |                                                         | During<br>communication<br>at different<br>potential (2.5 V,<br>3 V) (CSI mode)<br>(slave mode,<br>SCK10<br>external clock<br>input) | Select the TTL input buffer for SI10 and SCK10 and the N-ch open-drain output (V <sub>DD</sub> tolerance) mode for SO10 by using the PIM0 and POM0 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | pp.745,<br>746      |     |

|            |                |                                                         | During<br>communication<br>at different<br>potential (2.5 V,<br>3 V) (simplified<br>I <sup>2</sup> C mode)                           | Select the TTL input buffer and the N-ch open-drain output ( $V_{DD}$ tolerance) mode for SDA10 and the N-ch open-drain output ( $V_{DD}$ tolerance) mode for SCL10 by using the PIM0 and POM0 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                | pp.747,<br>748      |     |

| Chapter 28 | Hard           | Electrical<br>specifications<br>((A) grade<br>products) | 1                                                                                                                                    | The 78K0R/KE3 has an on-chip debug function, which is provided for development<br>and evaluation. Do not use the on-chip debug function in products designated for<br>mass production, because the guaranteed number of rewritable times of the flash<br>memory may be exceeded when this function is used, and product reliability<br>therefore cannot be guaranteed. NEC Electronics is not liable for problems<br>occurring when the on-chip debug function is used.                                                                                                                                                                                  | p.758               |     |

|            |                |                                                         | Absolute<br>maximum ratings                                                                                                          | Product quality may suffer if the absolute maximum rating is exceeded even<br>momentarily for any parameter. That is, the absolute maximum ratings are rated<br>values at which the product is on the verge of suffering physical damage, and<br>therefore the product must be used under conditions that ensure that the absolute<br>maximum ratings are not exceeded.                                                                                                                                                                                                                                                                                  |                     |     |

|            |                |                                                         | X1 oscillator<br>characteristics                                                                                                     | <ul> <li>When using the X1 oscillator, wire as follows in the area enclosed by the broken lines in the above figures to avoid an adverse effect from wiring capacitance.</li> <li>Keep the wiring length as short as possible.</li> <li>Do not cross the wiring with the other signal lines.</li> <li>Do not route the wiring near a signal line through which a high fluctuating current flows.</li> <li>Always make the ground point of the oscillator capacitor the same potential as Vss.</li> <li>Do not ground the capacitor to a ground pattern through which a high current flows.</li> <li>Do not fetch signals from the oscillator.</li> </ul> | p.760               |     |