Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                                   |

| Program Memory Size        | 128KB (128K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 8K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-VFBGA                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1144af1-an1-a |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

Correspondence between the address values and block numbers in the flash memory are shown below.

| Address Value    | Block<br>Number |

|------------------|-----------------|------------------|-----------------|------------------|-----------------|------------------|-----------------|

| 00000H to 007FFH | 00H             | 10000H to 107FFH | 20H             | 20000H to 207FFH | 40H             | 30000H to 307FFH | 60H             |

| 00800H to 00FFFH | 01H             | 10800H to 10FFFH | 21H             | 20800H to 20FFFH | 41H             | 30800H to 30FFFH | 61H             |

| 01000H to 017FFH | 02H             | 11000H to 117FFH | 22H             | 21000H to 217FFH | 42H             | 31000H to 317FFH | 62H             |

| 01800H to 01FFFH | 03H             | 11800H to 11FFFH | 23H             | 21800H to 21FFFH | 43H             | 31800H to 31FFFH | 63H             |

| 02000H to 027FFH | 04H             | 12000H to 127FFH | 24H             | 22000H to 227FFH | 44H             | 32000H to 327FFH | 64H             |

| 02800H to 02FFFH | 05H             | 12800H to 12FFFH | 25H             | 22800H to 22FFFH | 45H             | 32800H to 32FFFH | 65H             |

| 03000H to 037FFH | 06H             | 13000H to 137FFH | 26H             | 23000H to 237FFH | 46H             | 33000H to 337FFH | 66H             |

| 03800H to 03FFFH | 07H             | 13800H to 13FFFH | 27H             | 23800H to 23FFFH | 47H             | 33800H to 33FFFH | 67H             |

| 04000H to 047FFH | 08H             | 14000H to 147FFH | 28H             | 24000H to 247FFH | 48H             | 34000H to 347FFH | 68H             |

| 04800H to 04FFFH | 09H             | 14800H to 14FFFH | 29H             | 24800H to 24FFFH | 49H             | 34800H to 34FFFH | 69H             |

| 05000H to 057FFH | 0AH             | 15000H to 157FFH | 2AH             | 25000H to 257FFH | 4AH             | 35000H to 357FFH | 6AH             |

| 05800H to 05FFFH | 0BH             | 15800H to 15FFFH | 2BH             | 25800H to 25FFFH | 4BH             | 35800H to 35FFFH | 6BH             |

| 06000H to 067FFH | 0CH             | 16000H to 167FFH | 2CH             | 26000H to 267FFH | 4CH             | 36000H to 367FFH | 6CH             |

| 06800H to 06FFFH | 0DH             | 16800H to 16FFFH | 2DH             | 26800H to 26FFFH | 4DH             | 36800H to 36FFFH | 6DH             |

| 07000H to 077FFH | 0EH             | 17000H to 177FFH | 2EH             | 27000H to 277FFH | 4EH             | 37000H to 377FFH | 6EH             |

| 07800H to 07FFFH | 0FH             | 17800H to 17FFFH | 2FH             | 27800H to 27FFFH | 4FH             | 37800H to 37FFFH | 6FH             |

| 08000H to 087FFH | 10H             | 18000H to 187FFH | 30H             | 28000H to 287FFH | 50H             | 38000H to 387FFH | 70H             |

| 08800H to 08FFFH | 11H             | 18800H to 18FFFH | 31H             | 28800H to 28FFFH | 51H             | 38800H to 38FFFH | 71H             |

| 09000H to 097FFH | 12H             | 19000H to 197FFH | 32H             | 29000H to 297FFH | 52H             | 39000H to 397FFH | 72H             |

| 09800H to 09FFFH | 13H             | 19800H to 19FFFH | 33H             | 29800H to 29FFFH | 53H             | 39800H to 39FFFH | 73H             |

| 0A000H to 0A7FFH | 14H             | 1A000H to 1A7FFH | 34H             | 2A000H to 2A7FFH | 54H             | 3A000H to 3A7FFH | 74H             |

| 0A800H to 0AFFFH | 15H             | 1A800H to 1AFFFH | 35H             | 2A800H to 2AFFFH | 55H             | 3A800H to 3AFFFH | 75H             |

| 0B000H to 0B7FFH | 16H             | 1B000H to 1B7FFH | 36H             | 2B000H to 2B7FFH | 56H             | 3B000H to 3B7FFH | 76H             |

| 0B800H to 0BFFFH | 17H             | 1B800H to 1BFFFH | 37H             | 2B800H to 2BFFFH | 57H             | 3B800H to 3BFFFH | 77H             |

| 0C000H to 0C7FFH | 18H             | 1C000H to 1C7FFH | 38H             | 2C000H to 2C7FFH | 58H             | 3C000H to 3C7FFH | 78H             |

| 0C800H to 0CFFFH | 19H             | 1C800H to 1CFFFH | 39H             | 2C800H to 2CFFFH | 59H             | 3C800H to 3CFFFH | 79H             |

| 0D000H to 0D7FFH | 1AH             | 1D000H to 1D7FFH | ЗАН             | 2D000H to 2D7FFH | 5AH             | 3D000H to 3D7FFH | 7AH             |

| 0D800H to 0DFFFH | 1BH             | 1D800H to 1DFFFH | ЗВН             | 2D800H to 2DFFFH | 5BH             | 3D800H to 3DFFFH | 7BH             |

| 0E000H to 0E7FFH | 1CH             | 1E000H to 1E7FFH | ЗСН             | 2E000H to 2E7FFH | 5CH             | 3E000H to 3E7FFH | 7CH             |

| 0E800H to 0EFFFH | 1DH             | 1E800H to 1EFFFH | 3DH             | 2E800H to 2EFFFH | 5DH             | 3E800H to 3EFFFH | 7DH             |

| 0F000H to 0F7FFH | 1EH             | 1F000H to 1F7FFH | 3EH             | 2F000H to 2F7FFH | 5EH             | 3F000H to 3F7FFH | 7EH             |

| 0F800H to 0FFFFH | 1FH             | 1F800H to 1FFFFH | 3FH             | 2F800H to 2FFFFH | 5FH             | 3F800H to 3FFFFH | 7FH             |

| Table 3-1. Correspondence Between | Address Values and Block Numbers in Flash Memory |

|-----------------------------------|--------------------------------------------------|

|-----------------------------------|--------------------------------------------------|

Remark

μPD78F1142, PD78F1142A: Block numbers 00H to 1FH

μPD78F1143, PD78F1143A: Block numbers 00H to 2FH

μPD78F1144, PD78F1144A: Block numbers 00H to 3FH

μPD78F1145, PD78F1145A: Block numbers 00H to 5FH

μPD78F1146, PD78F1146A: Block numbers 00H to 7FH

# 4.3 Registers Controlling Port Function

Port functions are controlled by the following six types of registers.

- Port mode registers (PM0 to PM7, PM12, PM14)

- Port registers (P0 to P7, P12 to P14)

- Pull-up resistor option registers (PU0, PU1, PU3 to PU5, PU7, PU12, PU14)

- Port input mode register (PIM0)

- Port output mode register (POM0)

- A/D port configuration register (ADPC)

# (1) Port mode registers (PM0 to PM7, PM12, PM14)

These registers specify input or output mode for the port in 1-bit units.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

When port pins are used as alternate-function pins, set the port mode register by referencing 4.5 Settings of

Port Mode Register and Output Latch When Using Alternate Function.

## (6) A/D port configuration register (ADPC)

This register switches the P20/ANI0 to P27/ANI7 pins to digital I/O of port or analog input of A/D converter. ADPC can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 10H.

### Figure 4-33. Format of A/D Port Configuration Register (ADPC)

| Address: | F0017H | After reset: | 10H | R/W |

|----------|--------|--------------|-----|-----|

|          |        |              |     |     |

| Symbol | 7 | 6 | 5 | 4     | 3     | 2     | 1     | 0     |

|--------|---|---|---|-------|-------|-------|-------|-------|

| ADPC   | 0 | 0 | 0 | ADPC4 | ADPC3 | ADPC2 | ADPC1 | ADPC0 |

| ADPC4 | ADPC3            | ADPC2 | ADPC1 | ADPC0 |              | Analog input (A)/digital I/O (D) switching |              |              |              |              |              |              |

|-------|------------------|-------|-------|-------|--------------|--------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|

|       |                  |       |       |       | ANI7/<br>P27 | ANI6/<br>P26                               | ANI5/<br>P25 | ANI4/<br>P24 | ANI3/<br>P23 | ANI2/<br>P22 | ANI1/<br>P21 | ANI0/<br>P20 |

| 0     | 0                | 0     | 0     | 0     | А            | А                                          | А            | А            | А            | А            | А            | А            |

| 0     | 0                | 0     | 0     | 1     | А            | А                                          | А            | А            | А            | А            | А            | D            |

| 0     | 0                | 0     | 1     | 0     | А            | А                                          | А            | А            | А            | А            | D            | D            |

| 0     | 0                | 0     | 1     | 1     | А            | А                                          | А            | А            | А            | D            | D            | D            |

| 0     | 0                | 1     | 0     | 0     | А            | А                                          | А            | А            | D            | D            | D            | D            |

| 0     | 0                | 1     | 0     | 1     | А            | А                                          | А            | D            | D            | D            | D            | D            |

| 0     | 0                | 1     | 1     | 0     | А            | А                                          | D            | D            | D            | D            | D            | D            |

| 0     | 0                | 1     | 1     | 1     | А            | D                                          | D            | D            | D            | D            | D            | D            |

| 0     | 1                | 0     | 0     | 0     | D            | D                                          | D            | D            | D            | D            | D            | D            |

| 1     | 0                | 0     | 0     | 0     | D            | D                                          | D            | D            | D            | D            | D            | D            |

|       | Other than above |       |       |       |              |                                            | ted          |              |              |              |              |              |

- Cautions 1. Set the channel used for A/D conversion to the input mode by using port mode registers 2 (PM2).

- 2. Do not set the pin set by ADPC as digital I/O by analog input channel specification register (ADS).

- 3. When using all ANI0/P20 to ANI7/P27 pins as digital I/O (D), the setting can be done by ADPC4 to ADPC0 = either 01000 or 10000.

- 4. P20/ANI0 to P27/ANI7 are set as analog inputs in the order of P27/ANI7, ..., P20/ANI0 by the A/D port configuration register (ADPC). When using P20/ANI0 to P27/ANI7 as analog inputs, start designing from P27/ANI7.

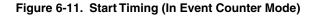

## (b) Start timing in event counter mode

- <1> While TE0n is set to 0, TCR0n holds the initial value.

- <2> Writing 1 to TS0n sets 1 to TE0n.

- <3> As soon as 1 has been written to TS0n and 1 has been set to TE0n, the "TDR0n value" is loaded to TCR0n to start counting.

- <4> After that, the TCR0n value is counted down according to the count clock.

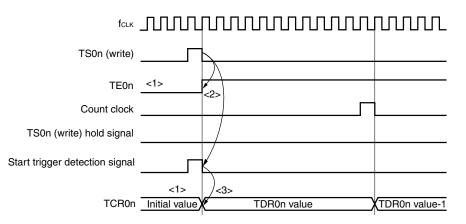

## (c) Start timing in capture mode

- <1> Writing 1 to TS0n sets TE0n = 1

- <2> The write data to TS0n is held until count clock generation.

- <3> TCR0n holds the initial value until count clock generation.

- <4> On generation of count clock, 0000H is loaded to TCR0n and count starts.

Figure 6-12. Start Timing (In Capture Mode)

Caution In the first cycle operation of count clock after writing TS0n, an error at a maximum of one clock is generated since count start delays until count clock has been generated. When the information on count start timing is necessary, an interrupt can be generated at count start by setting MD0n0 = 1.

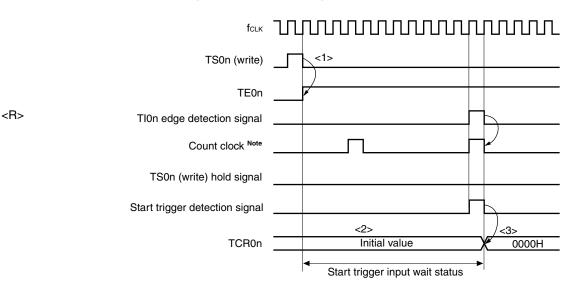

#### (e) Start timing in capture & one-count mode

- <1> Writing 1 to TS0n sets TE0n = 1

- <2> Enters the start trigger input wait status, and TCR0n holds the initial value.

- <3> On start trigger detection, 0000H is loaded to TCR0n and count starts.

Figure 6-14. Start Timing (In Capture & One-count Mode)

- Note When the capture & one-count mode is set, the operation clock (MCK) is selected as count clock (CCS0n = 0).

- Caution An input signal sampling error is generated since operation starts upon start trigger detection (The error is one count clock when TI0k is used).

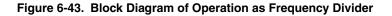

## 6.7.3 Operation as frequency divider (channel 0 only)

The timer array unit can be used as a frequency divider that divides a clock input to the TI00 pin and outputs the result from TO00.

The divided clock frequency output from TO00 can be calculated by the following expression.

- When rising edge/falling edge is selected:

- Divided clock frequency = Input clock frequency/{(Set value of TDR00 + 1) × 2}

- When both edges are selected:

- Divided clock frequency  $\cong$  Input clock frequency/(Set value of TDR00 + 1)

TCR00 operates as a down counter in the interval timer mode.

After the channel start trigger bit (TS00) is set to 1, TCR00 loads the value of TDR00 when the TI00 valid edge is detected. If MD000 of TMR00 = 0 at this time, INTTM00 is not output and TO00 is not toggled. If MD000 of TMR00 = 1, INTTM00 is output and TO00 is toggled.

After that, TCR00 counts down at the valid edge of TI0k. When TCR00 = 0000H, it toggles TO00. At the same time, TCR00 loads the value of TDR00 again, and continues counting.

If detection of both the edges of TI00 is selected, the duty factor error of the input clock affects the divided clock period of the TO00 output.

The period of the TO00 output clock includes a sampling error of one period of the operation clock.

Clock period of TO00 output = Ideal TO00 output clock period  $\pm$  Operation clock period (error)

TDR00 can be rewritten at any time. The new value of TDR00 becomes valid during the next count period.

|                               | Software Operation                                                                                                                                                                                                                                          | Hardware Status                                                                                                                                |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                                                             | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                     |

|                               | Sets the TAU0EN bit of the PER0 register to 1.                                                                                                                                                                                                              | <ul> <li>Power-on status. Each channel stops operating.</li> <li>(Clock supply is started and writing to each register is enabled.)</li> </ul> |

|                               | Sets the TPS0 register.<br>Determines clock frequencies of CK00 and CK01.                                                                                                                                                                                   |                                                                                                                                                |

| Channel<br>default<br>setting | Sets the TMR0n and TMR0m registers of two channels<br>to be used (determines operation mode of channels).<br>An output delay is set to the TDR0n register of the<br>master channel, and a pulse width is set to the TDR0m<br>register of the slave channel. | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                    |

|                               | Sets slave channel.<br>The TOM0m bit of the TOM0 register is set to 1<br>(combination-operation mode).<br>Sets the TOL0m bit.<br>Sets the TO0m bit and determines default level of the<br>TO0m output.                                                      | The TO0m pin goes into Hi-Z output state.<br>The TO0m default setting level is output when the port                                            |

|                               |                                                                                                                                                                                                                                                             | mode register is in output mode and the port register is 0.<br>TOOm does not change because channel stops operating.                           |

|                               | Clears the port register and port mode register to 0.                                                                                                                                                                                                       | The TO0m pin outputs the TO0m set level.                                                                                                       |

# Figure 6-64. Operation Procedure of One-Shot Pulse Output Function (1/2)

**Remark** n = 0, 2, 4

m = n + 1

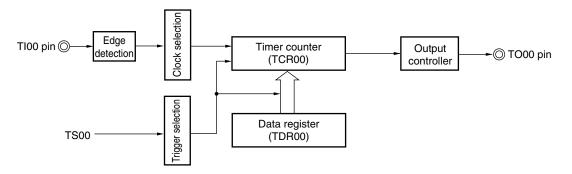

# (12) Internal equivalent circuit

The equivalent circuit of the analog input block is shown below.

# Figure 10-28. Internal Equivalent Circuit of ANIn Pin

Table 10-6. Resistance and Capacitance Values of Equivalent Circuit (Reference Values)

| AVREF                                 | R1     | C1   | C2   |

|---------------------------------------|--------|------|------|

| $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 8.1 kΩ | 8 pF | 5 pF |

| $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 31 kΩ  | 8 pF | 5 pF |

| $2.3~V \leq V_{\text{DD}} < 2.7~V$    | 381 kΩ | 8 pF | 5 pF |

**Remarks 1.** The resistance and capacitance values shown in Table 10-6 are not guaranteed values. **2.** n = 0 to 7

## <R> (13) Starting the A/D converter

Start the A/D converter after the AVREF voltage stabilize.

# (9) Serial channel start register m (SSm)

SSm is a trigger register that is used to enable starting communication/count by each channel. When 1 is written a bit of this register (SSmn), the corresponding bit (SEmn) of serial channel enable status register m (SEm) is set to 1. Because SSmn is a trigger bit, it is cleared immediately when SEmn = 1. SSm can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of SSm can be set with an 1-bit or 8-bit memory manipulation instruction with SSmL. Reset signal generation clears this register to 0000H.

## Figure 11-12. Format of Serial Channel Start Register m (SSm)

| Address: F01 | 122H, F0 | )123H   | After reset: 0000H                                                                                    |          |      | R/W |   |   |   |   |   |   |      |      |      |      |

|--------------|----------|---------|-------------------------------------------------------------------------------------------------------|----------|------|-----|---|---|---|---|---|---|------|------|------|------|

| Symbol       | 15       | 14      | 13                                                                                                    | 12       | 11   | 10  | 9 | 8 | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

| SS0          | 0        | 0       | 0                                                                                                     | 0        | 0    | 0   | 0 | 0 | 0 | 0 | 0 | 0 | SS03 | SS02 | SS01 | SS00 |

|              |          |         |                                                                                                       |          |      |     |   |   |   |   |   |   |      |      |      |      |

| Address: F01 | 162H, F0 | )163H   | After ı                                                                                               | reset: 0 | 000H | R/W |   |   |   |   |   |   |      |      |      |      |

| Symbol       | 15       | 14      | 13                                                                                                    | 12       | 11   | 10  | 9 | 8 | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

| SS1          | 0        | 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 SS13 SS12 0 0                                                               |          |      |     |   |   | 0 |   |   |   |      |      |      |      |

|              |          |         |                                                                                                       |          |      |     |   |   |   |   |   |   |      |      |      |      |

|              | SSmn     |         | Operation start trigger of channel n                                                                  |          |      |     |   |   |   |   |   |   |      |      |      |      |

|              | 0        | No trig | No trigger operation                                                                                  |          |      |     |   |   |   |   |   |   |      |      |      |      |

|              | 1        | Sets S  | ets SEmn to 1 and enters the communication wait status (if a communication operation is already under |          |      |     |   |   |   |   |   |   |      |      |      |      |

execution, the operation is stopped and the start condition is awaited).

#### Caution Be sure to clear bits 15 to 4 of SS0, and bits 15 to 4, 1 and 0 of SS1 to "0".

**Remarks 1.** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), mn = 00 to 03, 12, 13

2. When the SSm register is read, 0000H is always read.

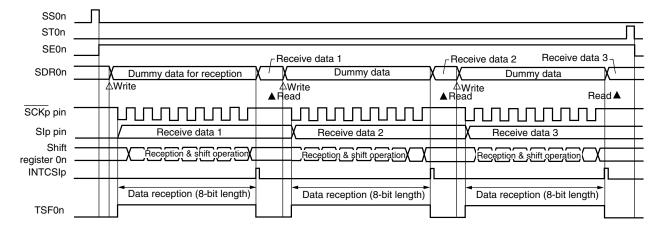

# (3) Processing flow (in single-reception mode)

**Remark** n: Channel number (n = 0, 2), p: CSI number (p = 00, 10)

#### (2) Operation procedure

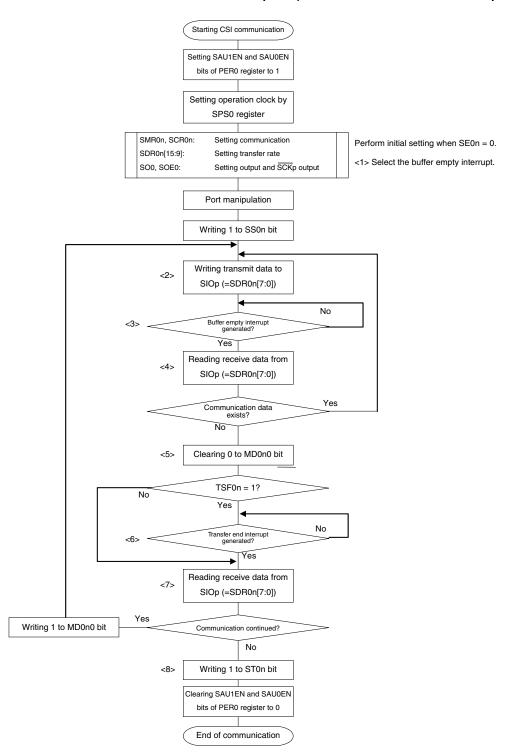

# Starting initial setting Release the serial array unit from the Setting PER0 register reset status and start clock supply. Set the operation clock. Setting SPS0 register Setting SMR0n register Set an operation mode, etc. Set a communication format. Setting SCR0n register Set a transfer baud rate. Setting SDR0n register Manipulate the SO0n and CKO0n bits Setting SO0 register and set an initial output level. Set the SOE0n bit to 1 and enable data Changing setting of SOE0 register output of the target channel. Enable data output and clock output of the target channel by setting a port Setting port register and a port mode register. SE0n = 1 when the SS0n bit of the target Writing to SS0 register channel is set to 1. Set transmit data to the SIOp register (bits 7 to 0 of the SDR0n register) and Starting communication start communication.

#### Figure 11-41. Initial Setting Procedure for Master Transmission/Reception

# Caution After setting the PER0 register to 1, be sure to set the SPS0 register after 4 or more clocks have elapsed.

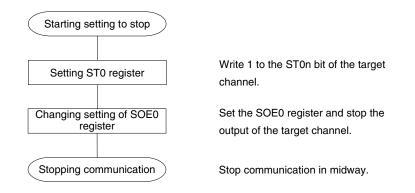

#### Figure 11-42. Procedure for Stopping Master Transmission/Reception

**Remark** Even after communication is stopped, the pin level is retained. To resume the operation, re-set the SO0 register (see Figure 11-43 Procedure for Resuming Master Transmission/Reception).

# Caution After setting the PER0 register to 1, be sure to set the SPS0 register after 4 or more clocks have elapsed.

**Remark** <1> to <8> in the figure correspond to <1> to <8> in Figure 11-46 Timing Chart of Master Transmission/Reception (in Continuous Transmission/Reception Mode).

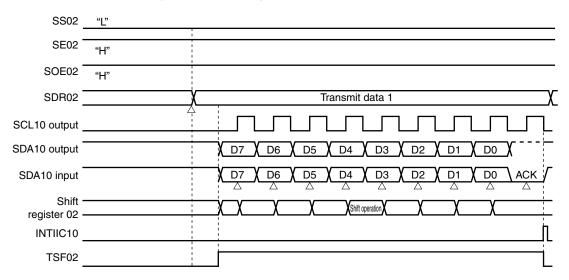

# (1) Register setting

| (a)       Serial output register 0 (SO0)       Do not manipulate this register during data transmission/reception.         SOO       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SOO       0       0       0       0       1       0/1***       1       ccccce       0       0       0       1       0/1***       1         (b)       Serial output reable register 0 (SOEO)       Do not manipulate this register during data transmission/reception.       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SOE0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       1       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 </th <th>(-)</th> <th></th>                                                                                                                                              | (-)                     |        |        |                        |            |        |                     |        |         |         |         |         |            |            |                     |         |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|--------|------------------------|------------|--------|---------------------|--------|---------|---------|---------|---------|------------|------------|---------------------|---------|------------|

| $SOO = \begin{bmatrix} 15 & 14 & 13 & 12 & 11 & 10 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 \\ \hline 0 & 0 & 0 & 0 & 1 & 0/1^{\text{tess}} & 1 & x & 0 & 0 & 0 & 0 & 0 & 1 & 0/1^{\text{tess}} & 1 \\ \hline x & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (a)                     | Serial | outpu  | ıt regi                | ster 0     | (SO0   | ) [                 | Do no  | t mani  | pulate  | e this  | regist  | er dur     | ing da     | ata                 |         |            |

| SO0  0  0  0  0  1  0  1  0  0  1  0  0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |        |        |                        |            |        | t                   | ransn  | nissio  | n/rece  | eption  |         |            |            |                     |         |            |

| 0         0         0         1         0/1****         1         ×         0         0         0         1         0/1****         1           (b)         Serial output enable register 0 (SOE0)         Do not manipulate this register during data transmission/reception.           SOE0         15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           SOE0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                             |                         | 15     | 14     | 13                     | 12         | 11     | 10                  | 9      | 8       | 7       | 6       | 5       | 4          | 3          | 2                   | 1       | 0          |

| (b) Serial output enable register 0 (SOE0) Do not manipulate this register during data transmission/reception.<br>15 14 13 12 11 10 9 8 7 6 5 4 3 2 1<br>SOE0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SO0                     |        |        |                        |            |        | CKO02               |        | CKO00   |         |         |         |            |            | SO02                |         | SO00       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         | 0      | 0      | 0                      | 0          | 1      | 0/1 <sup>Note</sup> | 1      | ×       | 0       | 0       | 0       | 0          | 1          | 0/1 <sup>Note</sup> | 1       | ×          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |        |        |                        |            |        |                     |        |         |         |         |         |            |            |                     |         |            |

| 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SOE0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <t< td=""><td>(b)</td><td>Serial</td><td>outpu</td><td>it ena</td><td>ble reg</td><td>gister</td><td>0 (SO</td><td>E0)</td><td>. Do i</td><td>not m</td><td>anipu</td><td>late th</td><td>is reg</td><td>ister o</td><td>during</td><td>data</td><td></td></t<>                                                                                                                                                                         | (b)                     | Serial | outpu  | it ena                 | ble reg    | gister | 0 (SO               | E0)    | . Do i  | not m   | anipu   | late th | is reg     | ister o    | during              | data    |            |

| SOE0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                 | transmission/reception. |        |        |                        |            |        |                     |        |         |         |         |         |            |            |                     |         |            |

| 0         0         0         0         0         0         0         0         0         0         0         0         0         1         0           (c)         Serial channel start register 0 (SS0)         Do not manipulate this register during data transmission/reception.           SS0         15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           SS0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                  |                         | 15     | 14     | 13                     | 12         | 11     | 10                  | 9      | 8       | 7       | 6       | 5       | 4          | 3          | 2                   | 1       | 0          |

| 0       0       0       0       0       0       0       0       0       0       0       0       0       0       1       0         (c)       Serial channel start register 0 (SS0)       Do not manipulate this register during data transmission/reception.       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SS0       0       0       0       0       0       0       0       0       0       0       2       1         (d)       Serial mode register 02 (SMR02)       Do not manipulate this register during data transmission/reception.       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SMR02       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SMR02       CKS02       CCS02       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <td< td=""><td>SOE0</td><td></td><td></td><td></td><td></td><td></td><td></td><td>-</td><td></td><td></td><td></td><td></td><td></td><td></td><td>SOE02</td><td></td><td>SOE00</td></td<>                                                                                                                                                  | SOE0                    |        |        |                        |            |        |                     | -      |         |         |         |         |            |            | SOE02               |         | SOE00      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         | 0      | 0      | 0                      | 0          | 0      | 0                   | 0      | 0       | 0       | 0       | 0       | 0          | 0          |                     |         | ×          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |        |        |                        |            |        |                     |        |         |         |         |         |            |            | <u> </u>            |         |            |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (c)                     | Serial | chanr  | nel sta                | art reg    | ister  | 0 (SS0              | )      | Do no   | t man   | ipulat  | e this  | regist     | er du      | ring d              | ata     |            |

| 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SS0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td>•</td><td>-</td><td></td><td></td><td>-</td><td></td><td>-</td><td></td><td>•</td><td></td><td></td></td<>                                                                                                                                                                                                                                                          |                         |        |        |                        |            |        | •                   | -      |         |         | -       |         | -          |            | •                   |         |            |

| 0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         | 15     | 14     | 13                     | 12         | 11     | 10                  |        |         |         |         | -       |            | 3          | 2                   | 1       | 0          |

| 0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                    | SS0                     |        |        |                        |            |        |                     |        |         |         |         |         |            | SS03       | 5502                | SS01    | SS00       |

| transmission/reception.         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SMR02       CKS02       CCS02       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <td>000</td> <td>0</td> <td></td> <td></td> <td></td> <td>×</td>                                                                                                                                                                                                                                      | 000                     | 0      | 0      | 0                      | 0          | 0      | 0                   | 0      | 0       | 0       | 0       | 0       | 0          |            |                     |         | ×          |

| transmission/reception.         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SMR02       CKS02       CCS02       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <td></td>                                                                                                                                                                                                                                                      |                         |        |        |                        |            |        |                     |        |         |         |         |         |            |            |                     |         |            |

| 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SMR02       CKS02       CCS02       0       0       0       0       0       0       0       0       0       1       0       0       0       0       1       0       0       0       1       0       0       0       1       0       0       0       1       0       0       0       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                | (d)                     | Serial | mode   | regis                  | ter 02     | (SMF   | R02)                | Do     | not m   | anipu   | late th | nis reg | ister o    | during     | g data              |         |            |

| 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SMR02       CKS02       CCS02       0       0       0       0       0       0       0       0       0       1       0       0       0       0       1       0       0       0       1       0       0       0       1       0       0       0       1       0       0       0       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                | . ,                     |        |        | •                      |            |        | -                   |        |         | -       |         | -       |            | -          |                     |         |            |

| 0/1       0       0       0       0       0       0       0       1       0       1       0         (e)       Serial communication operation setting register 02 (SCR02)       Do not manipulate the register, except the T. RXE02 bits, during data transmission/reception         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SCR02       Image: Txeo2       DAPO2       CKP02       0       EOC02       PTC021       PTC020       DIR02       0       SLC021       SLC021       SLC021       SLC021       Image: SLC021       I                                                                                                           |                         | 15     | 14     | 13                     | 12         | 11     | 10                  | 9      | 8       | 7       | 6       | 5       | 4          | 3          | 2                   | 1       | 0          |

| 0/1       0       0       0       0       0       0       0       1       0       1       0         (e)       Serial communication operation setting register 02 (SCR02)       Do not manipulate the register, except the T. RXE02 bits, during data transmission/reception         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SCR02       IXE02       DAP02       CKP02       0       EOC02       PTC021       PTC020       DIR02       0       SLC021       SLC020       0       DLS022       DLS023       DLS023 <td>SMB02</td> <td>01/000</td> <td>00000</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>07000</td> <td></td> <td>010000</td> <td>1</td> <td></td> <td></td> <td></td> <td>MDaad</td> <td>MD000</td> | SMB02                   | 01/000 | 00000  |                        |            |        |                     |        | 07000   |         | 010000  | 1       |            |            |                     | MDaad   | MD000      |

| (e) Serial communication operation setting register 02 (SCR02) Do not manipulate the register, except the T. RXE02 bits, during data transmission/reception of the register of the T. RXE02 bits, during data register 02 (SDR02) [PTC021 PTC020 DIR02 0 SLC021 SLC020 0 DLS022 DLS021 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51011102                |        |        | 0                      | 0          | 0      | 0                   | 0      |         | 0       |         |         | 0          | 0          |                     |         | MD020<br>0 |

| register, except the T.<br>RXE02 bits, during da<br>transmission/reception<br>SCR02 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1<br>TXE02 RXE02 DAP02 CKP02 0 EOC02 PTC021 PTC020 DIR02 0 SLC021 SLC020 0 DLS022 DLS021<br>1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 1<br>(f) Serial data register 02 (SDR02) (lower 8 bits: SIO10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         | L      |        |                        |            |        |                     |        |         |         |         |         |            |            |                     |         |            |

| register, except the T.<br>RXE02 bits, during da<br>transmission/reception<br>SCR02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (e)                     | Serial | comn   | nunica                 | ation c    | perat  | tion se             | ettina | reaist  | er 02 ( | SCRO    | )2)     | Do n       | ot ma      | nipula              | ate the | e bits     |

| RXE02 bits, during data         RXE02 bits, during data         Transmission/reception         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         SCR02       TXE02       RXE02       DAP02       CKP02       0       EOC02       PTC021       PTC020       DIR02       0       SLC021       SLC020       0       DLS022       DLS021         SCR02       TXE02       RXE02       DAP02       CKP02       0       EOC02       PTC021       PTC020       DIR02       0       SLC021       SLC021       DLS022       DLS021       DLS022       DLS021       1       1       1         (f) Serial data register 02 (SDR02) (lower 8 bits: SIO10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (-)                     |        |        |                        |            |        |                     | 5      | 5       |         |         | ,       |            |            | -                   |         |            |