Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                                   |

| Program Memory Size        | 192KB (192K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 10K × 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-VFBGA                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1145af1-an1-a |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **CHAPTER 2 PIN FUNCTIONS**

## 2.1 Pin Function List

There are three types of pin I/O buffer power supplies: AVREF, EVDD, and VDD. The relationship between these power supplies and the pins is shown below.

| Power Supply    | Corresponding Pins                                                                                    |

|-----------------|-------------------------------------------------------------------------------------------------------|

| AVREF           | P20 to P27                                                                                            |

| EVDD            | <ul> <li>Port pins other than P20 to P27 and P121 to P124</li> <li>RESET pin and FLMD0 pin</li> </ul> |

| V <sub>DD</sub> | P121 to P124     Pins other than port pins (except RESET pin and FLMD0 pin )                          |

| Table 2-1. | Pin I/O | Buffer | Power | Supplies |

|------------|---------|--------|-------|----------|

|------------|---------|--------|-------|----------|

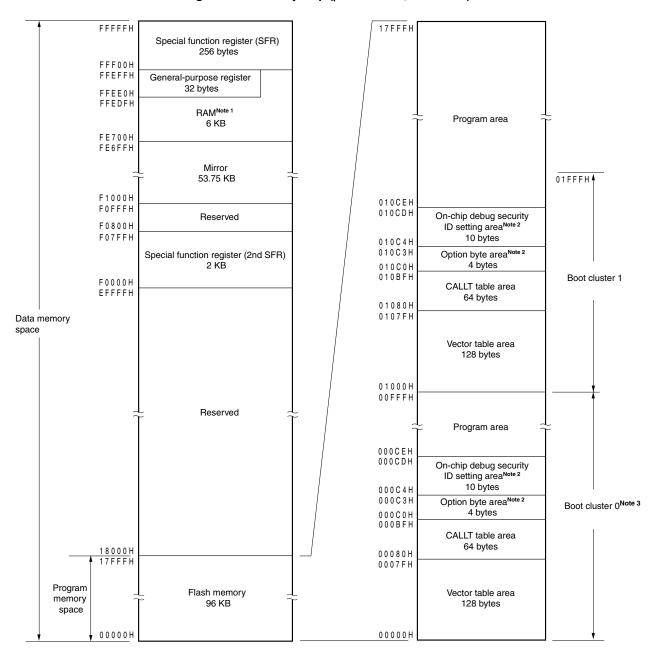

#### Figure 3-2. Memory Map (µPD78F1143, 78F1143A)

- 2. When boot swap is not used: Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

- When boot swap is used:Set the option bytes to 000C0H to 000C3H and 010C0H to 010C3H, and<br/>the on-chip debug security IDs to 000C4H to 000CDH and 010C4H to<br/>010CDH.

- 3. Writing boot cluster 0 can be prohibited depending on the setting of security (see 23.7 Security Setting).

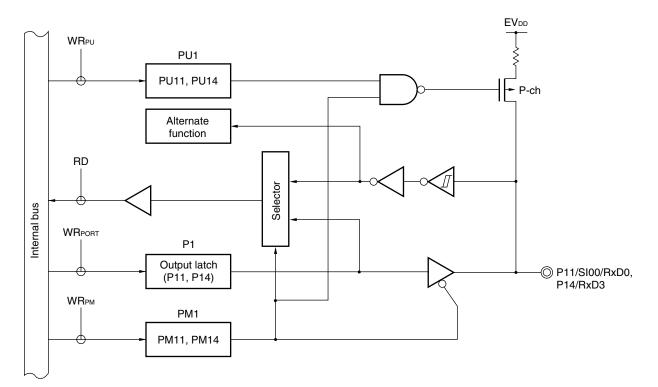

Figure 4-8. Block Diagram of P11 and P14

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

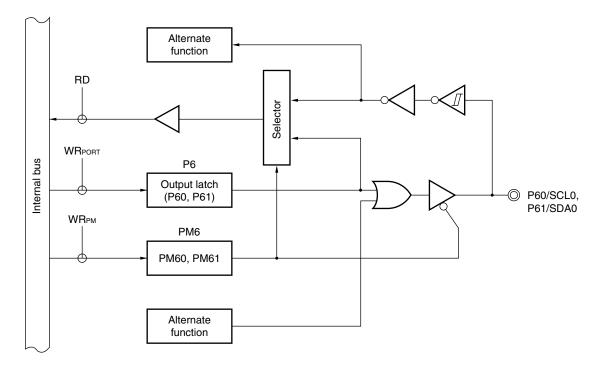

## 4.2.7 Port 6

Port 6 is a 4-bit I/O port with an output latch. Port 6 can be set to the input mode or output mode in 1-bit units using port mode register 6 (PM6).

The output of the P60 to P63 pins is N-ch open-drain output (6 V tolerance).

This port can also be used for serial interface data I/O and clock I/O.

Reset signal generation sets port 6 to input mode.

Figures 4-20 and 4-21 show block diagrams of port 6.

# Caution When using P60/SCL0 or P61/SDA0 as a general-purpose port, stop the operation of serial interface IIC0.

Figure 4-20. Block Diagram of P60 and P61

- P6: Port register 6

- PM6: Port mode register 6

- RD: Read signal

- WR××: Write signal

#### 6.7.5 Operation as input signal high-/low-level width measurement

By starting counting at one edge of TI0k and capturing the number of counts at another edge, the signal width (high-level width/low-level width) of TI0k can be measured. The signal width of TI0k can be calculated by the following expression.

Signal width of TI0k input = Period of count clock  $\times$  ((10000H  $\times$  TSRn: OVF) + (Capture value of TDR0n + 1))

## Caution The Tl0k pin input is sampled using the operating clock selected with the CKS0n bit of the TMR0n register, so an error equal to the number of operating clocks occurs.

TCR0n operates as an up counter in the capture & one-count mode.

When the channel start trigger (TS0n) is set to 1, TE0n is set to 1 and the TI0k pin start edge detection wait status is set.

When the TI0k start valid edge (rising edge of TI0k when the high-level width is to be measured) is detected, the counter counts up in synchronization with the count clock. When the valid capture edge (falling edge of TI0k when the high-level width is to be measured) is detected later, the count value is transferred to TDR0n and, at the same time, INTTM0n is output. If the counter overflows at this time, the OVF bit of the TSR0n register is set to 1. If the counter does not overflow, the OVF bit is cleared. TCR0n stops at the value "value transferred to TDR0n + 1", and the TI0k pin start edge detection wait status is set. After that, the above operation is repeated.

As soon as the count value has been captured to the TDR0n register, the OVF bit of the TSR0n register is updated depending on whether the counter overflows during the measurement period. Therefore, the overflow status of the captured value can be checked.

If the counter reaches a full count for two or more periods, it is judged to be an overflow occurrence, and the OVF bit of the TSR0n register is set to 1. However, the OVF bit is configured as an integral flag, and the correct interval value cannot be measured if an overflow occurs more than once.

Whether the high-level width or low-level width of the TI0k pin is to be measured can be selected by using the CIS0n1 and CIS0n0 bits of the TMR0n register.

Because this function is used to measure the signal width of the TI0k pin input, TS0n cannot be set to 1 while TE0n is 1.

CIS0n1, CIS0n0 of TMR0n = 10B: Low-level width is measured. CIS0n1, CIS0n0 of TMR0n = 11B: High-level width is measured.

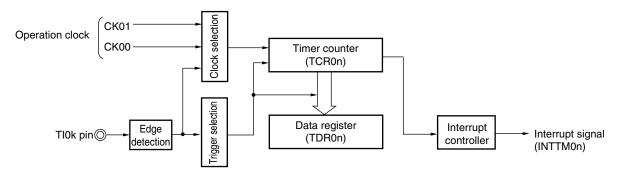

#### Figure 6-51. Block Diagram of Operation as Input Signal High-/Low-Level Width Measurement

**Remark** n = 0 to 7, k = 0 to 6

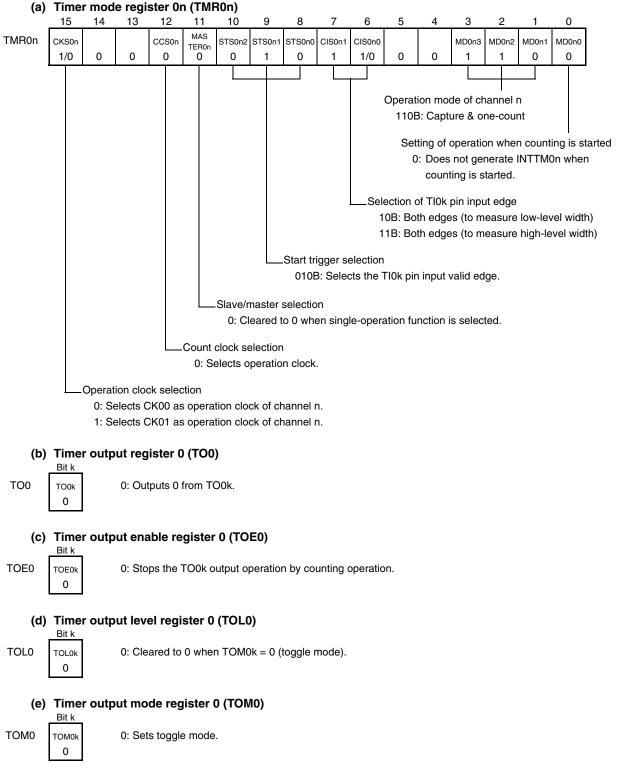

#### Figure 6-53. Example of Set Contents of Registers to Measure Input Signal High-/Low-Level Width

#### Correction example <2>

Example of correcting from 32767.4 Hz to 32768 Hz (32767.4 Hz + 18.3 ppm)

[Measuring the oscillation frequency]

The oscillation frequency<sup>Note</sup> of each product is measured by outputting about 32 kHz from the RTCCL pin or outputting about 1 Hz from the RTC1HZ pin when the watch error correction register is set to its initial value (00H).

**Note** See **7.4.5 1 Hz output of real-time counter** for the setting procedure of outputting about 1 Hz from the RTC1HZ pin, and **7.4.6 32.768 kHz output of real-time counter** for the setting procedure of outputting about 32 kHz from the RTCCL pin.

[Calculating the correction value]

(When the output frequency from the RTCCL pin is 0.9999817 Hz) Oscillation frequency =  $32768 \times 0.9999817 \approx 32767.4$  Hz Assume the target frequency to be 32768 Hz (32767.4 Hz + 18.3 ppm) and DEV to be 1. The expression for calculating the correction value when DEV is 1 is applied.

Correction value = Number of correction counts in 1 minute

| = (Oscillation frequency $\div$ Target frequency – 1) $\times$ 32768 $\times$ 60 |

|----------------------------------------------------------------------------------|

| = $(32767.4 \div 32768 - 1) \times 32768 \times 60$                              |

| = -36                                                                            |

[Calculating the values to be set to (F6 to F0)]

(When the correction value is -36)

If the correction value is 0 or less (when speeding up), assume F6 to be 1. Calculate (F5, F4, F3, F2, F1, F0) from the correction value.

| – {(/F5, /F4, /F3, /F2, /F1, /F0) + 1} × 2 | = -36                |

|--------------------------------------------|----------------------|

| (/F5, /F4, /F3, /F2, /F1, /F0)             | = 17                 |

| (/F5, /F4, /F3, /F2, /F1, /F0)             | = (0, 1, 0, 0, 0, 1) |

| (F5, F4, F3, F2, F1, F0)                   | = (1, 0, 1, 1, 1, 0) |

Consequently, when correcting from 32767.4 Hz to 32768 Hz (32767.4 Hz + 18.3 ppm), setting the correction register such that DEV is 1 and the correction value is -36 (bits 6 to 0 of SUBCUD: 1101110) results in 32768 Hz (0 ppm).

Figure 7-28 shows the operation when (DEV, F6, F5, F4, F3, F2, F1, F0) is (1, 1, 1, 0, 1, 1, 1, 0).

## **CHAPTER 8 WATCHDOG TIMER**

## 8.1 Functions of Watchdog Timer

The watchdog timer operates on the internal low-speed oscillation clock.

The watchdog timer is used to detect an inadvertent program loop. If a program loop is detected, an internal reset signal is generated.

Program loop is detected in the following cases.

- If the watchdog timer counter overflows

- If a 1-bit manipulation instruction is executed on the watchdog timer enable register (WDTE)

- If data other than "ACH" is written to WDTE

- If data is written to WDTE during a window close period

When a reset occurs due to the watchdog timer, bit 4 (WDRF) of the reset control flag register (RESF) is set to 1. For details of RESF, see **CHAPTER 18 RESET FUNCTION**.

When 75% of the overflow time is reached, an interval interrupt can be generated.

Cautions 4. The operation of the watchdog timer in the HALT and STOP modes differs as follows depending on the set value of bit 0 (WDSTBYON) of the option byte (000C0H).

|              | WDSTBYON = 0                    | WDSTBYON = 1                        |

|--------------|---------------------------------|-------------------------------------|

| In HALT mode | Watchdog timer operation stops. | Watchdog timer operation continues. |

| In STOP mode |                                 |                                     |

If WDSTBYON = 0, the watchdog timer resumes counting after the HALT or STOP mode is released. At this time, the counter is cleared to 0 and counting starts.

When operating with the X1 oscillation clock after releasing the STOP mode, the CPU starts operating after the oscillation stabilization time has elapsed.

Therefore, if the period between the STOP mode release and the watchdog timer overflow is short, an overflow occurs during the oscillation stabilization time, causing a reset.

Consequently, set the overflow time in consideration of the oscillation stabilization time when operating with the X1 oscillation clock and when the watchdog timer is to be cleared after the STOP mode release by an interval interrupt.

5. The watchdog timer continues its operation during self-programming of the flash memory and EEPROM emulation. During processing, the interrupt acknowledge time is delayed. Set the overflow time and window size taking this delay into consideration.

#### 8.4.2 Setting overflow time of watchdog timer

Set the overflow time of the watchdog timer by using bits 3 to 1 (WDCS2 to WDCS0) of the option byte (000C0H).

If an overflow occurs, an internal reset signal is generated. The present count is cleared and the watchdog timer starts counting again by writing "ACH" to WDTE during the window open period before the overflow time.

The following overflow time is set.

| WDCS2 | WDCS1 | WDCS0 | Overflow Time of Watchdog Timer   |

|-------|-------|-------|-----------------------------------|

| 0     | 0     | 0     | 2 <sup>¹0</sup> /fi∟ (3.88 ms)    |

| 0     | 0     | 1     | 2 <sup>11</sup> /fiL (7.76 ms)    |

| 0     | 1     | 0     | 2 <sup>12</sup> /f⊫ (15.52 ms)    |

| 0     | 1     | 1     | 2 <sup>¹3</sup> /fi∟ (31.03 ms)   |

| 1     | 0     | 0     | 2 <sup>¹5</sup> /f∟ (124.12 ms)   |

| 1     | 0     | 1     | 2 <sup>17</sup> /f⊫ (496.48 ms)   |

| 1     | 1     | 0     | 2 <sup>18</sup> /fi∟ (992.97 ms)  |

| 1     | 1     | 1     | 2 <sup>20</sup> /fiL (3971.88 ms) |

Table 8-3. Setting of Overflow Time of Watchdog Timer

Caution The watchdog timer continues its operation during self-programming of the flash memory and EEPROM emulation. During processing, the interrupt acknowledge time is delayed. Set the overflow time and window size taking this delay into consideration.

Remarks 1. fil: Internal low-speed oscillation clock frequency

**2.** ( ): fi∟ = 264 kHz (MAX.)

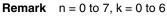

## (12) Internal equivalent circuit

The equivalent circuit of the analog input block is shown below.

## Figure 10-28. Internal Equivalent Circuit of ANIn Pin

Table 10-6. Resistance and Capacitance Values of Equivalent Circuit (Reference Values)

| AVREF                                 | R1     | C1   | C2   |

|---------------------------------------|--------|------|------|

| $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 8.1 kΩ | 8 pF | 5 pF |

| $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 31 kΩ  | 8 pF | 5 pF |

| $2.3~V \leq V_{\text{DD}} < 2.7~V$    | 381 kΩ | 8 pF | 5 pF |

**Remarks 1.** The resistance and capacitance values shown in Table 10-6 are not guaranteed values. **2.** n = 0 to 7

### <R> (13) Starting the A/D converter

Start the A/D converter after the AVREF voltage stabilize.

## (9) Serial channel start register m (SSm)

SSm is a trigger register that is used to enable starting communication/count by each channel. When 1 is written a bit of this register (SSmn), the corresponding bit (SEmn) of serial channel enable status register m (SEm) is set to 1. Because SSmn is a trigger bit, it is cleared immediately when SEmn = 1. SSm can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of SSm can be set with an 1-bit or 8-bit memory manipulation instruction with SSmL. Reset signal generation clears this register to 0000H.

### Figure 11-12. Format of Serial Channel Start Register m (SSm)

| Address: F01 | 122H, F0 | )123H   | After I                                                                                                | reset: 0 | 000H | R/W |       |          |           |          |        |   |      |      |      |      |

|--------------|----------|---------|--------------------------------------------------------------------------------------------------------|----------|------|-----|-------|----------|-----------|----------|--------|---|------|------|------|------|

| Symbol       | 15       | 14      | 13                                                                                                     | 12       | 11   | 10  | 9     | 8        | 7         | 6        | 5      | 4 | 3    | 2    | 1    | 0    |

| SS0          | 0        | 0       | 0                                                                                                      | 0        | 0    | 0   | 0     | 0        | 0         | 0        | 0      | 0 | SS03 | SS02 | SS01 | SS00 |

|              |          |         |                                                                                                        |          |      |     |       |          |           |          |        |   |      |      |      |      |

| Address: F01 | 162H, F0 | )163H   | After ı                                                                                                | reset: 0 | 000H | R/W |       |          |           |          |        |   |      |      |      |      |

| Symbol       | 15       | 14      | 13                                                                                                     | 12       | 11   | 10  | 9     | 8        | 7         | 6        | 5      | 4 | 3    | 2    | 1    | 0    |

| SS1          | 0        | 0       | 0                                                                                                      | 0        | 0    | 0   | 0     | 0        | 0         | 0        | 0      | 0 | SS13 | SS12 | 0    | 0    |

|              |          |         |                                                                                                        |          |      |     |       |          |           |          |        |   |      |      |      |      |

|              | SSmn     |         |                                                                                                        |          |      |     | Opera | tion sta | rt trigge | r of cha | nnel n |   |      |      |      |      |

|              | 0        | No trig | No trigger operation                                                                                   |          |      |     |       |          |           |          |        |   |      |      |      |      |

|              | 1        | Sets S  | Sets SEmn to 1 and enters the communication wait status (if a communication operation is already under |          |      |     |       |          |           |          |        |   |      |      |      |      |

execution, the operation is stopped and the start condition is awaited).

#### Caution Be sure to clear bits 15 to 4 of SS0, and bits 15 to 4, 1 and 0 of SS1 to "0".

**Remarks 1.** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), mn = 00 to 03, 12, 13

2. When the SSm register is read, 0000H is always read.

#### 11.4.2 Stopping the operation by channels

The stopping of the operation by channels is set using each of the following registers.

Figure 11-23. Each Register Setting When Stopping the Operation by Channels (1/2)

(a) Serial Channel Enable Status Register m (SEm) ... This register indicates whether data transmission/reception operation of each channel is enabled or stopped.

|     | 15                                                                                                                                                                                                                    | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3           | 2           | 1                  | 0           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|---|---|---|---|---|---|-------------|-------------|--------------------|-------------|

| SE0 | 0                                                                                                                                                                                                                     | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | SE03<br>0/1 | SE02<br>0/1 | SE01<br><b>0/1</b> | SE00<br>0/1 |

|     | 0: Operation stops                                                                                                                                                                                                    |    |    |    |    |    |   |   |   |   |   |   |             |             |                    |             |

|     | * The SE0 register is a read-only status register, whose operation is stopped by using the ST0 register.<br>With a channel whose operation is stopped, the value of CKO0n of the SO0 register can be set by software. |    |    |    |    |    |   |   |   |   |   |   |             |             |                    |             |

|     | 15                                                                                                                                                                                                                    | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3           | 2           | 1                  | 0           |

| SE1 | 0                                                                                                                                                                                                                     | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | SE13<br>0/1 | SE12<br>0/1 | 0                  | 0           |

|     | 0: Operation stops                                                                                                                                                                                                    |    |    |    |    |    |   |   |   |   |   |   |             |             |                    |             |

\* The SE1 register is a read-only status register, whose operation is stopped by using the ST1 register.

(b) Serial channel stop register m (STm) ... This register is a trigger register that is used to enable stopping communication/count by each channel.

|     | 15                                                        | 14      | 13        | 12        | 11          | 10      | 9       | 8       | 7      | 6  | 5 | 4 | 3                  | 2                  | 1    | 0    |

|-----|-----------------------------------------------------------|---------|-----------|-----------|-------------|---------|---------|---------|--------|----|---|---|--------------------|--------------------|------|------|

| ST0 |                                                           |         |           |           |             |         |         |         |        |    |   |   | ST03               | ST02               | ST01 | ST00 |

|     | 0                                                         | 0       | 0         | 0         | 0           | 0       | 0       | 0       | 0      | 0  | 0 | 0 | 0/1                | 0/1                | 0/1  | 0/1  |

|     | 1: Clears SE0n to 0 and stops the communication operation |         |           |           |             |         |         |         |        |    |   |   |                    |                    |      |      |

|     | * D                                                       | 0.70    |           |           |             |         |         |         | 050    | •  |   |   |                    |                    |      |      |

|     | " Beca                                                    | use ST0 | n is a tr | igger bit | , it is cle | ared im | mediate | ly when | SE0n = | 0. |   |   |                    |                    |      |      |

|     | 15                                                        | 14      | 13        | 12        | 11          | 10      | 9       | 8       | 7      | 6  | 5 | 4 | 3                  | 2                  | 1    | 0    |

| ST1 | 0                                                         | 0       | 0         | 0         | 0           | 0       | 0       | 0       | 0      | 0  | 0 | 0 | sт13<br><b>0/1</b> | ST12<br><b>0/1</b> | 0    | 0    |

|     | 1: Clears SE1n to 0 and stops the communication operation |         |           |           |             |         |         |         |        |    |   |   |                    |                    |      |      |

\* Because ST1n is a trigger bit, it is cleared immediately when SE1n = 0.

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3)

: Setting disabled (fixed by hardware), 0/1: Set to 0 or 1 depending on the usage of the user

## 11.6.4 LIN reception

Of UART reception, UART3 supports LIN communication. For LIN reception, channel 3 of unit 1 (SAU1) is used.

| UART                         | UART0                                                                                                                                                                                               | UART1                                                | UART3                      |  |  |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------|--|--|--|--|--|--|--|

| Support of LIN communication | Not supported                                                                                                                                                                                       | Supported                                            |                            |  |  |  |  |  |  |  |

| Target channel               | – – Channel 0 of SAU1                                                                                                                                                                               |                                                      |                            |  |  |  |  |  |  |  |

| Pins used                    | – – RxD3                                                                                                                                                                                            |                                                      |                            |  |  |  |  |  |  |  |

| Interrupt                    | _                                                                                                                                                                                                   | -                                                    | INTSR3                     |  |  |  |  |  |  |  |

|                              | Transfer end interrupt only (Set                                                                                                                                                                    | ting the buffer empty interrupt is p                 | prohibited.)               |  |  |  |  |  |  |  |

| Error interrupt              | -                                                                                                                                                                                                   | -                                                    | INTSRE3                    |  |  |  |  |  |  |  |

| Error detection flag         | <ul> <li>Framing error detection flag (FEF13)</li> <li>Parity error detection flag (PEF13)</li> <li>Overrun error detection flag (OVF13)</li> </ul>                                                 |                                                      |                            |  |  |  |  |  |  |  |

| Transfer data length         | 8 bits                                                                                                                                                                                              |                                                      |                            |  |  |  |  |  |  |  |

| Transfer rate                | Max. fмск/6 [bps] (SDR13 [15:9                                                                                                                                                                      | ] = 2 or more), Min. fclk/( $2 \times 2^{11} \times$ | 128) [bps] <sup>Note</sup> |  |  |  |  |  |  |  |

| Data phase                   | Forward output (default: high le<br>Reverse output (default: low lev                                                                                                                                | ,                                                    |                            |  |  |  |  |  |  |  |

| Parity bit                   | The following selectable <ul> <li>No parity bit (no parity check)</li> <li>Appending 0 parity (no parity check)</li> <li>Appending even parity check</li> <li>Appending odd parity check</li> </ul> |                                                      |                            |  |  |  |  |  |  |  |

| Stop bit                     | The following selectable <ul> <li>Appending 1 bit</li> <li>Appending 2 bits</li> </ul>                                                                                                              |                                                      |                            |  |  |  |  |  |  |  |

| Data direction               | MSB or LSB first                                                                                                                                                                                    |                                                      |                            |  |  |  |  |  |  |  |

Note Use this operation within a range that satisfies the conditions above and the AC characteristics in the electrical specifications (see CHAPTER 27 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS) and CHAPTER 28 ELECTRICAL SPECIFICATIONS ((A) GRADE PRODUCTS)).

**Remark** fMCK: Operation clock (MCK) frequency of target channel

fclk: System clock frequency

Figure 11-87 outlines a reception operation of LIN.

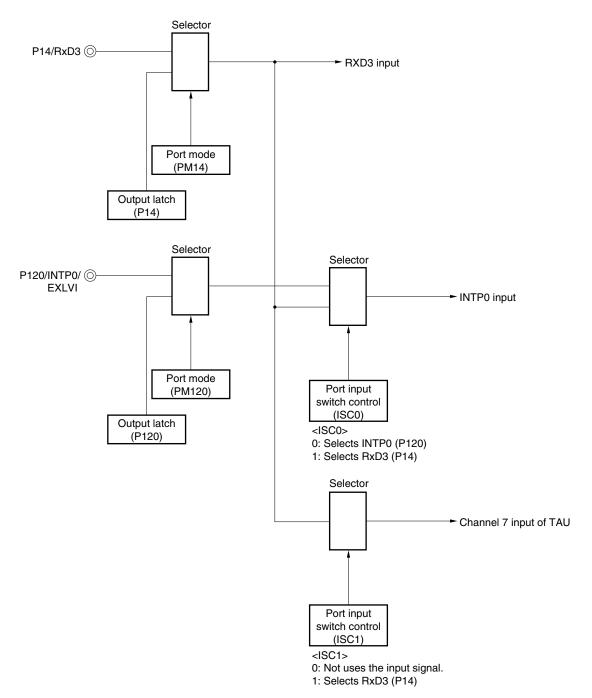

Figure 11-88 shows the configuration of a port that manipulates reception of LIN.

The wakeup signal transmitted from the master of LIN is received by detecting an edge of an external interrupt (INTP0). The length of the sync field transmitted from the master can be measured by using the external event capture operation of the timer array unit (TAU) to calculate a baud-rate error.

By controlling switch of port input (ISC0/ISC1), the input source of port input (RxD3) for reception can be input to the external interrupt pin (INTP0) and timer array unit (TAU).

Remark ISC0, ISC1: Bits 0 and 1 of the input switch control register (ISC) (See Figure 11-17.)

The peripheral functions used for the LIN communication operation are as follows.

<Peripheral functions used>

- External interrupt (INTP0); Wakeup signal detection

- Usage: To detect an edge of the wakeup signal and the start of communication

- Channel 7 of timer array unit (TAU); Baud rate error detection

- Usage: To detect the length of the sync field (SF) and divide it by the number of bits in order to detect an error (The interval of the edge input to RxD3 is measured in the capture mode.)

- Channels 2 and 3 (UART3) of serial array unit 1 (SAU1)

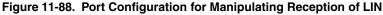

#### Figure 12-21. Communication Reservation Timing

| Remark | IIC0: | IIC shift register 0                    |  |  |  |

|--------|-------|-----------------------------------------|--|--|--|

|        | STT0: | Bit 1 of IIC control register 0 (IICC0) |  |  |  |

|        | STD0: | Bit 1 of IIC status register 0 (IICS0)  |  |  |  |

|        | SPD0: | Bit 0 of IIC status register 0 (IICS0)  |  |  |  |

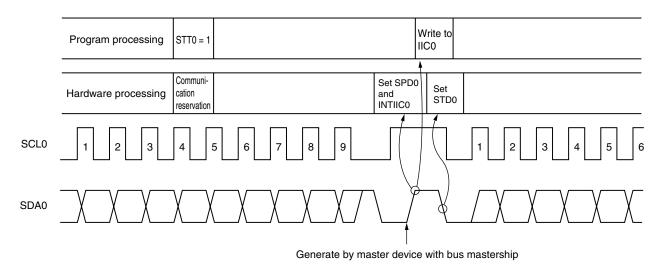

Communication reservations are accepted via the timing shown in Figure 12-22. After bit 1 (STD0) of IIC status register 0 (IICS0) is set to 1, a communication reservation can be made by setting bit 1 (STT0) of IIC control register 0 (IICC0) to 1 before a stop condition is detected.

Figure 12-23 shows the communication reservation protocol.

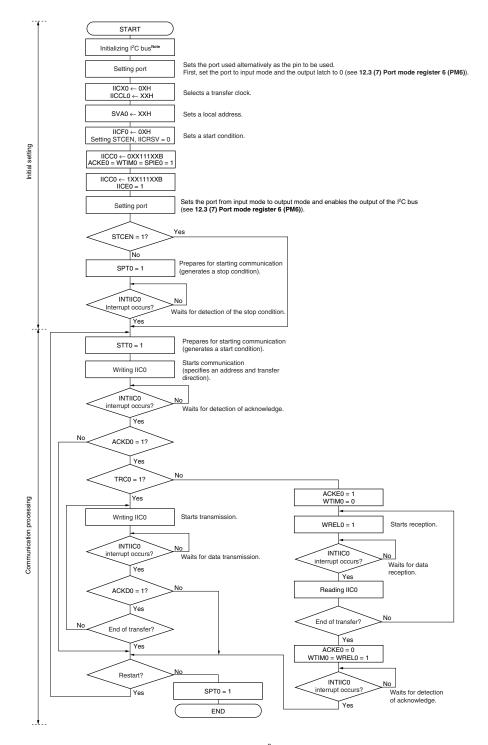

(1) Master operation in single-master system

- **Note** Release (SCL0 and SDA0 pins = high level) the l<sup>2</sup>C bus in conformance with the specifications of the product that is communicating. If EEPROM is outputting a low level to the SDA0 pin, for example, set the SCL0 pin in the output port mode, and output a clock pulse from the output port until the SDA0 pin is constantly at high level.

- **Remark** Conform to the specifications of the product that is communicating, with respect to the transmission and reception formats.

## **CHAPTER 17 STANDBY FUNCTION**

## 17.1 Standby Function and Configuration

#### 17.1.1 Standby function

The standby function reduces the operating current of the system, and the following two modes are available.

## (1) HALT mode

HALT instruction execution sets the HALT mode. In the HALT mode, the CPU operation clock is stopped. If the high-speed system clock oscillator, internal high-speed oscillator, or subsystem clock oscillator is operating before the HALT mode is set, oscillation of each clock continues. In this mode, the operating current is not decreased as much as in the STOP mode, but the HALT mode is effective for restarting operation immediately upon interrupt request generation and carrying out intermittent operations frequently.

### (2) STOP mode

STOP instruction execution sets the STOP mode. In the STOP mode, the high-speed system clock oscillator and internal high-speed oscillator stop, stopping the whole system, thereby considerably reducing the CPU operating current.

Because this mode can be cleared by an interrupt request, it enables intermittent operations to be carried out. However, because a wait time is required to secure the oscillation stabilization time after the STOP mode is released when the X1 clock is selected, select the HALT mode if it is necessary to start processing immediately upon interrupt request generation.

In either of these two modes, all the contents of registers, flags and data memory just before the standby mode is set are held. The I/O port output latches and output buffer statuses are also held.

- Cautions 1. The STOP mode can be used only when the CPU is operating on the main system clock. The STOP mode cannot be set while the CPU operates with the subsystem clock. The HALT mode can be used when the CPU is operating on either the main system clock or the subsystem clock.

- 2. When shifting to the STOP mode, be sure to stop the peripheral hardware operation operating with main system clock before executing STOP instruction.

- 3. The following sequence is recommended for operating current reduction of the A/D converter when the standby function is used: First clear bit 7 (ADCS) and bit 0 (ADCE) of the A/D converter mode register (ADM) to 0 to stop the A/D conversion operation, and then execute the STOP instruction.

- 4. It can be selected by the option byte whether the internal low-speed oscillator continues oscillating or stops in the HALT or STOP mode. For details, see CHAPTER 22 OPTION BYTE.

#### 17.1.2 Registers controlling standby function

The standby function is controlled by the following two registers.

- Oscillation stabilization time counter status register (OSTC)

- Oscillation stabilization time select register (OSTS)

Remark For the registers that start, stop, or select the clock, see CHAPTER 5 CLOCK GENERATOR.

| Pin Configuration of Dedicated Flash Memory Programmer |        |                                             | Pin Name       | Pin No.                                      |                          |

|--------------------------------------------------------|--------|---------------------------------------------|----------------|----------------------------------------------|--------------------------|

| Signal Name                                            | I/O    | Pin Function                                |                | LQFP (12x12),<br>LQFP (10x10),<br>TQFP (7x7) | FBGA (5x5)<br>FBGA (6x6) |

| SI/RxD <sup>Notes 1, 2</sup>                           | Input  | Receive signal                              | gnal TOOL0/P40 |                                              | D6                       |

| SO/TxD Note 2                                          | Output | Transmit signal                             |                |                                              |                          |

| SCK                                                    | Output | Transfer clock                              | _              | _                                            | _                        |

| CLK                                                    | Output | Clock output                                | _              | _                                            | _                        |

| /RESET                                                 | Output | Reset signal                                | RESET          | 6                                            | E7                       |

| FLMD0                                                  | Output | Mode signal                                 | FLMD0          | 9                                            | E8                       |

| Vdd                                                    | 1/0    | VDD voltage generation/<br>power monitoring | VDD            | 15                                           | B7                       |

|                                                        |        |                                             | EVDD           | 16                                           | A8                       |

|                                                        |        |                                             | AVREF          | 47                                           | G1                       |

| GND                                                    | -      | Ground                                      | Vss            | 13                                           | C7                       |

|                                                        |        |                                             | EVss           | 14                                           | B8                       |

|                                                        |        |                                             | AVss           | 48                                           | H1                       |

Table 23-1. Wiring Between 78K0R/KE3 and Dedicated Flash Memory Programmer

**Notes 1.** This pin is not required to be connected when using PG-FP5 or FL-PR5.

2. Connect SI/RxD or SO/TxD when using QB-MINI2.

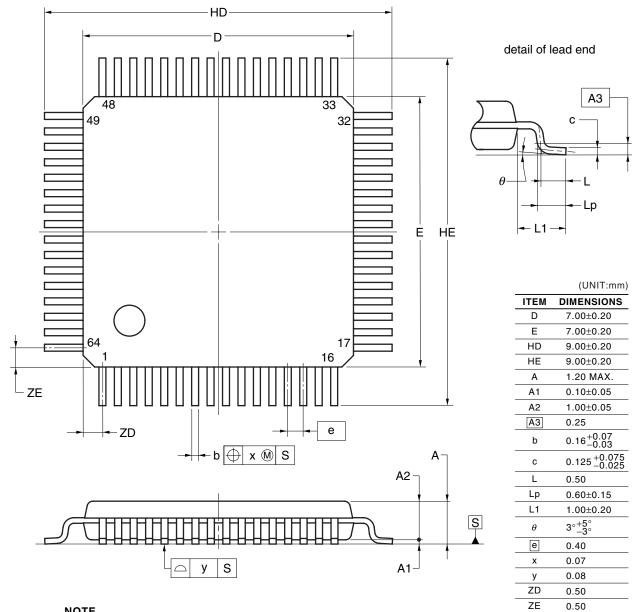

## 64-PIN PLASTIC TQFP (FINE PITCH) (7x7)

#### NOTE

Each lead centerline is located within 0.07mm of its true position at maximum material condition.

### © NEC Electronics Corporation 2005

P64GA-40-HAB