#

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 50                                                                                    |

| Program Memory Size        | 192КВ (192К х 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 10K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1145agb-gah-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                 |             |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                       |             |             | (2/2)       |  |  |  |

|-------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|--|--|--|

| Item                                            |             | μPD78F1142,                                                                                               | μPD78F1143,                                                                                                                                                                                                                                                                                                                                                           | μPD78F1144, | μPD78F1145, | μPD78F1146, |  |  |  |

|                                                 |             | μPD78F1142A                                                                                               | μPD78F1143A                                                                                                                                                                                                                                                                                                                                                           | μPD78F1144A | μPD78F1145A | μPD78F1146A |  |  |  |

| Serial interface                                |             | <ul> <li>UART supportin</li> <li>UART/CSI:</li> <li>UART/CSI/simp</li> <li>I<sup>2</sup>C bus:</li> </ul> | 1 cha                                                                                                                                                                                                                                                                                                                                                                 | annel       |             |             |  |  |  |

| Multiplier                                      |             | 16 bits × 16 bits =                                                                                       | 32 bits                                                                                                                                                                                                                                                                                                                                                               |             |             |             |  |  |  |

| DMA controller                                  |             | 2 channels                                                                                                |                                                                                                                                                                                                                                                                                                                                                                       |             |             |             |  |  |  |

| Vectored interrupt Internal<br>sources External |             | 25                                                                                                        | 25                                                                                                                                                                                                                                                                                                                                                                    |             |             |             |  |  |  |

|                                                 |             | 13                                                                                                        | 13                                                                                                                                                                                                                                                                                                                                                                    |             |             |             |  |  |  |

| Key interrupt                                   |             | Key interrupt (INTKR) occurs by detecting falling edge of the key input pins (KR0 to KR7).                |                                                                                                                                                                                                                                                                                                                                                                       |             |             |             |  |  |  |

| Reset                                           |             | <ul><li>Internal reset b</li><li>Internal reset b</li><li>Internal reset b</li></ul>                      | <ul> <li>Reset by RESET pin</li> <li>Internal reset by watchdog timer</li> <li>Internal reset by power-on-clear</li> <li>Internal reset by low-voltage detector</li> <li>Internal reset by illegal instruction execution<sup>Note 1</sup></li> </ul>                                                                                                                  |             |             |             |  |  |  |

| On-chip debug fund                              | ction       | Provided                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       |             |             |             |  |  |  |

| Power supply volta                              | ge          | V <sub>DD</sub> = 1.8 to 5.5 V                                                                            |                                                                                                                                                                                                                                                                                                                                                                       |             |             |             |  |  |  |

| Operating ambient                               | temperature | $T_{A} = -40 \text{ to } +85^{\circ}\text{C}$                                                             | T <sub>A</sub> = -40 to +85°C                                                                                                                                                                                                                                                                                                                                         |             |             |             |  |  |  |

| Package                                         |             | 64-pin plastic LQF<br>64-pin plastic TQF<br>64-pin plastic FBC                                            | 64-pin plastic LQFP ( $12 \times 12$ ) (0.65 mm pitch)<br>64-pin plastic LQFP (fine pitch) ( $10 \times 10$ ) (0.5 mm pitch)<br>64-pin plastic TQFP (fine pitch) ( $7 \times 7$ ) (0.4 mm pitch) <sup>Note 2</sup><br>64-pin plastic FBGA ( $5 \times 5$ ) (0.5 mm pitch) <sup>Note 2</sup><br>64-pin plastic FBGA ( $6 \times 6$ ) (0.65 mm pitch) <sup>Note 2</sup> |             |             |             |  |  |  |

**Notes 1.** The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution not issued by emulation with the in-circuit emulator or on-chip debug emulator.

2. Expanded-specification products (µPD78F114xA) only

- (b) In normal operation mode and when on-chip debugging is enabled (OCDENSET = 1) by an option byte (000C3H)

- => Connect this pin to EV<sub>DD</sub> via an external resistor, and always input a high level to the pin before reset release.

- (c) When on-chip debug function is used, or in write mode of flash memory programmer

- => Use this pin as TOOL0. Directly connect this pin to the on-chip debug emulator or a flash memory programmer, or pull it up by connecting it to EVDD via an external resistor.

## 2.2.6 P50 to P55 (port 5)

P50 to P55 function as a 6-bit I/O port. These pins also function as external interrupt request input. The following operation modes can be specified in 1-bit units.

## (1) Port mode

P50 to P55 function as a 6-bit I/O port. P50 to P55 can be set to input or output port in 1-bit units using port mode register 5 (PM5). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 5 (PU5).

## (2) Control mode

P50 and P51 function as external interrupt request input.

#### (a) INTP1, INTP2

These are the external interrupt request input pins for which the valid edge (rising edge, falling edge, or both rising and falling edges) can be specified.

#### 2.2.7 P60 to P63 (port 6)

P60 to P63 function as a 4-bit I/O port. These pins also function as serial interface data I/O and clock I/O. The following operation modes can be specified in 1-bit units.

#### (1) Port mode

P60 to P63 function as a 4-bit I/O port. P60 to P63 can be set to input port or output port in 1-bit units using port mode register 6 (PM6).

Output of P60 to P63 is N-ch open-drain output (6 V tolerance).

#### (2) Control mode

P60 and P61 function as serial interface data I/O and clock I/O.

#### (a) SDA0

This is a serial data I/O pin of serial interface IIC0.

## (b) SCL0

This is a serial clock I/O pin of serial interface IICO.

## 2.2.8 P70 to P77 (port 7)

P70 to P77 function as an 8-bit I/O port. These pins also function as key interrupt input and external interrupt request input.

The following operation modes can be specified in 1-bit units.

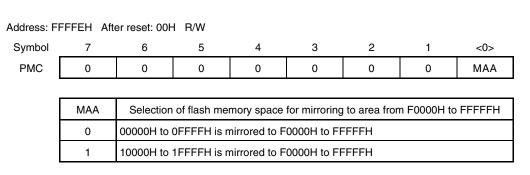

## • Processor mode control register (PMC)

This register selects the flash memory space for mirroring to area from F0000H to FFFFH. PMC can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to 00H.

#### Figure 3-6. Format of Configuration of Processor Mode Control Register (PMC)

- Cautions 1. Set PMC only once during the initial settings prior to operating the DMA controller. Rewriting PMC other than during the initial settings is prohibited.

- 2. After setting PMC, wait for at least one instruction and access the mirror area.

- 3. When the  $\mu$ PD78F1142 or 78F1142A is used, be sure to set bit 0 (MAA) of this register to 0.

## 3.1.3 Internal data memory space

78K0R/KE3 products incorporate the following RAMs.

| Part Number          | Internal RAM                            |

|----------------------|-----------------------------------------|

| μPD78F1142, 78F1142A | 4096 × 8 bits (FEF00H to FFEFFH)        |

| μPD78F1143, 78F1143A | 6144 × 8 bits (FE700H to FFEFFH)        |

| μPD78F1144, 78F1144A | 8192 $\times$ 8 bits (FDF00H to FFEFFH) |

| μPD78F1145, 78F1145A | 10240 × 8 bits (FD700H to FFEFFH)       |

| μPD78F1146, 78F1146A | 12288 × 8 bits (FCF00H to FFEFFH)       |

Table 3-4. Internal RAM Capacity

The internal RAM can be used as a data area and a program area where instructions are written and executed. Four general-purpose register banks consisting of eight 8-bit registers per bank are assigned to the 32-byte area of FFEE0H to FFEFFH of the internal RAM area. However, instructions cannot be executed by using general-purpose registers.

The internal RAM is used as a stack memory.

- Cautions 1. It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space for fetching instructions or as a stack area.

- 2. While using the self-programming function, the area of FFE20H to FFEFFH cannot be used as a stack memory. Furthermore, the areas of FCF00H to FD6FFH cannot be used with the  $\mu$ PD78F1146 and 78F1146A,.

## 3.2 Processor Registers

The 78K0R/KE3 products incorporate the following processor registers.

#### 3.2.1 Control registers

The control registers control the program sequence, statuses and stack memory. The control registers consist of a program counter (PC), a program status word (PSW) and a stack pointer (SP).

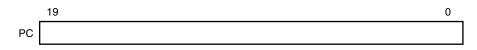

#### (1) Program counter (PC)

The program counter is a 20-bit register that holds the address information of the next program to be executed. In normal operation, PC is automatically incremented according to the number of bytes of the instruction to be fetched. When a branch instruction is executed, immediate data and register contents are set. Reset signal generation sets the reset vector table values at addresses 0000H and 0001H to the program counter.

#### Figure 3-12. Format of Program Counter

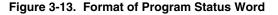

#### (2) Program status word (PSW)

The program status word is an 8-bit register consisting of various flags set/reset by instruction execution.

Program status word contents are stored in the stack area upon vector interrupt request acknowledgment or PUSH PSW instruction execution and are restored upon execution of the RETB, RETI and POP PSW instructions. Reset signal generation sets PSW to 06H.

#### (a) Interrupt enable flag (IE)

This flag controls the interrupt request acknowledge operations of the CPU.

When 0, the IE flag is set to the interrupt disabled (DI) state, and all maskable interrupt requests are disabled. When 1, the IE flag is set to the interrupt enabled (EI) state and interrupt request acknowledgment is controlled with an in-service priority flag (ISP1, ISP0), an interrupt mask flag for various interrupt sources, and a priority specification flag.

The IE flag is reset (0) upon DI instruction execution or interrupt acknowledgment and is set (1) upon EI instruction execution.

#### (b) Zero flag (Z)

When the operation result is zero, this flag is set (1). It is reset (0) in all other cases.

#### (c) Register bank select flags (RBS0, RBS1)

These are 2-bit flags to select one of the four register banks.

In these flags, the 2-bit information that indicates the register bank selected by SEL RBn instruction execution is stored.

| Address | Special Function Register (SFR) Name | Syr   | nbol | R/W | Manip        | ulable Bit   | Range        | After Reset |

|---------|--------------------------------------|-------|------|-----|--------------|--------------|--------------|-------------|

|         |                                      |       |      |     | 1-bit        | 8-bit        | 16-bit       |             |

| F0164H  | Serial channel stop register 1       | ST1L  | ST1  | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       |

| F0165H  |                                      | _     |      |     | _            | _            |              |             |

| F0166H  | Serial clock select register 1       | SPS1L | SPS1 | R/W | -            |              | $\checkmark$ | 0000H       |

| F0167H  |                                      | -     |      |     | -            | -            |              |             |

| F0168H  | Serial output register 1             | SO1   |      | R/W | -            | -            | $\checkmark$ | 0F0FH       |

| F0169H  |                                      |       |      |     |              |              |              |             |

| F016AH  | Serial output enable register 1      | SOE1L | SOE1 | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       |

| F016BH  |                                      | -     |      |     | -            | -            |              |             |

| F0174H  | Serial output level register 1       | SOL1L | SOL1 | R/W | _            | $\checkmark$ | $\checkmark$ | 0000H       |

| F0175H  |                                      | -     |      |     | -            | -            |              |             |

| F0180H  | Timer counter register 00            | TCR00 |      | R   | -            | -            | $\checkmark$ | FFFFH       |

| F0181H  |                                      |       |      |     |              |              |              |             |

| F0182H  | Timer counter register 01            | TCR01 |      | R   | -            | -            | $\checkmark$ | FFFFH       |

| F0183H  |                                      |       |      |     |              |              |              |             |

| F0184H  | Timer counter register 02            | TCR02 |      | R   | -            | -            | $\checkmark$ | FFFFH       |

| F0185H  |                                      |       |      |     |              |              |              |             |

| F0186H  | Timer counter register 03            | TCR03 |      | R   | -            | -            | $\checkmark$ | FFFFH       |

| F0187H  |                                      |       |      |     |              |              |              |             |

| F0188H  | Timer counter register 04            | TCR04 |      | R   | -            | -            | $\checkmark$ | FFFFH       |

| F0189H  |                                      |       |      |     |              |              |              |             |

| F018AH  | Timer counter register 05            | TCR05 |      | R   | -            | -            | $\checkmark$ | FFFFH       |

| F018BH  |                                      |       |      |     |              |              |              |             |

| F018CH  | Timer counter register 06            | TCR06 |      | R   | -            | -            | $\checkmark$ | FFFFH       |

| F018DH  |                                      |       |      |     |              |              |              |             |

| F018EH  | Timer counter register 07            | TCR07 |      | R   | -            | -            | $\checkmark$ | FFFFH       |

| F018FH  |                                      |       |      |     |              |              |              |             |

| F0190H  | Timer mode register 00               | TMR00 |      | R/W | -            | -            | $\checkmark$ | 0000H       |

| F0191H  |                                      |       |      |     |              |              |              |             |

| F0192H  | Timer mode register 01               | TMR01 |      | R/W | -            | -            | $\checkmark$ | 0000H       |

| F0193H  |                                      |       |      |     |              |              |              |             |

| F0194H  | Timer mode register 02               | TMR02 |      | R/W | -            | -            | $\checkmark$ | 0000H       |

| F0195H  |                                      |       |      |     |              |              |              |             |

| F0196H  | Timer mode register 03               | TMR03 |      | R/W | -            | -            | $\checkmark$ | 0000H       |

| F0197H  |                                      |       |      |     |              |              |              |             |

| F0198H  | Timer mode register 04               | TMR04 |      | R/W | -            | -            | $\checkmark$ | 0000H       |

| F0199H  |                                      |       |      |     |              |              |              |             |

| F019AH  | Timer mode register 05               | TMR05 |      | R/W | -            | -            | $\checkmark$ | 0000H       |

| F019BH  |                                      |       |      |     |              |              |              |             |

| F019CH  | Timer mode register 06               | TMR06 |      | R/W | -            | -            | $\checkmark$ | 0000H       |

| F019DH  |                                      |       |      |     |              |              |              |             |

| F019EH  | Timer mode register 07               | TMR07 |      | R/W | -            | -            | $\checkmark$ | 0000H       |

| F019FH  |                                      |       |      |     |              |              |              |             |

| Table 3-6. | Extended SFR | (2nd SFR | ) List (3/4) |

|------------|--------------|----------|--------------|

|------------|--------------|----------|--------------|

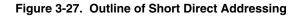

#### 3.4.4 Short direct addressing

## [Function]

Short direct addressing directly specifies the target addresses using 8-bit data in the instruction word. This type of addressing is applied only to the space from FFE20H to FFF1FH.

## [Operand format]

| Identifier | Description                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| SADDR      | Label, FFE20H to FFF1FH immediate data, or 0FE20H to 0FF1FH immediate data                                                                           |

|            | (only the space from FFE20H to FFF1FH is specifiable)                                                                                                |

| SADDRP     | Label, FFE20H to FFF1FH immediate data, or 0FE20H to 0FF1FH immediate data (even address only) (only the space from FFE20H to FFF1FH is specifiable) |

**Remark** SADDR and SADDRP are used to describe the values of addresses FE20H to FF1FH with 16-bit immediate data (higher 4 bits of actual address are omitted), and the values of addresses FFE20H to FFF1FH with 20-bit immediate data.

Regardless of whether 16-bit or 20-bit immediate data is used, addresses within the space from FFE20H to FFF1FH are specified for the memory.

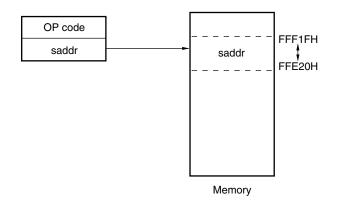

CHAPTER 5 CLOCK GENERATOR

## <R> Figure 5-1. Block Diagram of Clock Generator

- **Remark** fx: X1 clock oscillation frequency

- fin: Internal high-speed oscillation clock frequency

- fex: External main system clock frequency

- fmx: High-speed system clock frequency

- fmain: Main system clock frequency

- fmainc: Main system select clock frequency

- fxr: XT1 clock oscillation frequency

- fsub: Subsystem clock frequency

- fclk: CPU/peripheral hardware clock frequency

- fiL: Internal low-speed oscillation clock frequency

## 5.3 Registers Controlling Clock Generator

The following eight registers are used to control the clock generator.

- Clock operation mode control register (CMC)

- Clock operation status control register (CSC)

- Oscillation stabilization time counter status register (OSTC)

- Oscillation stabilization time select register (OSTS)

- System clock control register (CKC)

- Peripheral enable registers 0 (PER0)

- Operation speed mode control register (OSMC)

- Internal high-speed oscillator trimming register (HIOTRM)

User's Manual U17854EJ9V0UD

<R>

## 5.6 Controlling Clock

#### 5.6.1 Example of controlling high-speed system clock

The following two types of high-speed system clocks are available.

- X1 clock: Crystal/ceramic resonator is connected to the X1 and X2 pins.

- External main system clock: External clock is input to the EXCLK pin.

When the high-speed system clock is not used, the X1/P121 and X2/EXCLK/P122 pins can be used as input port pins.

#### Caution The X1/P121 and X2/EXCLK/P122 pins are in the input port mode after a reset release.

The following describes examples of setting procedures for the following cases.

- (1) When oscillating X1 clock

- (2) When using external main system clock

- (3) When using high-speed system clock as CPU/peripheral hardware clock

- (4) When stopping high-speed system clock

## (1) Example of setting procedure when oscillating the X1 clock

- <1> Setting P121/X1 and P122/X2/EXCLK pins and setting oscillation frequency (CMC register)

- 2 MHz  $\leq$  fx  $\leq$  10 MHz

| EXCLK | OSCSEL | 0 | OSCSELS | 0 | 0 | 0 | AMPH |

|-------|--------|---|---------|---|---|---|------|

| 0     | 1      | 0 | 0/1     | 0 | 0 | 0 | 0    |

• 10 MHz < fx  $\leq$  20 MHz

| EXCLK | OSCSEL | 0 | OSCSELS | 0 | 0 | 0 | AMPH |

|-------|--------|---|---------|---|---|---|------|

| 0     | 1      | 0 | 0/1     | 0 | 0 | 0 | 1    |

Remarks 1. fx: X1 clock oscillation frequency

For setting of the P123/XT1 and P124/XT2 pins, see 5.6.3 Example of controlling subsystem clock.

- <2> Controlling oscillation of X1 clock (CSC register) If MSTOP is cleared to 0, the X1 oscillator starts oscillating.

- <3> Waiting for the stabilization of the oscillation of X1 clock Check the OSTC register and wait for the necessary time. During the wait time, other software processing can be executed with the internal high-speed oscillation clock.

- Cautions 1. The CMC register can be written only once after reset release, by an 8-bit memory manipulation instruction. Therefore, it is necessary to also set the value of the OSCSELS bit at the same time. For

- OSCSELS bit, see 5.6.3 Example of controlling subsystem clock.

Set the X1 clock after the supply voltage has reached the operable voltage of the clock to be used (see CHAPTER 27 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS) and

CHAPTER 28 ELECTRICAL SPECIFICATIONS ((A) GRADE PRODUCTS)).

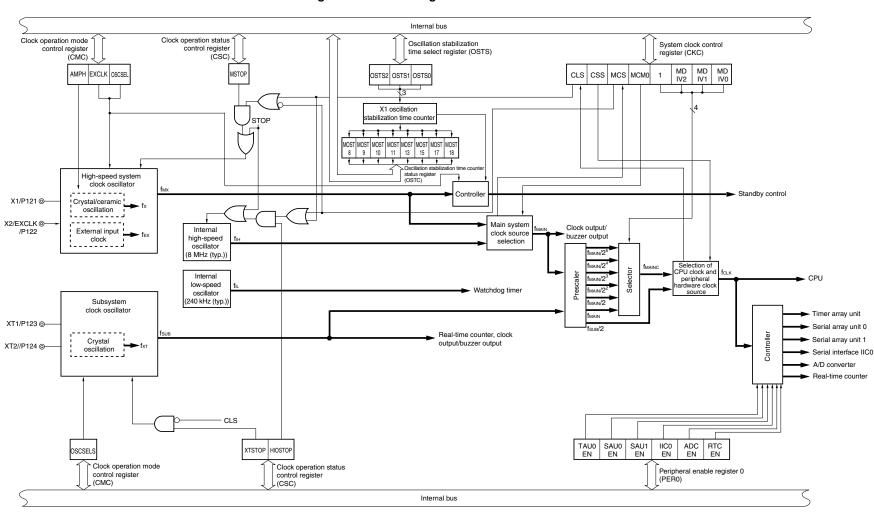

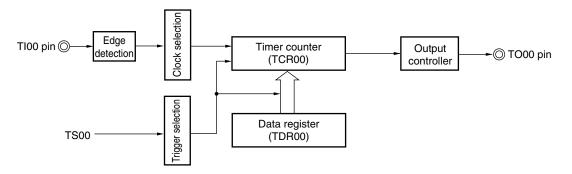

## 6.7.3 Operation as frequency divider (channel 0 only)

The timer array unit can be used as a frequency divider that divides a clock input to the TI00 pin and outputs the result from TO00.

The divided clock frequency output from TO00 can be calculated by the following expression.

- When rising edge/falling edge is selected:

- Divided clock frequency = Input clock frequency/{(Set value of TDR00 + 1) × 2}

- When both edges are selected:

- Divided clock frequency  $\cong$  Input clock frequency/(Set value of TDR00 + 1)

TCR00 operates as a down counter in the interval timer mode.

After the channel start trigger bit (TS00) is set to 1, TCR00 loads the value of TDR00 when the TI00 valid edge is detected. If MD000 of TMR00 = 0 at this time, INTTM00 is not output and TO00 is not toggled. If MD000 of TMR00 = 1, INTTM00 is output and TO00 is toggled.

After that, TCR00 counts down at the valid edge of TI0k. When TCR00 = 0000H, it toggles TO00. At the same time, TCR00 loads the value of TDR00 again, and continues counting.

If detection of both the edges of TI00 is selected, the duty factor error of the input clock affects the divided clock period of the TO00 output.

The period of the TO00 output clock includes a sampling error of one period of the operation clock.

Clock period of TO00 output = Ideal TO00 output clock period  $\pm$  Operation clock period (error)

TDR00 can be rewritten at any time. The new value of TDR00 becomes valid during the next count period.

The setting methods are described below.

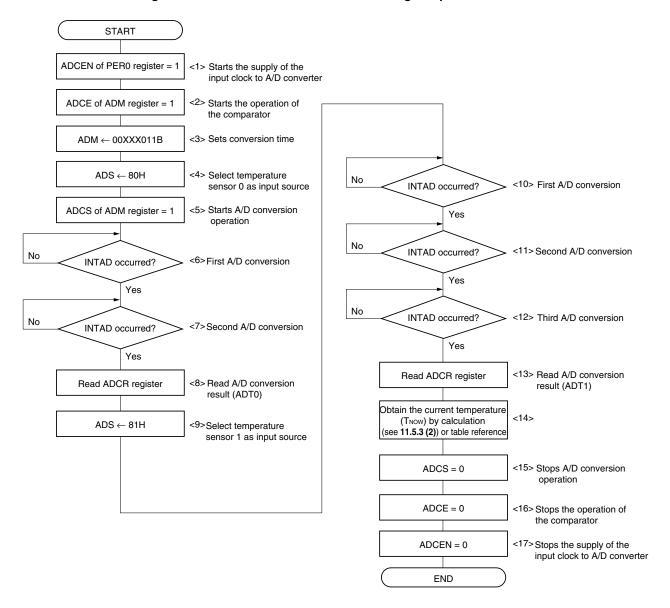

- <1> Set bit 5 (ADCEN) of peripheral enable register 0 (PER0) to 1.

- <2> Set bit 0 (ADCE) of the A/D converter mode register (ADM) to 1.

- <3> Set the channel to be used in the analog input mode by using bits 4 to 0 (ADPC4 to ADPC0) of the A/D port configuration register (ADPC) and bits 7 to 0 (PM27 to PM20) of port mode register 2 (PM2).

- <4> Select conversion time by using bits 5 to 1 (FR2 to FR0, LV1, and LV0) of ADM.

- <5> Select a channel to be used by using bits 7 and 2 to 0 (ADISS, ADS2 to ADS0) of the analog input channel specification register (ADS).

- <6> Set bit 7 (ADCS) of ADM to 1 to start A/D conversion.

- <7> When one A/D conversion has been completed, an interrupt request signal (INTAD) is generated.

- <8> Transfer the A/D conversion data to the A/D conversion result register (ADCR, ADCRH).

- <Change the channel>

- <9> Change the channel using bits 7 and 2 to 0 (ADISS, ADS2 to ADS0) of ADS to start A/D conversion.

- <10> When one A/D conversion has been completed, an interrupt request signal (INTAD) is generated.

- <11> Transfer the A/D conversion data to the A/D conversion result register (ADCR, ADCRH).

<Complete A/D conversion>

- <12> Clear ADCS to 0.

- <13> Clear ADCE to 0.

- <14> Clear bit 5 (ADCEN) of peripheral enable register 0 (PER0)

Cautions 1. Make sure the period of <2> to <6> is 1  $\mu$ s or more.

- 2. <2> may be done between <3> and <5>.

- 3. The period from <7> to <10> differs from the conversion time set using bits 5 to 1 (FR2 to FR0, LV1, LV0) of ADM. The period from <9> to <10> is the conversion time set using FR2 to FR0, LV1, and LV0.

- Caution Use the result of the second or later A/D conversion for temperature sensor 0 (ANI0 side), and the result of the third or later A/D conversion for temperature sensor 1 (ANI1 side).

- Remark Steps <1> to <17> in Figure 10-18 correspond to steps <1> to <17> in 10.5.4 (2) Procedure for obtaining ADT0 and ADT1 of temperature sensors 0 and 1.

| SMR0n<br>Register |            |            | ę          | SPS0 F     | Operation Clo | ock (MCK) <sup>Note 1</sup> |            |            |                      |               |

|-------------------|------------|------------|------------|------------|---------------|-----------------------------|------------|------------|----------------------|---------------|

| CKS0n             | PRS<br>013 | PRS<br>012 | PRS<br>011 | PRS<br>010 | PRS<br>003    | PRS<br>002                  | PRS<br>001 | PRS<br>000 |                      | fclк = 20 MHz |

| 0                 | х          | х          | х          | х          | 0             | 0                           | 0          | 0          | fclĸ                 | 20 MHz        |

|                   | х          | х          | х          | х          | 0             | 0                           | 0          | 1          | fclk/2               | 10 MHz        |

|                   | х          | х          | х          | х          | 0             | 0                           | 1          | 0          | fclk/2 <sup>2</sup>  | 5 MHz         |

|                   | х          | х          | х          | х          | 0             | 0                           | 1          | 1          | fclk/2 <sup>3</sup>  | 2.5 MHz       |

|                   | х          | х          | х          | х          | 0             | 1                           | 0          | 0          | fclk/2 <sup>4</sup>  | 1.25 MHz      |

|                   | х          | х          | х          | х          | 0             | 1                           | 0          | 1          | fc∟ĸ/2⁵              | 625 kHz       |

|                   | х          | х          | х          | х          | 0             | 1                           | 1          | 0          | fclk/2 <sup>6</sup>  | 313 kHz       |

|                   | х          | х          | х          | х          | 0             | 1                           | 1          | 1          | fclk/2 <sup>7</sup>  | 156 kHz       |

|                   | х          | х          | х          | х          | 1             | 0                           | 0          | 0          | fclĸ/2 <sup>8</sup>  | 78.1 kHz      |

|                   | х          | х          | х          | х          | 1             | 0                           | 0          | 1          | fclĸ/2 <sup>9</sup>  | 39.1 kHz      |

|                   | х          | х          | х          | х          | 1             | 0                           | 1          | 0          | fclk/2 <sup>10</sup> | 19.5 kHz      |

|                   | х          | х          | х          | х          | 1             | 0                           | 1          | 1          | fclk/2 <sup>11</sup> | 9.77 kHz      |

|                   | х          | х          | х          | х          | 1             | 1                           | 1          | 1          | INTTM02 Note 2       |               |

| 1                 | 0          | 0          | 0          | 0          | х             | х                           | х          | х          | fclĸ                 | 20 MHz        |

|                   | 0          | 0          | 0          | 1          | х             | х                           | х          | х          | fclк/2               | 10 MHz        |

|                   | 0          | 0          | 1          | 0          | х             | х                           | х          | х          | fclk/2 <sup>2</sup>  | 5 MHz         |

|                   | 0          | 0          | 1          | 1          | х             | х                           | х          | Х          | fclk/2 <sup>3</sup>  | 2.5 MHz       |

|                   | 0          | 1          | 0          | 0          | х             | х                           | х          | х          | fclk/2 <sup>4</sup>  | 1.25 MHz      |

|                   | 0          | 1          | 0          | 1          | х             | х                           | х          | х          | fc∟ĸ/2⁵              | 625 kHz       |

|                   | 0          | 1          | 1          | 0          | х             | х                           | х          | х          | fclĸ/2 <sup>6</sup>  | 313 kHz       |

|                   | 0          | 1          | 1          | 1          | х             | х                           | х          | х          | fclk/2 <sup>7</sup>  | 156 kHz       |

|                   | 1          | 0          | 0          | 0          | х             | х                           | х          | Х          | fclĸ/2 <sup>8</sup>  | 78.1 kHz      |

|                   | 1          | 0          | 0          | 1          | х             | х                           | х          | Х          | fclĸ/2 <sup>9</sup>  | 39.1 kHz      |

|                   | 1          | 0          | 1          | 0          | х             | х                           | х          | х          | fclk/2 <sup>10</sup> | 19.5 kHz      |

|                   | 1          | 0          | 1          | 1          | х             | х                           | х          | х          | fclk/2 <sup>11</sup> | 9.77 kHz      |

|                   | 1          | 1          | 1          | 1          | х             | х                           | х          | х          | INTTM02 Note 2       |               |

|                   |            | (          | Other th   | nan abo    | ove           |                             |            |            | Setting prohibi      | ted           |

| Table 11-2 | Operating | <b>Clock Selection</b> |

|------------|-----------|------------------------|

|------------|-----------|------------------------|

Notes 1. When changing the clock selected for fcLk (by changing the system clock control register (CKC) value), do so after having stopped (ST0 = 000FH) the operation of the serial array unit (SAU). When selecting INTTM02 for the operation clock, also stop the timer array unit (TAU) (TT0 = 00FFH).

2. SAU can be operated at a fixed division ratio of the subsystem clock, regardless of the fcLk frequency (main system clock, subsystem clock), by operating the interval timer for which fsUB/4 has been selected as the count clock (setting TIS02 (if m = 0) or TIS03 (if m = 1) of the TIS0 register to 1) and selecting INTTM02 and INTTM03 by using the SPSm register in channels 2 and 3 of TAU. When changing fcLk, however, SAU and TAU must be stopped as described in Note 1 above.

Remarks 1. X: Don't care

**2.** n: Channel number (n = 0, 2)

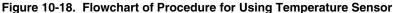

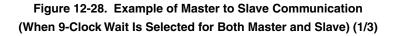

## 12.5.7 Wait

The wait is used to notify the communication partner that a device (master or slave) is preparing to transmit or receive data (i.e., is in a wait state).

Setting the SCL0 pin to low level notifies the communication partner of the wait state. When wait state has been canceled for both the master and slave devices, the next data transfer can begin.

## Figure 12-19. Wait (1/2)

## (1) When master device has a nine-clock wait and slave device has an eight-clock wait (master transmits, slave receives, and ACKE0 = 1)

| Master       Master returns to high impedance but slave is in wait state (low level).       Wait after output of ninth clock         IIC0       IIC0       IIC0 data write (cancel wait)         ScLo       6       7       8       9       1       2       3         Slave       Wait after output of eighth clock       IIC0 or WREL0 is set to 1         IIC0 |   |                |       |                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|-------|---------------------------------------------------------------------------------------|

| IICo       is in wait state (low level).       Wait after output<br>of ninht clock         SCLO       6       7       8       9       1       2       3         Slave       Wait after output<br>of eighth clock       IICo or WREL0 is set to 1         IICo                                                                                                    |   | Master         |       | Maatao oo ka biab                                                                     |

| Slave<br>Wait after output<br>of eighth clock<br>IICO<br>SCL0<br>ACKE0<br>H<br>Transfer lines<br>Wait from slave<br>SCL0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                                                                        |   |                | IIC0  | impedance but slave Wait after output<br>is in wait state (low level). of ninth clock |

| Wait after output<br>of eighth clock<br>SCL0<br>ACKE0<br>H<br>Transfer lines<br>SCL0<br>6<br>7<br>8<br>4<br>4<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5                                                                                                                                                               |   |                | SCL0  |                                                                                       |

| <pre>FFH is written to IIC0 or WREL0 is set to 1 SCL0 ACKE0 H Transfer lines SCL0 6 7 8 9 1 2 3</pre>                                                                                                                                                                                                                                                            | [ | Slave          | ]     | Wait after output                                                                     |

| ACKE0 H<br>Transfer lines Wait from slave Wait from master SCL0 $6$ $7$ $8$ $9$ $1$ $2$ $3$                                                                                                                                                                                                                                                                      |   |                | IIC0  |                                                                                       |

| Transfer lines<br>Wait from slave Wait from master<br>SCL0 6 7 8 9 1 2 3                                                                                                                                                                                                                                                                                         |   |                | SCL0  |                                                                                       |

| Wait from slave Wait from master                                                                                                                                                                                                                                                                                                                                 |   |                | ACKE0 | Н                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                  | [ | Transfer lines | ]     |                                                                                       |

| SDA0 D2 D1 D0 ACK D7 D6 D5                                                                                                                                                                                                                                                                                                                                       |   |                | SCL0  |                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                  |   |                | SDA0  | D2         D1         D0         ACK         D7         D6         D5                 |

## Figure 12-25. Master Operation in Multi-Master System (2/3)

## (1) Start condition ~ address

Notes 1. Write data to IIC0, not setting WREL0, in order to cancel a wait state during master transmission.2. To cancel a slave wait state, write "FFH" to IIC0 or set WREL0.

Standard Products

## DC Characteristics (4/10) (TA = -40 to +85°C, 1.8 V $\leq$ VDD = EVDD $\leq$ 5.5 V, 1.8 V $\leq$ AVREF $\leq$ VDD, VSS = EVSS = AVSS = 0 V)

| Items                   | Symbol           | Conditions                                                               |                                                                                                                                                | MIN.                       | TYP. | MAX. | Unit |

|-------------------------|------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|------|------|

| Output voltage,<br>high | V <sub>OH1</sub> | P00 to P06, P10 to P17, P30, P31,<br>P40 to P43, P50 to P55, P70 to P77, | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OH1}} = \ - \ 3.0 \ mA \end{array}$                                     | $V_{\text{DD}} - 0.7$      |      |      | V    |

|                         |                  | P120, P130, P140, P141                                                   | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} \leq 5.5 \mbox{ V}, \\ I_{\mbox{OH1}} = -1.0 \mbox{ mA} \end{array}$ | $V_{\text{DD}} - 0.5$      |      |      | ۷    |

|                         | Vон2             | P20 to P27                                                               | $AV_{REF} \le V_{DD},$<br>Ioh2 = -0.1 mA                                                                                                       | AV <sub>REF</sub> –<br>0.5 |      |      | ۷    |

| Output voltage,<br>low  | V <sub>OL1</sub> | P00 to P02, P05, P06, P10 to P17,<br>P30, P31, P40 to P43, P50 to P55,   | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 8.5 \ mA \end{array} \label{eq:DD}$                             |                            |      | 0.7  | ۷    |

|                         |                  | P70 to P77, P120, P130, P140,<br>P141                                    | $\label{eq:VDD} \begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 1.0 \ mA \end{array}$                            |                            |      | 0.5  | ۷    |

|                         |                  |                                                                          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} \leq 5.5 \mbox{ V}, \\ I_{\mbox{OL1}} = 0.5 \mbox{ mA} \end{array}$  |                            |      | 0.4  | V    |

|                         |                  | P03, P04                                                                 | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 8.5 \ mA \end{array} \label{eq:DD}$                             |                            |      | 0.7  | V    |

|                         |                  |                                                                          | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 1.5 \ mA \end{array} \end{array} \label{eq:DD}$                 |                            |      | 0.5  | V    |

|                         |                  |                                                                          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} \leq 5.5 \mbox{ V}, \\ I_{\mbox{OL1}} = 0.6 \mbox{ mA} \end{array}$  |                            |      | 0.4  | V    |

|                         | Vol2             | P20 to P27                                                               | $AV_{REF} \le V_{DD},$<br>Iol2 = 0.4 mA                                                                                                        |                            |      | 0.4  | V    |

|                         | Vol3             | P60 to P63                                                               | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 15.0 \ mA \end{array} \end{array} \label{eq:VDD}$               |                            |      | 2.0  | V    |

|                         |                  |                                                                          | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 5.0 \ mA \end{array} \label{eq:DD}$                             |                            |      | 0.4  | V    |

|                         |                  |                                                                          | $\label{eq:VDD} \begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 3.0 \ mA \end{array}$                            |                            |      | 0.4  | V    |

|                         |                  |                                                                          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} \leq 5.5 \mbox{ V}, \\ I_{\mbox{OL1}} = 2.0 \mbox{ mA} \end{array}$  |                            |      | 0.4  | V    |

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

Standard Products

(2) Serial interface: Serial array unit (6/18)

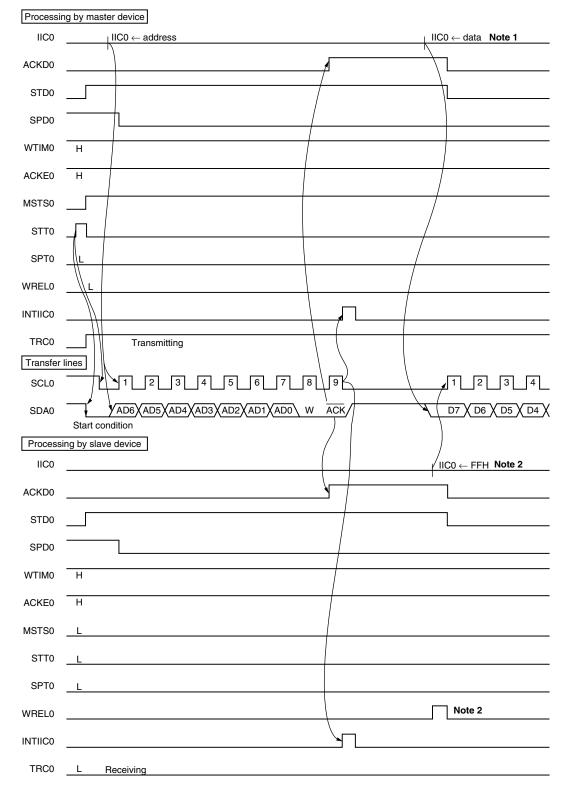

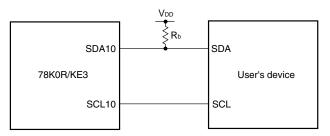

Simplified I<sup>2</sup>C mode mode connection diagram (during communication at same potential)

Simplified I<sup>2</sup>C mode serial transfer timing (during communication at same potential)

- Caution Select the normal input buffer and the N-ch open drain output (VDD tolerance) mode for SDA10 and the normal output mode for SCL10 by using the PIM0 and POM0 registers.

- $\label{eq:Remarks 1.} \begin{array}{ll} R_b[\Omega]: Communication line (SDA10) \mbox{ pull-up resistance}, \\ C_b[F]: \mbox{ Communication line (SCL10, SDA10) load capacitance} \end{array}$

- fMCK: Serial array unit operation clock frequency (Operation clock to be set by the CKS02 bit of the SMR02 register.)

### (2) Serial interface: Serial array unit (2/18)

<R>

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

| Parameter                                                                          | Symbol        | Conditions                            | MIN.                  | TYP. | MAX. | Unit |

|------------------------------------------------------------------------------------|---------------|---------------------------------------|-----------------------|------|------|------|

| SCKp cycle time                                                                    | tксү1         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 200 <sup>Note 1</sup> |      |      | ns   |

|                                                                                    |               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 300 Note 1            |      |      | ns   |

|                                                                                    |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | 600 Note 1            |      |      | ns   |

| SCKp high-/low-level width                                                         | tĸнı,<br>tĸ∟ı | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | tксү1/2 – 20          |      |      | ns   |

|                                                                                    |               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | tксү1/2 – 35          |      |      | ns   |

|                                                                                    |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | tксү1/2 – 80          |      |      | ns   |

| Slp setup time (to SCKp↑) <sup>№te 1</sup>                                         | tsıкı         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 70                    |      |      | ns   |

|                                                                                    |               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 100                   |      |      | ns   |

|                                                                                    |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | 190                   |      |      | ns   |

| SIp hold time (from $\overline{\text{SCKp}}^{\uparrow}$ ) Note 2                   | tksi1         |                                       | 30                    |      |      | ns   |

| Delay time from $\overline{\text{SCKp}}\downarrow$ to SOp output <sup>Note 3</sup> | tkso1         | C = 30 pF <sup>Note 4</sup>           |                       |      | 40   | ns   |

#### (b) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output)

**Notes 1.** The value must also be 4/fcLK or more.

- 2. When DAP0n = 0 and CKP0n = 0, or DAP0n = 1 and CKP0n = 1. The SIp setup time becomes "to  $\overline{SCKp}\downarrow$ " when DAP0n = 0 and CKP0n = 1, or DAP0n = 1 and CKP0n = 0.

- **3.** When DAP0n = 0 and CKP0n = 0, or DAP0n = 1 and CKP0n = 1. The SIp hold time becomes "from  $\overline{SCKp}\downarrow$ " when DAP0n = 0 and CKP0n = 1, or DAP0n = 1 and CKP0n = 0.

- 4. When DAP0n = 0 and CKP0n = 0, or DAP0n = 1 and CKP0n = 1. The delay time to SOp output becomes "from  $\overline{SCKp}^{\uparrow}$ " when DAP0n = 0 and CKP0n = 1, or DAP0n = 1 and CKP0n = 0.

- 5. C is the load capacitance of the  $\overline{\text{SCKp}}$  and SOp output lines.

## Caution When using CSI10, select the normal input buffer for SI10 and the normal output mode for SO10 and SCK10 by using the PIM0 and POM0 registers.

**Remark** p: CSI number (p = 00, 10), n: Channel number (n = 0, 2)

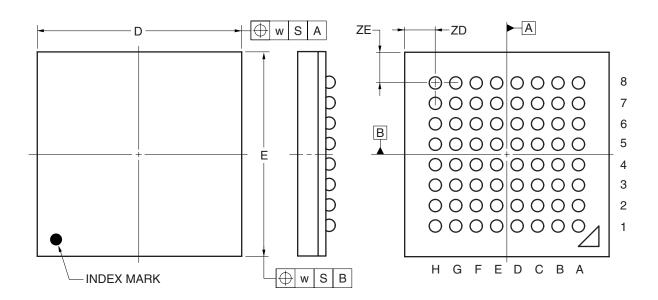

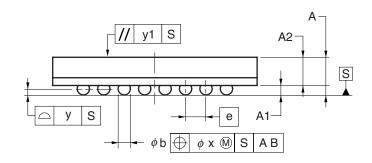

## 64-PIN PLASTIC FBGA (5x5)

|   |      | (UNIT:mm)    |  |  |

|---|------|--------------|--|--|

|   | ITEM | DIMENSIONS   |  |  |

| - | D    | 5.00±0.10    |  |  |

|   | Е    | 5.00±0.10    |  |  |

|   | w    | 0.20         |  |  |

|   | А    | 0.90±0.10    |  |  |

|   | A1   | 0.21±0.05    |  |  |

|   | A2   | 0.69         |  |  |

|   | е    | 0.50         |  |  |

|   | b    | 0.32±0.05    |  |  |

|   | х    | 0.05         |  |  |

|   | У    | 0.08         |  |  |

|   | y1   | 0.20         |  |  |

|   | ZD   | 0.75         |  |  |

|   | ZE   | 0.75         |  |  |

| - |      | P64F1-50-AN1 |  |  |

© NEC Electronics Corporation 2006