#

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 50                                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 12K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1146agb-gah-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Windows and Windows NT are registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

EEPROM is a trademark of NEC Electronics Corporation.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

Caution: This product uses SuperFlash<sup>®</sup> technology licensed from Silicon Storage Technology, Inc.

- The information in this document is current as of September, 2009. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. In addition, NEC Electronics products are not taken measures to prevent radioactive rays in the product design. When customers use NEC Electronics products with their products, customers shall, on their own responsibility, incorporate sufficient safety measures such as redundancy, fire-containment and anti-failure features to their products in order to avoid risks of the damages to property (including public or social property) or injury (including death) to persons, as the result of defects of NEC Electronics products.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

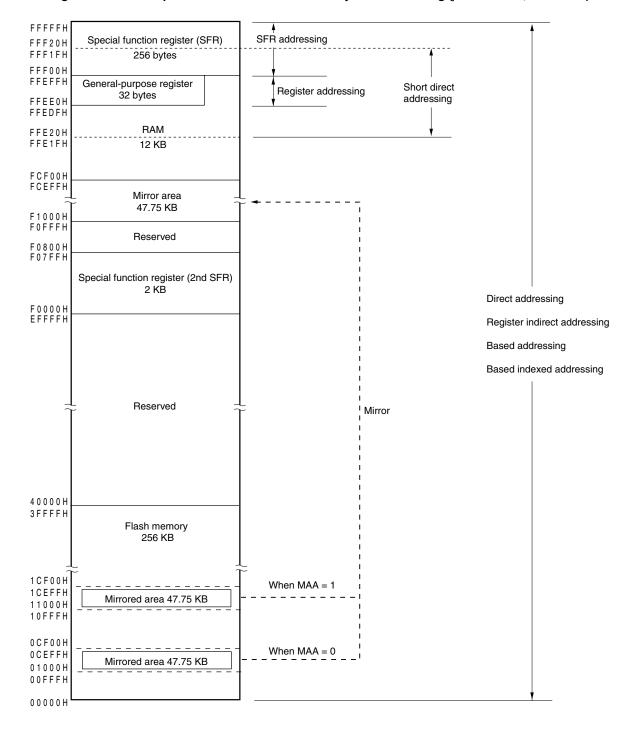

# <R> Figure 3-11. Correspondence Between Data Memory and Addressing (µPD78F1146, 78F1146A)

**Note** Use of the area FCF00H to FD6FFH is prohibited when using the self-programming function. Since this area is used for self-programming library.

# (d) Auxiliary carry flag (AC)

If the operation result has a carry from bit 3 or a borrow at bit 3, this flag is set (1). It is reset (0) in all other cases.

# (e) In-service priority flags (ISP1, ISP0)

This flag manages the priority of acknowledgeable maskable vectored interrupts. Vectored interrupt requests specified lower than the value of ISP0 and ISP1 by a priority specification flag register (PRn0L, PRn0H, PRn1L, PRn1H, PRn2L, PRn2H) (see **15.3 (3)**) can not be acknowledged. Actual request acknowledgment is controlled by the interrupt enable flag (IE).

**Remark** n = 0, 1

# (f) Carry flag (CY)

This flag stores overflow and underflow upon add/subtract instruction execution. It stores the shift-out value upon rotate instruction execution and functions as a bit accumulator during bit operation instruction execution.

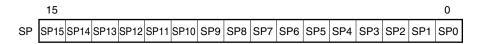

# (3) Stack pointer (SP)

This is a 16-bit register to hold the start address of the memory stack area. Only the internal RAM area can be set as the stack area.

# Figure 3-14. Format of Stack Pointer

The SP is decremented ahead of write (save) to the stack memory and is incremented after read (restored) from the stack memory.

Each stack operation saves data as shown in Figure 3-15.

- Cautions 1. Since reset signal generation makes the SP contents undefined, be sure to initialize the SP before using the stack.

- 2. The values of the stack pointer must be set to even numbers. If odd numbers are specified, the least significant bit is automatically cleared to 0.

- 3. It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space as a stack area.

- 4. While using the self-programming function, the area of FFE20H to FFEFFH cannot be used as a stack memory. Furthermore, the areas of FCF00H to FD6FFH cannot be used with the  $\mu$ PD78F1146 and 78F1146A.

<R>

| Address | Special Function Register (SFR) Name             | Sym    | bol   | R/W | Manipu       | ulable Bit   | Range  | After Reset |

|---------|--------------------------------------------------|--------|-------|-----|--------------|--------------|--------|-------------|

|         |                                                  |        |       |     | 1-bit        | 8-bit        | 16-bit |             |

| F0017H  | A/D port configuration register                  | ADPC   |       | R/W | -            |              | -      | 10H         |

| F0030H  | Pull-up resistor option register 0               | PU0    |       | R/W | $\checkmark$ |              | _      | 00H         |

| F0031H  | Pull-up resistor option register 1               | PU1    |       | R/W |              |              | _      | 00H         |

| F0033H  | Pull-up resistor option register 3               | PU3    |       | R/W |              |              | _      | 00H         |

| F0034H  | Pull-up resistor option register 4               | PU4    |       | R/W | $\checkmark$ |              | _      | 00H         |

| F0035H  | Pull-up resistor option register 5               | PU5    |       | R/W |              |              | _      | 00H         |

| F0037H  | Pull-up resistor option register 7               | PU7    |       | R/W |              |              | _      | 00H         |

| F003CH  | Pull-up resistor option register 12              | PU12   |       | R/W | $\checkmark$ |              | _      | 00H         |

| F003EH  | Pull-up resistor option register 14              | PU14   |       | R/W | $\checkmark$ |              | _      | 00H         |

| F0040H  | Port input mode register 0                       | PIM0   |       | R/W | $\checkmark$ |              | _      | 00H         |

| F0050H  | Port output mode register 0                      | POM0   |       | R/W | $\checkmark$ |              | _      | 00H         |

| F0060H  | Noise filter enable register 0                   | NFEN0  |       | R/W | $\checkmark$ |              | _      | 00H         |

| F0061H  | Noise filter enable register 1                   | NFEN1  |       | R/W | $\checkmark$ |              | _      | 00H         |

| F00F0H  | Peripheral enable register 0                     | PER0   |       | R/W | $\checkmark$ |              | _      | 00H         |

| F00F2H  | Internal high-speed oscillator trimming register | HIOTRM |       | R/W | _            |              | _      | 10H         |

| F00F3H  | Operation speed mode control register            | OSMC   |       | R/W | _            |              | _      | 00H         |

| F00F4H  | Regulator mode control register                  | RMC    |       | R/W | _            |              | _      | 00H         |

| F00FEH  | BCD adjust result register                       | BCDADJ |       | R   | _            | $\checkmark$ | -      | Undefined   |

| F0100H  | Serial status register 00                        | SSR00L | SSR00 | R   | _            |              |        | 0000H       |

| F0101H  |                                                  | _      |       |     | _            | _            |        |             |

| F0102H  | Serial status register 01                        | SSR01L | SSR01 | R   | _            |              |        | 0000H       |

| F0103H  |                                                  | _      |       |     | _            | _            |        |             |

| F0104H  | Serial status register 02                        | SSR02L | SSR02 | R   | _            |              |        | 0000H       |

| F0105H  |                                                  | _      |       |     | _            | _            |        |             |

| F0106H  | Serial status register 03                        | SSR03L | SSR03 | R   | _            |              |        | 0000H       |

| F0107H  |                                                  | _      |       |     | _            | _            |        |             |

| F0108H  | Serial flag clear trigger register 00            | SIR00L | SIR00 | R/W | -            |              |        | 0000H       |

| F0109H  |                                                  | _      |       |     | _            | _            |        |             |

| F010AH  | Serial flag clear trigger register 01            | SIR01L | SIR01 | R/W | _            |              |        | 0000H       |

| F010BH  |                                                  | _      | 1     |     | _            | -            |        |             |

| F010CH  | Serial flag clear trigger register 02            | SIR02L | SIR02 | R/W | _            |              |        | 0000H       |

| F010DH  |                                                  | _      | 1     |     | _            | -            |        |             |

| F010EH  | Serial flag clear trigger register 03            | SIR03L | SIR03 | R/W | _            |              |        | 0000H       |

| F010FH  |                                                  | _      | -     |     | _            | _            |        |             |

| F0110H  | Serial mode register 00                          | SMR00  | 1     | R/W | _            | _            |        | 0020H       |

| F0111H  |                                                  |        |       |     |              |              |        |             |

| F0112H  | Serial mode register 01                          | SMR01  |       | R/W | -            | -            |        | 0020H       |

| F0113H  | Ť                                                |        |       |     |              |              |        |             |

| F0114H  | Serial mode register 02                          | SMR02  |       | R/W | _            | _            |        | 0020H       |

| F0115H  |                                                  |        |       |     |              |              |        |             |

| F0116H  | Serial mode register 03                          | SMR03  |       | R/W | _            | _            |        | 0020H       |

| F0117H  |                                                  |        |       |     |              |              |        |             |

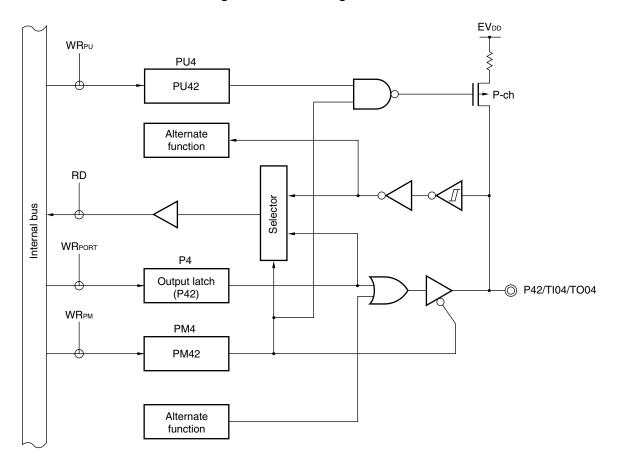

Figure 4-16. Block Diagram of P42

- P4: Port register 4

- PU4: Pull-up resistor option register 4

- PM4: Port mode register 4

- RD: Read signal

- WR××: Write signal

| ymbol | 7     | 6     | 5     | 4     | 3     | 2      | 1                                                | 0       |

|-------|-------|-------|-------|-------|-------|--------|--------------------------------------------------|---------|

| OTRM  | 0     | 0     | 0     | TTRM4 | TTRM3 | TTRM2  | TTRM1                                            | TTRMC   |

|       | TTRM4 | TTRM3 | TTRM2 | TTRM1 | TTRM0 | Cloc   | k correction v                                   | value   |

|       |       |       |       |       |       | (2.7   | $7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.8$ | 5 V)    |

|       |       |       |       |       |       | MIN.   | TYP.                                             | MAX.    |

|       | 0     | 0     | 0     | 0     | 0     | -5.54% | -4.88%                                           | -4.02%  |

|       | 0     | 0     | 0     | 0     | 1     | -5.28% | -4.62%                                           | -3.76%  |

|       | 0     | 0     | 0     | 1     | 0     | -4.99% | -4.33%                                           | -3.47%  |

|       | 0     | 0     | 0     | 1     | 1     | -4.69% | -4.03%                                           | -3.17%  |

|       | 0     | 0     | 1     | 0     | 0     | -4.39% | -3.73%                                           | -2.87%  |

|       | 0     | 0     | 1     | 0     | 1     | -4.09% | -3.43%                                           | -2.57%  |

|       | 0     | 0     | 1     | 1     | 0     | -3.79% | -3.13%                                           | -2.27%  |

|       | 0     | 0     | 1     | 1     | 1     | -3.49% | -2.83%                                           | -1.97%  |

|       | 0     | 1     | 0     | 0     | 0     | -3.19% | -2.53%                                           | -1.67%  |

|       | 0     | 1     | 0     | 0     | 1     | -2.88% | -2.22%                                           | -1.36%  |

|       | 0     | 1     | 0     | 1     | 0     | -2.23% | -1.91%                                           | -1.31%  |

|       | 0     | 1     | 0     | 1     | 1     | -1.92% | -1.60%                                           | -1.28%  |

|       | 0     | 1     | 1     | 0     | 0     | -1.60% | -1.28%                                           | -0.96.% |

|       | 0     | 1     | 1     | 0     | 1     | -1.28% | -0.96%                                           | -0.64%  |

|       | 0     | 1     | 1     | 1     | 0     | -0.96% | -0.64%                                           | -0.32%  |

|       | 0     | 1     | 1     | 1     | 1     | -0.64% | -0.32%                                           | ±0%     |

|       | 1     | 0     | 0     | 0     | 0     |        | ±0% (default)                                    |         |

|       | 1     | 0     | 0     | 0     | 1     | +0%    | +0.32%                                           | +0.64%  |

|       | 1     | 0     | 0     | 1     | 0     | +0.33% | +0.65%                                           | +0.97%  |

|       | 1     | 0     | 0     | 1     | 1     | +0.66% | +0.98%                                           | +1.30%  |

|       | 1     | 0     | 1     | 0     | 0     | +0.99% | +1.31%                                           | +1.63%  |

|       | 1     | 0     | 1     | 0     | 1     | +1.32% | +1.64%                                           | +1.96%  |

|       | 1     | 0     | 1     | 1     | 0     | +1.38% | +1.98%                                           | +2.30%  |

|       | 1     | 0     | 1     | 1     | 1     | +1.46% | +2.32%                                           | +2.98%  |

|       | 1     | 1     | 0     | 0     | 0     | +1.80% | +2.66%                                           | +3.32%  |

|       | 1     | 1     | 0     | 0     | 1     | +2.14% | +3.00%                                           | +3.66%  |

|       | 1     | 1     | 0     | 1     | 0     | +2.48% | +3.34%                                           | +4.00%  |

|       | 1     | 1     | 0     | 1     | 1     | +2.83% | +3.69%                                           | +4.35%  |

|       | 1     | 1     | 1     | 0     | 0     | +3.18% | +4.04%                                           | +4.70%  |

|       | 1     | 1     | 1     | 0     | 1     | +3.53% | +4.39%                                           | +5.05%  |

|       | 1     | 1     | 1     | 1     | 0     | +3.88% | +4.74%                                           | +5.40%  |

|       | 1     | 1     | 1     | 1     | 1     | +4.24% | +5.10%                                           | +5.76%  |

# Figure 5-9. Format of Internal High-Speed Oscillator Trimming Register (HIOTRM)

Caution The internal high-speed oscillation frequency becomes faster/slower by increasing/decreasing the HIOTRM value to a value larger/smaller than a certain value. A reversal, such as the frequency becoming slower/faster by increasing/decreasing the HIOTRM value does not occur.

# Table 5-4. CPU Clock Transition and SFR Register Setting Examples (3/4)

# (6) CPU clock changing from high-speed system clock (C) to internal high-speed oscillation clock (B)

| (Setting sequence of SFR registers) |              |                      |              |

|-------------------------------------|--------------|----------------------|--------------|

| Setting Flag of SFR Register        | CSC Register | Oscillation accuracy | CKC Register |

| Status Transition                   | HIOSTOP      | stabilization time   | MCM0         |

| $(C) \to (B)$                       | 0            | 10 <i>μ</i> s        | 0            |

|                                     |              | ,                    |              |

# (7) CPU clock changing from high-speed system clock (C) to subsystem clock (D)

| (Set              | ting sequence of SFR registers) |                              |              |                                         |              |

|-------------------|---------------------------------|------------------------------|--------------|-----------------------------------------|--------------|

|                   | Setting Flag of SFR Register    | CMC Register <sup>Note</sup> | CSC Register | Waiting for                             | CKC Register |

| Status Transition |                                 | OSCSELS                      | XTSTOP       | Oscillation<br>Stabilization            | CSS          |

| $(C) \to (D)$     |                                 | 1                            | 0            | Necessary                               | 1            |

|                   |                                 |                              |              | ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ |              |

Unnecessary if the CPU is operating with the subsystem clock

Note The CMC register can be written only once by an 8-bit memory manipulation instruction after reset release.

# (8) CPU clock changing from subsystem clock (D) to internal high-speed oscillation clock (B)

# (Setting sequence of SFR registers)

| Setting Flag of SFR Register | CSC Register | CKC R | legister |

|------------------------------|--------------|-------|----------|

| Status Transition            | HIOSTOP      | MCM0  | CSS      |

| $(D)\to(B)$                  | 0            | 0     | 0        |

Unnecessary if the CPU I is operating with the re internal high-speed oscillation clock

Unnecessary if this register is already set

**Remark** (A) to (I) in Table 5-4 correspond to (A) to (I) in Figure 5-15.

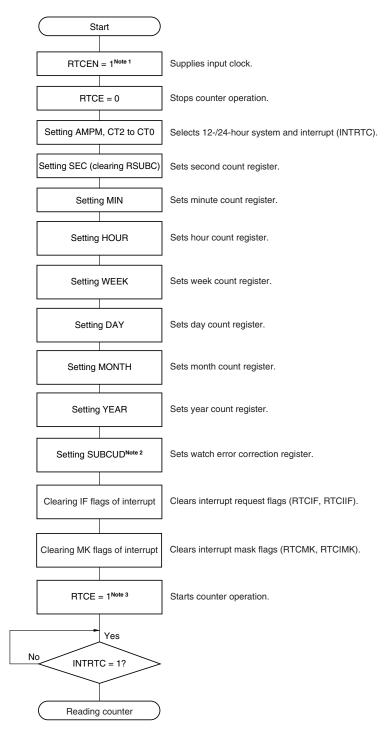

# 7.4 Real-Time Counter Operation

# 7.4.1 Starting operation of real-time counter

Notes 1. First set RTCEN to 1, while oscillation of the subsystem clock (fsub) is stable.

<R>

<R>

- 2. Set up SUBCUD only if the watch error must be corrected. For details about how to calculate the correction value, see 7.4.8 Example of watch error correction of real-time counter.

- 3. Confirm the procedure described in 7.4.2 Shifting to STOP mode after starting operation when shifting to STOP mode without waiting for INTRTC = 1 after RTCE = 1.

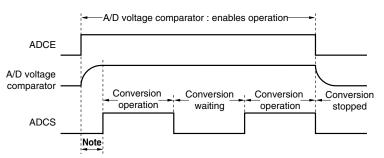

# (2) A/D converter mode register (ADM)

This register sets the conversion time for analog input to be A/D converted, and starts/stops conversion. ADM can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

# Figure 10-4. Format of A/D Converter Mode Register (ADM)

Address: FFF30H After reset: 00H R/W

| ADCS | A/D conversion operation control |  |  |  |

|------|----------------------------------|--|--|--|

| 0    | Stops conversion operation       |  |  |  |

| 1    | Enables conversion operation     |  |  |  |

| ADCE | A/D voltage comparator operation control <sup>Note 2</sup> |  |  |  |

|------|------------------------------------------------------------|--|--|--|

| 0    | Stops A/D voltage comparator operation                     |  |  |  |

| 1    | Enables A/D voltage comparator operation                   |  |  |  |

# Notes 1. For details of FR2 to FR0, LV1, LV0, and A/D conversion, see Table 10-3 A/D Conversion Time Selection.

2. The operation of the A/D voltage comparator is controlled by ADCS and ADCE, and it takes 1 µs from operation start to operation stabilization. Therefore, when ADCS is set to 1 after 1 µs or more has elapsed from the time ADCE is set to 1, the conversion result at that time has priority over the first conversion result. Otherwise, ignore data of the first conversion.

#### <R>

# Table 10-2. Settings of ADCS and ADCE

| ADCS | ADCE | A/D Conversion Operation                                             |  |  |  |

|------|------|----------------------------------------------------------------------|--|--|--|

| 0    | 0    | Stop status (DC power consumption path does not exist)               |  |  |  |

| 0    | 1    | Conversion waiting mode (only A/D voltage comparator consumes power) |  |  |  |

| 1    | 0    | Setting prohibited                                                   |  |  |  |

| 1    | 1    | Conversion mode (A/D voltage comparator: enables operation)          |  |  |  |

#### <R>

### Figure 10-5. Timing Chart When A/D voltage Comparator Is Used

- Note To stabilize the internal circuit, the time from the rising of the ADCE bit to the falling of the ADCS bit must be 1  $\mu$ s or longer.

- Caution A/D conversion must be stopped before rewriting bits FR0 to FR2, LV1, and LV0 to values other than the identical data.

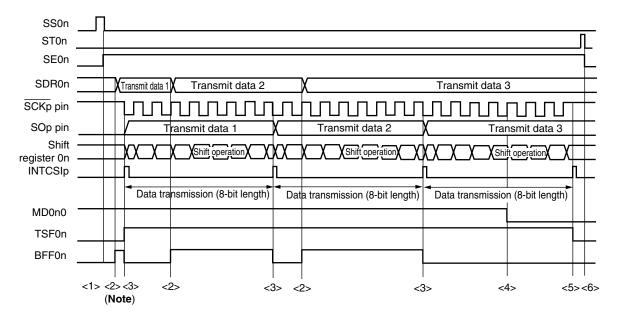

# (4) Processing flow (in continuous transmission mode)

Note When transmit data is written to the SDR0n register while BFF0n = 1, the transmit data is overwritten.

- Caution The MD0n0 bit can be rewritten even during operation. However, rewrite it before transfer of the last bit is started, so that it will be rewritten before the transfer end interrupt of the last transmit data.

- **Remark** n: Channel number (n = 0, 2), p: CSI number (p = 00, 10)

# 11.6.3 LIN transmission

Of UART transmission, UART3 supports LIN communication. For LIN transmission, channel 2 of unit 1 (SAU1) is used.

| UART                         | UART0                                                                                                                                               | UART1                               | UART3                            |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------|--|--|--|

| Support of LIN communication | Not supported                                                                                                                                       | Not supported                       | Supported                        |  |  |  |

| Target channel               | -                                                                                                                                                   | -                                   | Channel 2 of SAU1                |  |  |  |

| Pins used                    | -                                                                                                                                                   | -                                   | TxD3                             |  |  |  |

| Interrupt                    | _                                                                                                                                                   | _                                   | INTST3                           |  |  |  |

|                              | Transfer end interrupt (in single mode) can be selected.                                                                                            | e-transfer mode) or buffer empty in | nterrupt (in continuous transfer |  |  |  |

| Error detection flag         | None                                                                                                                                                |                                     |                                  |  |  |  |

| Transfer data length         | 8 bits                                                                                                                                              |                                     |                                  |  |  |  |

| Transfer rate                | Max. fмск/6 [bps] (SDR12 [15:9] = 2 or more), Min. fcLк/(2 × 2 <sup>11</sup> × 128) [bps] <sup>Note</sup>                                           |                                     |                                  |  |  |  |

| Data phase                   | Forward output (default: high level)<br>Reverse output (default: low level)                                                                         |                                     |                                  |  |  |  |

| Parity bit                   | The following selectable <ul> <li>No parity bit</li> <li>Appending 0 parity</li> <li>Appending even parity</li> <li>Appending odd parity</li> </ul> |                                     |                                  |  |  |  |

| Stop bit                     | The following selectable <ul> <li>Appending 1 bit</li> <li>Appending 2 bits</li> </ul>                                                              |                                     |                                  |  |  |  |

| Data direction               | MSB or LSB first                                                                                                                                    |                                     |                                  |  |  |  |

Note Use this operation within a range that satisfies the conditions above and the AC characteristics in the electrical specifications (see CHAPTER 27 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS) and CHAPTER 28 ELECTRICAL SPECIFICATIONS ((A) GRADE PRODUCTS)).

**Remark** fMCK: Operation clock (MCK) frequency of target channel

fclk: System clock frequency

LIN stands for Local Interconnect Network and is a low-speed (1 to 20 kbps) serial communication protocol designed to reduce the cost of an automobile network.

Communication of LIN is single-master communication and up to 15 slaves can be connected to one master.

The slaves are used to control switches, actuators, and sensors, which are connected to the master via LIN.

Usually, the master is connected to a network such as CAN (Controller Area Network).

A LIN bus is a single-wire bus to which nodes are connected via transceiver conforming to ISO9141.

According to the protocol of LIN, the master transmits a frame by attaching baud rate information to it. A slave receives this frame and corrects a baud rate error from the master. If the baud rate error of a slave is within  $\pm 15\%$ , communication can be established.

Figure 11-85 outlines a transmission operation of LIN.

# (2) Baud rate error during transmission

The baud rate error of UART (UART0, UART1, UART3) communication during transmission can be calculated by the following expression. Make sure that the baud rate at the transmission side is within the permissible baud rate range at the reception side.

(Baud rate error) = (Calculated baud rate value)  $\div$  (Target baud rate)  $\times$  100 – 100 [%]

Here is an example of setting a UART baud rate at  $f_{CLK} = 20$  MHz.

| UART Baud Rate     |                       | fo          | ськ <b>= 20 MHz</b>  |                             |

|--------------------|-----------------------|-------------|----------------------|-----------------------------|

| (Target Baud Rate) | Operation Clock (MCK) | SDRmn[15:9] | Calculated Baud Rate | Error from Target Baud Rate |

| 300 bps            | fclк/2 <sup>9</sup>   | 64          | 300.48 bps           | +0.16 %                     |

| 600 bps            | fc∟ĸ/2 <sup>8</sup>   | 64          | 600.96 bps           | +0.16 %                     |

| 1200 bps           | fclк/2 <sup>7</sup>   | 64          | 1201.92 bps          | +0.16 %                     |

| 2400 bps           | fclк/2 <sup>6</sup>   | 64          | 2403.85 bps          | +0.16 %                     |

| 4800 bps           | fc∟ĸ/2⁵               | 64          | 4807.69 bps          | +0.16 %                     |

| 9600 bps           | fc∟ĸ/2⁴               | 64          | 9615.38 bps          | +0.16 %                     |

| 19200 bps          | fclк/2³               | 64          | 19230.8 bps          | +0.16 %                     |

| 31250 bps          | fclк/2³               | 39          | 31250.0 bps          | ±0.0 %                      |

| 38400 bps          | fclk/2²               | 64          | 38461.5 bps          | +0.16 %                     |

| 76800 bps          | fclk/2                | 64          | 76923.1 bps          | +0.16 %                     |

| 153600 bps         | fclк                  | 64          | 153846 bps           | +0.16 %                     |

| 312500 bps         | fclк                  | 31          | 312500 bps           | ±0.0 %                      |

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0, 2), mn = 00, 02, 12

# (1) Register setting

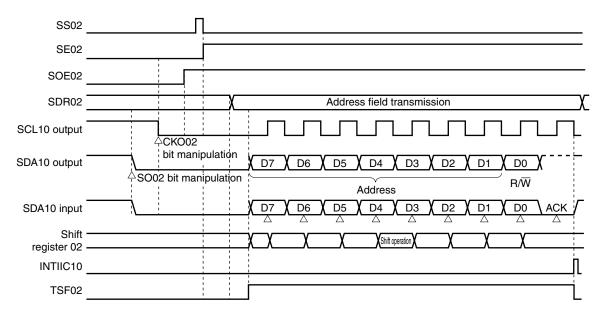

# Figure 11-93. Example of Contents of Registers for Address Field Transmission of Simplified I<sup>2</sup>C (IIC10)

| (a)   | Serial            | outpu             | ut regi    | ster 0             | (SO0)    | ) Se         | ets on      | ly the             | bits o                                  | f the t     | arget       | chanr       | nel.      |                     |                    |             |

|-------|-------------------|-------------------|------------|--------------------|----------|--------------|-------------|--------------------|-----------------------------------------|-------------|-------------|-------------|-----------|---------------------|--------------------|-------------|

|       | 15                | 14                | 13         | 12                 | 11       | 10           | 9           | 8                  | 7                                       | 6           | 5           | 4           | 3         | 2                   | 1                  | 0           |

| SO0   | 0                 | 0                 | 0          | 0                  | 1        | скоо2<br>0/1 | 1           | СКО00<br>×         | 0                                       | 0           | 0           | 0           | 1         | soo2<br>0/1         | 1                  | SO00<br>×   |

|       |                   | <u>.</u>          |            |                    |          | •<br>•       | Star        | t conditi          | on is g                                 | enerat      | ed by m     | nanipul     | ating th  | ne SO0              | 2 bit.             |             |

| (b)   | Serial            | outpu             | ıt enal    | ole reg            | gister   | 0 (SO        | E0)         | . Sets             | only t                                  | he bit      | s of th     | ne targ     | get ch    | annel.              |                    |             |

|       | 15                | 14                | 13         | 12                 | 11       | 10           | 9           | 8                  | 7                                       | 6           | 5           | 4           | 3         | 2                   | 1                  | 0           |

| SOE0  | 0                 | 0                 | 0          | 0                  | 0        | 0            | 0           | 0                  | 0                                       | 0           | 0           | 0           | 0         | SOE02<br>0/1        | 0                  | SOE00<br>×  |

|       |                   |                   |            |                    |          |              |             | :02 = 0<br>genera  |                                         | e start     | conditio    | on is ge    | enerate   | ed, and             | SOE02              | 2 = 1       |

| (c)   | Serial            | chanr             | nel sta    | rt reg             | ister (  | ) (SSC       | )) S        | ets on             | ly the                                  | bits o      | of the      | target      | chan      | nel is              | 1.                 |             |

|       | 15                | 14                | 13         | 12                 | 11       | 10           | 9           | 8                  | 7                                       | 6           | 5           | 4           | 3         | 2                   | 1                  | 0           |

| SS0   | 0                 | 0                 | 0          | 0                  | 0        | 0            | 0           | 0                  | 0                                       | 0           | 0           | 0           | SS03<br>× | sso2<br>0/1         | SS01<br>×          | SS00<br>×   |

| (d)   | Serial            | mode              | regis      | ter 02             | (SMR     | 102)         |             |                    |                                         |             |             |             |           |                     |                    |             |

|       | 15                | 14                | 13         | 12                 | 11       | 10           | 9           | 8                  | 7                                       | 6           | 5           | 4           | 3         | 2                   | 1                  | 0           |

| SMR02 | скѕо2<br>0/1      | CCS02<br>0        | 0          | 0                  | 0        | 0            | 0           | stso2<br>0         | 0                                       | SIS020<br>0 | 1           | 0           | 0         | MD022<br>1          | MD021<br>0         | MD020<br>0  |

|       |                   |                   |            |                    |          |              |             |                    |                                         |             |             |             |           | urces of<br>nd inte |                    | iel 2       |

| (e)   | Serial            | comn              | nunica     | tion c             | perat    | ion se       | ettina      | reaist             | er 02 (                                 | SCRO        | )2)         |             |           |                     |                    |             |

| ( )   | 15                | 14                | 13         | 12                 | 11       | 10           | 9           | 8                  | 7                                       | 6           | 5           | 4           | 3         | 2                   | 1                  | 0           |

| SCR02 | тхео2<br><b>1</b> | RXE02<br>0        | DAP02<br>0 | скро2<br>0         | 0        | EOC02<br>0   | PTC021<br>0 | ртсо20<br><b>О</b> | DIR02<br>0                              | 0           | SLC021<br>O | SLC020<br>1 | 0         | DLS022<br>1         | DLS021<br><b>1</b> | DLS020<br>1 |

|       | <u> </u>          | •                 |            | etting o<br>0B: No |          | / bit        |             |                    |                                         | <u> </u>    |             |             |           | ng of si<br>Appen   |                    | bit (ACK    |

| (f)   | Serial            | data ı            | registe    | er 02 (            | SDR0     | 2) (lov      | ver 8       | bits: S            | IO10)                                   |             |             |             |           |                     |                    |             |

| .,    | 15                | 14                | 13         | 12                 | 11       | 10           | 9           | 8                  | 7                                       | 6           | 5           | 4           | 3         | 2                   | 1                  | 0           |

| SDR02 |                   | Baud rate setting |            |                    |          |              |             |                    | 0 Transmit data setting (address + R/W) |             |             |             |           |                     |                    |             |

|       |                   |                   |            |                    |          |              |             |                    |                                         |             |             | SI          |           |                     |                    |             |

| Rer   | nark              | 🔲 : Se            | etting i   | s fixec            | l in the | e IIC m      | node,       | : Se               | tting d                                 | lisable     | d (set      | to the      | initial   | value)              |                    |             |

x: Bit that cannot be used in this mode (set to the initial value when not used in any mode) 0/1: Set to 0 or 1 depending on the usage of the user

# (3) Processing flow

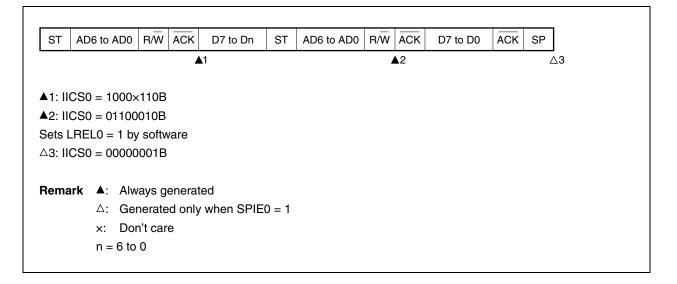

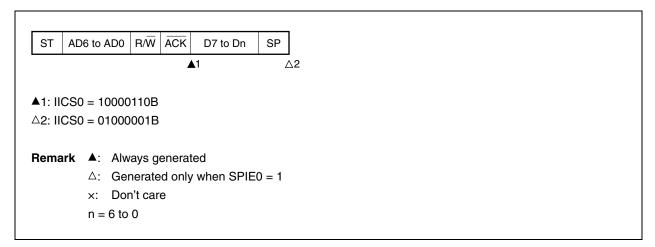

Figure 11-95. Timing Chart of Address Field Transmission

(ii) Extension code

(e) When loss occurs due to stop condition during data transfer

- (b) When LVI Default Start Function Enabled Is Set (Option Byte: LVIOFF = 0)

- When starting operation

- <1> Start in the following initial setting state.

- Set bit 7 (LVION) of LVIM to 1 (enables LVI operation)

- Clear bit 2 (LVISEL) of the low-voltage detection register (LVIM) to 0 (detects level of supply voltage (VDD))

- Set the low-voltage detection level selection register (LVIS) to 0EH (default value:  $V_{\text{LVI}}$  = 2.07 V  $\pm 0.1$  V ).

- Set bit 1 (LVIMD) of LVIM to 1 (generates reset when the level is detected)

- Set bit 0 (LVIF) of LVIM to 0 (Detects falling edge "Supply voltage (V\_DD)  $\geq$  detection voltage (V\_LVI)")

- <2> Clear bit 1 (LVIMD) of LVIM to 0 (generates interrupt signal when the level is detected) (default value).

- <3> Release the interrupt mask flag of LVI (LVIMK).

- <4> Execute the El instruction (when vector interrupts are used).

Figure 20-9 shows the timing of the interrupt signal generated by the low-voltage detector. The numbers in this timing chart correspond to <1> to <3> above.

- When stopping operation Either of the following procedures must be executed.

- When using 8-bit memory manipulation instruction: Write 00H to LVIM.

- When using 1-bit memory manipulation instruction: Clear LVION to 0.

- Cautions 1. Even when the LVI default start function is used, if it is set to LVI operation prohibition by the software, it operates as follows:

- Does not perform low-voltage detection during LVION = 0.

- If a reset is generated while LVION = 0, LVION will be re-set to 1 when the CPU starts after reset release. There is a period when low-voltage detection cannot be performed normally, however, when a reset occurs due to WDT and illegal instruction execution. This is due to the fact that while the pulse width detected by LVI must be 200 µs max., LVION = 1 is set upon reset occurrence, and the CPU starts operating without waiting for the LVI stabilization time.

- When the LVI default start function (bit 0 (LVIOFF) of 000C1H = 0) is used, the LVIRF flag may become 1 from the beginning due to the power-on waveform.

For details of RESF, see CHAPTER 18 RESET FUNCTION.

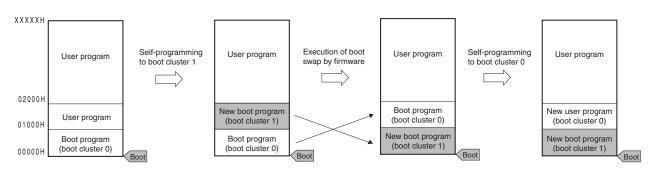

# 23.9.1 Boot swap function

If rewriting the boot area failed by temporary power failure or other reasons, restarting a program by resetting or overwriting is disabled due to data destruction in the boot area.

The boot swap function is used to avoid this problem.

Before erasing boot cluster 0<sup>Note</sup>, which is a boot program area, by self-programming, write a new boot program to boot cluster 1 in advance. When the program has been correctly written to boot cluster 1, swap this boot cluster 1 and boot cluster 0 by using the set information function of the firmware of the 78K0R/KE3, so that boot cluster 1 is used as a boot area. After that, erase or write the original boot program area, boot cluster 0.

As a result, even if a power failure occurs while the boot programming area is being rewritten, the program is executed correctly because it is booted from boot cluster 1 to be swapped when the program is reset and started next.

Note A boot cluster is a 4 KB area and boot clusters 0 and 1 are swapped by the boot swap function.

Figure 23-11. Boot Swap Function

In an example of above figure, it is as follows.

Boot cluster 0: Boot program area before boot swap Boot cluster 1: Boot program area after boot swap

# (A) Grade Products

| Manufacturer        | Part   | SMD/     | Frequency | Load Capacitance | Recomme | ended Circuit | Oscillation Voltage Range |          |          |

|---------------------|--------|----------|-----------|------------------|---------|---------------|---------------------------|----------|----------|

|                     | Number | Lead     | (kHz)     | CL (pF)          | C3 (pF) | C4 (pF)       | Rd (kΩ)                   | MIN. (V) | MAX. (V) |

| Seiko               | SP-T2A | SMD      | 32.768    | 6.0              | 5       | 5             | 0                         | 1.8      | 5.5      |

| Instruments         |        |          |           | 12.5             | 18      | 18            | 0                         |          |          |

| Inc.                | SSP-T7 | Small    |           | 7.0              | 7       | 7             | 0                         |          |          |

|                     |        | SMD      | -         | 12.5             | 18      | 18            | 0                         |          |          |

|                     | VT-200 | Lead     |           | 6.0              | 5       | 5             | 0                         |          |          |

|                     |        |          |           | 12.5             | 18      | 18            | 0                         |          |          |

| CITIZEN             | CM200S | SMD      | 32.768    | 9.0              | 12      | 15            | 0                         | 1.8      | 5.5      |

| FINETECH            |        |          |           |                  | 12      | 15            | 100                       | -        |          |

| MIYOTA CO.,<br>LTD. | CM315  | M315 SMD |           | 9.0              | 15      | 15            | 0                         |          |          |

|                     |        |          |           |                  | 15      | 15            | 100                       |          |          |

|                     | CM519  | SMD      |           | 9.0              | 15      | 12            | 0                         |          |          |

|                     |        |          |           |                  | 15      | 12            | 100                       |          |          |

# (5) XT1 oscillation: Crystal resonator ( $T_A = -40$ to +85°C)

- Caution The oscillator constants shown above are reference values based on evaluation in a specific environment by the resonator manufacturer. If it is necessary to optimize the oscillator characteristics in the actual application, apply to the resonator manufacturer for evaluation on the implementation circuit.

- When doing so, check the conditions for using the RMC register, and whether to enter or exit the STOP mode.

The oscillation voltage and oscillation frequency only indicate the oscillator characteristic. Use the 78K0R/KE3 so that the internal operation conditions are within the specifications of the DC and AC characteristics.

| Manufacturer        | Part       | SMD/ | Frequency | Load Capacitance<br>CL (pF) | Recomme | ended Circuit | Oscillation Voltage Range |          |          |

|---------------------|------------|------|-----------|-----------------------------|---------|---------------|---------------------------|----------|----------|

|                     | Number     | Lead | (kHz)     |                             | C3 (pF) | C4 (pF)       | Rd (kΩ)                   | MIN. (V) | MAX. (V) |

| CITIZEN             | CFS-206 Le | Lead | 32.768    | 9.0                         | 22      | 18            | 0                         | 0 1.8    |          |

| FINETECH            |            |      |           |                             | 22      | 18            | 100                       |          |          |

| MIYOTA CO.,<br>LTD. |            |      |           |                             | 12      | 15            | 0                         |          |          |

|                     |            |      |           |                             |         | 12            | 15                        | 100      |          |

(6) XT1 oscillation: Crystal resonator ( $T_A = -20$  to  $+70^{\circ}$ C)

Caution The oscillator constants shown above are reference values based on evaluation in a specific environment by the resonator manufacturer. If it is necessary to optimize the oscillator characteristics in the actual application, apply to the resonator manufacturer for evaluation on the implementation circuit.

When doing so, check the conditions for using the RMC register, and whether to enter or exit the STOP mode.

The oscillation voltage and oscillation frequency only indicate the oscillator characteristic. Use the 78K0R/KE3 so that the internal operation conditions are within the specifications of the DC and AC characteristics.

<R>

<R>

# (2) Serial interface: Serial array unit (14/18)

<R>

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

| Parameter                                         | Symbol        | (                                                                                                                                 | Conditions                      | MIN.            | TYP.            | MAX.            | Unit |

|---------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------|-----------------|-----------------|------|

| SCK10 cycle time                                  | <b>t</b> ксү2 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                                                                                            | 13.6 MHz < fмск                 | <b>10/f</b> мск |                 |                 | ns   |

|                                                   |               | $2.7~V \leq V_b \leq 4.0~V$                                                                                                       | 6.8 MHz < fмск ≤ 13.6 MHz       | 8/fмск          |                 |                 | ns   |

|                                                   |               |                                                                                                                                   | fмск ≤ 6.8 MHz                  | 6/fмск          |                 |                 | ns   |

|                                                   |               | $\begin{array}{l} 2.7 \ V \leq V_{DD} < 4.0 \ V, \\ 2.3 \ V \leq V_b \leq 2.7 \ V \end{array}$                                    | 18.5 MHz < fмск                 | <b>16/f</b> мск |                 |                 | ns   |

|                                                   |               |                                                                                                                                   | 14.8 MHz < fмск $\leq$ 18.5 MHz | <b>14/f</b> мск |                 |                 | ns   |

|                                                   |               |                                                                                                                                   | 11.1 MHz < fмск ≤ 14.8 MHz      | <b>12/f</b> мск |                 |                 | ns   |

|                                                   |               |                                                                                                                                   | 7.4 MHz < fмск ≤ 11.1 MHz       | <b>10/f</b> мск |                 |                 | ns   |

|                                                   |               |                                                                                                                                   | 3.7 MHz < fмск ≤ 7.4 MHz        | 8/fмск          |                 |                 | ns   |

|                                                   |               |                                                                                                                                   | fмск $\leq$ 3.7 MHz             | 6/fмск          |                 |                 | ns   |

| SCK10 high-/low-level                             | tкн2,         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                                                                                            | $2.7~V \leq V_b \leq 4.0~V$     | fксү2/2 – 20    |                 |                 | ns   |

| width                                             | tkl2          | $2.7~V \leq V_{\text{DD}} < 4.0~V,$                                                                                               | $2.3~V \leq V_b \leq 2.7~V$     | fксү2/2 – 35    |                 |                 | ns   |

| SI10 setup time<br>(to SCK10↑) <sup>Note 1</sup>  | tsik2         |                                                                                                                                   |                                 | 90              |                 |                 | ns   |

| SI10 hold time<br>(from SCK10↑) <sup>Note 2</sup> | tksi2         |                                                                                                                                   |                                 | 1/fмск + 50     |                 |                 | ns   |

| Delay time from<br>SCK10↓ to SO10                 | tkso2         | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} = 30 \ p\text{F}, \ R_{\text{b}} = 1.4 \end{array}$    |                                 |                 | 2/fмск +<br>120 | ns              |      |

| output <sup>Note 3</sup>                          |               | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V},$<br>$C_{\text{b}} = 30 \text{ pF}, \text{ R}_{\text{b}} = 2.7 \text{ V}$ |                                 |                 |                 | 2/fмск +<br>230 | ns   |

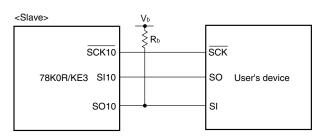

(g) During communication at different potential (2.5 V, 3 V) (CSI mode) (slave mode, SCK10... external clock input)

- Notes 1. When DAP02 = 0 and CKP02 = 0, or DAP02 = 1 and CKP02 = 1. The SI10 setup time becomes "to  $\overline{SCK10}\downarrow$ " when DAP02 = 0 and CKP02 = 1, or DAP02 = 1 and CKP02 = 0.

- **2.** When DAP02 = 0 and CKP02 = 0, or DAP02 = 1 and CKP02 = 1. The SI10 hold time becomes "from  $\overline{SCK10}\downarrow$ " when DAP02 = 0 and CKP02 = 1, or DAP02 = 1 and CKP02 = 0.

- **3.** When DAP02 = 0 and CKP02 = 0, or DAP02 = 1 and CKP02 = 1. The delay time to SO10 output becomes "from  $\overline{SCK10}$ <sup>↑</sup>" when DAP02 = 0 and CKP02 = 1, or DAP02 = 1 and CKP02 = 0.

# CSI mode connection diagram (during communication at different potential)

(Caution and Remark are given on the next page.)

|           |                   |                        |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (2/3         | 33) |  |  |  |

|-----------|-------------------|------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|--|--|--|

| Chapter   | Classification    | Function               | Details of<br>Function                                                                         | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |     |  |  |  |

| Chapter 3 | Soft              | Memory<br>space        | Internal data<br>memory space                                                                  | It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space for fetching instructions or as a stack area.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | p.56         |     |  |  |  |

| Chal      |                   |                        |                                                                                                | While using the self-programming function, the area of FFE20H to FFEFFH cannot be used as a stack memory. Furthermore, the areas of FCF00H to FD6FFH cannot be used with the $\mu$ PD78F1146 and 78F1146A.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | p.56         |     |  |  |  |

|           |                   |                        | SFR: Special<br>function register<br>area                                                      | Do not access addresses to which SFRs are not assigned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | pp.57,<br>68 |     |  |  |  |

|           |                   |                        | 2nd SFR:<br>Extended<br>special function<br>register                                           | Do not access addresses to which extended SFR is not assigned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | pp.57,<br>74 |     |  |  |  |

|           |                   | Processor<br>registers | SP: Stack<br>pointer                                                                           | Since reset signal generation makes the SP contents undefined, be sure to initialize the SP before using the stack.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | p.64         |     |  |  |  |

|           |                   |                        |                                                                                                | The values of the stack pointer must be set to even numbers. If odd numbers are specified, the least significant bit is automatically cleared to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | p.64         |     |  |  |  |

|           |                   |                        | It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space as a stack area. | p.64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |     |  |  |  |

|           |                   |                        |                                                                                                | While using the self-programming function, the area of FFE20H to FFEFFH cannot be used as a stack memory. Furthermore, the areas of FCF00H to FD6FFH cannot be used with the $\mu$ PD78F1146 and 78F1146A.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | p.64         |     |  |  |  |

|           |                   |                        | General-purpose<br>registers                                                                   | It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space for fetching instructions or as a stack area.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | p.65         |     |  |  |  |

| Chapter 4 | Fort<br>functions |                        | P01/TO00,<br>P05/TI05/TO05,<br>P06/TI06/TO06                                                   | To use P01/TO00, P05/TI05/TO05, or P06/TI06/TO06 as a general-purpose port, set bits 0, 5,and 6 (TO00, TO05, TO06) of timer output register 0 (TO0) and bits 0, 5, and 6 (TOE00, TOE05,TOE06) of timer output enable register 0 (TOE0) to "0", which is the same as their default status setting.                                                                                                                                                                                                                                                                                                                                                                  | p.96         |     |  |  |  |

|           |                   |                        | P02/SO10/TxD1,<br>P03/SI10/RxD1/<br>SDA10,<br>P04/SCK10/<br>SCL10                              | <ul> <li>To use P02/SO10/TxD1, P03/SI10/RxD1/SDA10, or P04/SCK10/SCL10 as a general-purpose port, note the serial array unit 0 setting. For details, refer to the following tables.</li> <li>Table 11-7 Relationship Between Register Settings and Pins (Channel 2 of Unit 0: CSI10, UART1 Transmission, IIC10)</li> <li>Table 11-8 Relationship Between Register Settings and Pins (Channel 3 of Unit 0: UART1 Reception)</li> </ul>                                                                                                                                                                                                                              | p.96         |     |  |  |  |

|           |                   |                        | P10/SCK00/,<br>P11/SI00/RxD0,<br>P12/SO00/TxD0<br>P13/TxD3,<br>P14/RxD3                        | <ul> <li>To use P10/SCK00, P11/SI00/RxD0, P12/SO00/TxD0, P13/TxD3, or P14/RxD3 as a general-purpose port, note the serial array unit setting. For details, refer to the following tables.</li> <li>Table 11-5 Relationship Between Register Settings and Pins (Channel 0 of Unit 0: CSI00, UART0 Transmission)</li> <li>Table 11-6 Relationship Between Register Settings and Pins (Channel 1 of Unit 0:, UART0 Reception)</li> <li>Table 11-9 Relationship Between Register Settings and Pins (Channel 2 of Unit 1: UART3 Transmission)</li> <li>Table 11-10 Relationship Between Register Settings and Pins (Channel 2 of Unit 1: UART3 Transmission)</li> </ul> | p.101        |     |  |  |  |