# E·XFL

# Intel - EPF10K100EFC256-1 Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

# Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 624                                                          |

| Number of Logic Elements/Cells | 4992                                                         |

| Total RAM Bits                 | 49152                                                        |

| Number of I/O                  | 191                                                          |

| Number of Gates                | 257000                                                       |

| Voltage - Supply               | 2.375V ~ 2.625V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                              |

| Package / Case                 | 256-LBGA                                                     |

| Supplier Device Package        | 256-BGA (27x27)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k100efc256-1 |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Functional Description

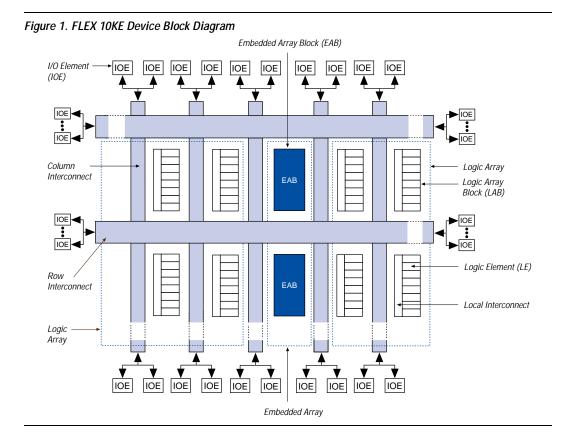

Each FLEX 10KE device contains an enhanced embedded array to implement memory and specialized logic functions, and a logic array to implement general logic.

The embedded array consists of a series of EABs. When implementing memory functions, each EAB provides 4,096 bits, which can be used to create RAM, ROM, dual-port RAM, or first-in first-out (FIFO) functions. When implementing logic, each EAB can contribute 100 to 600 gates towards complex logic functions, such as multipliers, microcontrollers, state machines, and DSP functions. EABs can be used independently, or multiple EABs can be combined to implement larger functions.

The logic array consists of logic array blocks (LABs). Each LAB contains eight LEs and a local interconnect. An LE consists of a four-input look-up table (LUT), a programmable flipflop, and dedicated signal paths for carry and cascade functions. The eight LEs can be used to create medium-sized blocks of logic—such as 8-bit counters, address decoders, or state machines—or combined across LABs to create larger logic blocks. Each LAB represents about 96 usable gates of logic.

Signal interconnections within FLEX 10KE devices (as well as to and from device pins) are provided by the FastTrack Interconnect routing structure, which is a series of fast, continuous row and column channels that run the entire length and width of the device.

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect routing structure. Each IOE contains a bidirectional I/O buffer and a flipflop that can be used as either an output or input register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. As inputs, they provide setup times as low as 0.9 ns and hold times of 0 ns. As outputs, these registers provide clock-to-output times as low as 3.0 ns. IOEs provide a variety of features, such as JTAG BST support, slew-rate control, tri-state buffers, and open-drain outputs. Figure 1 shows a block diagram of the FLEX 10KE architecture. Each group of LEs is combined into an LAB; groups of LABs are arranged into rows and columns. Each row also contains a single EAB. The LABs and EABs are interconnected by the FastTrack Interconnect routing structure. IOEs are located at the end of each row and column of the FastTrack Interconnect routing structure.

FLEX 10KE devices provide six dedicated inputs that drive the flipflops' control inputs and ensure the efficient distribution of high-speed, low-skew (less than 1.5 ns) control signals. These signals use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect routing structure. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device.

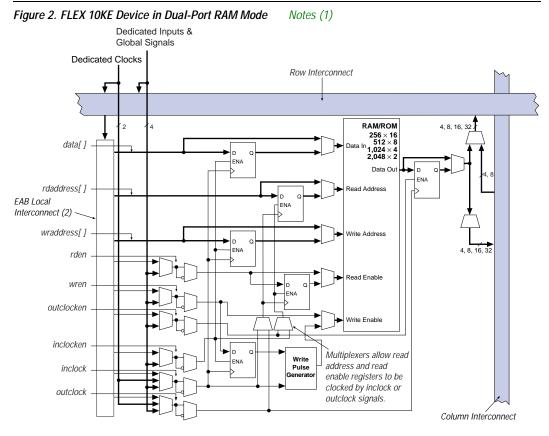

The EAB can also be used for bidirectional, dual-port memory applications where two ports read or write simultaneously. To implement this type of dual-port memory, two EABs are used to support two simultaneous read or writes.

Alternatively, one clock and clock enable can be used to control the input registers of the EAB, while a different clock and clock enable control the output registers (see Figure 2).

#### Notes:

- (1) All registers can be asynchronously cleared by EAB local interconnect signals, global signals, or the chip-wide reset.

- (2) EPF10K30E and EPF10K50E devices have 88 EAB local interconnect channels; EPF10K100E, EPF10K130E, and EPF10K200E devices have 104 EAB local interconnect channels.

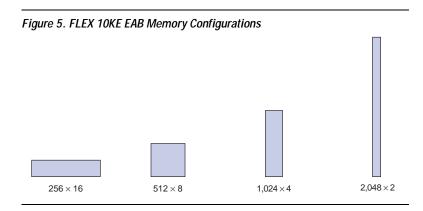

When used as RAM, each EAB can be configured in any of the following sizes:  $256 \times 16$ ,  $512 \times 8$ ,  $1,024 \times 4$ , or  $2,048 \times 2$  (see Figure 5).

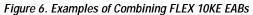

Larger blocks of RAM are created by combining multiple EABs. For example, two  $256 \times 16$  RAM blocks can be combined to form a  $256 \times 32$  block; two  $512 \times 8$  RAM blocks can be combined to form a  $512 \times 16$  block (see Figure 6).

If necessary, all EABs in a device can be cascaded to form a single RAM block. EABs can be cascaded to form RAM blocks of up to 2,048 words without impacting timing. The Altera software automatically combines EABs to meet a designer's RAM specifications.

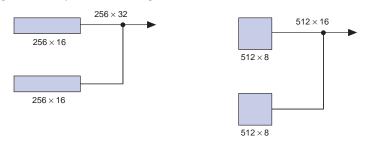

Figure 9 shows how an *n*-bit full adder can be implemented in n + 1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for an accumulator function. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it can be used as a general-purpose signal.

Figure 9. FLEX 10KE Carry Chain Operation (n-Bit Full Adder)

# FastTrack Interconnect Routing Structure

In the FLEX 10KE architecture, connections between LEs, EABs, and device I/O pins are provided by the FastTrack Interconnect routing structure, which is a series of continuous horizontal and vertical routing channels that traverses the device. This global routing structure provides predictable performance, even in complex designs. In contrast, the segmented routing in FPGAs requires switch matrices to connect a variable number of routing paths, increasing the delays between logic resources and reducing performance.

The FastTrack Interconnect routing structure consists of row and column interconnect channels that span the entire device. Each row of LABs is served by a dedicated row interconnect. The row interconnect can drive I/O pins and feed other LABs in the row. The column interconnect routes signals between rows and can drive I/O pins.

Row channels drive into the LAB or EAB local interconnect. The row signal is buffered at every LAB or EAB to reduce the effect of fan-out on delay. A row channel can be driven by an LE or by one of three column channels. These four signals feed dual 4-to-1 multiplexers that connect to two specific row channels. These multiplexers, which are connected to each LE, allow column channels to drive row channels even when all eight LEs in a LAB drive the row interconnect.

Each column of LABs or EABs is served by a dedicated column interconnect. The column interconnect that serves the EABs has twice as many channels as other column interconnects. The column interconnect can then drive I/O pins or another row's interconnect to route the signals to other LABs or EABs in the device. A signal from the column interconnect, which can be either the output of a LE or an input from an I/O pin, must be routed to the row interconnect before it can enter a LAB or EAB. Each row channel that is driven by an IOE or EAB can drive one specific column channel.

Access to row and column channels can be switched between LEs in adjacent pairs of LABs. For example, a LE in one LAB can drive the row and column channels normally driven by a particular LE in the adjacent LAB in the same row, and vice versa. This flexibility enables routing resources to be used more efficiently (see Figure 13).

| Peripheral<br>Control Signal | EPF10K100E | EPF10K130E | EPF10K200E<br>EPF10K200S |  |

|------------------------------|------------|------------|--------------------------|--|

| OE0                          | Row A      | Row C      | Row G                    |  |

| OE1                          | Row C      | Row E      | Row I                    |  |

| OE2                          | Row E      | Row G      | Row K                    |  |

| OE 3                         | Row L      | Row N      | Row R                    |  |

| OE4                          | Row I      | Row K      | Row O                    |  |

| OE5                          | Row K      | Row M      | Row Q                    |  |

| CLKENA0/CLK0/GLOBAL0         | Row F      | Row H      | Row L                    |  |

| CLKENA1/OE6/GLOBAL1          | Row D      | Row F      | Row J                    |  |

| CLKENA2/CLR0                 | Row B      | Row D      | Row H                    |  |

| CLKENA3/OE7/GLOBAL2          | Row H      | Row J      | Row N                    |  |

| CLKENA4/CLR1                 | Row J      | Row L      | Row P                    |  |

| CLKENA5/CLK1/GLOBAL3         | Row G      | Row I      | Row M                    |  |

Signals on the peripheral control bus can also drive the four global signals, referred to as GLOBAL0 through GLOBAL3 in Tables 8 and 9. An internally generated signal can drive a global signal, providing the same low-skew, low-delay characteristics as a signal driven by an input pin. An LE drives the global signal by driving a row line that drives the peripheral bus, which then drives the global signal. This feature is ideal for internally generated clear or clock signals with high fan-out. However, internally driven global signals offer no advantage over the general-purpose interconnect for routing data signals. The dedicated input pin should be driven to a known logic state (such as ground) and not be allowed to float.

The chip-wide output enable pin is an active-high pin (DEV\_OE) that can be used to tri-state all pins on the device. This option can be set in the Altera software. On EPF10K50E and EPF10K200E devices, the built-in I/O pin pull-up resistors (which are active during configuration) are active when the chip-wide output enable pin is asserted. The registers in the IOE can also be reset by the chip-wide reset pin.

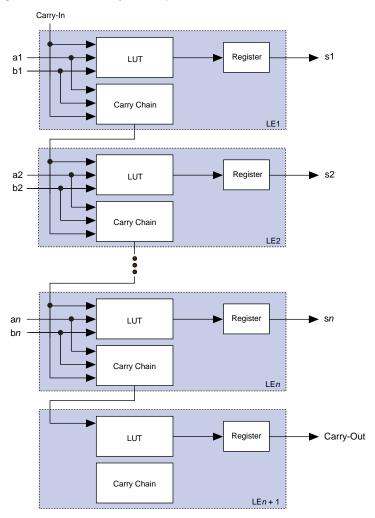

Row-to-IOE Connections

When an IOE is used as an input signal, it can drive two separate row channels. The signal is accessible by all LEs within that row. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the row channels. Up to eight IOEs connect to each side of each row channel (see Figure 16).

# Figure 16. FLEX 10KE Row-to-IOE Connections The values for m and n are provided in Table 10.

m loe1

| Table 10 lists the FLEX 10KE row-to-IOE interco | onnect resources. |

|-------------------------------------------------|-------------------|

|-------------------------------------------------|-------------------|

| Table 10. FLEX 10KE Row-to-IOE Interconnect Resources |                      |                          |  |  |  |  |  |  |

|-------------------------------------------------------|----------------------|--------------------------|--|--|--|--|--|--|

| Device                                                | Channels per Row (n) | Row Channels per Pin (m) |  |  |  |  |  |  |

| EPF10K30E                                             | 216                  | 27                       |  |  |  |  |  |  |

| EPF10K50E                                             | 216                  | 27                       |  |  |  |  |  |  |

| EPF10K50S                                             |                      |                          |  |  |  |  |  |  |

| EPF10K100E                                            | 312                  | 39                       |  |  |  |  |  |  |

| EPF10K130E                                            | 312                  | 39                       |  |  |  |  |  |  |

| EPF10K200E                                            | 312                  | 39                       |  |  |  |  |  |  |

| EPF10K200S                                            |                      |                          |  |  |  |  |  |  |

$\bigcirc$

Column-to-IOE Connections

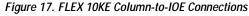

When an IOE is used as an input, it can drive up to two separate column channels. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the column channels. Two IOEs connect to each side of the column channels. Each IOE can be driven by column channels via a multiplexer. The set of column channels is different for each IOE (see Figure 17).

The values for m and n are provided in Table 11.

### Table 11 lists the FLEX 10KE column-to-IOE interconnect resources.

| Table 11. FLEX 10KE Column-to-IOE Interconnect Resources |                         |                             |  |  |  |  |  |  |

|----------------------------------------------------------|-------------------------|-----------------------------|--|--|--|--|--|--|

| Device                                                   | Channels per Column (n) | Column Channels per Pin (m) |  |  |  |  |  |  |

| EPF10K30E                                                | 24                      | 16                          |  |  |  |  |  |  |

| EPF10K50E<br>EPF10K50S                                   | 24                      | 16                          |  |  |  |  |  |  |

| EPF10K100E                                               | 24                      | 16                          |  |  |  |  |  |  |

| EPF10K130E                                               | 32                      | 24                          |  |  |  |  |  |  |

| EPF10K200E<br>EPF10K200S                                 | 48                      | 40                          |  |  |  |  |  |  |

The VCCINT pins must always be connected to a 2.5-V power supply. With a 2.5-V V<sub>CCINT</sub> level, input voltages are compatible with 2.5-V, 3.3-V, and 5.0-V inputs. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is at 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with V<sub>CCIO</sub> levels higher than 3.0 V achieve a faster timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ .

| Table 14. FLEX 10KE MultiVolt I/O Support |                                    |              |      |                      |              |              |  |  |  |

|-------------------------------------------|------------------------------------|--------------|------|----------------------|--------------|--------------|--|--|--|

| V <sub>CCIO</sub> (V)                     | Input Signal (V) Output Signal (V) |              |      |                      |              |              |  |  |  |

|                                           | 2.5                                | 3.3          | 5.0  | 2.5                  | 3.3          | 5.0          |  |  |  |

| 2.5                                       | $\checkmark$                       | ✓(1)         | ✓(1) | <ul> <li></li> </ul> |              |              |  |  |  |

| 3.3                                       | ~                                  | $\checkmark$ | ✓(1) | <b>√</b> (2)         | $\checkmark$ | $\checkmark$ |  |  |  |

Table 14 summarizes FLEX 10KE MultiVolt I/O support.

#### Notes:

(1) The PCI clamping diode must be disabled to drive an input with voltages higher than  $V_{\rm CCIO}$ .

(2) When  $V_{CCIO}$  = 3.3 V, a FLEX 10KE device can drive a 2.5-V device that has 3.3-V tolerant inputs.

Open-drain output pins on FLEX 10KE devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a  $V_{\rm IH}$  of 3.5 V. When the open-drain pin is active, it will drive low. When the pin is inactive, the trace will be pulled up to 5.0 V by the resistor. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The I<sub>OL</sub> current specification should be considered when selecting a pull-up resistor.

### Power Sequencing & Hot-Socketing

Because FLEX 10KE devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  power planes can be powered in any order.

Signals can be driven into FLEX 10KE devices before and during power up without damaging the device. Additionally, FLEX 10KE devices do not drive out during power up. Once operating conditions are reached, FLEX 10KE devices operate as specified by the user.

| Table 27. EAE          | 3 Timing Macroparameters Note (1), (6)                                                  |            |  |  |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------|------------|--|--|--|--|--|--|

| Symbol                 | Parameter                                                                               | Conditions |  |  |  |  |  |  |

| t <sub>EABAA</sub>     | EAB address access delay                                                                |            |  |  |  |  |  |  |

| t <sub>EABRCCOMB</sub> | EAB asynchronous read cycle time                                                        |            |  |  |  |  |  |  |

| t <sub>EABRCREG</sub>  | EAB synchronous read cycle time                                                         |            |  |  |  |  |  |  |

| t <sub>EABWP</sub>     | EAB write pulse width                                                                   |            |  |  |  |  |  |  |

| t <sub>EABWCCOMB</sub> | EAB asynchronous write cycle time                                                       |            |  |  |  |  |  |  |

| t <sub>EABWCREG</sub>  | EAB synchronous write cycle time                                                        |            |  |  |  |  |  |  |

| t <sub>EABDD</sub>     | EAB data-in to data-out valid delay                                                     |            |  |  |  |  |  |  |

| t <sub>EABDATACO</sub> | EAB clock-to-output delay when using output registers                                   |            |  |  |  |  |  |  |

| t <sub>EABDATASU</sub> | EAB data/address setup time before clock when using input register                      |            |  |  |  |  |  |  |

| t <sub>EABDATAH</sub>  | EAB data/address hold time after clock when using input register                        |            |  |  |  |  |  |  |

| t <sub>EABWESU</sub>   | EAB WE setup time before clock when using input register                                |            |  |  |  |  |  |  |

| t <sub>EABWEH</sub>    | EAB WE hold time after clock when using input register                                  |            |  |  |  |  |  |  |

| t <sub>EABWDSU</sub>   | EAB data setup time before falling edge of write pulse when not using input registers   |            |  |  |  |  |  |  |

| t <sub>EABWDH</sub>    | EAB data hold time after falling edge of write pulse when not using input registers     |            |  |  |  |  |  |  |

| t <sub>EABWASU</sub>   | EAB address setup time before rising edge of write pulse when not using input registers |            |  |  |  |  |  |  |

| t <sub>EABWAH</sub>    | EAB address hold time after falling edge of write pulse when not using input registers  |            |  |  |  |  |  |  |

| t <sub>EABWO</sub>     | EAB write enable to data output valid delay                                             |            |  |  |  |  |  |  |

| Symbol             | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|--------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                    | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>CGENR</sub> |                | 0.1 |                | 0.1 |                | 0.2 | ns   |

| t <sub>CASC</sub>  |                | 0.6 |                | 0.8 |                | 1.0 | ns   |

| t <sub>C</sub>     |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>CO</sub>    |                | 0.3 |                | 0.4 |                | 0.5 | ns   |

| t <sub>COMB</sub>  |                | 0.4 |                | 0.4 |                | 0.6 | ns   |

| t <sub>SU</sub>    | 0.4            |     | 0.6            |     | 0.6            |     | ns   |

| t <sub>H</sub>     | 0.7            |     | 1.0            |     | 1.3            |     | ns   |

| t <sub>PRE</sub>   |                | 0.8 |                | 0.9 |                | 1.2 | ns   |

| t <sub>CLR</sub>   |                | 0.8 |                | 0.9 |                | 1.2 | ns   |

| t <sub>CH</sub>    | 2.0            |     | 2.5            |     | 2.5            |     | ns   |

| t <sub>CL</sub>    | 2.0            |     | 2.5            |     | 2.5            |     | ns   |

| Symbol              | -1 Spee | ed Grade | -2 Speed Grade |     | -3 Spee | ed Grade | Unit |

|---------------------|---------|----------|----------------|-----|---------|----------|------|

|                     | Min     | Max      | Min            | Max | Min     | Max      |      |

| t <sub>IOD</sub>    |         | 2.4      |                | 2.8 |         | 3.8      | ns   |

| t <sub>IOC</sub>    |         | 0.3      |                | 0.4 |         | 0.5      | ns   |

| t <sub>IOCO</sub>   |         | 1.0      |                | 1.1 |         | 1.6      | ns   |

| t <sub>IOCOMB</sub> |         | 0.0      |                | 0.0 |         | 0.0      | ns   |

| t <sub>IOSU</sub>   | 1.2     |          | 1.4            |     | 1.9     |          | ns   |

| t <sub>IOH</sub>    | 0.3     |          | 0.4            |     | 0.5     |          | ns   |

| t <sub>IOCLR</sub>  |         | 1.0      |                | 1.1 |         | 1.6      | ns   |

| t <sub>OD1</sub>    |         | 1.9      |                | 2.3 |         | 3.0      | ns   |

| t <sub>OD2</sub>    |         | 1.4      |                | 1.8 |         | 2.5      | ns   |

| t <sub>OD3</sub>    |         | 4.4      |                | 5.2 |         | 7.0      | ns   |

| t <sub>XZ</sub>     |         | 2.7      |                | 3.1 |         | 4.3      | ns   |

| t <sub>ZX1</sub>    |         | 2.7      |                | 3.1 |         | 4.3      | ns   |

| t <sub>ZX2</sub>    |         | 2.2      |                | 2.6 |         | 3.8      | ns   |

| t <sub>ZX3</sub>    |         | 5.2      |                | 6.0 |         | 8.3      | ns   |

| t <sub>INREG</sub>  |         | 3.4      |                | 4.1 |         | 5.5      | ns   |

| t <sub>IOFD</sub>   |         | 0.8      |                | 1.3 |         | 2.4      | ns   |

| t <sub>INCOMB</sub> |         | 0.8      |                | 1.3 |         | 2.4      | ns   |

| Symbol                  | -1 Spee | d Grade | -2 Speed Grade |     | -3 Spee | ed Grade | Unit |

|-------------------------|---------|---------|----------------|-----|---------|----------|------|

|                         | Min     | Max     | Min            | Max | Min     | Max      |      |

| t <sub>DIN2IOE</sub>    |         | 1.8     |                | 2.4 |         | 2.9      | ns   |

| t <sub>DIN2LE</sub>     |         | 1.5     |                | 1.8 |         | 2.4      | ns   |

| t <sub>DIN2DATA</sub>   |         | 1.5     |                | 1.8 |         | 2.2      | ns   |

| t <sub>DCLK2IOE</sub>   |         | 2.2     |                | 2.6 |         | 3.0      | ns   |

| t <sub>DCLK2LE</sub>    |         | 1.5     |                | 1.8 |         | 2.4      | ns   |

| t <sub>SAMELAB</sub>    |         | 0.1     |                | 0.2 |         | 0.3      | ns   |

| t <sub>SAMEROW</sub>    |         | 2.0     |                | 2.4 |         | 2.7      | ns   |

| t <sub>SAMECOLUMN</sub> |         | 0.7     |                | 1.0 |         | 0.8      | ns   |

| t <sub>DIFFROW</sub>    |         | 2.7     |                | 3.4 |         | 3.5      | ns   |

| t <sub>TWOROWS</sub>    |         | 4.7     |                | 5.8 |         | 6.2      | ns   |

| t <sub>LEPERIPH</sub>   |         | 2.7     |                | 3.4 |         | 3.8      | ns   |

| t <sub>LABCARRY</sub>   |         | 0.3     |                | 0.4 |         | 0.5      | ns   |

| t <sub>LABCASC</sub>    |         | 0.8     |                | 0.8 |         | 1.1      | ns   |

| Symbol                            | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | ed Grade | Unit |

|-----------------------------------|---------|----------------|-----|----------------|-----|----------|------|

|                                   | Min     | Max            | Min | Max            | Min | Max      |      |

| t <sub>DRR</sub>                  |         | 8.0            |     | 9.5            |     | 12.5     | ns   |

| t <sub>INSU</sub> (3)             | 2.1     |                | 2.5 |                | 3.9 |          | ns   |

| t <sub>INH</sub> (3)              | 0.0     |                | 0.0 |                | 0.0 |          | ns   |

| <sup>t</sup> оитсо <sup>(3)</sup> | 2.0     | 4.9            | 2.0 | 5.9            | 2.0 | 7.6      | ns   |

| t <sub>INSU</sub> (4)             | 1.1     |                | 1.5 |                | -   |          | ns   |

| t <sub>INH</sub> (4)              | 0.0     |                | 0.0 |                | -   |          | ns   |

| t <sub>оитсо</sub> (4)            | 0.5     | 3.9            | 0.5 | 4.9            | -   | -        | ns   |

| t <sub>PCISU</sub>                | 3.0     |                | 4.2 |                | -   |          | ns   |

| t <sub>PCIH</sub>                 | 0.0     |                | 0.0 |                | -   |          | ns   |

| t <sub>PCICO</sub>                | 2.0     | 6.0            | 2.0 | 7.5            | _   | -        | ns   |

| Table 38. EPF10K50E Device LE Timing Microparameters (Part 2 of 2)       Note (1) |                |     |                |     |                |     |      |  |

|-----------------------------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|

| Symbol                                                                            | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |

|                                                                                   | Min            | Max | Min            | Max | Min            | Max |      |  |

| t <sub>H</sub>                                                                    | 0.9            |     | 1.0            |     | 1.4            |     | ns   |  |

| t <sub>PRE</sub>                                                                  |                | 0.5 |                | 0.6 |                | 0.8 | ns   |  |

| t <sub>CLR</sub>                                                                  |                | 0.5 |                | 0.6 |                | 0.8 | ns   |  |

| t <sub>CH</sub>                                                                   | 2.0            |     | 2.5            |     | 3.0            |     | ns   |  |

| t <sub>CL</sub>                                                                   | 2.0            |     | 2.5            |     | 3.0            |     | ns   |  |

| Table 39. EPF10     | 1              |     | -<br>I         |     | te (1)         | i   |      |

|---------------------|----------------|-----|----------------|-----|----------------|-----|------|

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|                     | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>IOD</sub>    |                | 2.2 |                | 2.4 |                | 3.3 | ns   |

| t <sub>IOC</sub>    |                | 0.3 |                | 0.3 |                | 0.5 | ns   |

| t <sub>IOCO</sub>   |                | 1.0 |                | 1.0 |                | 1.4 | ns   |

| t <sub>IOCOMB</sub> |                | 0.0 |                | 0.0 |                | 0.2 | ns   |

| t <sub>IOSU</sub>   | 1.0            |     | 1.2            |     | 1.7            |     | ns   |

| t <sub>IOH</sub>    | 0.3            |     | 0.3            |     | 0.5            |     | ns   |

| t <sub>IOCLR</sub>  |                | 0.9 |                | 1.0 |                | 1.4 | ns   |

| t <sub>OD1</sub>    |                | 0.8 |                | 0.9 |                | 1.2 | ns   |

| t <sub>OD2</sub>    |                | 0.3 |                | 0.4 |                | 0.7 | ns   |

| t <sub>OD3</sub>    |                | 3.0 |                | 3.5 |                | 3.5 | ns   |

| t <sub>XZ</sub>     |                | 1.4 |                | 1.7 |                | 2.3 | ns   |

| t <sub>ZX1</sub>    |                | 1.4 |                | 1.7 |                | 2.3 | ns   |

| t <sub>ZX2</sub>    |                | 0.9 |                | 1.2 |                | 1.8 | ns   |

| t <sub>ZX3</sub>    |                | 3.6 |                | 4.3 |                | 4.6 | ns   |

| t <sub>INREG</sub>  |                | 4.9 |                | 5.8 |                | 7.8 | ns   |

| t <sub>IOFD</sub>   |                | 2.8 |                | 3.3 |                | 4.5 | ns   |

| t <sub>INCOMB</sub> |                | 2.8 |                | 3.3 |                | 4.5 | ns   |

| Symbol                 | -1 Spee | ed Grade | -2 Spee | d Grade | -3 Spee | ed Grade | Unit |

|------------------------|---------|----------|---------|---------|---------|----------|------|

|                        | Min     | Max      | Min     | Max     | Min     | Max      |      |

| t <sub>EABDATA1</sub>  |         | 1.7      |         | 2.0     |         | 2.7      | ns   |

| t <sub>EABDATA1</sub>  |         | 0.6      |         | 0.7     |         | 0.9      | ns   |

| t <sub>EABWE1</sub>    |         | 1.1      |         | 1.3     |         | 1.8      | ns   |

| t <sub>EABWE2</sub>    |         | 0.4      |         | 0.4     |         | 0.6      | ns   |

| t <sub>EABRE1</sub>    |         | 0.8      |         | 0.9     |         | 1.2      | ns   |

| t <sub>EABRE2</sub>    |         | 0.4      |         | 0.4     |         | 0.6      | ns   |

| t <sub>EABCLK</sub>    |         | 0.0      |         | 0.0     |         | 0.0      | ns   |

| t <sub>EABCO</sub>     |         | 0.3      |         | 0.3     |         | 0.5      | ns   |

| t <sub>EABBYPASS</sub> |         | 0.5      |         | 0.6     |         | 0.8      | ns   |

| t <sub>EABSU</sub>     | 0.9     |          | 1.0     |         | 1.4     |          | ns   |

| t <sub>EABH</sub>      | 0.4     |          | 0.4     |         | 0.6     |          | ns   |

| t <sub>EABCLR</sub>    | 0.3     |          | 0.3     |         | 0.5     |          | ns   |

| t <sub>AA</sub>        |         | 3.2      |         | 3.8     |         | 5.1      | ns   |

| t <sub>WP</sub>        | 2.5     |          | 2.9     |         | 3.9     |          | ns   |

| t <sub>RP</sub>        | 0.9     |          | 1.1     |         | 1.5     |          | ns   |

| t <sub>WDSU</sub>      | 0.9     |          | 1.0     |         | 1.4     |          | ns   |

| t <sub>WDH</sub>       | 0.1     |          | 0.1     |         | 0.2     |          | ns   |

| t <sub>WASU</sub>      | 1.7     |          | 2.0     |         | 2.7     |          | ns   |

| t <sub>WAH</sub>       | 1.8     |          | 2.1     |         | 2.9     |          | ns   |

| t <sub>RASU</sub>      | 3.1     |          | 3.7     |         | 5.0     |          | ns   |

| t <sub>RAH</sub>       | 0.2     |          | 0.2     |         | 0.3     |          | ns   |

| t <sub>WO</sub>        |         | 2.5      |         | 2.9     |         | 3.9      | ns   |

| t <sub>DD</sub>        |         | 2.5      |         | 2.9     |         | 3.9      | ns   |

| t <sub>EABOUT</sub>    |         | 0.5      |         | 0.6     |         | 0.8      | ns   |

| t <sub>EABCH</sub>     | 1.5     |          | 2.0     |         | 2.5     |          | ns   |

| t <sub>EABCL</sub>     | 2.5     |          | 2.9     |         | 3.9     |          | ns   |

| Table 43. EPF10    | K50E Externa   | l Timing Pai | rameters | Notes (1), (   | (2) |          |      |

|--------------------|----------------|--------------|----------|----------------|-----|----------|------|

| Symbol             | -1 Speed Grade |              | -2 Spee  | -2 Speed Grade |     | ed Grade | Unit |

|                    | Min            | Max          | Min      | Max            | Min | Max      |      |

| t <sub>DRR</sub>   |                | 8.5          |          | 10.0           |     | 13.5     | ns   |

| t <sub>INSU</sub>  | 2.7            |              | 3.2      |                | 4.3 |          | ns   |

| t <sub>INH</sub>   | 0.0            |              | 0.0      |                | 0.0 |          | ns   |

| t <sub>оитсо</sub> | 2.0            | 4.5          | 2.0      | 5.2            | 2.0 | 7.3      | ns   |

| t <sub>PCISU</sub> | 3.0            |              | 4.2      |                | -   |          | ns   |

| t <sub>PCIH</sub>  | 0.0            |              | 0.0      |                | -   |          | ns   |

| t <sub>PCICO</sub> | 2.0            | 6.0          | 2.0      | 7.7            | -   | -        | ns   |

Table 44. EPF10K50E External Bidirectional Timing Parameters

Notes (1), (2)

| Symbol                  | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | ed Grade | Unit |

|-------------------------|----------------|-----|---------|---------|---------|----------|------|

|                         | Min            | Max | Min     | Max     | Min     | Max      |      |

| t <sub>INSUBIDIR</sub>  | 2.7            |     | 3.2     |         | 4.3     |          | ns   |

| t <sub>INHBIDIR</sub>   | 0.0            |     | 0.0     |         | 0.0     |          | ns   |

| t <sub>OUTCOBIDIR</sub> | 2.0            | 4.5 | 2.0     | 5.2     | 2.0     | 7.3      | ns   |

| t <sub>XZBIDIR</sub>    |                | 6.8 |         | 7.8     |         | 10.1     | ns   |

| t <sub>ZXBIDIR</sub>    |                | 6.8 |         | 7.8     |         | 10.1     | ns   |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) These parameters are specified by characterization.

Tables 45 through 51 show EPF10K100E device internal and external timing parameters.

| Table 45. EPF10K100E Device LE Timing Microparameters       Note (1) |                |     |         |                |     |         |      |  |  |  |

|----------------------------------------------------------------------|----------------|-----|---------|----------------|-----|---------|------|--|--|--|

| Symbol                                                               | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | d Grade | Unit |  |  |  |

|                                                                      | Min            | Max | Min     | Max            | Min | Max     |      |  |  |  |

| t <sub>LUT</sub>                                                     |                | 0.7 |         | 1.0            |     | 1.5     | ns   |  |  |  |

| t <sub>CLUT</sub>                                                    |                | 0.5 |         | 0.7            |     | 0.9     | ns   |  |  |  |

| t <sub>RLUT</sub>                                                    |                | 0.6 |         | 0.8            |     | 1.1     | ns   |  |  |  |

| t <sub>PACKED</sub>                                                  |                | 0.3 |         | 0.4            |     | 0.5     | ns   |  |  |  |

| t <sub>EN</sub>                                                      |                | 0.2 |         | 0.3            |     | 0.3     | ns   |  |  |  |

| t <sub>CICO</sub>                                                    |                | 0.1 |         | 0.1            |     | 0.2     | ns   |  |  |  |

| t <sub>CGEN</sub>                                                    |                | 0.4 |         | 0.5            |     | 0.7     | ns   |  |  |  |

| Table 54. EPF10K    | 130E Device    | e EAB Intern | al Micropara | ameters (Pa    | art 2 of 2) | Note (1) |      |

|---------------------|----------------|--------------|--------------|----------------|-------------|----------|------|

| Symbol              | -1 Speed Grade |              | -2 Spee      | -2 Speed Grade |             | d Grade  | Unit |

|                     | Min            | Max          | Min          | Max            | Min         | Max      |      |

| t <sub>DD</sub>     |                | 1.5          |              | 2.0            |             | 2.6      | ns   |

| t <sub>EABOUT</sub> |                | 0.2          |              | 0.3            |             | 0.3      | ns   |

| t <sub>EABCH</sub>  | 1.5            |              | 2.0          |                | 2.5         |          | ns   |

| t <sub>EABCL</sub>  | 2.7            |              | 3.5          |                | 4.7         |          | ns   |

| Table 55. EPF10        | Table 55. EPF10K130E Device EAB Internal Timing Macroparameters       Note (1) |         |                |     |                |     |      |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------|---------|----------------|-----|----------------|-----|------|--|--|--|--|

| Symbol                 | -1 Spee                                                                        | d Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |  |  |  |

|                        | Min                                                                            | Max     | Min            | Max | Min            | Max |      |  |  |  |  |

| t <sub>EABAA</sub>     |                                                                                | 5.9     |                | 7.5 |                | 9.9 | ns   |  |  |  |  |

| t <sub>EABRCOMB</sub>  | 5.9                                                                            |         | 7.5            |     | 9.9            |     | ns   |  |  |  |  |

| t <sub>EABRCREG</sub>  | 5.1                                                                            |         | 6.4            |     | 8.5            |     | ns   |  |  |  |  |

| t <sub>EABWP</sub>     | 2.7                                                                            |         | 3.5            |     | 4.7            |     | ns   |  |  |  |  |

| t <sub>EABWCOMB</sub>  | 5.9                                                                            |         | 7.7            |     | 10.3           |     | ns   |  |  |  |  |

| t <sub>EABWCREG</sub>  | 5.4                                                                            |         | 7.0            |     | 9.4            |     | ns   |  |  |  |  |

| t <sub>EABDD</sub>     |                                                                                | 3.4     |                | 4.5 |                | 5.9 | ns   |  |  |  |  |

| t <sub>EABDATACO</sub> |                                                                                | 0.5     |                | 0.7 |                | 0.8 | ns   |  |  |  |  |

| t <sub>EABDATASU</sub> | 0.8                                                                            |         | 1.0            |     | 1.4            |     | ns   |  |  |  |  |

| t <sub>EABDATAH</sub>  | 0.1                                                                            |         | 0.1            |     | 0.2            |     | ns   |  |  |  |  |

| t <sub>EABWESU</sub>   | 1.1                                                                            |         | 1.4            |     | 1.9            |     | ns   |  |  |  |  |

| t <sub>EABWEH</sub>    | 0.0                                                                            |         | 0.0            |     | 0.0            |     | ns   |  |  |  |  |

| t <sub>EABWDSU</sub>   | 1.0                                                                            |         | 1.3            |     | 1.7            |     | ns   |  |  |  |  |

| t <sub>EABWDH</sub>    | 0.2                                                                            |         | 0.2            |     | 0.3            |     | ns   |  |  |  |  |

| t <sub>EABWASU</sub>   | 4.1                                                                            |         | 5.1            |     | 6.8            |     | ns   |  |  |  |  |

| t <sub>EABWAH</sub>    | 0.0                                                                            |         | 0.0            |     | 0.0            |     | ns   |  |  |  |  |

| t <sub>EABWO</sub>     |                                                                                | 3.4     |                | 4.5 |                | 5.9 | ns   |  |  |  |  |

| Symbol           | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | d Grade | Unit |

|------------------|---------|----------------|-----|----------------|-----|---------|------|

|                  | Min     | Max            | Min | Max            | Min | Мах     |      |

| t <sub>H</sub>   | 0.9     |                | 1.1 |                | 1.5 |         | ns   |

| t <sub>PRE</sub> |         | 0.5            |     | 0.6            |     | 0.8     | ns   |

| t <sub>CLR</sub> |         | 0.5            |     | 0.6            |     | 0.8     | ns   |

| t <sub>CH</sub>  | 2.0     |                | 2.5 |                | 3.0 |         | ns   |

| t <sub>CL</sub>  | 2.0     |                | 2.5 |                | 3.0 |         | ns   |

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|---------------------|----------------|-----|----------------|-----|----------------|------|------|

|                     | Min            | Max | Min            | Max | Min            | Max  |      |

| t <sub>IOD</sub>    |                | 1.6 |                | 1.9 |                | 2.6  | ns   |

| t <sub>IOC</sub>    |                | 0.3 |                | 0.3 |                | 0.5  | ns   |

| t <sub>IOCO</sub>   |                | 1.6 |                | 1.9 |                | 2.6  | ns   |

| t <sub>IOCOMB</sub> |                | 0.5 |                | 0.6 |                | 0.8  | ns   |

| t <sub>IOSU</sub>   | 0.8            |     | 0.9            |     | 1.2            |      | ns   |

| t <sub>IOH</sub>    | 0.7            |     | 0.8            |     | 1.1            |      | ns   |

| t <sub>IOCLR</sub>  |                | 0.2 |                | 0.2 |                | 0.3  | ns   |

| t <sub>OD1</sub>    |                | 0.6 |                | 0.7 |                | 0.9  | ns   |

| t <sub>OD2</sub>    |                | 0.1 |                | 0.2 |                | 0.7  | ns   |

| t <sub>OD3</sub>    |                | 2.5 |                | 3.0 |                | 3.9  | ns   |

| t <sub>XZ</sub>     |                | 4.4 |                | 5.3 |                | 7.1  | ns   |

| t <sub>ZX1</sub>    |                | 4.4 |                | 5.3 |                | 7.1  | ns   |

| t <sub>ZX2</sub>    |                | 3.9 |                | 4.8 |                | 6.9  | ns   |

| t <sub>ZX3</sub>    |                | 6.3 |                | 7.6 |                | 10.1 | ns   |

| t <sub>INREG</sub>  |                | 4.8 |                | 5.7 |                | 7.7  | ns   |

| t <sub>IOFD</sub>   |                | 1.5 |                | 1.8 |                | 2.4  | ns   |

| t <sub>INCOMB</sub> |                | 1.5 |                | 1.8 |                | 2.4  | ns   |

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|---------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                     | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>LUT</sub>    |                | 0.7 |                | 0.8 |                | 1.2 | ns   |

| t <sub>CLUT</sub>   |                | 0.4 |                | 0.5 |                | 0.6 | ns   |

| t <sub>RLUT</sub>   |                | 0.5 |                | 0.7 |                | 0.9 | ns   |

| t <sub>PACKED</sub> |                | 0.4 |                | 0.5 |                | 0.7 | ns   |

| t <sub>EN</sub>     |                | 0.6 |                | 0.5 |                | 0.6 | ns   |

| tcico               |                | 0.1 |                | 0.2 |                | 0.3 | ns   |

| t <sub>CGEN</sub>   |                | 0.3 |                | 0.4 |                | 0.6 | ns   |

| t <sub>CGENR</sub>  |                | 0.1 |                | 0.2 |                | 0.3 | ns   |

| t <sub>CASC</sub>   |                | 0.7 |                | 0.8 |                | 1.2 | ns   |

| t <sub>C</sub>      |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| <sup>t</sup> co     |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| t <sub>COMB</sub>   |                | 0.3 |                | 0.6 |                | 0.8 | ns   |

| t <sub>SU</sub>     | 0.4            |     | 0.6            |     | 0.7            |     | ns   |

| tн                  | 1.0            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>PRE</sub>    |                | 0.4 |                | 0.6 |                | 0.8 | ns   |

| t <sub>CLR</sub>    |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| <sup>t</sup> CH     | 2.0            |     | 2.5            |     | 3.0            |     | ns   |

| ĊL                  | 2.0            |     | 2.5            |     | 3.0            |     | ns   |

Table 74. EPF10K200S Device IOE Timing Microparameters (Part 1 of 2)

Note (1)

| Symbol              | -1 Spee | ed Grade | -2 Spee | ed Grade | -3 Spee | ed Grade | Unit |

|---------------------|---------|----------|---------|----------|---------|----------|------|

|                     | Min     | Max      | Min     | Мах      | Min     | Max      |      |

| t <sub>IOD</sub>    |         | 1.8      |         | 1.9      |         | 2.6      | ns   |

| t <sub>IOC</sub>    |         | 0.3      |         | 0.3      |         | 0.5      | ns   |

| t <sub>IOCO</sub>   |         | 1.7      |         | 1.9      |         | 2.6      | ns   |

| t <sub>IOCOMB</sub> |         | 0.5      |         | 0.6      |         | 0.8      | ns   |

| t <sub>IOSU</sub>   | 0.8     |          | 0.9     |          | 1.2     |          | ns   |

| t <sub>IOH</sub>    | 0.4     |          | 0.8     |          | 1.1     |          | ns   |

| t <sub>IOCLR</sub>  |         | 0.2      |         | 0.2      |         | 0.3      | ns   |

| t <sub>OD1</sub>    |         | 1.3      |         | 0.7      |         | 0.9      | ns   |

| t <sub>OD2</sub>    |         | 0.8      |         | 0.2      |         | 0.4      | ns   |

| t <sub>OD3</sub>    |         | 2.9      |         | 3.0      |         | 3.9      | ns   |

| t <sub>XZ</sub>     |         | 5.0      |         | 5.3      |         | 7.1      | ns   |

| t <sub>ZX1</sub>    |         | 5.0      |         | 5.3      |         | 7.1      | ns   |

| Table 74. EPF10k    | K200S Device   | e IOE Timing | g Microparaı   | neters (Par | t 2 of 2)      | Note (1) |      |

|---------------------|----------------|--------------|----------------|-------------|----------------|----------|------|

| Symbol              | -1 Speed Grade |              | -2 Speed Grade |             | -3 Speed Grade |          | Unit |

|                     | Min            | Max          | Min            | Max         | Min            | Max      |      |

| t <sub>ZX2</sub>    |                | 4.5          |                | 4.8         |                | 6.6      | ns   |

| t <sub>ZX3</sub>    |                | 6.6          |                | 7.6         |                | 10.1     | ns   |

| t <sub>INREG</sub>  |                | 3.7          |                | 5.7         |                | 7.7      | ns   |

| t <sub>IOFD</sub>   |                | 1.8          |                | 3.4         |                | 4.0      | ns   |

| t <sub>INCOMB</sub> |                | 1.8          |                | 3.4         |                | 4.0      | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max | ]    |

| t <sub>EABDATA1</sub>  |                | 1.8 |                | 2.4 |                | 3.2 | ns   |

| t <sub>EABDATA1</sub>  |                | 0.4 |                | 0.5 |                | 0.6 | ns   |

| t <sub>EABWE1</sub>    |                | 1.1 |                | 1.7 |                | 2.3 | ns   |

| t <sub>EABWE2</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABRE1</sub>    |                | 0   |                | 0   |                | 0   | ns   |

| t <sub>EABRE2</sub>    |                | 0.4 |                | 0.5 |                | 0.6 | ns   |

| t <sub>EABCLK</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABCO</sub>     |                | 0.8 |                | 0.9 |                | 1.2 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.0 |                | 0.1 |                | 0.1 | ns   |

| t <sub>EABSU</sub>     | 0.7            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>EABH</sub>      | 0.4            |     | 0.5            |     | 0.6            |     | ns   |

| t <sub>EABCLR</sub>    | 0.8            |     | 0.9            |     | 1.2            |     | ns   |

| t <sub>AA</sub>        |                | 2.1 |                | 3.7 |                | 4.9 | ns   |

| t <sub>WP</sub>        | 2.1            |     | 4.0            |     | 5.3            |     | ns   |

| t <sub>RP</sub>        | 1.1            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>WDSU</sub>      | 0.5            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>WDH</sub>       | 0.1            |     | 0.1            |     | 0.1            |     | ns   |

| twasu                  | 1.1            |     | 1.6            |     | 2.1            |     | ns   |

| t <sub>WAH</sub>       | 1.6            |     | 2.5            |     | 3.3            |     | ns   |

| t <sub>RASU</sub>      | 1.6            |     | 2.6            |     | 3.5            |     | ns   |

| t <sub>RAH</sub>       | 0.1            |     | 0.1            |     | 0.2            |     | ns   |

| t <sub>WO</sub>        |                | 2.0 |                | 2.4 |                | 3.2 | ns   |

| t <sub>DD</sub>        |                | 2.0 |                | 2.4 |                | 3.2 | ns   |

| t <sub>EABOUT</sub>    |                | 0.0 |                | 0.1 |                | 0.1 | ns   |

| t <sub>EABCH</sub>     | 1.5            |     | 2.0            |     | 2.5            |     | ns   |

| t <sub>EABCL</sub>     | 2.1            |     | 2.8            |     | 3.8            |     | ns   |

Altera Corporation