# E·XFL

# Intel - EPF10K100EFC484-3N Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Deta | ils |

|------|-----|

|      |     |

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 624                                                           |

| Number of Logic Elements/Cells | 4992                                                          |

| Total RAM Bits                 | 49152                                                         |

| Number of I/O                  | 338                                                           |

| Number of Gates                | 257000                                                        |

| Voltage - Supply               | 2.375V ~ 2.625V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 70°C (TA)                                               |

| Package / Case                 | 484-BBGA                                                      |

| Supplier Device Package        | 484-FBGA (23x23)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k100efc484-3n |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Software design support and automatic place-and-route provided by Altera's development systems for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800

- Flexible package options

- Available in a variety of packages with 144 to 672 pins, including the innovative FineLine BGA<sup>™</sup> packages (see Tables 3 and 4)

- SameFrame<sup>™</sup> pin-out compatibility between FLEX 10KA and FLEX 10KE devices across a range of device densities and pin counts

- Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), DesignWare components, Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, VeriBest, and Viewlogic

| Table 3. FLE | Table 3. FLEX 10KE Package Options & I/O Pin Count     Notes (1), (2) |                 |                         |                            |                |                            |                |                |                            |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------|-----------------|-------------------------|----------------------------|----------------|----------------------------|----------------|----------------|----------------------------|--|--|--|--|--|--|

| Device       | 144-Pin<br>TQFP                                                       | 208-Pin<br>PQFP | 240-Pin<br>PQFP<br>RQFP | 256-Pin<br>FineLine<br>BGA | 356-Pin<br>BGA | 484-Pin<br>FineLine<br>BGA | 599-Pin<br>PGA | 600-Pin<br>BGA | 672-Pin<br>FineLine<br>BGA |  |  |  |  |  |  |

| EPF10K30E    | 102                                                                   | 147             |                         | 176                        |                | 220                        |                |                | 220 (3)                    |  |  |  |  |  |  |

| EPF10K50E    | 102                                                                   | 147             | 189                     | 191                        |                | 254                        |                |                | 254 (3)                    |  |  |  |  |  |  |

| EPF10K50S    | 102                                                                   | 147             | 189                     | 191                        | 220            | 254                        |                |                | 254 (3)                    |  |  |  |  |  |  |

| EPF10K100E   |                                                                       | 147             | 189                     | 191                        | 274            | 338                        |                |                | 338 (3)                    |  |  |  |  |  |  |

| EPF10K130E   |                                                                       |                 | 186                     |                            | 274            | 369                        |                | 424            | 413                        |  |  |  |  |  |  |

| EPF10K200E   |                                                                       |                 |                         |                            |                |                            | 470            | 470            | 470                        |  |  |  |  |  |  |

| EPF10K200S   |                                                                       |                 | 182                     |                            | 274            | 369                        | 470            | 470            | 470                        |  |  |  |  |  |  |

### Notes:

- (1) FLEX 10KE device package types include thin quad flat pack (TQFP), plastic quad flat pack (PQFP), power quad flat pack (RQFP), pin-grid array (PGA), and ball-grid array (BGA) packages.

- (2) Devices in the same package are pin-compatible, although some devices have more I/O pins than others. When planning device migration, use the I/O pins that are common to all devices.

- (3) This option is supported with a 484-pin FineLine BGA package. By using SameFrame pin migration, all FineLine BGA packages are pin-compatible. For example, a board can be designed to support 256-pin, 484-pin, and 672-pin FineLine BGA packages. The Altera software automatically avoids conflicting pins when future migration is set.

# **Embedded Array Block**

The EAB is a flexible block of RAM, with registers on the input and output ports, that is used to implement common gate array megafunctions. Because it is large and flexible, the EAB is suitable for functions such as multipliers, vector scalars, and error correction circuits. These functions can be combined in applications such as digital filters and microcontrollers.

Logic functions are implemented by programming the EAB with a readonly pattern during configuration, thereby creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results, rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of EABs. The large capacity of EABs enables designers to implement complex functions in one logic level without the routing delays associated with linked LEs or field-programmable gate array (FPGA) RAM blocks. For example, a single EAB can implement any function with 8 inputs and 16 outputs. Parameterized functions such as LPM functions can take advantage of the EAB automatically.

The FLEX 10KE EAB provides advantages over FPGAs, which implement on-board RAM as arrays of small, distributed RAM blocks. These small FPGA RAM blocks must be connected together to make RAM blocks of manageable size. The RAM blocks are connected together using multiplexers implemented with more logic blocks. These extra multiplexers cause extra delay, which slows down the RAM block. FPGA RAM blocks are also prone to routing problems because small blocks of RAM must be connected together to make larger blocks. In contrast, EABs can be used to implement large, dedicated blocks of RAM that eliminate these timing and routing concerns.

The FLEX 10KE enhanced EAB adds dual-port capability to the existing EAB structure. The dual-port structure is ideal for FIFO buffers with one or two clocks. The FLEX 10KE EAB can also support up to 16-bit-wide RAM blocks and is backward-compatible with any design containing FLEX 10K EABs. The FLEX 10KE EAB can act in dual-port or single-port mode. When in dual-port mode, separate clocks may be used for EAB read and write sections, which allows the EAB to be written and read at different rates. It also has separate synchronous clock enable signals for the EAB read and write sections, which allow independent control of these sections.

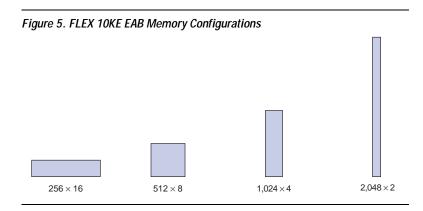

When used as RAM, each EAB can be configured in any of the following sizes:  $256 \times 16$ ,  $512 \times 8$ ,  $1,024 \times 4$ , or  $2,048 \times 2$  (see Figure 5).

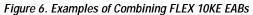

Larger blocks of RAM are created by combining multiple EABs. For example, two  $256 \times 16$  RAM blocks can be combined to form a  $256 \times 32$  block; two  $512 \times 8$  RAM blocks can be combined to form a  $512 \times 16$  block (see Figure 6).

If necessary, all EABs in a device can be cascaded to form a single RAM block. EABs can be cascaded to form RAM blocks of up to 2,048 words without impacting timing. The Altera software automatically combines EABs to meet a designer's RAM specifications.

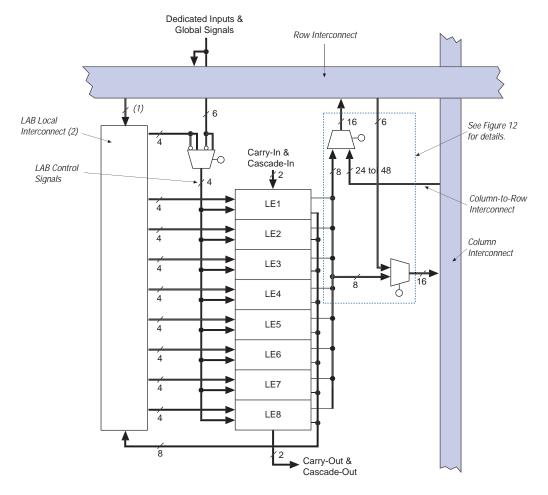

# Figure 7. FLEX 10KE LAB

### Notes:

- (1) EPF10K30E, EPF10K50E, and EPF10K50S devices have 22 inputs to the LAB local interconnect channel from the row; EPF10K100E, EPF10K130E, EPF10K200E, and EPF10K200S devices have 26.

- (2) EPF10K30E, EPF10K50E, and EPF10K50S devices have 30 LAB local interconnect channels; EPF10K100E, EPF10K130E, EPF10K200E, and EPF10K200S devices have 34.

The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock, clear, and preset control signals on the flipflop can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the flipflop is bypassed and the output of the LUT drives the output of the LE.

The LE has two outputs that drive the interconnect: one drives the local interconnect and the other drives either the row or column FastTrack Interconnect routing structure. The two outputs can be controlled independently. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, can improve LE utilization because the register and the LUT can be used for unrelated functions.

The FLEX 10KE architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. The carry chain supports high-speed counters and adders and the cascade chain implements wide-input functions with minimum delay. Carry and cascade chains connect all LEs in a LAB as well as all LABs in the same row. Intensive use of carry and cascade chains can reduce routing flexibility. Therefore, the use of these chains should be limited to speed-critical portions of a design.

# Carry Chain

The carry chain provides a very fast (as low as 0.2 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the FLEX 10KE architecture to implement high-speed counters, adders, and comparators of arbitrary width efficiently. Carry chain logic can be created automatically by the Altera Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as LPM and DesignWare functions automatically take advantage of carry chains.

Carry chains longer than eight LEs are automatically implemented by linking LABs together. For enhanced fitting, a long carry chain skips alternate LABs in a row. A carry chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from oddnumbered LAB to odd-numbered LAB. For example, the last LE of the first LAB in a row carries to the first LE of the third LAB in the row. The carry chain does not cross the EAB at the middle of the row. For instance, in the EPF10K50E device, the carry chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB. On all FLEX 10KE devices (except EPF10K50E and EPF10K200E devices), the input path from the I/O pad to the FastTrack Interconnect has a programmable delay element that can be used to guarantee a zero hold time. EPF10K50S and EPF10K200S devices also support this feature. Depending on the placement of the IOE relative to what it is driving, the designer may choose to turn on the programmable delay to ensure a zero hold time or turn it off to minimize setup time. This feature is used to reduce setup time for complex pin-to-register paths (e.g., PCI designs).

Each IOE selects the clock, clear, clock enable, and output enable controls from a network of I/O control signals called the peripheral control bus. The peripheral control bus uses high-speed drivers to minimize signal skew across the device and provides up to 12 peripheral control signals that can be allocated as follows:

- Up to eight output enable signals

- Up to six clock enable signals

- Up to two clock signals

- Up to two clear signals

If more than six clock enable or eight output enable signals are required, each IOE on the device can be controlled by clock enable and output enable signals driven by specific LEs. In addition to the two clock signals available on the peripheral control bus, each IOE can use one of two dedicated clock pins. Each peripheral control signal can be driven by any of the dedicated input pins or the first LE of each LAB in a particular row. In addition, a LE in a different row can drive a column interconnect, which causes a row interconnect to drive the peripheral control signal. The chipwide reset signal resets all IOE registers, overriding any other control signals.

When a dedicated clock pin drives IOE registers, it can be inverted for all IOEs in the device. All IOEs must use the same sense of the clock. For example, if any IOE uses the inverted clock, all IOEs must use the inverted clock and no IOE can use the non-inverted clock. However, LEs can still use the true or complement of the clock on a LAB-by-LAB basis.

The incoming signal may be inverted at the dedicated clock pin and will drive all IOEs. For the true and complement of a clock to be used to drive IOEs, drive it into both global clock pins. One global clock pin will supply the true, and the other will supply the complement.

When the true and complement of a dedicated input drives IOE clocks, two signals on the peripheral control bus are consumed, one for each sense of the clock.

| Symbol                | Parameter                                                                     | Condition            | Min | Тур | Max        | Unit |

|-----------------------|-------------------------------------------------------------------------------|----------------------|-----|-----|------------|------|

| t <sub>R</sub>        | Input rise time                                                               |                      |     |     | 5          | ns   |

| t <sub>F</sub>        | Input fall time                                                               |                      |     |     | 5          | ns   |

| t <sub>INDUTY</sub>   | Input duty cycle                                                              |                      | 40  |     | 60         | %    |

| f <sub>CLK1</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 1)       |                      | 25  |     | 75         | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2)       |                      | 16  |     | 37.5       | MHz  |

| f <sub>CLKDEV</sub>   | Input deviation from user<br>specification in the MAX+PLUS II<br>software (1) |                      |     |     | 25,000 (2) | PPM  |

| t <sub>INCLKSTB</sub> | Input clock stability (measured between adjacent clocks)                      |                      |     |     | 100        | ps   |

| t <sub>LOCK</sub>     | Time required for ClockLock or ClockBoost to acquire lock (3)                 |                      |     |     | 10         | μs   |

| t <sub>JITTER</sub>   | Jitter on ClockLock or ClockBoost-                                            | $t_{INCLKSTB} < 100$ |     |     | 250        | ps   |

|                       | generated clock (4)                                                           | $t_{INCLKSTB} < 50$  |     |     | 200 (4)    | ps   |

| toutduty              | Duty cycle for ClockLock or<br>ClockBoost-generated clock                     |                      | 40  | 50  | 60         | %    |

### Notes to tables:

- (1) To implement the ClockLock and ClockBoost circuitry with the MAX+PLUS II software, designers must specify the input frequency. The Altera software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The f<sub>CLKDEV</sub> parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) Twenty-five thousand parts per million (PPM) equates to 2.5% of input clock period.

- (3) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration because the t<sub>LOCK</sub> value is less than the time required for configuration.

- (4) The t<sub>ITTER</sub> specification is measured under long-term observation. The maximum value for t<sub>ITTER</sub> is 200 ps if t<sub>INCLKSTB</sub> is lower than 50 ps.

# I/O Configuration

This section discusses the peripheral component interconnect (PCI) pull-up clamping diode option, slew-rate control, open-drain output option, and MultiVolt I/O interface for FLEX 10KE devices. The PCI pull-up clamping diode, slew-rate control, and open-drain output options are controlled pin-by-pin via Altera software logic options. The MultiVolt I/O interface is controlled by connecting  $V_{CCIO}$  to a different voltage than  $V_{CCINT}$ . Its effect can be simulated in the Altera software via the **Global Project Device Options** dialog box (Assign menu).

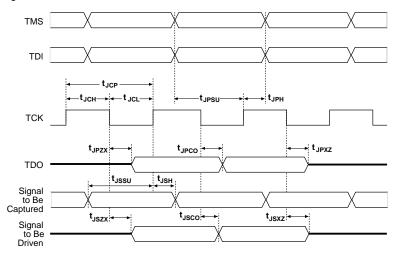

Figure 20 shows the timing requirements for the JTAG signals.

Figure 20. FLEX 10KE JTAG Waveforms

# Table 18 shows the timing parameters and values for FLEX 10KE devices.

| Sumbol            | Parameter                                      | Min    | Max   | Unit |

|-------------------|------------------------------------------------|--------|-------|------|

| Symbol            | Parameter                                      | IVIIII | IVIAX | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100    |       | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50     |       | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50     |       | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20     |       | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45     |       | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |        | 25    | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |        | 25    | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |        | 25    | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20     |       | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45     |       | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |        | 35    | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output |        | 35    | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |        | 35    | ns   |

| Symbol            | Parameter                                                                                          | Conditions                                                                         | Min                            | Тур | Max                                 | Unit       |

|-------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------|-----|-------------------------------------|------------|

| V <sub>IH</sub>   | High-level input<br>voltage                                                                        |                                                                                    | $1.7, 0.5 \times V_{CCIO}$ (8) |     | 5.75                                | V          |

| V <sub>IL</sub>   | Low-level input voltage                                                                            |                                                                                    | -0.5                           |     | 0.8,<br>0.3 × V <sub>CCIO</sub> (8) | V          |

| V <sub>OH</sub>   | 3.3-V high-level TTL<br>output voltage                                                             | I <sub>OH</sub> = -8 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(9)</i>               | 2.4                            |     |                                     | V          |

|                   | 3.3-V high-level<br>CMOS output voltage                                                            | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(9)</i>             | V <sub>CCIO</sub> -0.2         |     |                                     | V          |

|                   | 3.3-V high-level PCI<br>output voltage                                                             | $I_{OH} = -0.5 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{ V} (9)$ | $0.9 	imes V_{CCIO}$           |     |                                     | V          |

|                   | 2.5-V high-level output $I_{OH} = -0.1 \text{ mA DC},$<br>voltage $V_{CCIO} = 2.30 \text{ V } (9)$ |                                                                                    | 2.1                            |     |                                     | V          |

|                   |                                                                                                    | I <sub>OH</sub> = –1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(9)</i>               | 2.0                            |     |                                     | V          |

|                   |                                                                                                    | $I_{OH} = -2 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (9)$                   | 1.7                            |     |                                     | V          |

| V <sub>OL</sub>   | 3.3-V low-level TTL<br>output voltage                                                              | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (10)                     |                                |     | 0.45                                | V          |

|                   | 3.3-V low-level CMOS<br>output voltage                                                             | $I_{OL} = 0.1 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ V} (10)$                  |                                |     | 0.2                                 | V          |

|                   | 3.3-V low-level PCI<br>output voltage                                                              | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>(10)         |                                |     | $0.1 	imes V_{CCIO}$                | V          |

|                   | 2.5-V low-level output voltage                                                                     | $I_{OL} = 0.1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V} (10)$                  |                                |     | 0.2                                 | V          |

|                   |                                                                                                    | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                      |                                |     | 0.4                                 | V          |

|                   |                                                                                                    | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                      |                                |     | 0.7                                 | V          |

| I <sub>I</sub>    | Input pin leakage<br>current                                                                       | $V_{I} = V_{CCIOmax}$ to 0 V (11)                                                  | -10                            |     | 10                                  | μA         |

| I <sub>OZ</sub>   | Tri-stated I/O pin<br>leakage current                                                              | $V_{O} = V_{CCIOmax}$ to 0 V (11)                                                  | -10                            |     | 10                                  | μ <b>A</b> |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current<br>(standby)                                                        | V <sub>I</sub> = ground, no load, no<br>toggling inputs                            |                                | 5   |                                     | mA         |

|                   |                                                                                                    | V <sub>I</sub> = ground, no load, no toggling inputs <i>(12)</i>                   |                                | 10  |                                     | mA         |

| R <sub>CONF</sub> | Value of I/O pin pull-                                                                             | V <sub>CCIO</sub> = 3.0 V (13)                                                     | 20                             |     | 50                                  | k¾         |

|                   | up resistor before and<br>during configuration                                                     | up resistor before and $V_{CCIO} = 2.3 V (13)$ during configuration                |                                |     | 80                                  | k¾         |

| Table 2            | Table 23. FLEX 10KE Device Capacitance     Note (14) |                                     |     |     |      |  |  |  |  |  |  |  |

|--------------------|------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|--|--|--|--|

| Symbol             | Parameter                                            | Conditions                          | Min | Max | Unit |  |  |  |  |  |  |  |

| C <sub>IN</sub>    | Input capacitance                                    | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |  |  |  |  |  |  |

| C <sub>INCLK</sub> | Input capacitance on<br>dedicated clock pin          | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |  |  |  |  |  |

| C <sub>OUT</sub>   | Output capacitance                                   | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |  |  |  |  |  |  |  |

### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before  $V_{CCINT}$  and  $V_{CCIO}$  are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  V or 3.3 V.

- (7) These values are specified under the FLEX 10KE Recommended Operating Conditions shown in Tables 20 and 21.

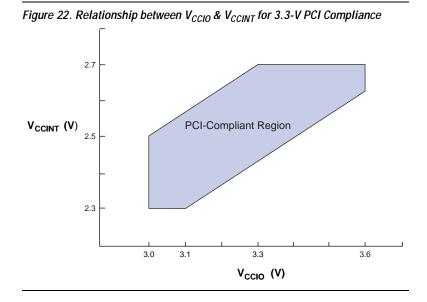

(8) The FLEX 10KE input buffers are compatible with 2.5-V, 3.3-V (LVTTL and LVCMOS), and 5.0-V TTL and CMOS

- signals. Additionally, the input buffers are 3.3-V PCI compliant when  $V_{CCIO}$  and  $V_{CCINT}$  meet the relationship shown in Figure 22.

- (9) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (10) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (11) This value is specified for normal device operation. The value may vary during power-up.

- (12) This parameter applies to -1 speed-grade commercial-temperature devices and -2 speed-grade-industrial temperature devices.

- (13) Pin pull-up resistance values will be lower if the pin is driven higher than  $V_{CCIO}$  by an external source.

- (14) Capacitance is sample-tested only.

Figure 22 shows the required relationship between  $V_{CCIO}$  and  $V_{CCINT}$  for 3.3-V PCI compliance.

Figure 23 shows the typical output drive characteristics of FLEX 10KE devices with 3.3-V and 2.5-V V<sub>CCIO</sub>. The output driver is compliant to the 3.3-V *PCI Local Bus Specification*, *Revision 2.2* (when VCCIO pins are connected to 3.3 V). FLEX 10KE devices with a -1 speed grade also comply with the drive strength requirements of the *PCI Local Bus Specification*, *Revision 2.2* (when VCCINT pins are powered with a minimum supply of 2.375 V, and VCCIO pins are connected to 3.3 V). Therefore, these devices can be used in open 5.0-V PCI systems.

#### **Altera Corporation**

| Symbol                  | -1 Spee | d Grade | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|-------------------------|---------|---------|---------|----------------|-----|----------|------|

|                         | Min     | Max     | Min     | Max            | Min | Max      |      |

| t <sub>DIN2IOE</sub>    |         | 1.8     |         | 2.4            |     | 2.9      | ns   |

| t <sub>DIN2LE</sub>     |         | 1.5     |         | 1.8            |     | 2.4      | ns   |

| t <sub>DIN2DATA</sub>   |         | 1.5     |         | 1.8            |     | 2.2      | ns   |

| t <sub>DCLK2IOE</sub>   |         | 2.2     |         | 2.6            |     | 3.0      | ns   |

| t <sub>DCLK2LE</sub>    |         | 1.5     |         | 1.8            |     | 2.4      | ns   |

| t <sub>SAMELAB</sub>    |         | 0.1     |         | 0.2            |     | 0.3      | ns   |

| t <sub>SAMEROW</sub>    |         | 2.0     |         | 2.4            |     | 2.7      | ns   |

| t <sub>SAMECOLUMN</sub> |         | 0.7     |         | 1.0            |     | 0.8      | ns   |

| t <sub>DIFFROW</sub>    |         | 2.7     |         | 3.4            |     | 3.5      | ns   |

| t <sub>TWOROWS</sub>    |         | 4.7     |         | 5.8            |     | 6.2      | ns   |

| t <sub>LEPERIPH</sub>   |         | 2.7     |         | 3.4            |     | 3.8      | ns   |

| t <sub>LABCARRY</sub>   |         | 0.3     |         | 0.4            |     | 0.5      | ns   |

| t <sub>LABCASC</sub>    |         | 0.8     |         | 0.8            |     | 1.1      | ns   |

| Symbol                            | -1 Spee | ed Grade | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|-----------------------------------|---------|----------|---------|----------------|-----|----------|------|

|                                   | Min     | Max      | Min     | Max            | Min | Max      |      |

| t <sub>DRR</sub>                  |         | 8.0      |         | 9.5            |     | 12.5     | ns   |

| t <sub>INSU</sub> (3)             | 2.1     |          | 2.5     |                | 3.9 |          | ns   |

| t <sub>INH</sub> (3)              | 0.0     |          | 0.0     |                | 0.0 |          | ns   |

| <sup>t</sup> оитсо <sup>(3)</sup> | 2.0     | 4.9      | 2.0     | 5.9            | 2.0 | 7.6      | ns   |

| t <sub>INSU</sub> (4)             | 1.1     |          | 1.5     |                | -   |          | ns   |

| t <sub>INH</sub> (4)              | 0.0     |          | 0.0     |                | -   |          | ns   |

| t <sub>оитсо</sub> (4)            | 0.5     | 3.9      | 0.5     | 4.9            | -   | -        | ns   |

| t <sub>PCISU</sub>                | 3.0     |          | 4.2     |                | -   |          | ns   |

| t <sub>PCIH</sub>                 | 0.0     |          | 0.0     |                | -   |          | ns   |

| t <sub>PCICO</sub>                | 2.0     | 6.0      | 2.0     | 7.5            | _   | -        | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | d Grade | Unit |

|------------------------|----------------|-----|----------------|-----|---------|---------|------|

|                        | Min            | Max | Min            | Max | Min     | Max     |      |

| t <sub>EABDATA1</sub>  |                | 1.5 |                | 2.0 |         | 2.6     | ns   |

| t <sub>EABDATA1</sub>  |                | 0.0 |                | 0.0 |         | 0.0     | ns   |

| t <sub>EABWE1</sub>    |                | 1.5 |                | 2.0 |         | 2.6     | ns   |

| t <sub>EABWE2</sub>    |                | 0.3 |                | 0.4 |         | 0.5     | ns   |

| t <sub>EABRE1</sub>    |                | 0.3 |                | 0.4 |         | 0.5     | ns   |

| t <sub>EABRE2</sub>    |                | 0.0 |                | 0.0 |         | 0.0     | ns   |

| t <sub>EABCLK</sub>    |                | 0.0 |                | 0.0 |         | 0.0     | ns   |

| t <sub>EABCO</sub>     |                | 0.3 |                | 0.4 |         | 0.5     | ns   |

| t <sub>EABBYPASS</sub> |                | 0.1 |                | 0.1 |         | 0.2     | ns   |

| t <sub>EABSU</sub>     | 0.8            |     | 1.0            |     | 1.4     |         | ns   |

| t <sub>EABH</sub>      | 0.1            |     | 0.1            |     | 0.2     |         | ns   |

| t <sub>EABCLR</sub>    | 0.3            |     | 0.4            |     | 0.5     |         | ns   |

| t <sub>AA</sub>        |                | 4.0 |                | 5.1 |         | 6.6     | ns   |

| t <sub>WP</sub>        | 2.7            |     | 3.5            |     | 4.7     |         | ns   |

| t <sub>RP</sub>        | 1.0            |     | 1.3            |     | 1.7     |         | ns   |

| t <sub>WDSU</sub>      | 1.0            |     | 1.3            |     | 1.7     |         | ns   |

| t <sub>WDH</sub>       | 0.2            |     | 0.2            |     | 0.3     |         | ns   |

| t <sub>WASU</sub>      | 1.6            |     | 2.1            |     | 2.8     |         | ns   |

| t <sub>WAH</sub>       | 1.6            |     | 2.1            |     | 2.8     |         | ns   |

| t <sub>RASU</sub>      | 3.0            |     | 3.9            |     | 5.2     |         | ns   |

| t <sub>RAH</sub>       | 0.1            |     | 0.1            |     | 0.2     |         | ns   |

| t <sub>WO</sub>        |                | 1.5 |                | 2.0 |         | 2.6     | ns   |

| t <sub>DD</sub>        |                | 1.5 |                | 2.0 |         | 2.6     | ns   |

| t <sub>EABOUT</sub>    |                | 0.2 |                | 0.3 |         | 0.3     | ns   |

| t <sub>EABCH</sub>     | 1.5            |     | 2.0            |     | 2.5     |         | ns   |

| t <sub>EABCL</sub>     | 2.7            |     | 3.5            |     | 4.7     |         | ns   |

Table 48. EPF10K100E Device EAB Internal Timing Macroparameters (Part 1 of

| 2) | Note | (1)   |

|----|------|-------|

| -/ |      | V . V |

| Symbol                | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | d Grade | Unit |

|-----------------------|----------------|-----|---------|----------------|-----|---------|------|

|                       | Min            | Max | Min     | Max            | Min | Max     |      |

| t <sub>EABAA</sub>    |                | 5.9 |         | 7.6            |     | 9.9     | ns   |

| t <sub>EABRCOMB</sub> | 5.9            |     | 7.6     |                | 9.9 |         | ns   |

| t <sub>EABRCREG</sub> | 5.1            |     | 6.5     |                | 8.5 |         | ns   |

| t <sub>EABWP</sub>    | 2.7            |     | 3.5     |                | 4.7 |         | ns   |

| Symbol                 | -1 Spee | d Grade | -2 Speed Grade |     | -3 Spee | d Grade | Unit |

|------------------------|---------|---------|----------------|-----|---------|---------|------|

|                        | Min     | Max     | Min            | Max | Min     | Max     |      |

| t <sub>EABWCOMB</sub>  | 5.9     |         | 7.7            |     | 10.3    |         | ns   |

| t <sub>EABWCREG</sub>  | 5.4     |         | 7.0            |     | 9.4     |         | ns   |

| t <sub>EABDD</sub>     |         | 3.4     |                | 4.5 |         | 5.9     | ns   |

| t <sub>EABDATACO</sub> |         | 0.5     |                | 0.7 |         | 0.8     | ns   |

| t <sub>EABDATASU</sub> | 0.8     |         | 1.0            |     | 1.4     |         | ns   |

| t <sub>EABDATAH</sub>  | 0.1     |         | 0.1            |     | 0.2     |         | ns   |

| t <sub>EABWESU</sub>   | 1.1     |         | 1.4            |     | 1.9     |         | ns   |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0            |     | 0.0     |         | ns   |

| t <sub>EABWDSU</sub>   | 1.0     |         | 1.3            |     | 1.7     |         | ns   |

| t <sub>EABWDH</sub>    | 0.2     |         | 0.2            |     | 0.3     |         | ns   |

| t <sub>EABWASU</sub>   | 4.1     |         | 5.2            |     | 6.8     |         | ns   |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0            |     | 0.0     |         | ns   |

| t <sub>EABWO</sub>     |         | 3.4     |                | 4.5 |         | 5.9     | ns   |

Table 49. EPF10K100E Device Interconnect Timing Microparameters

Note (1)

|                         |                |     | -       |                |     |                |    |

|-------------------------|----------------|-----|---------|----------------|-----|----------------|----|

| Symbol                  | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | -3 Speed Grade |    |

|                         | Min            | Max | Min     | Max            | Min | Мах            |    |

| t <sub>DIN2IOE</sub>    |                | 3.1 |         | 3.6            |     | 4.4            | ns |

| t <sub>DIN2LE</sub>     |                | 0.3 |         | 0.4            |     | 0.5            | ns |

| t <sub>DIN2DATA</sub>   |                | 1.6 |         | 1.8            |     | 2.0            | ns |

| t <sub>DCLK2IOE</sub>   |                | 0.8 |         | 1.1            |     | 1.4            | ns |

| t <sub>DCLK2LE</sub>    |                | 0.3 |         | 0.4            |     | 0.5            | ns |

| t <sub>SAMELAB</sub>    |                | 0.1 |         | 0.1            |     | 0.2            | ns |

| t <sub>SAMEROW</sub>    |                | 1.5 |         | 2.5            |     | 3.4            | ns |

| t <sub>SAMECOLUMN</sub> |                | 0.4 |         | 1.0            |     | 1.6            | ns |

| t <sub>DIFFROW</sub>    |                | 1.9 |         | 3.5            |     | 5.0            | ns |

| t <sub>TWOROWS</sub>    |                | 3.4 |         | 6.0            |     | 8.4            | ns |

| t <sub>LEPERIPH</sub>   |                | 4.3 |         | 5.4            |     | 6.5            | ns |

| t <sub>LABCARRY</sub>   |                | 0.5 |         | 0.7            |     | 0.9            | ns |

| t <sub>LABCASC</sub>    |                | 0.8 |         | 1.0            |     | 1.4            | ns |

Tables 52 through 58 show EPF10K130E device internal and external timing parameters.

| Table 52. EPF10     | K130E Device | e LE Timing | Microparan | neters N | lote (1) |          |      |

|---------------------|--------------|-------------|------------|----------|----------|----------|------|

| Symbol              | -1 Spee      | d Grade     | -2 Spe     | ed Grade | -3 Spee  | ed Grade | Unit |

|                     | Min          | Max         | Min        | Max      | Min      | Мах      |      |

| t <sub>LUT</sub>    |              | 0.6         |            | 0.9      |          | 1.3      | ns   |

| t <sub>CLUT</sub>   |              | 0.6         |            | 0.8      |          | 1.0      | ns   |

| t <sub>RLUT</sub>   |              | 0.7         |            | 0.9      |          | 0.2      | ns   |

| t <sub>PACKED</sub> |              | 0.3         |            | 0.5      |          | 0.6      | ns   |

| t <sub>EN</sub>     |              | 0.2         |            | 0.3      |          | 0.4      | ns   |

| t <sub>CICO</sub>   |              | 0.1         |            | 0.1      |          | 0.2      | ns   |

| t <sub>CGEN</sub>   |              | 0.4         |            | 0.6      |          | 0.8      | ns   |

| t <sub>CGENR</sub>  |              | 0.1         |            | 0.1      |          | 0.2      | ns   |

| tCASC               |              | 0.6         |            | 0.9      |          | 1.2      | ns   |

| t <sub>C</sub>      |              | 0.3         |            | 0.5      |          | 0.6      | ns   |

| t <sub>CO</sub>     |              | 0.5         |            | 0.7      |          | 0.8      | ns   |

| t <sub>COMB</sub>   |              | 0.3         |            | 0.5      |          | 0.6      | ns   |

| t <sub>SU</sub>     | 0.5          |             | 0.7        |          | 0.8      |          | ns   |

| t <sub>H</sub>      | 0.6          |             | 0.7        |          | 1.0      |          | ns   |

| t <sub>PRE</sub>    |              | 0.9         |            | 1.2      |          | 1.6      | ns   |

| t <sub>CLR</sub>    |              | 0.9         |            | 1.2      |          | 1.6      | ns   |

| t <sub>CH</sub>     | 1.5          |             | 1.5        |          | 2.5      |          | ns   |

| t <sub>CL</sub>     | 1.5          |             | 1.5        |          | 2.5      |          | ns   |

Table 53. EPF10K130E Device IOE Timing Microparameters

Note (1)

| Symbol              | -1 Spee | -1 Speed Grade |     | ed Grade | -3 Spee | ed Grade | Unit |

|---------------------|---------|----------------|-----|----------|---------|----------|------|

|                     | Min     | Max            | Min | Max      | Min     | Max      |      |

| t <sub>IOD</sub>    |         | 1.3            |     | 1.5      |         | 2.0      | ns   |

| t <sub>IOC</sub>    |         | 0.0            |     | 0.0      |         | 0.0      | ns   |

| t <sub>IOCO</sub>   |         | 0.6            |     | 0.8      |         | 1.0      | ns   |

| t <sub>IOCOMB</sub> |         | 0.6            |     | 0.8      |         | 1.0      | ns   |

| t <sub>IOSU</sub>   | 1.0     |                | 1.2 |          | 1.6     |          | ns   |

| t <sub>IOH</sub>    | 0.9     |                | 0.9 |          | 1.4     |          | ns   |

| t <sub>IOCLR</sub>  |         | 0.6            |     | 0.8      |         | 1.0      | ns   |

| t <sub>OD1</sub>    |         | 2.8            |     | 4.1      |         | 5.5      | ns   |

| t <sub>OD2</sub>    |         | 2.8            |     | 4.1      |         | 5.5      | ns   |

| Table 54. EPF10K    | 130E Device | e EAB Intern | al Micropara | ameters (Pa    | art 2 of 2) | Note (1) |      |

|---------------------|-------------|--------------|--------------|----------------|-------------|----------|------|

| Symbol              | -1 Spee     | d Grade      | -2 Spee      | -2 Speed Grade |             | d Grade  | Unit |

|                     | Min         | Max          | Min          | Max            | Min         | Max      |      |

| t <sub>DD</sub>     |             | 1.5          |              | 2.0            |             | 2.6      | ns   |

| t <sub>EABOUT</sub> |             | 0.2          |              | 0.3            |             | 0.3      | ns   |

| t <sub>EABCH</sub>  | 1.5         |              | 2.0          |                | 2.5         |          | ns   |

| t <sub>EABCL</sub>  | 2.7         |              | 3.5          |                | 4.7         |          | ns   |

| Table 55. EPF10        | K130E Device   | e EAB Intern | al Timing M    | lacroparame | eters Note     | e (1) |      |

|------------------------|----------------|--------------|----------------|-------------|----------------|-------|------|

| Symbol                 | -1 Speed Grade |              | -2 Speed Grade |             | -3 Speed Grade |       | Unit |

|                        | Min            | Max          | Min            | Max         | Min            | Max   |      |

| t <sub>EABAA</sub>     |                | 5.9          |                | 7.5         |                | 9.9   | ns   |

| t <sub>EABRCOMB</sub>  | 5.9            |              | 7.5            |             | 9.9            |       | ns   |

| t <sub>EABRCREG</sub>  | 5.1            |              | 6.4            |             | 8.5            |       | ns   |

| t <sub>EABWP</sub>     | 2.7            |              | 3.5            |             | 4.7            |       | ns   |

| t <sub>EABWCOMB</sub>  | 5.9            |              | 7.7            |             | 10.3           |       | ns   |

| t <sub>EABWCREG</sub>  | 5.4            |              | 7.0            |             | 9.4            |       | ns   |

| t <sub>EABDD</sub>     |                | 3.4          |                | 4.5         |                | 5.9   | ns   |

| t <sub>EABDATACO</sub> |                | 0.5          |                | 0.7         |                | 0.8   | ns   |

| t <sub>EABDATASU</sub> | 0.8            |              | 1.0            |             | 1.4            |       | ns   |

| t <sub>EABDATAH</sub>  | 0.1            |              | 0.1            |             | 0.2            |       | ns   |

| t <sub>EABWESU</sub>   | 1.1            |              | 1.4            |             | 1.9            |       | ns   |

| t <sub>EABWEH</sub>    | 0.0            |              | 0.0            |             | 0.0            |       | ns   |

| t <sub>EABWDSU</sub>   | 1.0            |              | 1.3            |             | 1.7            |       | ns   |

| t <sub>EABWDH</sub>    | 0.2            |              | 0.2            |             | 0.3            |       | ns   |

| t <sub>EABWASU</sub>   | 4.1            |              | 5.1            |             | 6.8            |       | ns   |

| t <sub>EABWAH</sub>    | 0.0            |              | 0.0            |             | 0.0            |       | ns   |

| t <sub>EABWO</sub>     |                | 3.4          |                | 4.5         |                | 5.9   | ns   |

| Symbol                 | -1 Spee | d Grade | -2 Spee | -2 Speed Grade |      | d Grade | Unit |

|------------------------|---------|---------|---------|----------------|------|---------|------|

|                        | Min     | Max     | Min     | Max            | Min  | Мах     |      |

| t <sub>EABWCOMB</sub>  | 6.7     |         | 8.1     |                | 10.7 |         | ns   |

| t <sub>EABWCREG</sub>  | 6.6     |         | 8.0     |                | 10.6 |         | ns   |

| t <sub>EABDD</sub>     |         | 4.0     |         | 5.1            |      | 6.7     | ns   |

| t <sub>EABDATACO</sub> |         | 0.8     |         | 1.0            |      | 1.3     | ns   |

| t <sub>EABDATASU</sub> | 1.3     |         | 1.6     |                | 2.1  |         | ns   |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |                | 0.0  |         | ns   |

| t <sub>EABWESU</sub>   | 0.9     |         | 1.1     |                | 1.5  |         | ns   |

| t <sub>EABWEH</sub>    | 0.4     |         | 0.5     |                | 0.6  |         | ns   |

| t <sub>EABWDSU</sub>   | 1.5     |         | 1.8     |                | 2.4  |         | ns   |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |                | 0.0  |         | ns   |

| t <sub>EABWASU</sub>   | 3.0     |         | 3.6     |                | 4.7  |         | ns   |

| t <sub>EABWAH</sub>    | 0.4     |         | 0.5     |                | 0.7  |         | ns   |

| t <sub>EABWO</sub>     |         | 3.4     |         | 4.4            |      | 5.8     | ns   |

Table 63. EPF10K200E Device Interconnect Timing Microparameters

Note (1)

| Symbol                  | -1 Spee | ed Grade | -2 Spee | ed Grade -3 Spec |     | ed Grade | Unit |

|-------------------------|---------|----------|---------|------------------|-----|----------|------|

|                         | Min     | Max      | Min     | Max              | Min | Max      |      |

| t <sub>DIN2IOE</sub>    |         | 4.2      |         | 4.6              |     | 5.7      | ns   |

| t <sub>DIN2LE</sub>     |         | 1.7      |         | 1.7              |     | 2.0      | ns   |

| t <sub>DIN2DATA</sub>   |         | 1.9      |         | 2.1              |     | 3.0      | ns   |

| t <sub>DCLK2IOE</sub>   |         | 2.5      |         | 2.9              |     | 4.0      | ns   |

| t <sub>DCLK2LE</sub>    |         | 1.7      |         | 1.7              |     | 2.0      | ns   |

| t <sub>SAMELAB</sub>    |         | 0.1      |         | 0.1              |     | 0.2      | ns   |

| t <sub>SAMEROW</sub>    |         | 2.3      |         | 2.6              |     | 3.6      | ns   |

| t <sub>SAMECOLUMN</sub> |         | 2.5      |         | 2.7              |     | 4.1      | ns   |

| t <sub>DIFFROW</sub>    |         | 4.8      |         | 5.3              |     | 7.7      | ns   |

| t <sub>TWOROWS</sub>    |         | 7.1      |         | 7.9              |     | 11.3     | ns   |

| t <sub>LEPERIPH</sub>   |         | 7.0      |         | 7.6              |     | 9.0      | ns   |

| t <sub>LABCARRY</sub>   |         | 0.1      |         | 0.1              |     | 0.2      | ns   |

| t <sub>LABCASC</sub>    |         | 0.9      |         | 1.0              |     | 1.4      | ns   |

| Table 77. EPF10K     | 200S Device | Interconne | ct Timing M | icroparame | ters (Part 2 | of 2) Not      | te (1) |  |

|----------------------|-------------|------------|-------------|------------|--------------|----------------|--------|--|

| Symbol               | -1 Spee     | d Grade    | -2 Spee     | d Grade    | -3 Spee      | -3 Speed Grade |        |  |

|                      | Min         | Мах        | Min         | Max        | Min          | Max            |        |  |

| t <sub>LABCASC</sub> |             | 0.5        |             | 1.0        |              | 1.4            | ns     |  |

Table 78. EPF10K200S External Timing Parameters

Note (1)

| Symbol                        | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | ed Grade | Unit |

|-------------------------------|----------------|-----|---------|---------|---------|----------|------|

|                               | Min            | Max | Min     | Max     | Min     | Max      |      |

| t <sub>DRR</sub>              |                | 9.0 |         | 12.0    |         | 16.0     | ns   |

| t <sub>INSU</sub> (2)         | 3.1            |     | 3.7     |         | 4.7     |          | ns   |

| t <sub>INH</sub> (2)          | 0.0            |     | 0.0     |         | 0.0     |          | ns   |

| t <sub>оитсо</sub> (2)        | 2.0            | 3.7 | 2.0     | 4.4     | 2.0     | 6.3      | ns   |

| t <sub>INSU</sub> (3)         | 2.1            |     | 2.7     |         | -       |          | ns   |

| t <sub>INH</sub> (3)          | 0.0            |     | 0.0     |         | -       |          | ns   |

| <b>t</b> оитсо <sup>(3)</sup> | 0.5            | 2.7 | 0.5     | 3.4     | -       | -        | ns   |

| t <sub>PCISU</sub>            | 3.0            |     | 4.2     |         | -       |          | ns   |

| t <sub>PCIH</sub>             | 0.0            |     | 0.0     |         | -       |          | ns   |

| t <sub>PCICO</sub>            | 2.0            | 6.0 | 2.0     | 8.9     | -       | _        | ns   |

Table 79. EPF10K200S External Bidirectional Timing Parameters Note (1) Symbol -1 Speed Grade -2 Speed Grade -3 Speed Grade Unit Min Max Min Max Min Max t<sub>INSUBIDIR</sub> (2) 2.3 3.4 4.4 ns 0.0 t<sub>INHBIDIR</sub> (2) 0.0 0.0 ns tINSUBIDIR (3) 3.3 4.4 \_ ns t<sub>INHBIDIR</sub> (3) 0.0 0.0 \_ ns toutcobidir (2) 2.0 3.7 2.0 4.4 2.0 6.3 ns t<sub>XZBIDIR</sub> (2) 6.9 7.6 9.2 ns t<sub>ZXBIDIR</sub> (2) 5.9 6.6 \_ ns toutcobidir (3) 0.5 2.7 0.5 3.4 \_ \_ ns t<sub>XZBIDIR</sub> (3) 6.9 7.6 9.2 ns t<sub>ZXBIDIR</sub> (3) 6.6 5.9 \_ ns

# Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

(3) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

### **Altera Corporation**

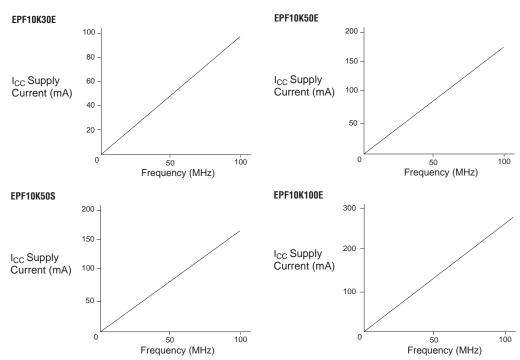

To better reflect actual designs, the power model (and the constant K in the power calculation equations) for continuous interconnect FLEX devices assumes that LEs drive FastTrack Interconnect channels. In contrast, the power model of segmented FPGAs assumes that all LEs drive only one short interconnect segment. This assumption may lead to inaccurate results when compared to measured power consumption for actual designs in segmented FPGAs.

Figure 31 shows the relationship between the current and operating frequency of FLEX 10KE devices.

Figure 31. FLEX 10KE I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 1 of 2)

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: lit\_reg@altera.com Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending

applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Altera Corporation

100