# E·XFL

# Altera - EPF10K200SBC356-2X Datasheet

Welcome to <u>E-XFL.COM</u>

# Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Active                                                          |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells | -                                                               |

| Total RAM Bits                 | -                                                               |

| Number of I/O                  | 274                                                             |

| Number of Gates                | -                                                               |

| Voltage - Supply               | 2.375V ~ 2.625V                                                 |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                 |

| Package / Case                 | 356-LBGA                                                        |

| Supplier Device Package        | 356-BGA (35x35)                                                 |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=epf10k200sbc356-2x |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2. FLEX 10KE Device Features | Table 2. FLEX 10KE Device Features |            |                          |  |  |  |  |  |  |  |  |

|------------------------------------|------------------------------------|------------|--------------------------|--|--|--|--|--|--|--|--|

| Feature                            | EPF10K100E (2)                     | EPF10K130E | EPF10K200E<br>EPF10K200S |  |  |  |  |  |  |  |  |

| Typical gates (1)                  | 100,000                            | 130,000    | 200,000                  |  |  |  |  |  |  |  |  |

| Maximum system gates               | 257,000                            | 342,000    | 513,000                  |  |  |  |  |  |  |  |  |

| Logic elements (LEs)               | 4,992                              | 6,656      | 9,984                    |  |  |  |  |  |  |  |  |

| EABs                               | 12                                 | 16         | 24                       |  |  |  |  |  |  |  |  |

| Total RAM bits                     | 49,152                             | 65,536     | 98,304                   |  |  |  |  |  |  |  |  |

| Maximum user I/O pins              | 338                                | 413        | 470                      |  |  |  |  |  |  |  |  |

#### Note to tables:

- (1) The embedded IEEE Std. 1149.1 JTAG circuitry adds up to 31,250 gates in addition to the listed typical or maximum system gates.

- (2) New EPF10K100B designs should use EPF10K100E devices.

# ...and More

- Fabricated on an advanced process and operate with a 2.5-V internal supply voltage

- In-circuit reconfigurability (ICR) via external configuration devices, intelligent controller, or JTAG port

- ClockLock<sup>™</sup> and ClockBoost<sup>™</sup> options for reduced clock \_ delay/skew and clock multiplication

- Built-in low-skew clock distribution trees

- 100% functional testing of all devices; test vectors or scan chains are not required

- Pull-up on I/O pins before and during configuration

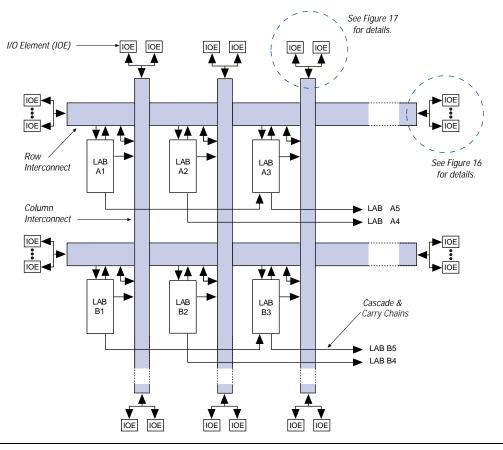

- Flexible interconnect

- FastTrack<sup>®</sup> Interconnect continuous routing structure for fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Tri-state emulation that implements internal tri-state buses

- Up to six global clock signals and four global clear signals

- Powerful I/O pins

- Individual tri-state output enable control for each pin

- Open-drain option on each I/O pin

- Programmable output slew-rate control to reduce switching noise

- Clamp to V<sub>CCIO</sub> user-selectable on a pin-by-pin basis

- Supports hot-socketing

EABs provide flexible options for driving and controlling clock signals. Different clocks and clock enables can be used for reading and writing to the EAB. Registers can be independently inserted on the data input, EAB output, write address, write enable signals, read address, and read enable signals. The global signals and the EAB local interconnect can drive write enable, read enable, and clock enable signals. The global signals, dedicated clock pins, and EAB local interconnect can drive the EAB clock signals. Because the LEs drive the EAB local interconnect, the LEs can control write enable, read enable, clear, clock, and clock enable signals.

An EAB is fed by a row interconnect and can drive out to row and column interconnects. Each EAB output can drive up to two row channels and up to two column channels; the unused row channel can be driven by other LEs. This feature increases the routing resources available for EAB outputs (see Figures 2 and 4). The column interconnect, which is adjacent to the EAB, has twice as many channels as other columns in the device.

# Logic Array Block

An LAB consists of eight LEs, their associated carry and cascade chains, LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure to the FLEX 10KE architecture, facilitating efficient routing with optimum device utilization and high performance (see Figure 7).

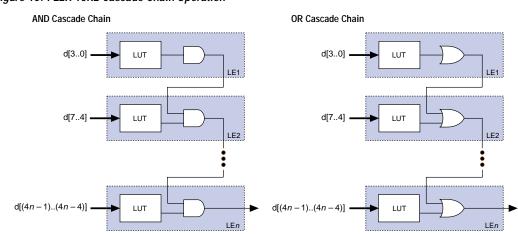

#### Cascade Chain

With the cascade chain, the FLEX 10KE architecture can implement functions that have a very wide fan-in. Adjacent LUTs can be used to compute portions of the function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. An a delay as low as 0.6 ns per LE, each additional LE provides four more inputs to the effective width of a function. Cascade chain logic can be created automatically by the Altera Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than eight bits are implemented automatically by linking several LABs together. For easier routing, a long cascade chain skips every other LAB in a row. A cascade chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB (e.g., the last LE of the first LAB in a row cascades to the first LE of the third LAB). The cascade chain does not cross the center of the row (e.g., in the EPF10K50E device, the cascade chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB). This break is due to the EAB's placement in the middle of the row.

Figure 10 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in. These examples show functions of 4n variables implemented with n LEs. The LE delay is 0.9 ns; the cascade chain delay is 0.6 ns. With the cascade chain, 2.7 ns are needed to decode a 16-bit address.

Figure 10. FLEX 10KE Cascade Chain Operation

Altera Corporation

# I/O Element

An IOE contains a bidirectional I/O buffer and a register that can be used either as an input register for external data that requires a fast setup time, or as an output register for data that requires fast clock-to-output performance. In some cases, using an LE register for an input register will result in a faster setup time than using an IOE register. IOEs can be used as input, output, or bidirectional pins. For bidirectional registered I/O implementation, the output register should be in the IOE, and the data input and output enable registers should be LE registers placed adjacent to the bidirectional pin. The Altera Compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. Figure 15 shows the bidirectional I/O registers.

# ClockLock & ClockBoost Timing Parameters

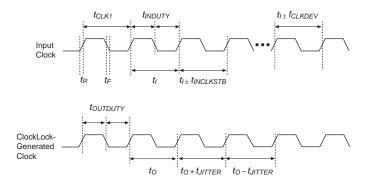

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. Figure 19 shows the incoming and generated clock specifications.

#### Figure 19. Specifications for Incoming & Generated Clocks

The  $t_l$  parameter refers to the nominal input clock period; the  $t_0$  parameter refers to the nominal output clock period.

The VCCINT pins must always be connected to a 2.5-V power supply. With a 2.5-V V<sub>CCINT</sub> level, input voltages are compatible with 2.5-V, 3.3-V, and 5.0-V inputs. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is at 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with V<sub>CCIO</sub> levels higher than 3.0 V achieve a faster timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ .

| Table 14. FLEX 10                                        | Table 14. FLEX 10KE MultiVolt I/O Support |              |      |                      |              |              |  |  |  |  |  |  |  |

|----------------------------------------------------------|-------------------------------------------|--------------|------|----------------------|--------------|--------------|--|--|--|--|--|--|--|

| V <sub>CCI0</sub> (V) Input Signal (V) Output Signal (V) |                                           |              |      |                      |              |              |  |  |  |  |  |  |  |

|                                                          | 2.5                                       | 3.3          | 5.0  | 2.5                  | 3.3          | 5.0          |  |  |  |  |  |  |  |

| 2.5                                                      | $\checkmark$                              | ✓(1)         | ✓(1) | <ul> <li></li> </ul> |              |              |  |  |  |  |  |  |  |

| 3.3                                                      | ~                                         | $\checkmark$ | ✓(1) | <b>√</b> (2)         | $\checkmark$ | $\checkmark$ |  |  |  |  |  |  |  |

Table 14 summarizes FLEX 10KE MultiVolt I/O support.

#### Notes:

(1) The PCI clamping diode must be disabled to drive an input with voltages higher than  $V_{\rm CCIO}$ .

(2) When  $V_{CCIO}$  = 3.3 V, a FLEX 10KE device can drive a 2.5-V device that has 3.3-V tolerant inputs.

Open-drain output pins on FLEX 10KE devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a  $V_{\rm IH}$  of 3.5 V. When the open-drain pin is active, it will drive low. When the pin is inactive, the trace will be pulled up to 5.0 V by the resistor. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The I<sub>OL</sub> current specification should be considered when selecting a pull-up resistor.

# Power Sequencing & Hot-Socketing

Because FLEX 10KE devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  power planes can be powered in any order.

Signals can be driven into FLEX 10KE devices before and during power up without damaging the device. Additionally, FLEX 10KE devices do not drive out during power up. Once operating conditions are reached, FLEX 10KE devices operate as specified by the user.

| Symbol            | Parameter                                      | Conditions                                                                         | Min                            | Тур | Max                                 | Unit       |

|-------------------|------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------|-----|-------------------------------------|------------|

| V <sub>IH</sub>   | High-level input<br>voltage                    |                                                                                    | $1.7, 0.5 \times V_{CCIO}$ (8) |     | 5.75                                | V          |

| V <sub>IL</sub>   | Low-level input voltage                        |                                                                                    | -0.5                           |     | 0.8,<br>0.3 × V <sub>CCIO</sub> (8) | V          |

| V <sub>OH</sub>   | 3.3-V high-level TTL<br>output voltage         | I <sub>OH</sub> = -8 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(9)</i>               | 2.4                            |     |                                     | V          |

|                   | 3.3-V high-level<br>CMOS output voltage        | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(9)</i>             | V <sub>CCIO</sub> -0.2         |     |                                     | V          |

|                   | 3.3-V high-level PCI<br>output voltage         | $I_{OH} = -0.5 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{ V} (9)$ | $0.9 	imes V_{CCIO}$           |     |                                     | V          |

|                   | 2.5-V high-level output voltage                | $I_{OH} = -0.1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V} (9)$                  | 2.1                            |     |                                     | V          |

|                   |                                                | I <sub>OH</sub> = –1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(9)</i>               | 2.0                            |     |                                     | V          |

|                   |                                                | $I_{OH} = -2 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (9)$                   | 1.7                            |     |                                     | V          |

| V <sub>OL</sub>   | 3.3-V low-level TTL<br>output voltage          | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (10)                     |                                |     | 0.45                                | V          |

|                   | 3.3-V low-level CMOS<br>output voltage         | $I_{OL} = 0.1 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ V} (10)$                  |                                |     | 0.2                                 | V          |

|                   | 3.3-V low-level PCI<br>output voltage          | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>(10)         |                                |     | $0.1 	imes V_{CCIO}$                | V          |

|                   | 2.5-V low-level output voltage                 | $I_{OL} = 0.1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V} (10)$                  |                                |     | 0.2                                 | V          |

|                   |                                                | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                      |                                |     | 0.4                                 | V          |

|                   |                                                | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                      |                                |     | 0.7                                 | V          |

| I <sub>I</sub>    | Input pin leakage<br>current                   | $V_{I} = V_{CCIOmax}$ to 0 V (11)                                                  | -10                            |     | 10                                  | μA         |

| I <sub>OZ</sub>   | Tri-stated I/O pin<br>leakage current          | $V_{O} = V_{CCIOmax}$ to 0 V (11)                                                  | -10                            |     | 10                                  | μ <b>A</b> |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current<br>(standby)    | V <sub>I</sub> = ground, no load, no<br>toggling inputs                            |                                | 5   |                                     | mA         |

|                   |                                                | V <sub>I</sub> = ground, no load, no toggling inputs <i>(12)</i>                   |                                | 10  |                                     | mA         |

| R <sub>CONF</sub> | Value of I/O pin pull-                         | V <sub>CCIO</sub> = 3.0 V (13)                                                     | 20                             |     | 50                                  | k¾         |

|                   | up resistor before and<br>during configuration | $V_{CCIO} = 2.3 V (13)$                                                            | 30                             |     | 80                                  | k¾         |

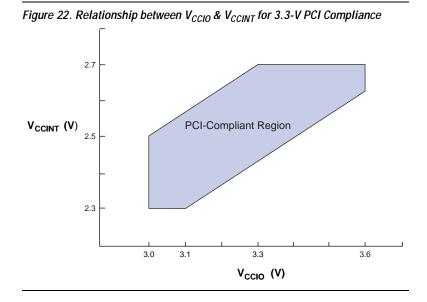

Figure 22 shows the required relationship between  $V_{CCIO}$  and  $V_{CCINT}$  for 3.3-V PCI compliance.

Figure 23 shows the typical output drive characteristics of FLEX 10KE devices with 3.3-V and 2.5-V V<sub>CCIO</sub>. The output driver is compliant to the 3.3-V *PCI Local Bus Specification*, *Revision 2.2* (when VCCIO pins are connected to 3.3 V). FLEX 10KE devices with a -1 speed grade also comply with the drive strength requirements of the *PCI Local Bus Specification*, *Revision 2.2* (when VCCINT pins are powered with a minimum supply of 2.375 V, and VCCIO pins are connected to 3.3 V). Therefore, these devices can be used in open 5.0-V PCI systems.

#### **Altera Corporation**

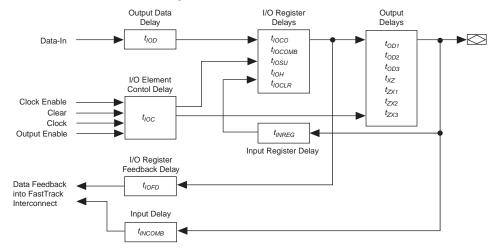

Figure 26. FLEX 10KE Device IOE Timing Model

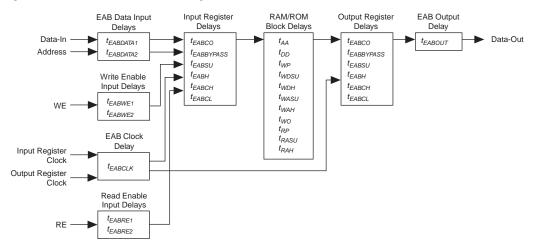

Figure 27. FLEX 10KE Device EAB Timing Model

| Symbol                 | Parameter                                                              | Conditions |

|------------------------|------------------------------------------------------------------------|------------|

| t <sub>EABDATA1</sub>  | Data or address delay to EAB for combinatorial input                   |            |

| t <sub>EABDATA2</sub>  | Data or address delay to EAB for registered input                      |            |

| t <sub>EABWE1</sub>    | Write enable delay to EAB for combinatorial input                      |            |

| t <sub>EABWE2</sub>    | Write enable delay to EAB for registered input                         |            |

| t <sub>EABRE1</sub>    | Read enable delay to EAB for combinatorial input                       |            |

| t <sub>EABRE2</sub>    | Read enable delay to EAB for registered input                          |            |

| t <sub>EABCLK</sub>    | EAB register clock delay                                               |            |

| t <sub>EABCO</sub>     | EAB register clock-to-output delay                                     |            |

| t <sub>EABBYPASS</sub> | Bypass register delay                                                  |            |

| t <sub>EABSU</sub>     | EAB register setup time before clock                                   |            |

| t <sub>EABH</sub>      | EAB register hold time after clock                                     |            |

| t <sub>EABCLR</sub>    | EAB register asynchronous clear time to output delay                   |            |

| t <sub>AA</sub>        | Address access delay (including the read enable to output delay)       |            |

| t <sub>WP</sub>        | Write pulse width                                                      |            |

| t <sub>RP</sub>        | Read pulse width                                                       |            |

| t <sub>WDSU</sub>      | Data setup time before falling edge of write pulse                     | (5)        |

| t <sub>WDH</sub>       | Data hold time after falling edge of write pulse                       | (5)        |

| t <sub>WASU</sub>      | Address setup time before rising edge of write pulse                   | (5)        |

| t <sub>WAH</sub>       | Address hold time after falling edge of write pulse                    | (5)        |

| t <sub>RASU</sub>      | Address setup time with respect to the falling edge of the read enable |            |

| t <sub>RAH</sub>       | Address hold time with respect to the falling edge of the read enable  |            |

| t <sub>WO</sub>        | Write enable to data output valid delay                                |            |

| t <sub>DD</sub>        | Data-in to data-out valid delay                                        |            |

| t <sub>EABOUT</sub>    | Data-out delay                                                         |            |

| t <sub>EABCH</sub>     | Clock high time                                                        |            |

| t <sub>EABCL</sub>     | Clock low time                                                         |            |

| Table 30. Ext          | ternal Bidirectional Timing Parameters Note (9)                                                 |            |

|------------------------|-------------------------------------------------------------------------------------------------|------------|

| Symbol                 | Parameter                                                                                       | Conditions |

| t <sub>INSUBIDIR</sub> | Setup time for bi-directional pins with global clock at same-row or same-<br>column LE register |            |

| t <sub>inhbidir</sub>  | Hold time for bidirectional pins with global clock at same-row or same-column LE register       |            |

| t <sub>INH</sub>       | Hold time with global clock at IOE register                                                     |            |

| <b>t</b> OUTCOBIDIR    | Clock-to-output delay for bidirectional pins with global clock at IOE register                  | C1 = 35 pF |

| t <sub>XZBIDIR</sub>   | Synchronous IOE output buffer disable delay                                                     | C1 = 35 pF |

| t <sub>ZXBIDIR</sub>   | Synchronous IOE output buffer enable delay, slow slew rate= off                                 | C1 = 35 pF |

#### Notes to tables:

- (1) Microparameters are timing delays contributed by individual architectural elements. These parameters cannot be measured explicitly.

- (2) Operating conditions: VCCIO =  $3.3 \text{ V} \pm 10\%$  for commercial or industrial use.

- (3) Operating conditions: VCCIO = 2.5 V ±5% for commercial or industrial use in EPF10K30E, EPF10K50S, EPF10K100E, EPF10K130E, and EPF10K200S devices.

- (4) Operating conditions: VCCIO = 3.3 V.

- (5) Because the RAM in the EAB is self-timed, this parameter can be ignored when the WE signal is registered.

- (6) EAB macroparameters are internal parameters that can simplify predicting the behavior of an EAB at its boundary; these parameters are calculated by summing selected microparameters.

- (7) These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

- (8) Contact Altera Applications for test circuit specifications and test conditions.

- (9) This timing parameter is sample-tested only.

- (10) This parameter is measured with the measurement and test conditions, including load, specified in the PCI Local Bus Specification, revision 2.2.

Figures 29 and 30 show the asynchronous and synchronous timing waveforms, respectively, or the EAB macroparameters in Tables 26 and 27.

EAB Asynchronous Read WE \_ a0 a2 Address a1 a3 – t<sub>EABAA</sub>t<sub>EABRCCOMB</sub> Data-Out d0 d3 d1 d2 **EAB Asynchronous Write** WE  $t_{EABWP}$ ► t<sub>EABWDH</sub> t<sub>EABWDSU</sub> ×. din0 din1 Data-In t<sub>EABWASU</sub> t<sub>EABWAH</sub> t<sub>EABWCCOMB</sub> Address a0 a1 a2  $t_{EABDD}$ Data-Out din0 din1 dout2

#### Figure 29. EAB Asynchronous Timing Waveforms

| Symbol                 | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|----------|---------|---------|------|

|                        | Min     | Max     | Min     | Max      | Min     | Max     |      |

| t <sub>EABAA</sub>     |         | 6.4     |         | 7.6      |         | 8.8     | ns   |

| t <sub>EABRCOMB</sub>  | 6.4     |         | 7.6     |          | 8.8     |         | ns   |

| t <sub>EABRCREG</sub>  | 4.4     |         | 5.1     |          | 6.0     |         | ns   |

| t <sub>EABWP</sub>     | 2.5     |         | 2.9     |          | 3.3     |         | ns   |

| t <sub>EABWCOMB</sub>  | 6.0     |         | 7.0     |          | 8.0     |         | ns   |

| t <sub>EABWCREG</sub>  | 6.8     |         | 7.8     |          | 9.0     |         | ns   |

| t <sub>EABDD</sub>     |         | 5.7     |         | 6.7      |         | 7.7     | ns   |

| t <sub>EABDATACO</sub> |         | 0.8     |         | 0.9      |         | 1.1     | ns   |

| t <sub>EABDATASU</sub> | 1.5     |         | 1.7     |          | 2.0     |         | ns   |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWESU</sub>   | 1.3     |         | 1.4     |          | 1.7     |         | ns   |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWDSU</sub>   | 1.5     |         | 1.7     |          | 2.0     |         | ns   |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWASU</sub>   | 3.0     |         | 3.6     |          | 4.3     |         | ns   |

| t <sub>EABWAH</sub>    | 0.5     |         | 0.5     |          | 0.4     |         | ns   |

| t <sub>EABWO</sub>     |         | 5.1     |         | 6.0      |         | 6.8     | ns   |

| Table 37. EPF10K30E External Bidirectional Timing Parameters       Notes (1), (2) |                |     |         |                |     |         |      |  |  |  |

|-----------------------------------------------------------------------------------|----------------|-----|---------|----------------|-----|---------|------|--|--|--|

| Symbol                                                                            | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | d Grade | Unit |  |  |  |

|                                                                                   | Min            | Max | Min     | Max            | Min | Max     |      |  |  |  |

| t <sub>INSUBIDIR</sub> (3)                                                        | 2.8            |     | 3.9     |                | 5.2 |         | ns   |  |  |  |

| t <sub>INHBIDIR</sub> (3)                                                         | 0.0            |     | 0.0     |                | 0.0 |         | ns   |  |  |  |

| t <sub>INSUBIDIR</sub> (4)                                                        | 3.8            |     | 4.9     |                | -   |         | ns   |  |  |  |

| t <sub>INHBIDIR</sub> (4)                                                         | 0.0            |     | 0.0     |                | -   |         | ns   |  |  |  |

| t <sub>OUTCOBIDIR</sub> (3)                                                       | 2.0            | 4.9 | 2.0     | 5.9            | 2.0 | 7.6     | ns   |  |  |  |

| t <sub>XZBIDIR</sub> (3)                                                          |                | 6.1 |         | 7.5            |     | 9.7     | ns   |  |  |  |

| t <sub>ZXBIDIR</sub> (3)                                                          |                | 6.1 |         | 7.5            |     | 9.7     | ns   |  |  |  |

| t <sub>OUTCOBIDIR</sub> (4)                                                       | 0.5            | 3.9 | 0.5     | 4.9            | -   | -       | ns   |  |  |  |

| t <sub>XZBIDIR</sub> (4)                                                          |                | 5.1 |         | 6.5            |     | -       | ns   |  |  |  |

| t <sub>ZXBIDIR</sub> (4)                                                          |                | 5.1 |         | 6.5            |     | -       | ns   |  |  |  |

# Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) These parameters are specified by characterization.

(3) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

(4) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

# Tables 38 through 44 show EPF10K50E device internal and external timing parameters.

| Symbol              | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|---------------------|---------|---------|---------|---------|---------|---------|------|

|                     | Min     | Мах     | Min     | Мах     | Min     | Max     |      |

| t <sub>LUT</sub>    |         | 0.6     |         | 0.9     |         | 1.3     | ns   |

| t <sub>CLUT</sub>   |         | 0.5     |         | 0.6     |         | 0.8     | ns   |

| t <sub>RLUT</sub>   |         | 0.7     |         | 0.8     |         | 1.1     | ns   |

| t <sub>PACKED</sub> |         | 0.4     |         | 0.5     |         | 0.6     | ns   |

| t <sub>EN</sub>     |         | 0.6     |         | 0.7     |         | 0.9     | ns   |

| t <sub>CICO</sub>   |         | 0.2     |         | 0.2     |         | 0.3     | ns   |

| t <sub>CGEN</sub>   |         | 0.5     |         | 0.5     |         | 0.8     | ns   |

| t <sub>CGENR</sub>  |         | 0.2     |         | 0.2     |         | 0.3     | ns   |

| t <sub>CASC</sub>   |         | 0.8     |         | 1.0     |         | 1.4     | ns   |

| t <sub>C</sub>      |         | 0.5     |         | 0.6     |         | 0.8     | ns   |

| t <sub>CO</sub>     |         | 0.7     |         | 0.7     |         | 0.9     | ns   |

| t <sub>COMB</sub>   |         | 0.5     |         | 0.6     |         | 0.8     | ns   |

| t <sub>SU</sub>     | 0.7     |         | 0.7     |         | 0.8     |         | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|------------------------|----------------|-----|---------|----------------|-----|----------|------|

|                        | Min            | Max | Min     | Max            | Min | Max      |      |

| t <sub>EABDATA1</sub>  |                | 1.7 |         | 2.0            |     | 2.7      | ns   |

| t <sub>EABDATA1</sub>  |                | 0.6 |         | 0.7            |     | 0.9      | ns   |

| t <sub>EABWE1</sub>    |                | 1.1 |         | 1.3            |     | 1.8      | ns   |

| t <sub>EABWE2</sub>    |                | 0.4 |         | 0.4            |     | 0.6      | ns   |

| t <sub>EABRE1</sub>    |                | 0.8 |         | 0.9            |     | 1.2      | ns   |

| t <sub>EABRE2</sub>    |                | 0.4 |         | 0.4            |     | 0.6      | ns   |

| t <sub>EABCLK</sub>    |                | 0.0 |         | 0.0            |     | 0.0      | ns   |

| t <sub>EABCO</sub>     |                | 0.3 |         | 0.3            |     | 0.5      | ns   |

| t <sub>EABBYPASS</sub> |                | 0.5 |         | 0.6            |     | 0.8      | ns   |

| t <sub>EABSU</sub>     | 0.9            |     | 1.0     |                | 1.4 |          | ns   |

| t <sub>EABH</sub>      | 0.4            |     | 0.4     |                | 0.6 |          | ns   |

| t <sub>EABCLR</sub>    | 0.3            |     | 0.3     |                | 0.5 |          | ns   |

| t <sub>AA</sub>        |                | 3.2 |         | 3.8            |     | 5.1      | ns   |

| t <sub>WP</sub>        | 2.5            |     | 2.9     |                | 3.9 |          | ns   |

| t <sub>RP</sub>        | 0.9            |     | 1.1     |                | 1.5 |          | ns   |

| t <sub>WDSU</sub>      | 0.9            |     | 1.0     |                | 1.4 |          | ns   |

| t <sub>WDH</sub>       | 0.1            |     | 0.1     |                | 0.2 |          | ns   |

| t <sub>WASU</sub>      | 1.7            |     | 2.0     |                | 2.7 |          | ns   |

| t <sub>WAH</sub>       | 1.8            |     | 2.1     |                | 2.9 |          | ns   |

| t <sub>RASU</sub>      | 3.1            |     | 3.7     |                | 5.0 |          | ns   |

| t <sub>RAH</sub>       | 0.2            |     | 0.2     |                | 0.3 |          | ns   |

| t <sub>WO</sub>        |                | 2.5 |         | 2.9            |     | 3.9      | ns   |

| t <sub>DD</sub>        |                | 2.5 |         | 2.9            |     | 3.9      | ns   |

| t <sub>EABOUT</sub>    |                | 0.5 |         | 0.6            |     | 0.8      | ns   |

| t <sub>EABCH</sub>     | 1.5            |     | 2.0     |                | 2.5 |          | ns   |

| t <sub>EABCL</sub>     | 2.5            |     | 2.9     |                | 3.9 |          | ns   |

| Table 43. EPF10    | K50E Externa | l Timing Pai   | rameters | Notes (1), (   | (2) |          |      |

|--------------------|--------------|----------------|----------|----------------|-----|----------|------|

| Symbol             | -1 Spee      | -1 Speed Grade |          | -2 Speed Grade |     | ed Grade | Unit |

|                    | Min          | Max            | Min      | Max            | Min | Max      |      |

| t <sub>DRR</sub>   |              | 8.5            |          | 10.0           |     | 13.5     | ns   |

| t <sub>INSU</sub>  | 2.7          |                | 3.2      |                | 4.3 |          | ns   |

| t <sub>INH</sub>   | 0.0          |                | 0.0      |                | 0.0 |          | ns   |

| t <sub>оитсо</sub> | 2.0          | 4.5            | 2.0      | 5.2            | 2.0 | 7.3      | ns   |

| t <sub>PCISU</sub> | 3.0          |                | 4.2      |                | -   |          | ns   |

| t <sub>PCIH</sub>  | 0.0          |                | 0.0      |                | -   |          | ns   |

| t <sub>PCICO</sub> | 2.0          | 6.0            | 2.0      | 7.7            | -   | -        | ns   |

Table 44. EPF10K50E External Bidirectional Timing Parameters

Notes (1), (2)

| Symbol                  | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|-------------------------|----------------|-----|---------|----------------|-----|----------|------|

|                         | Min            | Max | Min     | Max            | Min | Max      |      |

| t <sub>INSUBIDIR</sub>  | 2.7            |     | 3.2     |                | 4.3 |          | ns   |

| t <sub>INHBIDIR</sub>   | 0.0            |     | 0.0     |                | 0.0 |          | ns   |

| t <sub>OUTCOBIDIR</sub> | 2.0            | 4.5 | 2.0     | 5.2            | 2.0 | 7.3      | ns   |

| t <sub>XZBIDIR</sub>    |                | 6.8 |         | 7.8            |     | 10.1     | ns   |

| t <sub>ZXBIDIR</sub>    |                | 6.8 |         | 7.8            |     | 10.1     | ns   |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) These parameters are specified by characterization.

Tables 45 through 51 show EPF10K100E device internal and external timing parameters.

| Table 45. EPF10K100E Device LE Timing Microparameters       Note (1) |                |     |                |     |                |     |      |

|----------------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|

| Symbol                                                               | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|                                                                      | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>LUT</sub>                                                     |                | 0.7 |                | 1.0 |                | 1.5 | ns   |

| t <sub>CLUT</sub>                                                    |                | 0.5 |                | 0.7 |                | 0.9 | ns   |

| t <sub>RLUT</sub>                                                    |                | 0.6 |                | 0.8 |                | 1.1 | ns   |

| t <sub>PACKED</sub>                                                  |                | 0.3 |                | 0.4 |                | 0.5 | ns   |

| t <sub>EN</sub>                                                      |                | 0.2 |                | 0.3 |                | 0.3 | ns   |

| t <sub>CICO</sub>                                                    |                | 0.1 |                | 0.1 |                | 0.2 | ns   |

| t <sub>CGEN</sub>                                                    |                | 0.4 |                | 0.5 |                | 0.7 | ns   |

| Symbol             | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|--------------------|----------------|------|----------------|------|----------------|------|------|

|                    | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>DRR</sub>   |                | 10.0 |                | 12.0 |                | 16.0 | ns   |

| t <sub>INSU</sub>  | 2.8            |      | 3.4            |      | 4.4            |      | ns   |

| t <sub>INH</sub>   | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| tоитсо             | 2.0            | 4.5  | 2.0            | 5.3  | 2.0            | 7.8  | ns   |

| t <sub>PCISU</sub> | 3.0            |      | 6.2            |      | -              |      | ns   |

| t <sub>PCIH</sub>  | 0.0            |      | 0.0            |      | -              |      | ns   |

| t <sub>PCICO</sub> | 2.0            | 6.0  | 2.0            | 8.9  | -              | -    | ns   |

Table 65. EPF10K200E External Bidirectional Timing Parameters Notes (1), (2)

| Symbol                  | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|-------------------------|---------|---------|---------|---------|---------|---------|------|

|                         | Min     | Max     | Min     | Max     | Min     | Max     |      |

| t <sub>INSUBIDIR</sub>  | 3.0     |         | 4.0     |         | 5.5     |         | ns   |

| t <sub>INHBIDIR</sub>   | 0.0     |         | 0.0     |         | 0.0     |         | ns   |

| t <sub>OUTCOBIDIR</sub> | 2.0     | 4.5     | 2.0     | 5.3     | 2.0     | 7.8     | ns   |

| t <sub>XZBIDIR</sub>    |         | 8.1     |         | 9.5     |         | 13.0    | ns   |

| t <sub>ZXBIDIR</sub>    |         | 8.1     |         | 9.5     |         | 13.0    | ns   |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) These parameters are specified by characterization.

Tables 66 through 79 show EPF10K50S and EPF10K200S device external timing parameters.

| Table 66. EPF10K50S Device LE Timing Microparameters (Part 1 of 2)       Note (1) |         |                |     |                |     |         |      |

|-----------------------------------------------------------------------------------|---------|----------------|-----|----------------|-----|---------|------|

| Symbol                                                                            | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | d Grade | Unit |

|                                                                                   | Min     | Max            | Min | Max            | Min | Max     |      |

| t <sub>LUT</sub>                                                                  |         | 0.6            |     | 0.8            |     | 1.1     | ns   |

| t <sub>CLUT</sub>                                                                 |         | 0.5            |     | 0.6            |     | 0.8     | ns   |

| t <sub>RLUT</sub>                                                                 |         | 0.6            |     | 0.7            |     | 0.9     | ns   |

| t <sub>PACKED</sub>                                                               |         | 0.2            |     | 0.3            |     | 0.4     | ns   |

| t <sub>EN</sub>                                                                   |         | 0.6            |     | 0.7            |     | 0.9     | ns   |

| t <sub>CICO</sub>                                                                 |         | 0.1            |     | 0.1            |     | 0.1     | ns   |

| t <sub>CGEN</sub>                                                                 |         | 0.4            |     | 0.5            |     | 0.6     | ns   |

| Symbol                       | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|------------------------------|----------------|-----|----------------|-----|----------------|------|------|

|                              | Min            | Max | Min            | Max | Min            | Max  |      |

| t <sub>DRR</sub>             |                | 8.0 |                | 9.5 |                | 12.5 | ns   |

| t <sub>INSU</sub> (2)        | 2.4            |     | 2.9            |     | 3.9            |      | ns   |

| t <sub>INH</sub> (2)         | 0.0            |     | 0.0            |     | 0.0            |      | ns   |

| t <sub>оитсо</sub> (2)       | 2.0            | 4.3 | 2.0            | 5.2 | 2.0            | 7.3  | ns   |

| t <sub>INSU</sub> (3)        | 2.4            |     | 2.9            |     |                |      | ns   |

| t <sub>INH</sub> (3)         | 0.0            |     | 0.0            |     |                |      | ns   |

| <b>t<sub>оитсо (3)</sub></b> | 0.5            | 3.3 | 0.5            | 4.1 |                |      | ns   |

| t <sub>PCISU</sub>           | 2.4            |     | 2.9            |     | -              |      | ns   |

| t <sub>PCIH</sub>            | 0.0            |     | 0.0            |     | -              |      | ns   |

| t <sub>PCICO</sub>           | 2.0            | 6.0 | 2.0            | 7.7 | -              | -    | ns   |

Table 72. EPF10K50S External Bidirectional Timing Parameters

Note (1)

| Symbol                     | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|----------------------------|----------------|-----|----------------|-----|----------------|------|------|

|                            | Min            | Мах | Min            | Max | Min            | Max  |      |

| t <sub>INSUBIDIR</sub> (2) | 2.7            |     | 3.2            |     | 4.3            |      | ns   |

| t <sub>INHBIDIR</sub> (2)  | 0.0            |     | 0.0            |     | 0.0            |      | ns   |

| t <sub>inhbidir</sub> (3)  | 0.0            |     | 0.0            |     | -              |      | ns   |

| t <sub>insubidir</sub> (3) | 3.7            |     | 4.2            |     | -              |      | ns   |

| toutcobidir (2)            | 2.0            | 4.5 | 2.0            | 5.2 | 2.0            | 7.3  | ns   |

| t <sub>XZBIDIR</sub> (2)   |                | 6.8 |                | 7.8 |                | 10.1 | ns   |

| t <sub>ZXBIDIR</sub> (2)   |                | 6.8 |                | 7.8 |                | 10.1 | ns   |

| toutcobidir (3)            | 0.5            | 3.5 | 0.5            | 4.2 | -              | -    |      |

| t <sub>XZBIDIR</sub> (3)   |                | 6.8 |                | 8.4 |                | -    | ns   |

| t <sub>ZXBIDIR</sub> (3)   |                | 6.8 |                | 8.4 |                | -    | ns   |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30.

(2) This parameter is measured without use of the ClockLock or ClockBoost circuits.

(3) This parameter is measured with use of the ClockLock or ClockBoost circuits

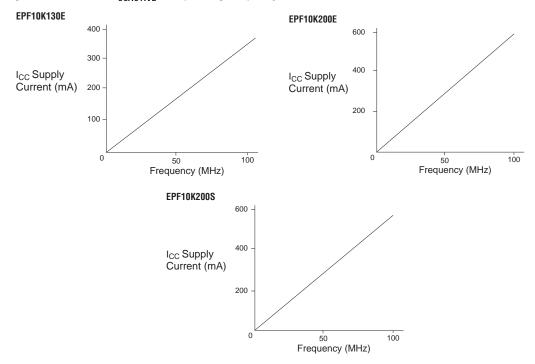

# Figure 31. FLEX 10KE I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 2 of 2)

# Configuration & Operation

The FLEX 10KE architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

# **Operating Modes**

The FLEX 10KE architecture uses SRAM configuration elements that require configuration data to be loaded every time the circuit powers up. The process of physically loading the SRAM data into the device is called *configuration*. Before configuration, as  $V_{CC}$  rises, the device initiates a Power-On Reset (POR). This POR event clears the device and prepares it for configuration. The FLEX 10KE POR time does not exceed 50 µs.

When configuring with a configuration device, refer to the respective configuration device data sheet for POR timing information.

Additionally, the Altera software offers several features that help plan for future device migration by preventing the use of conflicting I/O pins.

| Table 81. I/O Counts for FLEX 10KA & FLEX 10KE Devices |           |                |           |  |  |  |

|--------------------------------------------------------|-----------|----------------|-----------|--|--|--|

| FLEX 10                                                | KA        | FLEX 10        | KE        |  |  |  |

| Device                                                 | I/O Count | Device         | I/O Count |  |  |  |

| EPF10K30AF256                                          | 191       | EPF10K30EF256  | 176       |  |  |  |

| EPF10K30AF484                                          | 246       | EPF10K30EF484  | 220       |  |  |  |

| EPF10K50VB356                                          | 274       | EPF10K50SB356  | 220       |  |  |  |

| EPF10K50VF484                                          | 291       | EPF10K50EF484  | 254       |  |  |  |

| EPF10K50VF484                                          | 291       | EPF10K50SF484  | 254       |  |  |  |

| EPF10K100AF484                                         | 369       | EPF10K100EF484 | 338       |  |  |  |

**Configuration Schemes**

The configuration data for a FLEX 10KE device can be loaded with one of five configuration schemes (see Table 82), chosen on the basis of the target application. An EPC1, EPC2, or EPC16 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of a FLEX 10KE device, allowing automatic configuration on system power-up.

Multiple FLEX 10KE devices can be configured in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device. Additional FLEX 10K, FLEX 10KA, FLEX 10KE, and FLEX 6000 devices can be configured in the same serial chain.

| Table 82. Data Sources for FLEX 10KE Configuration |                                                                                                     |  |  |  |  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| Configuration Scheme                               | Data Source                                                                                         |  |  |  |  |

| Configuration device                               | EPC1, EPC2, or EPC16 configuration device                                                           |  |  |  |  |

| Passive serial (PS)                                | BitBlaster, ByteBlasterMV, or MasterBlaster download cables, or serial data source                  |  |  |  |  |

| Passive parallel asynchronous (PPA)                | Parallel data source                                                                                |  |  |  |  |

| Passive parallel synchronous (PPS)                 | Parallel data source                                                                                |  |  |  |  |

| JTAG                                               | BitBlaster or ByteBlasterMV download cables, or<br>microprocessor with a Jam STAPL file or JBC file |  |  |  |  |