# E·XFL

## Intel - EPF10K30EFC256-2N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 216                                                          |

| Number of Logic Elements/Cells | 1728                                                         |

| Total RAM Bits                 | 24576                                                        |

| Number of I/O                  | 176                                                          |

| Number of Gates                | 119000                                                       |

| Voltage - Supply               | 2.375V ~ 2.625V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                              |

| Package / Case                 | 256-BGA                                                      |

| Supplier Device Package        | 256-FBGA (17x17)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k30efc256-2n |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 5. FLEX 10KE Perform                  | nance    |         |                |                |                |     |

|---------------------------------------------|----------|---------|----------------|----------------|----------------|-----|

| Application                                 | Resource | es Used | Performance    |                |                |     |

|                                             | LEs      | EABs    | -1 Speed Grade | -2 Speed Grade | -3 Speed Grade |     |

| 16-bit loadable counter                     | 16       | 0       | 285            | 250            | 200            | MHz |

| 16-bit accumulator                          | 16       | 0       | 285            | 250            | 200            | MHz |

| 16-to-1 multiplexer (1)                     | 10       | 0       | 3.5            | 4.9            | 7.0            | ns  |

| 16-bit multiplier with 3-stage pipeline (2) | 592      | 0       | 156            | 131            | 93             | MHz |

| $256 \times 16$ RAM read cycle speed (2)    | 0        | 1       | 196            | 154            | 118            | MHz |

| $256 \times 16$ RAM write cycle speed (2)   | 0        | 1       | 185            | 143            | 106            | MHz |

## Table 5. FLEX 10KE Performance

#### Notes:

(1) This application uses combinatorial inputs and outputs.

(2) This application uses registered inputs and outputs.

Table 6 shows FLEX 10KE performance for more complex designs. These designs are available as Altera MegaCore $^{\circ}$  functions.

| Table 6. FLEX 10KE Performanc                                  | e for Complex | Designs        |                |                |        |  |

|----------------------------------------------------------------|---------------|----------------|----------------|----------------|--------|--|

| Application                                                    | LEs Used      |                | Performance    |                |        |  |

|                                                                |               | -1 Speed Grade | -2 Speed Grade | -3 Speed Grade |        |  |

| 8-bit, 16-tap parallel finite impulse<br>response (FIR) filter | 597           | 192            | 156            | 116            | MSPS   |  |

| 8-bit, 512-point fast Fourier                                  | 1,854         | 23.4           | 28.7           | 38.9           | µs (1) |  |

| transform (FFT) function                                       |               | 113            | 92             | 68             | MHz    |  |

| a16450 universal asynchronous<br>receiver/transmitter (UART)   | 342           | 36             | 28             | 20.5           | MHz    |  |

#### Note:

(1) These values are for calculation time. Calculation time = number of clocks required /  $f_{max}$ . Number of clocks required = ceiling [log 2 (points)/2] × [points +14 + ceiling]

EABs provide flexible options for driving and controlling clock signals. Different clocks and clock enables can be used for reading and writing to the EAB. Registers can be independently inserted on the data input, EAB output, write address, write enable signals, read address, and read enable signals. The global signals and the EAB local interconnect can drive write enable, read enable, and clock enable signals. The global signals, dedicated clock pins, and EAB local interconnect can drive the EAB clock signals. Because the LEs drive the EAB local interconnect, the LEs can control write enable, read enable, clear, clock, and clock enable signals.

An EAB is fed by a row interconnect and can drive out to row and column interconnects. Each EAB output can drive up to two row channels and up to two column channels; the unused row channel can be driven by other LEs. This feature increases the routing resources available for EAB outputs (see Figures 2 and 4). The column interconnect, which is adjacent to the EAB, has twice as many channels as other columns in the device.

## Logic Array Block

An LAB consists of eight LEs, their associated carry and cascade chains, LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure to the FLEX 10KE architecture, facilitating efficient routing with optimum device utilization and high performance (see Figure 7).

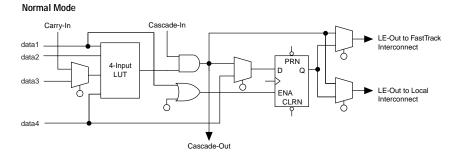

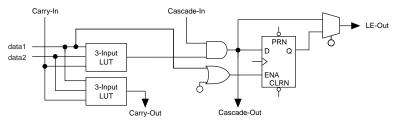

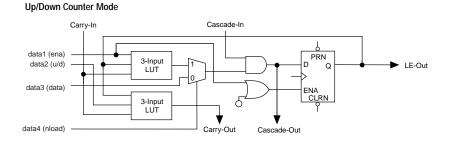

## Figure 11. FLEX 10KE LE Operating Modes

#### **Clearable Counter Mode**

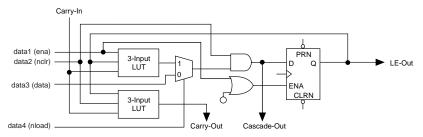

In addition to the six clear and preset modes, FLEX 10KE devices provide a chip-wide reset pin that can reset all registers in the device. Use of this feature is set during design entry. In any of the clear and preset modes, the chip-wide reset overrides all other signals. Registers with asynchronous presets may be preset when the chip-wide reset is asserted. Inversion can be used to implement the asynchronous preset. Figure 12 shows examples of how to setup the preset and clear inputs for the desired functionality.

## Altera Corporation

## ClockLock & ClockBoost Features

To support high-speed designs, FLEX 10KE devices offer optional ClockLock and ClockBoost circuitry containing a phase-locked loop (PLL) used to increase design speed and reduce resource usage. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by resource sharing within the device. The ClockBoost feature allows the designer to distribute a low-speed clock and multiply that clock on-device. Combined, the ClockLock and ClockBoost features provide significant improvements in system performance and bandwidth.

All FLEX 10KE devices, except EPF10K50E and EPF10K200E devices, support ClockLock and ClockBoost circuitry. EPF10K50S and EPF10K200S devices support this circuitry. Devices that support Clock-Lock and ClockBoost circuitry are distinguished with an "X" suffix in the ordering code; for instance, the EPF10K200SFC672-1X device supports this circuit.

The ClockLock and ClockBoost features in FLEX 10KE devices are enabled through the Altera software. External devices are not required to use these features. The output of the ClockLock and ClockBoost circuits is not available at any of the device pins.

The ClockLock and ClockBoost circuitry locks onto the rising edge of the incoming clock. The circuit output can drive the clock inputs of registers only; the generated clock cannot be gated or inverted.

The dedicated clock pin (GCLK1) supplies the clock to the ClockLock and ClockBoost circuitry. When the dedicated clock pin is driving the ClockLock or ClockBoost circuitry, it cannot drive elsewhere in the device.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to the GCLK1 pin. In the Altera software, the GCLK1 pin can feed both the ClockLock and ClockBoost circuitry in the FLEX 10KE device. However, when both circuits are used, the other clock pin cannot be used.

Tables 12 and 13 summarize the ClockLock and ClockBoost parameters for -1 and -2 speed-grade devices, respectively.

| Symbol                | Parameter                                                                     | Condition            | Min | Тур | Max        | Unit |

|-----------------------|-------------------------------------------------------------------------------|----------------------|-----|-----|------------|------|

| t <sub>R</sub>        | Input rise time                                                               |                      |     |     | 5          | ns   |

| t <sub>F</sub>        | Input fall time                                                               |                      |     |     | 5          | ns   |

| t <sub>INDUTY</sub>   | Input duty cycle                                                              |                      | 40  |     | 60         | %    |

| f <sub>CLK1</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 1)       |                      | 25  |     | 180        | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2)       |                      | 16  |     | 90         | MHz  |

| f <sub>CLKDEV</sub>   | Input deviation from user<br>specification in the MAX+PLUS II<br>software (1) |                      |     |     | 25,000 (2) | PPM  |

| t <sub>INCLKSTB</sub> | Input clock stability (measured between adjacent clocks)                      |                      |     |     | 100        | ps   |

| t <sub>LOCK</sub>     | Time required for ClockLock or ClockBoost to acquire lock $(3)$               |                      |     |     | 10         | μs   |

| t <sub>JITTER</sub>   | Jitter on ClockLock or ClockBoost-                                            | $t_{INCLKSTB} < 100$ |     |     | 250        | ps   |

|                       | generated clock (4)                                                           | $t_{INCLKSTB} < 50$  |     |     | 200 (4)    | ps   |

| t <sub>OUTDUTY</sub>  | Duty cycle for ClockLock or<br>ClockBoost-generated clock                     |                      | 40  | 50  | 60         | %    |

| Table 17. 32-            | Bit IDCOD           | E for FLEX 10KE Devices | Note (1)                             |                         |  |  |  |  |

|--------------------------|---------------------|-------------------------|--------------------------------------|-------------------------|--|--|--|--|

| Device                   |                     | IDCODE (32 Bits)        |                                      |                         |  |  |  |  |

|                          | Version<br>(4 Bits) | Part Number (16 Bits)   | Manufacturer's<br>Identity (11 Bits) | <b>1 (1 Bit)</b><br>(2) |  |  |  |  |

| EPF10K30E                | 0001                | 0001 0000 0011 0000     | 00001101110                          | 1                       |  |  |  |  |

| EPF10K50E<br>EPF10K50S   | 0001                | 0001 0000 0101 0000     | 00001101110                          | 1                       |  |  |  |  |

| EPF10K100E               | 0010                | 0000 0001 0000 0000     | 00001101110                          | 1                       |  |  |  |  |

| EPF10K130E               | 0001                | 0000 0001 0011 0000     | 00001101110                          | 1                       |  |  |  |  |

| EPF10K200E<br>EPF10K200S | 0001                | 0000 0010 0000 0000     | 00001101110                          | 1                       |  |  |  |  |

#### Notes:

(1) The most significant bit (MSB) is on the left.

(2) The least significant bit (LSB) for all JTAG IDCODEs is 1.

FLEX 10KE devices include weak pull-up resistors on the JTAG pins.

For more information, see the following documents:

- Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- BitBlaster Serial Download Cable Data Sheet

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- Jam Programming & Test Language Specification

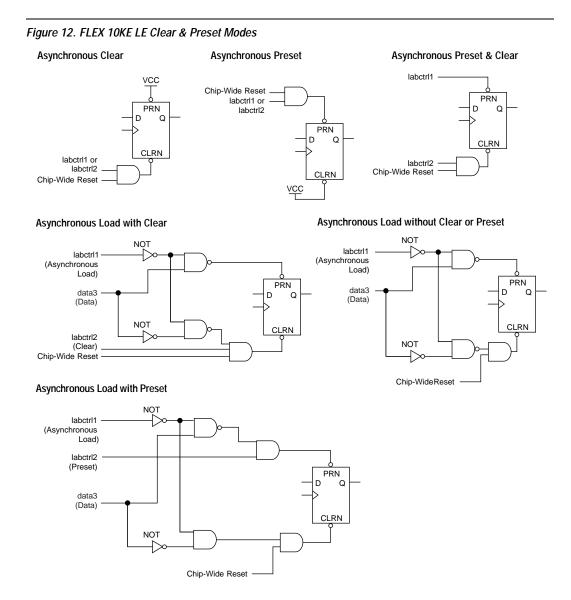

Figure 20 shows the timing requirements for the JTAG signals.

Figure 20. FLEX 10KE JTAG Waveforms

## Table 18 shows the timing parameters and values for FLEX 10KE devices.

| Sumbol            | Parameter                                      | Min    | Max   | Unit |

|-------------------|------------------------------------------------|--------|-------|------|

| Symbol            | Parameter                                      | IVIIII | IVIAX | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100    |       | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50     |       | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50     |       | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20     |       | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45     |       | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |        | 25    | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |        | 25    | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |        | 25    | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20     |       | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45     |       | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |        | 35    | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output |        | 35    | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |        | 35    | ns   |

| Symbol            | Parameter                                      | Conditions                                                                         | Min                            | Тур | Max                                 | Unit       |

|-------------------|------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------|-----|-------------------------------------|------------|

| V <sub>IH</sub>   | High-level input<br>voltage                    |                                                                                    | $1.7, 0.5 \times V_{CCIO}$ (8) |     | 5.75                                | V          |

| V <sub>IL</sub>   | Low-level input voltage                        |                                                                                    | -0.5                           |     | 0.8,<br>0.3 × V <sub>CCIO</sub> (8) | V          |

| V <sub>OH</sub>   | 3.3-V high-level TTL<br>output voltage         | I <sub>OH</sub> = -8 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(9)</i>               | 2.4                            |     |                                     | V          |

|                   | 3.3-V high-level<br>CMOS output voltage        | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(9)</i>             | V <sub>CCIO</sub> -0.2         |     |                                     | V          |

|                   | 3.3-V high-level PCI<br>output voltage         | $I_{OH} = -0.5 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{ V} (9)$ | $0.9 	imes V_{CCIO}$           |     |                                     | V          |

|                   | 2.5-V high-level output voltage                | $I_{OH} = -0.1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V} (9)$                  | 2.1                            |     |                                     | V          |

|                   |                                                | I <sub>OH</sub> = –1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(9)</i>               | 2.0                            |     |                                     | V          |

|                   |                                                | $I_{OH} = -2 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (9)$                   | 1.7                            |     |                                     | V          |

| V <sub>OL</sub>   | 3.3-V low-level TTL<br>output voltage          | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (10)                     |                                |     | 0.45                                | V          |

|                   | 3.3-V low-level CMOS<br>output voltage         | $I_{OL} = 0.1 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ V} (10)$                  |                                |     | 0.2                                 | V          |

|                   | 3.3-V low-level PCI<br>output voltage          | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>(10)         |                                |     | $0.1 	imes V_{CCIO}$                | V          |

|                   | 2.5-V low-level output voltage                 | $I_{OL} = 0.1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V} (10)$                  |                                |     | 0.2                                 | V          |

|                   |                                                | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                      |                                |     | 0.4                                 | V          |

|                   |                                                | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                      |                                |     | 0.7                                 | V          |

| I <sub>I</sub>    | Input pin leakage<br>current                   | $V_{I} = V_{CCIOmax}$ to 0 V (11)                                                  | -10                            |     | 10                                  | μA         |

| I <sub>OZ</sub>   | Tri-stated I/O pin<br>leakage current          | $V_{O} = V_{CCIOmax}$ to 0 V (11)                                                  | -10                            |     | 10                                  | μ <b>A</b> |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current<br>(standby)    | V <sub>I</sub> = ground, no load, no<br>toggling inputs                            |                                | 5   |                                     | mA         |

|                   |                                                | V <sub>I</sub> = ground, no load, no toggling inputs <i>(12)</i>                   |                                | 10  |                                     | mA         |

| R <sub>CONF</sub> | Value of I/O pin pull-                         | V <sub>CCIO</sub> = 3.0 V (13)                                                     | 20                             |     | 50                                  | k¾         |

|                   | up resistor before and<br>during configuration | $V_{CCIO} = 2.3 V (13)$                                                            | 30                             |     | 80                                  | k¾         |

| Table 2            | 3. FLEX 10KE Device Capacit                 | ance Note (14)                      |     |     |      |

|--------------------|---------------------------------------------|-------------------------------------|-----|-----|------|

| Symbol             | Parameter                                   | Conditions                          | Min | Max | Unit |

| C <sub>IN</sub>    | Input capacitance                           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |

| C <sub>INCLK</sub> | Input capacitance on<br>dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |

| C <sub>OUT</sub>   | Output capacitance                          | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before  $V_{CCINT}$  and  $V_{CCIO}$  are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  V or 3.3 V.

- (7) These values are specified under the FLEX 10KE Recommended Operating Conditions shown in Tables 20 and 21.

(8) The FLEX 10KE input buffers are compatible with 2.5-V, 3.3-V (LVTTL and LVCMOS), and 5.0-V TTL and CMOS

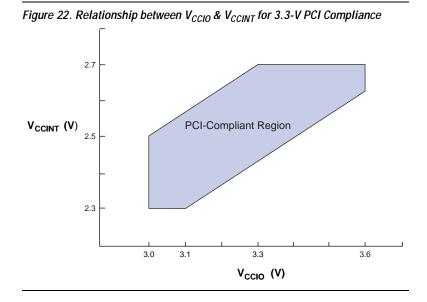

- signals. Additionally, the input buffers are 3.3-V PCI compliant when  $V_{CCIO}$  and  $V_{CCINT}$  meet the relationship shown in Figure 22.

- (9) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (10) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (11) This value is specified for normal device operation. The value may vary during power-up.

- (12) This parameter applies to -1 speed-grade commercial-temperature devices and -2 speed-grade-industrial temperature devices.

- (13) Pin pull-up resistance values will be lower if the pin is driven higher than  $V_{CCIO}$  by an external source.

- (14) Capacitance is sample-tested only.

Figure 22 shows the required relationship between  $V_{CCIO}$  and  $V_{CCINT}$  for 3.3-V PCI compliance.

Figure 23 shows the typical output drive characteristics of FLEX 10KE devices with 3.3-V and 2.5-V V<sub>CCIO</sub>. The output driver is compliant to the 3.3-V *PCI Local Bus Specification*, *Revision 2.2* (when VCCIO pins are connected to 3.3 V). FLEX 10KE devices with a -1 speed grade also comply with the drive strength requirements of the *PCI Local Bus Specification*, *Revision 2.2* (when VCCINT pins are powered with a minimum supply of 2.375 V, and VCCIO pins are connected to 3.3 V). Therefore, these devices can be used in open 5.0-V PCI systems.

#### **Altera Corporation**

| Symbol                  | Parameter                                                                                                            |     |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| t <sub>DIN2IOE</sub>    | Delay from dedicated input pin to IOE control input                                                                  | (7) |  |  |  |  |

| t <sub>DIN2LE</sub>     | Delay from dedicated input pin to LE or EAB control input                                                            | (7) |  |  |  |  |

| t <sub>DCLK2IOE</sub>   | Delay from dedicated clock pin to IOE clock                                                                          | (7) |  |  |  |  |

| t <sub>DCLK2LE</sub>    | Delay from dedicated clock pin to LE or EAB clock                                                                    | (7) |  |  |  |  |

| t <sub>DIN2DATA</sub>   | Delay from dedicated input or clock to LE or EAB data                                                                | (7) |  |  |  |  |

| t <sub>SAMELAB</sub>    | Routing delay for an LE driving another LE in the same LAB                                                           |     |  |  |  |  |

| t <sub>SAMEROW</sub>    | Routing delay for a row IOE, LE, or EAB driving a row IOE, LE, or EAB in the same row                                | (7) |  |  |  |  |

| t <sub>SAMECOLUMN</sub> | Routing delay for an LE driving an IOE in the same column                                                            | (7) |  |  |  |  |

| t <sub>DIFFROW</sub>    | Routing delay for a column IOE, LE, or EAB driving an LE or EAB in a different row                                   | (7) |  |  |  |  |

| t <sub>TWOROWS</sub>    | Routing delay for a row IOE or EAB driving an LE or EAB in a different row                                           | (7) |  |  |  |  |

| t <sub>LEPERIPH</sub>   | Routing delay for an LE driving a control signal of an IOE via the peripheral control bus                            | (7) |  |  |  |  |

| t <sub>LABCARRY</sub>   | Routing delay for the carry-out signal of an LE driving the carry-in signal of a different LE in a different LAB     |     |  |  |  |  |

| t <sub>LABCASC</sub>    | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |     |  |  |  |  |

| Table 29. Ex       | ternal Timing Parameters                                                                       |            |

|--------------------|------------------------------------------------------------------------------------------------|------------|

| Symbol             | Parameter                                                                                      | Conditions |

| t <sub>DRR</sub>   | Register-to-register delay via four LEs, three row interconnects, and four local interconnects | (8)        |

| t <sub>INSU</sub>  | Setup time with global clock at IOE register                                                   | (9)        |

| t <sub>INH</sub>   | Hold time with global clock at IOE register                                                    | (9)        |

| t <sub>outco</sub> | Clock-to-output delay with global clock at IOE register                                        | (9)        |

| t <sub>PCISU</sub> | Setup time with global clock for registers used in PCI designs                                 | (9),(10)   |

| t <sub>PCIH</sub>  | Hold time with global clock for registers used in PCI designs                                  | (9),(10)   |

| t <sub>PCICO</sub> | Clock-to-output delay with global clock for registers used in PCI designs                      | (9),(10)   |

| Symbol                  | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | ed Grade | Unit |

|-------------------------|---------|---------|---------|---------|---------|----------|------|

|                         | Min     | Max     | Min     | Max     | Min     | Max      |      |

| t <sub>DIN2IOE</sub>    |         | 1.8     |         | 2.4     |         | 2.9      | ns   |

| t <sub>DIN2LE</sub>     |         | 1.5     |         | 1.8     |         | 2.4      | ns   |

| t <sub>DIN2DATA</sub>   |         | 1.5     |         | 1.8     |         | 2.2      | ns   |

| t <sub>DCLK2IOE</sub>   |         | 2.2     |         | 2.6     |         | 3.0      | ns   |

| t <sub>DCLK2LE</sub>    |         | 1.5     |         | 1.8     |         | 2.4      | ns   |

| t <sub>SAMELAB</sub>    |         | 0.1     |         | 0.2     |         | 0.3      | ns   |

| t <sub>SAMEROW</sub>    |         | 2.0     |         | 2.4     |         | 2.7      | ns   |

| t <sub>SAMECOLUMN</sub> |         | 0.7     |         | 1.0     |         | 0.8      | ns   |

| t <sub>DIFFROW</sub>    |         | 2.7     |         | 3.4     |         | 3.5      | ns   |

| t <sub>TWOROWS</sub>    |         | 4.7     |         | 5.8     |         | 6.2      | ns   |

| t <sub>LEPERIPH</sub>   |         | 2.7     |         | 3.4     |         | 3.8      | ns   |

| t <sub>LABCARRY</sub>   |         | 0.3     |         | 0.4     |         | 0.5      | ns   |

| t <sub>LABCASC</sub>    |         | 0.8     |         | 0.8     |         | 1.1      | ns   |

| Symbol                            | -1 Spee | ed Grade | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|-----------------------------------|---------|----------|---------|----------------|-----|----------|------|

|                                   | Min     | Max      | Min     | Max            | Min | Max      |      |

| t <sub>DRR</sub>                  |         | 8.0      |         | 9.5            |     | 12.5     | ns   |

| t <sub>INSU</sub> (3)             | 2.1     |          | 2.5     |                | 3.9 |          | ns   |

| t <sub>INH</sub> (3)              | 0.0     |          | 0.0     |                | 0.0 |          | ns   |

| <sup>t</sup> оитсо <sup>(3)</sup> | 2.0     | 4.9      | 2.0     | 5.9            | 2.0 | 7.6      | ns   |

| t <sub>INSU</sub> (4)             | 1.1     |          | 1.5     |                | -   |          | ns   |

| t <sub>INH</sub> (4)              | 0.0     |          | 0.0     |                | -   |          | ns   |

| t <sub>оитсо</sub> (4)            | 0.5     | 3.9      | 0.5     | 4.9            | -   | -        | ns   |

| t <sub>PCISU</sub>                | 3.0     |          | 4.2     |                | -   |          | ns   |

| t <sub>PCIH</sub>                 | 0.0     |          | 0.0     |                | -   |          | ns   |

| t <sub>PCICO</sub>                | 2.0     | 6.0      | 2.0     | 7.5            | -   | -        | ns   |

| Table 38. EPF10K | 50E Device | LE Timing N | licroparame | eters (Part 2 | ? of 2) No     | te (1) |      |

|------------------|------------|-------------|-------------|---------------|----------------|--------|------|

| Symbol           | -1 Spee    | d Grade     | -2 Spee     | d Grade       | -3 Speed Grade |        | Unit |

|                  | Min        | Max         | Min         | Max           | Min            | Max    |      |

| t <sub>H</sub>   | 0.9        |             | 1.0         |               | 1.4            |        | ns   |

| t <sub>PRE</sub> |            | 0.5         |             | 0.6           |                | 0.8    | ns   |

| t <sub>CLR</sub> |            | 0.5         |             | 0.6           |                | 0.8    | ns   |

| t <sub>CH</sub>  | 2.0        |             | 2.5         |               | 3.0            |        | ns   |

| t <sub>CL</sub>  | 2.0        |             | 2.5         |               | 3.0            |        | ns   |

| Table 39. EPF10     | 1       |          | -<br>I  |          | te (1)  | i        |      |

|---------------------|---------|----------|---------|----------|---------|----------|------|

| Symbol              | -1 Spee | ed Grade | -2 Spee | ed Grade | -3 Spee | ed Grade | Unit |

|                     | Min     | Max      | Min     | Max      | Min     | Max      |      |

| t <sub>IOD</sub>    |         | 2.2      |         | 2.4      |         | 3.3      | ns   |

| t <sub>IOC</sub>    |         | 0.3      |         | 0.3      |         | 0.5      | ns   |

| t <sub>IOCO</sub>   |         | 1.0      |         | 1.0      |         | 1.4      | ns   |

| t <sub>IOCOMB</sub> |         | 0.0      |         | 0.0      |         | 0.2      | ns   |

| t <sub>IOSU</sub>   | 1.0     |          | 1.2     |          | 1.7     |          | ns   |

| t <sub>IOH</sub>    | 0.3     |          | 0.3     |          | 0.5     |          | ns   |

| t <sub>IOCLR</sub>  |         | 0.9      |         | 1.0      |         | 1.4      | ns   |

| t <sub>OD1</sub>    |         | 0.8      |         | 0.9      |         | 1.2      | ns   |

| t <sub>OD2</sub>    |         | 0.3      |         | 0.4      |         | 0.7      | ns   |

| t <sub>OD3</sub>    |         | 3.0      |         | 3.5      |         | 3.5      | ns   |

| t <sub>XZ</sub>     |         | 1.4      |         | 1.7      |         | 2.3      | ns   |

| t <sub>ZX1</sub>    |         | 1.4      |         | 1.7      |         | 2.3      | ns   |

| t <sub>ZX2</sub>    |         | 0.9      |         | 1.2      |         | 1.8      | ns   |

| t <sub>ZX3</sub>    |         | 3.6      |         | 4.3      |         | 4.6      | ns   |

| t <sub>INREG</sub>  |         | 4.9      |         | 5.8      |         | 7.8      | ns   |

| t <sub>IOFD</sub>   |         | 2.8      |         | 3.3      |         | 4.5      | ns   |

| t <sub>INCOMB</sub> |         | 2.8      |         | 3.3      |         | 4.5      | ns   |

| Symbol                 | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|----------|---------|---------|------|

|                        | Min     | Мах     | Min     | Max      | Min     | Max     |      |

| t <sub>EABAA</sub>     |         | 6.4     |         | 7.6      |         | 10.2    | ns   |

| t <sub>EABRCOMB</sub>  | 6.4     |         | 7.6     |          | 10.2    |         | ns   |

| t <sub>EABRCREG</sub>  | 4.4     |         | 5.1     |          | 7.0     |         | ns   |

| t <sub>EABWP</sub>     | 2.5     |         | 2.9     |          | 3.9     |         | ns   |

| t <sub>EABWCOMB</sub>  | 6.0     |         | 7.0     |          | 9.5     |         | ns   |

| t <sub>EABWCREG</sub>  | 6.8     |         | 7.8     |          | 10.6    |         | ns   |

| t <sub>EABDD</sub>     |         | 5.7     |         | 6.7      |         | 9.0     | ns   |

| t <sub>EABDATACO</sub> |         | 0.8     |         | 0.9      |         | 1.3     | ns   |

| t <sub>EABDATASU</sub> | 1.5     |         | 1.7     |          | 2.3     |         | ns   |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWESU</sub>   | 1.3     |         | 1.4     |          | 2.0     |         | ns   |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWDSU</sub>   | 1.5     |         | 1.7     |          | 2.3     |         | ns   |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWASU</sub>   | 3.0     |         | 3.6     |          | 4.8     |         | ns   |

| t <sub>EABWAH</sub>    | 0.5     |         | 0.5     |          | 0.8     |         | ns   |

| t <sub>EABWO</sub>     |         | 5.1     |         | 6.0      |         | 8.1     | ns   |

| Symbol                   | -1 Spee | d Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|--------------------------|---------|---------|----------------|-----|----------------|-----|------|

|                          | Min     | Max     | Min            | Max | Min            | Max |      |

| t <sub>DIN2IOE</sub>     |         | 3.5     |                | 4.3 |                | 5.6 | ns   |

| t <sub>DIN2LE</sub>      |         | 2.1     |                | 2.5 |                | 3.4 | ns   |

| t <sub>DIN2DATA</sub>    |         | 2.2     |                | 2.4 |                | 3.1 | ns   |

| t <sub>DCLK2IOE</sub>    |         | 2.9     |                | 3.5 |                | 4.7 | ns   |

| t <sub>DCLK2LE</sub>     |         | 2.1     |                | 2.5 |                | 3.4 | ns   |

| t <sub>SAMELAB</sub>     |         | 0.1     |                | 0.1 |                | 0.2 | ns   |

| t <sub>SAMEROW</sub>     |         | 1.1     |                | 1.1 |                | 1.5 | ns   |

| t <sub>SAME</sub> COLUMN |         | 0.8     |                | 1.0 |                | 1.3 | ns   |

| t <sub>DIFFROW</sub>     |         | 1.9     |                | 2.1 |                | 2.8 | ns   |

| t <sub>TWOROWS</sub>     |         | 3.0     |                | 3.2 |                | 4.3 | ns   |

| t <sub>LEPERIPH</sub>    |         | 3.1     |                | 3.3 |                | 3.7 | ns   |

| t <sub>LABCARRY</sub>    |         | 0.1     |                | 0.1 |                | 0.2 | ns   |

| t <sub>LABCASC</sub>     |         | 0.3     |                | 0.3 |                | 0.5 | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | d Grade | Unit |

|------------------------|----------------|-----|---------|----------------|-----|---------|------|

|                        | Min            | Max | Min     | Max            | Min | Max     |      |

| t <sub>DRR</sub>       |                | 9.0 |         | 12.0           |     | 16.0    | ns   |

| t <sub>INSU</sub> (3)  | 2.0            |     | 2.5     |                | 3.3 |         | ns   |

| t <sub>INH</sub> (3)   | 0.0            |     | 0.0     |                | 0.0 |         | ns   |

| t <sub>оитсо</sub> (3) | 2.0            | 5.2 | 2.0     | 6.9            | 2.0 | 9.1     | ns   |

| t <sub>INSU</sub> (4)  | 2.0            |     | 2.2     |                | -   |         | ns   |

| t <sub>INH</sub> (4)   | 0.0            |     | 0.0     |                | -   |         | ns   |

| t <sub>оитсо</sub> (4) | 0.5            | 3.0 | 0.5     | 4.6            | -   | -       | ns   |

| t <sub>PCISU</sub>     | 3.0            |     | 6.2     |                | -   |         | ns   |

| t <sub>PCIH</sub>      | 0.0            |     | 0.0     |                | -   |         | ns   |

| t <sub>PCICO</sub>     | 2.0            | 6.0 | 2.0     | 6.9            | -   | _       | ns   |

Table 51. EPF10K100E External Bidirectional Timing Parameters

Notes (1), (2)

| Symbol                     | -1 Spee | ed Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |  |

|----------------------------|---------|----------|---------|---------|---------|---------|------|--|

|                            | Min     | Max      | Min     | Max     | Min     | Max     |      |  |

| t <sub>INSUBIDIR</sub> (3) | 1.7     |          | 2.5     |         | 3.3     |         | ns   |  |

| t <sub>inhbidir</sub> (3)  | 0.0     |          | 0.0     |         | 0.0     |         | ns   |  |

| t <sub>INSUBIDIR</sub> (4) | 2.0     |          | 2.8     |         | -       |         | ns   |  |

| t <sub>INHBIDIR</sub> (4)  | 0.0     |          | 0.0     |         | -       |         | ns   |  |

| toutcobidir (3)            | 2.0     | 5.2      | 2.0     | 6.9     | 2.0     | 9.1     | ns   |  |

| t <sub>XZBIDIR</sub> (3)   |         | 5.6      |         | 7.5     |         | 10.1    | ns   |  |

| t <sub>ZXBIDIR</sub> (3)   |         | 5.6      |         | 7.5     |         | 10.1    | ns   |  |

| toutcobidir (4)            | 0.5     | 3.0      | 0.5     | 4.6     | -       | -       | ns   |  |

| t <sub>XZBIDIR</sub> (4)   |         | 4.6      |         | 6.5     |         | -       | ns   |  |

| t <sub>ZXBIDIR</sub> (4)   |         | 4.6      |         | 6.5     |         | -       | ns   |  |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) These parameters are specified by characterization.

(3) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

(4) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

| Symbol                  | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|-------------------------|----------------|-----|----------------|-----|----------------|------|------|

|                         | Min            | Max | Min            | Max | Min            | Max  |      |

| t <sub>DIN2IOE</sub>    |                | 2.8 |                | 3.5 |                | 4.4  | ns   |

| t <sub>DIN2LE</sub>     |                | 0.7 |                | 1.2 |                | 1.6  | ns   |

| t <sub>DIN2DATA</sub>   |                | 1.6 |                | 1.9 |                | 2.2  | ns   |

| t <sub>DCLK2IOE</sub>   |                | 1.6 |                | 2.1 |                | 2.7  | ns   |

| t <sub>DCLK2LE</sub>    |                | 0.7 |                | 1.2 |                | 1.6  | ns   |

| t <sub>SAMELAB</sub>    |                | 0.1 |                | 0.2 |                | 0.2  | ns   |

| t <sub>SAMEROW</sub>    |                | 1.9 |                | 3.4 |                | 5.1  | ns   |

| t <sub>SAMECOLUMN</sub> |                | 0.9 |                | 2.6 |                | 4.4  | ns   |

| t <sub>DIFFROW</sub>    |                | 2.8 |                | 6.0 |                | 9.5  | ns   |

| t <sub>TWOROWS</sub>    |                | 4.7 |                | 9.4 |                | 14.6 | ns   |

| t <sub>LEPERIPH</sub>   |                | 3.1 |                | 4.7 |                | 6.9  | ns   |

| t <sub>LABCARRY</sub>   |                | 0.6 |                | 0.8 |                | 1.0  | ns   |

| t <sub>LABCASC</sub>    |                | 0.9 |                | 1.2 |                | 1.6  | ns   |

| Table 57. EPF10       | K130E Extern | <b>130E External Timing Parameters</b> Notes (1), (2) |     |          |         |         |      |  |  |  |

|-----------------------|--------------|-------------------------------------------------------|-----|----------|---------|---------|------|--|--|--|

| Symbol                | -1 Spee      | -1 Speed Grade                                        |     | ed Grade | -3 Spee | d Grade | Unit |  |  |  |

|                       | Min          | Max                                                   | Min | Max      | Min     | Max     |      |  |  |  |

| t <sub>DRR</sub>      |              | 9.0                                                   |     | 12.0     |         | 16.0    | ns   |  |  |  |

| t <sub>INSU</sub> (3) | 1.9          |                                                       | 2.1 |          | 3.0     |         | ns   |  |  |  |

| t <sub>INH</sub> (3)  | 0.0          |                                                       | 0.0 |          | 0.0     |         | ns   |  |  |  |

| <b>t</b> оитсо (3)    | 2.0          | 5.0                                                   | 2.0 | 7.0      | 2.0     | 9.2     | ns   |  |  |  |

| t <sub>INSU</sub> (4) | 0.9          |                                                       | 1.1 |          | -       |         | ns   |  |  |  |

| t <sub>INH</sub> (4)  | 0.0          |                                                       | 0.0 |          | -       |         | ns   |  |  |  |

| tоитсо <i>(4)</i>     | 0.5          | 4.0                                                   | 0.5 | 6.0      | -       | -       | ns   |  |  |  |

| t <sub>PCISU</sub>    | 3.0          |                                                       | 6.2 |          | -       |         | ns   |  |  |  |

| t <sub>PCIH</sub>     | 0.0          |                                                       | 0.0 |          | -       |         | ns   |  |  |  |

| t <sub>PCICO</sub>    | 2.0          | 6.0                                                   | 2.0 | 6.9      | -       | -       | ns   |  |  |  |

| Symbol                 | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|----------|---------|---------|------|

|                        | Min     | Max     | Min     | Max      | Min     | Max     |      |

| t <sub>EABAA</sub>     |         | 3.7     |         | 5.2      |         | 7.0     | ns   |

| t <sub>EABRCCOMB</sub> | 3.7     |         | 5.2     |          | 7.0     |         | ns   |

| t <sub>EABRCREG</sub>  | 3.5     |         | 4.9     |          | 6.6     |         | ns   |

| t <sub>EABWP</sub>     | 2.0     |         | 2.8     |          | 3.8     |         | ns   |

| t <sub>EABWCCOMB</sub> | 4.5     |         | 6.3     |          | 8.6     |         | ns   |

| t <sub>EABWCREG</sub>  | 5.6     |         | 7.8     |          | 10.6    |         | ns   |

| t <sub>EABDD</sub>     |         | 3.8     |         | 5.3      |         | 7.2     | ns   |

| t <sub>EABDATACO</sub> |         | 0.8     |         | 1.1      |         | 1.5     | ns   |

| t <sub>EABDATASU</sub> | 1.1     |         | 1.6     |          | 2.1     |         | ns   |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWESU</sub>   | 0.7     |         | 1.0     |          | 1.3     |         | ns   |

| t <sub>EABWEH</sub>    | 0.4     |         | 0.6     |          | 0.8     |         | ns   |

| t <sub>EABWDSU</sub>   | 1.2     |         | 1.7     |          | 2.2     |         | ns   |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWASU</sub>   | 1.6     |         | 2.3     |          | 3.0     |         | ns   |

| t <sub>EABWAH</sub>    | 0.9     |         | 1.2     |          | 1.8     |         | ns   |

| t <sub>EABWO</sub>     |         | 3.1     |         | 4.3      |         | 5.9     | ns   |

| Table 70. EPF10         | K50S Device | Interconnec | t Timing Mi | croparamete | e <b>rs</b> Note | e (1)    |      |

|-------------------------|-------------|-------------|-------------|-------------|------------------|----------|------|

| Symbol                  | -1 Spee     | ed Grade    | -2 Spee     | d Grade     | -3 Spee          | ed Grade | Unit |

|                         | Min         | Max         | Min         | Max         | Min              | Max      |      |

| t <sub>DIN2IOE</sub>    |             | 3.1         |             | 3.7         |                  | 4.6      | ns   |

| t <sub>DIN2LE</sub>     |             | 1.7         |             | 2.1         |                  | 2.7      | ns   |

| t <sub>DIN2DATA</sub>   |             | 2.7         |             | 3.1         |                  | 5.1      | ns   |

| t <sub>DCLK2IOE</sub>   |             | 1.6         |             | 1.9         |                  | 2.6      | ns   |

| t <sub>DCLK2LE</sub>    |             | 1.7         |             | 2.1         |                  | 2.7      | ns   |

| t <sub>SAMELAB</sub>    |             | 0.1         |             | 0.1         |                  | 0.2      | ns   |

| t <sub>SAMEROW</sub>    |             | 1.5         |             | 1.7         |                  | 2.4      | ns   |

| t <sub>SAMECOLUMN</sub> |             | 1.0         |             | 1.3         |                  | 2.1      | ns   |

| t <sub>DIFFROW</sub>    |             | 2.5         |             | 3.0         |                  | 4.5      | ns   |

| t <sub>TWOROWS</sub>    |             | 4.0         |             | 4.7         |                  | 6.9      | ns   |

| t <sub>LEPERIPH</sub>   |             | 2.6         |             | 2.9         |                  | 3.4      | ns   |

| t <sub>LABCARRY</sub>   |             | 0.1         |             | 0.2         |                  | 0.2      | ns   |

| t <sub>LABCASC</sub>    |             | 0.8         |             | 1.0         |                  | 1.3      | ns   |

| Symbol                 | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|----------|---------|---------|------|

|                        | Min     | Max     | Min     | Max      | Min     | Max     |      |

| t <sub>EABAA</sub>     |         | 3.9     |         | 6.4      |         | 8.4     | ns   |

| t <sub>EABRCOMB</sub>  | 3.9     |         | 6.4     |          | 8.4     |         | ns   |

| t <sub>EABRCREG</sub>  | 3.6     |         | 5.7     |          | 7.6     |         | ns   |

| t <sub>EABWP</sub>     | 2.1     |         | 4.0     |          | 5.3     |         | ns   |

| t <sub>EABWCOMB</sub>  | 4.8     |         | 8.1     |          | 10.7    |         | ns   |

| t <sub>EABWCREG</sub>  | 5.4     |         | 8.0     |          | 10.6    |         | ns   |

| t <sub>EABDD</sub>     |         | 3.8     |         | 5.1      |         | 6.7     | ns   |

| t <sub>EABDATACO</sub> |         | 0.8     |         | 1.0      |         | 1.3     | ns   |

| t <sub>EABDATASU</sub> | 1.1     |         | 1.6     |          | 2.1     |         | ns   |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWESU</sub>   | 0.7     |         | 1.1     |          | 1.5     |         | ns   |

| t <sub>EABWEH</sub>    | 0.4     |         | 0.5     |          | 0.6     |         | ns   |

| t <sub>EABWDSU</sub>   | 1.2     |         | 1.8     |          | 2.4     |         | ns   |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |          | 0.0     |         | ns   |

| t <sub>EABWASU</sub>   | 1.9     |         | 3.6     |          | 4.7     |         | ns   |

| t <sub>EABWAH</sub>    | 0.8     |         | 0.5     |          | 0.7     |         | ns   |

| t <sub>EABWO</sub>     |         | 3.1     |         | 4.4      |         | 5.8     | ns   |

| Symbol                   | -1 Speed Grade |     | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|--------------------------|----------------|-----|----------------|------|----------------|------|------|

|                          | Min            | Мах | Min            | Мах  | Min            | Max  |      |

| t <sub>DIN2IOE</sub>     |                | 4.4 |                | 4.8  |                | 5.5  | ns   |

| t <sub>DIN2LE</sub>      |                | 0.6 |                | 0.6  |                | 0.9  | ns   |

| t <sub>DIN2DATA</sub>    |                | 1.8 |                | 2.1  |                | 2.8  | ns   |

| t <sub>DCLK2IOE</sub>    |                | 1.7 |                | 2.0  |                | 2.8  | ns   |

| t <sub>DCLK2LE</sub>     |                | 0.6 |                | 0.6  |                | 0.9  | ns   |

| t <sub>SAMELAB</sub>     |                | 0.1 |                | 0.1  |                | 0.2  | ns   |

| t <sub>SAMEROW</sub>     |                | 3.0 |                | 4.6  |                | 5.7  | ns   |

| t <sub>SAME</sub> COLUMN |                | 3.5 |                | 4.9  |                | 6.4  | ns   |

| t <sub>DIFFROW</sub>     |                | 6.5 |                | 9.5  |                | 12.1 | ns   |

| t <sub>TWOROWS</sub>     |                | 9.5 |                | 14.1 |                | 17.8 | ns   |

| t <sub>LEPERIPH</sub>    |                | 5.5 |                | 6.2  |                | 7.2  | ns   |

| t <sub>LABCARRY</sub>    |                | 0.3 |                | 0.1  |                | 0.2  | ns   |

During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.

SRAM configuration elements allow FLEX 10KE devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming user-mode operation. The entire reconfiguration process requires less than 85 ms and can be used to reconfigure an entire system dynamically. In-field upgrades can be performed by distributing new configuration files.

Before and during configuration, all I/O pins (except dedicated inputs, clock, or configuration pins) are pulled high by a weak pull-up resistor.

## **Programming Files**

Despite being function- and pin-compatible, FLEX 10KE devices are not programming- or configuration file-compatible with FLEX 10K or FLEX 10KA devices. A design therefore must be recompiled before it is transferred from a FLEX 10K or FLEX 10KA device to an equivalent FLEX 10KE device. This recompilation should be performed both to create a new programming or configuration file and to check design timing in FLEX 10KE devices, which has different timing characteristics than FLEX 10K or FLEX 10KA devices.

FLEX 10KE devices are generally pin-compatible with equivalent FLEX 10KA devices. In some cases, FLEX 10KE devices have fewer I/O pins than the equivalent FLEX 10KA devices. Table 81 shows which FLEX 10KE devices have fewer I/O pins than equivalent FLEX 10KA devices. However, power, ground, JTAG, and configuration pins are the same on FLEX 10KA and FLEX 10KE devices, enabling migration from a FLEX 10KA design to a FLEX 10KE design.