# E·XFL

# Intel - EPF10K30EFC484-1 Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

# Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 216                                                         |

| Number of Logic Elements/Cells | 1728                                                        |

| Total RAM Bits                 | 24576                                                       |

| Number of I/O                  | 220                                                         |

| Number of Gates                | 119000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                             |

| Package / Case                 | 484-BBGA                                                    |

| Supplier Device Package        | 484-FBGA (23x23)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k30efc484-1 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

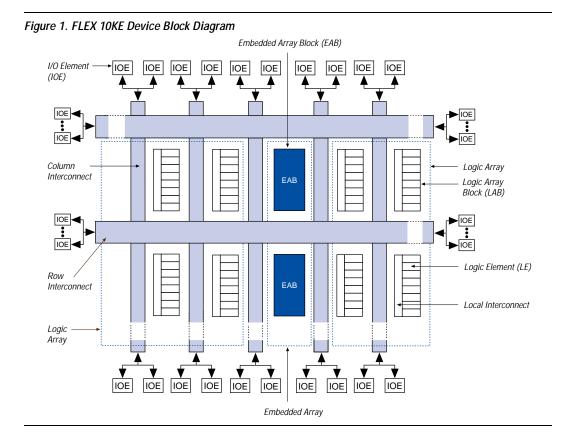

Figure 1 shows a block diagram of the FLEX 10KE architecture. Each group of LEs is combined into an LAB; groups of LABs are arranged into rows and columns. Each row also contains a single EAB. The LABs and EABs are interconnected by the FastTrack Interconnect routing structure. IOEs are located at the end of each row and column of the FastTrack Interconnect routing structure.

FLEX 10KE devices provide six dedicated inputs that drive the flipflops' control inputs and ensure the efficient distribution of high-speed, low-skew (less than 1.5 ns) control signals. These signals use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect routing structure. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device.

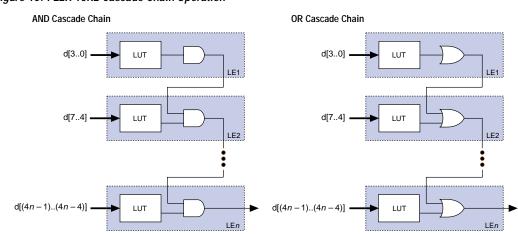

#### Cascade Chain

With the cascade chain, the FLEX 10KE architecture can implement functions that have a very wide fan-in. Adjacent LUTs can be used to compute portions of the function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. An a delay as low as 0.6 ns per LE, each additional LE provides four more inputs to the effective width of a function. Cascade chain logic can be created automatically by the Altera Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than eight bits are implemented automatically by linking several LABs together. For easier routing, a long cascade chain skips every other LAB in a row. A cascade chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB (e.g., the last LE of the first LAB in a row cascades to the first LE of the third LAB). The cascade chain does not cross the center of the row (e.g., in the EPF10K50E device, the cascade chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB). This break is due to the EAB's placement in the middle of the row.

Figure 10 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in. These examples show functions of 4n variables implemented with n LEs. The LE delay is 0.9 ns; the cascade chain delay is 0.6 ns. With the cascade chain, 2.7 ns are needed to decode a 16-bit address.

Figure 10. FLEX 10KE Cascade Chain Operation

Altera Corporation

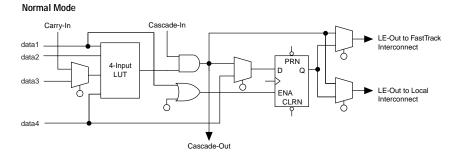

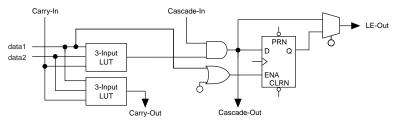

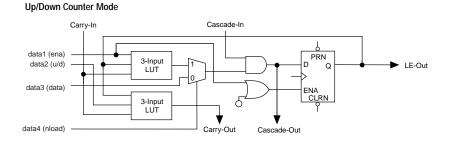

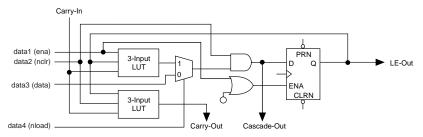

# Figure 11. FLEX 10KE LE Operating Modes

#### **Clearable Counter Mode**

For improved routing, the row interconnect consists of a combination of full-length and half-length channels. The full-length channels connect to all LABs in a row; the half-length channels connect to the LABs in half of the row. The EAB can be driven by the half-length channels in the left half of the row and by the full-length channels. The EAB drives out to the fulllength channels. In addition to providing a predictable, row-wide interconnect, this architecture provides increased routing resources. Two neighboring LABs can be connected using a half-row channel, thereby saving the other half of the channel for the other half of the row.

Table 7 summarizes the FastTrack Interconnect routing structure resources available in each FLEX 10KE device.

| Table 7. FLEX 1          | Table 7. FLEX 10KE FastTrack Interconnect Resources |                     |         |                        |  |  |  |  |

|--------------------------|-----------------------------------------------------|---------------------|---------|------------------------|--|--|--|--|

| Device                   | Rows                                                | Channels per<br>Row | Columns | Channels per<br>Column |  |  |  |  |

| EPF10K30E                | 6                                                   | 216                 | 36      | 24                     |  |  |  |  |

| EPF10K50E<br>EPF10K50S   | 10                                                  | 216                 | 36      | 24                     |  |  |  |  |

| EPF10K100E               | 12                                                  | 312                 | 52      | 24                     |  |  |  |  |

| EPF10K130E               | 16                                                  | 312                 | 52      | 32                     |  |  |  |  |

| EPF10K200E<br>EPF10K200S | 24                                                  | 312                 | 52      | 48                     |  |  |  |  |

In addition to general-purpose I/O pins, FLEX 10KE devices have six dedicated input pins that provide low-skew signal distribution across the device. These six inputs can be used for global clock, clear, preset, and peripheral output enable and clock enable control signals. These signals are available as control signals for all LABs and IOEs in the device. The dedicated inputs can also be used as general-purpose data inputs because they can feed the local interconnect of each LAB in the device.

Figure 14 shows the interconnection of adjacent LABs and EABs, with row, column, and local interconnects, as well as the associated cascade and carry chains. Each LAB is labeled according to its location: a letter represents the row and a number represents the column. For example, LAB B3 is in row B, column 3.

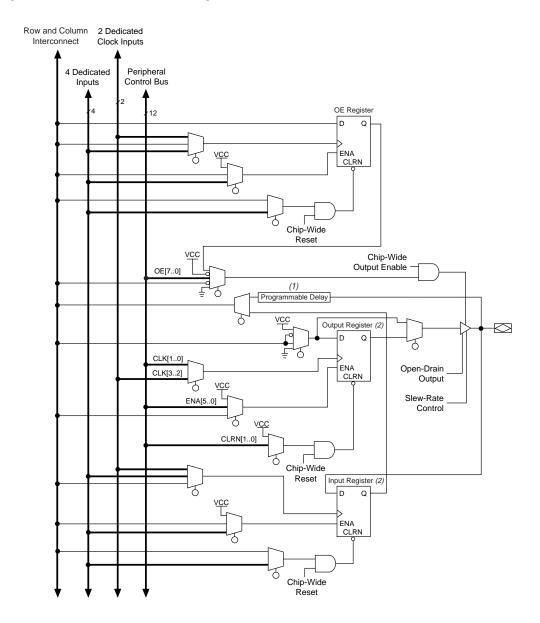

Figure 15. FLEX 10KE Bidirectional I/O Registers

#### Note:

(1) All FLEX 10KE devices (except the EPF10K50E and EPF10K200E devices) have a programmable input delay buffer on the input path.

#### **Altera Corporation**

When dedicated inputs drive non-inverted and inverted peripheral clears, clock enables, and output enables, two signals on the peripheral control bus will be used.

Tables 8 and 9 list the sources for each peripheral control signal, and show how the output enable, clock enable, clock, and clear signals share 12 peripheral control signals. The tables also show the rows that can drive global signals.

| Table 8. Peripheral Bus Sources for EPF10K30E, E | PF10K50E & EPF10K50S Devi | ices                   |

|--------------------------------------------------|---------------------------|------------------------|

| Peripheral<br>Control Signal                     | EPF10K30E                 | EPF10K50E<br>EPF10K50S |

| OEO                                              | Row A                     | Row A                  |

| OE1                                              | Row B                     | Row B                  |

| OE2                                              | Row C                     | Row D                  |

| OE3                                              | Row D                     | Row F                  |

| OE4                                              | Row E                     | Row H                  |

| OE5                                              | Row F                     | Row J                  |

| CLKENA0/CLK0/GLOBAL0                             | Row A                     | Row A                  |

| CLKENA1/OE6/GLOBAL1                              | Row B                     | Row C                  |

| CLKENA2/CLR0                                     | Row C                     | Row E                  |

| CLKENA3/OE7/GLOBAL2                              | Row D                     | Row G                  |

| CLKENA4/CLR1                                     | Row E                     | Row I                  |

| CLKENA5/CLK1/GLOBAL3                             | Row F                     | Row J                  |

Г

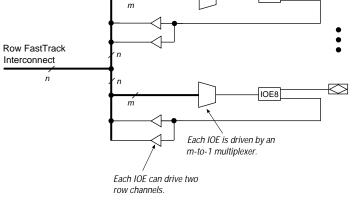

Row-to-IOE Connections

When an IOE is used as an input signal, it can drive two separate row channels. The signal is accessible by all LEs within that row. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the row channels. Up to eight IOEs connect to each side of each row channel (see Figure 16).

# Figure 16. FLEX 10KE Row-to-IOE Connections The values for m and n are provided in Table 10.

m loe1

| Table 10 lists the FLEX 10KE row-to-IOE interco | onnect resources. |

|-------------------------------------------------|-------------------|

|-------------------------------------------------|-------------------|

| Table 10. FLEX 10K | Table 10. FLEX 10KE Row-to-IOE Interconnect Resources |                          |  |  |  |  |  |

|--------------------|-------------------------------------------------------|--------------------------|--|--|--|--|--|

| Device             | Channels per Row (n)                                  | Row Channels per Pin (m) |  |  |  |  |  |

| EPF10K30E          | 216                                                   | 27                       |  |  |  |  |  |

| EPF10K50E          | 216                                                   | 27                       |  |  |  |  |  |

| EPF10K50S          |                                                       |                          |  |  |  |  |  |

| EPF10K100E         | 312                                                   | 39                       |  |  |  |  |  |

| EPF10K130E         | 312                                                   | 39                       |  |  |  |  |  |

| EPF10K200E         | 312                                                   | 39                       |  |  |  |  |  |

| EPF10K200S         |                                                       |                          |  |  |  |  |  |

$\bigcirc$

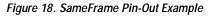

# SameFrame Pin-Outs FLEX 10KE devices support the SameFrame pin-out feature for FineLine BGA packages. The SameFrame pin-out feature is the arrangement of balls on FineLine BGA packages such that the lower-ballcount packages form a subset of the higher-ball-count packages. SameFrame pin-outs provide the flexibility to migrate not only from device to device within the same package, but also from one package to another. A given printed circuit board (PCB) layout can support multiple device density/package combinations. For example, a single board layout can support a range of devices from an EPF10K30E device in a 256-pin FineLine BGA package.

The Altera software provides support to design PCBs with SameFrame pin-out devices. Devices can be defined for present and future use. The Altera software generates pin-outs describing how to lay out a board to take advantage of this migration (see Figure 18).

Printed Circuit Board Designed for 672-Pin FineLine BGA Package

256-Pin FineLine BGA Package (Reduced I/O Count or Logic Requirements)

672-Pin FineLine BGA Package (Increased I/O Count or Logic Requirements)

# ClockLock & ClockBoost Features

To support high-speed designs, FLEX 10KE devices offer optional ClockLock and ClockBoost circuitry containing a phase-locked loop (PLL) used to increase design speed and reduce resource usage. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by resource sharing within the device. The ClockBoost feature allows the designer to distribute a low-speed clock and multiply that clock on-device. Combined, the ClockLock and ClockBoost features provide significant improvements in system performance and bandwidth.

All FLEX 10KE devices, except EPF10K50E and EPF10K200E devices, support ClockLock and ClockBoost circuitry. EPF10K50S and EPF10K200S devices support this circuitry. Devices that support Clock-Lock and ClockBoost circuitry are distinguished with an "X" suffix in the ordering code; for instance, the EPF10K200SFC672-1X device supports this circuit.

The ClockLock and ClockBoost features in FLEX 10KE devices are enabled through the Altera software. External devices are not required to use these features. The output of the ClockLock and ClockBoost circuits is not available at any of the device pins.

The ClockLock and ClockBoost circuitry locks onto the rising edge of the incoming clock. The circuit output can drive the clock inputs of registers only; the generated clock cannot be gated or inverted.

The dedicated clock pin (GCLK1) supplies the clock to the ClockLock and ClockBoost circuitry. When the dedicated clock pin is driving the ClockLock or ClockBoost circuitry, it cannot drive elsewhere in the device.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to the GCLK1 pin. In the Altera software, the GCLK1 pin can feed both the ClockLock and ClockBoost circuitry in the FLEX 10KE device. However, when both circuits are used, the other clock pin cannot be used.

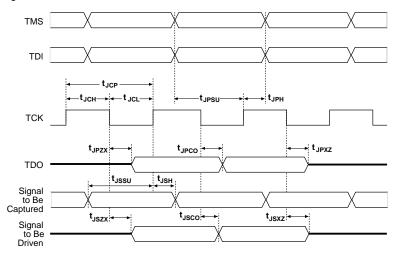

Figure 20 shows the timing requirements for the JTAG signals.

Figure 20. FLEX 10KE JTAG Waveforms

# Table 18 shows the timing parameters and values for FLEX 10KE devices.

| Sumbol            | Parameter                                      | Min    | Max   | Unit |

|-------------------|------------------------------------------------|--------|-------|------|

| Symbol            | Parameter                                      | IVIIII | IVIAX | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100    |       | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50     |       | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50     |       | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20     |       | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45     |       | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |        | 25    | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |        | 25    | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |        | 25    | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20     |       | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45     |       | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |        | 35    | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output |        | 35    | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |        | 35    | ns   |

| Table 2            | Table 23. FLEX 10KE Device Capacitance     Note (14) |                                     |     |     |      |  |  |

|--------------------|------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|

| Symbol             | Parameter                                            | Conditions                          | Min | Max | Unit |  |  |

| C <sub>IN</sub>    | Input capacitance                                    | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |  |

| C <sub>INCLK</sub> | Input capacitance on<br>dedicated clock pin          | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |

| C <sub>OUT</sub>   | Output capacitance                                   | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |  |  |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before  $V_{CCINT}$  and  $V_{CCIO}$  are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  V or 3.3 V.

- (7) These values are specified under the FLEX 10KE Recommended Operating Conditions shown in Tables 20 and 21.

(8) The FLEX 10KE input buffers are compatible with 2.5-V, 3.3-V (LVTTL and LVCMOS), and 5.0-V TTL and CMOS

- signals. Additionally, the input buffers are 3.3-V PCI compliant when  $V_{CCIO}$  and  $V_{CCINT}$  meet the relationship shown in Figure 22.

- (9) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (10) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (11) This value is specified for normal device operation. The value may vary during power-up.

- (12) This parameter applies to -1 speed-grade commercial-temperature devices and -2 speed-grade-industrial temperature devices.

- (13) Pin pull-up resistance values will be lower if the pin is driven higher than  $V_{CCIO}$  by an external source.

- (14) Capacitance is sample-tested only.

| Symbol                  | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|-------------------------|----------------|-----|---------|----------------|-----|----------|------|

|                         | Min            | Max | Min     | Max            | Min | Max      |      |

| t <sub>DIN2IOE</sub>    |                | 1.8 |         | 2.4            |     | 2.9      | ns   |

| t <sub>DIN2LE</sub>     |                | 1.5 |         | 1.8            |     | 2.4      | ns   |

| t <sub>DIN2DATA</sub>   |                | 1.5 |         | 1.8            |     | 2.2      | ns   |

| t <sub>DCLK2IOE</sub>   |                | 2.2 |         | 2.6            |     | 3.0      | ns   |

| t <sub>DCLK2LE</sub>    |                | 1.5 |         | 1.8            |     | 2.4      | ns   |

| t <sub>SAMELAB</sub>    |                | 0.1 |         | 0.2            |     | 0.3      | ns   |

| t <sub>SAMEROW</sub>    |                | 2.0 |         | 2.4            |     | 2.7      | ns   |

| t <sub>SAMECOLUMN</sub> |                | 0.7 |         | 1.0            |     | 0.8      | ns   |

| t <sub>DIFFROW</sub>    |                | 2.7 |         | 3.4            |     | 3.5      | ns   |

| t <sub>TWOROWS</sub>    |                | 4.7 |         | 5.8            |     | 6.2      | ns   |

| t <sub>LEPERIPH</sub>   |                | 2.7 |         | 3.4            |     | 3.8      | ns   |

| t <sub>LABCARRY</sub>   |                | 0.3 |         | 0.4            |     | 0.5      | ns   |

| t <sub>LABCASC</sub>    |                | 0.8 |         | 0.8            |     | 1.1      | ns   |

| Symbol                            | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|-----------------------------------|----------------|-----|----------------|-----|----------------|------|------|

|                                   | Min            | Max | Min            | Max | Min            | Max  |      |

| t <sub>DRR</sub>                  |                | 8.0 |                | 9.5 |                | 12.5 | ns   |

| t <sub>INSU</sub> (3)             | 2.1            |     | 2.5            |     | 3.9            |      | ns   |

| t <sub>INH</sub> (3)              | 0.0            |     | 0.0            |     | 0.0            |      | ns   |

| <sup>t</sup> оитсо <sup>(3)</sup> | 2.0            | 4.9 | 2.0            | 5.9 | 2.0            | 7.6  | ns   |

| t <sub>INSU</sub> (4)             | 1.1            |     | 1.5            |     | -              |      | ns   |

| t <sub>INH</sub> (4)              | 0.0            |     | 0.0            |     | -              |      | ns   |

| t <sub>оитсо</sub> (4)            | 0.5            | 3.9 | 0.5            | 4.9 | -              | -    | ns   |

| t <sub>PCISU</sub>                | 3.0            |     | 4.2            |     | -              |      | ns   |

| t <sub>PCIH</sub>                 | 0.0            |     | 0.0            |     | -              |      | ns   |

| t <sub>PCICO</sub>                | 2.0            | 6.0 | 2.0            | 7.5 | _              | -    | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|------|------|

|                        | Min            | Мах | Min            | Max | Min            | Max  |      |

| t <sub>EABAA</sub>     |                | 6.4 |                | 7.6 |                | 10.2 | ns   |

| t <sub>EABRCOMB</sub>  | 6.4            |     | 7.6            |     | 10.2           |      | ns   |

| t <sub>EABRCREG</sub>  | 4.4            |     | 5.1            |     | 7.0            |      | ns   |

| t <sub>EABWP</sub>     | 2.5            |     | 2.9            |     | 3.9            |      | ns   |

| t <sub>EABWCOMB</sub>  | 6.0            |     | 7.0            |     | 9.5            |      | ns   |

| t <sub>EABWCREG</sub>  | 6.8            |     | 7.8            |     | 10.6           |      | ns   |

| t <sub>EABDD</sub>     |                | 5.7 |                | 6.7 |                | 9.0  | ns   |

| t <sub>EABDATACO</sub> |                | 0.8 |                | 0.9 |                | 1.3  | ns   |

| t <sub>EABDATASU</sub> | 1.5            |     | 1.7            |     | 2.3            |      | ns   |

| t <sub>EABDATAH</sub>  | 0.0            |     | 0.0            |     | 0.0            |      | ns   |

| t <sub>EABWESU</sub>   | 1.3            |     | 1.4            |     | 2.0            |      | ns   |

| t <sub>EABWEH</sub>    | 0.0            |     | 0.0            |     | 0.0            |      | ns   |

| t <sub>EABWDSU</sub>   | 1.5            |     | 1.7            |     | 2.3            |      | ns   |

| t <sub>EABWDH</sub>    | 0.0            |     | 0.0            |     | 0.0            |      | ns   |

| t <sub>EABWASU</sub>   | 3.0            |     | 3.6            |     | 4.8            |      | ns   |

| t <sub>EABWAH</sub>    | 0.5            |     | 0.5            |     | 0.8            |      | ns   |

| t <sub>EABWO</sub>     |                | 5.1 |                | 6.0 |                | 8.1  | ns   |

| Symbol                   | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | d Grade | Unit |

|--------------------------|----------------|-----|---------|----------------|-----|---------|------|

|                          | Min            | Max | Min     | Max            | Min | Max     |      |

| t <sub>DIN2IOE</sub>     |                | 3.5 |         | 4.3            |     | 5.6     | ns   |

| t <sub>DIN2LE</sub>      |                | 2.1 |         | 2.5            |     | 3.4     | ns   |

| t <sub>DIN2DATA</sub>    |                | 2.2 |         | 2.4            |     | 3.1     | ns   |

| t <sub>DCLK2IOE</sub>    |                | 2.9 |         | 3.5            |     | 4.7     | ns   |

| t <sub>DCLK2LE</sub>     |                | 2.1 |         | 2.5            |     | 3.4     | ns   |

| t <sub>SAMELAB</sub>     |                | 0.1 |         | 0.1            |     | 0.2     | ns   |

| t <sub>SAMEROW</sub>     |                | 1.1 |         | 1.1            |     | 1.5     | ns   |

| t <sub>SAME</sub> COLUMN |                | 0.8 |         | 1.0            |     | 1.3     | ns   |

| t <sub>DIFFROW</sub>     |                | 1.9 |         | 2.1            |     | 2.8     | ns   |

| t <sub>TWOROWS</sub>     |                | 3.0 |         | 3.2            |     | 4.3     | ns   |

| t <sub>LEPERIPH</sub>    |                | 3.1 |         | 3.3            |     | 3.7     | ns   |

| t <sub>LABCARRY</sub>    |                | 0.1 |         | 0.1            |     | 0.2     | ns   |

| t <sub>LABCASC</sub>     |                | 0.3 |         | 0.3            |     | 0.5     | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|------------------------|----------------|-----|----------------|------|----------------|------|------|

|                        | Min            | Max | Min            | Max  | Min            | Max  |      |

| t <sub>DRR</sub>       |                | 9.0 |                | 12.0 |                | 16.0 | ns   |

| t <sub>INSU</sub> (3)  | 2.0            |     | 2.5            |      | 3.3            |      | ns   |

| t <sub>INH</sub> (3)   | 0.0            |     | 0.0            |      | 0.0            |      | ns   |

| t <sub>оитсо</sub> (3) | 2.0            | 5.2 | 2.0            | 6.9  | 2.0            | 9.1  | ns   |

| t <sub>INSU</sub> (4)  | 2.0            |     | 2.2            |      | -              |      | ns   |

| t <sub>INH</sub> (4)   | 0.0            |     | 0.0            |      | -              |      | ns   |

| t <sub>оитсо</sub> (4) | 0.5            | 3.0 | 0.5            | 4.6  | -              | -    | ns   |

| t <sub>PCISU</sub>     | 3.0            |     | 6.2            |      | -              |      | ns   |

| t <sub>PCIH</sub>      | 0.0            |     | 0.0            |      | -              |      | ns   |

| t <sub>PCICO</sub>     | 2.0            | 6.0 | 2.0            | 6.9  | -              | _    | ns   |

Table 51. EPF10K100E External Bidirectional Timing Parameters

Notes (1), (2)

| Symbol                     | -1 Spee | ed Grade | -2 Spee | -2 Speed Grade |     | d Grade | Unit |

|----------------------------|---------|----------|---------|----------------|-----|---------|------|

|                            | Min     | Max      | Min     | Max            | Min | Max     |      |

| t <sub>INSUBIDIR</sub> (3) | 1.7     |          | 2.5     |                | 3.3 |         | ns   |

| t <sub>inhbidir</sub> (3)  | 0.0     |          | 0.0     |                | 0.0 |         | ns   |

| t <sub>INSUBIDIR</sub> (4) | 2.0     |          | 2.8     |                | -   |         | ns   |

| t <sub>INHBIDIR</sub> (4)  | 0.0     |          | 0.0     |                | -   |         | ns   |

| toutcobidir (3)            | 2.0     | 5.2      | 2.0     | 6.9            | 2.0 | 9.1     | ns   |

| t <sub>XZBIDIR</sub> (3)   |         | 5.6      |         | 7.5            |     | 10.1    | ns   |

| t <sub>ZXBIDIR</sub> (3)   |         | 5.6      |         | 7.5            |     | 10.1    | ns   |

| toutcobidir (4)            | 0.5     | 3.0      | 0.5     | 4.6            | -   | -       | ns   |

| t <sub>XZBIDIR</sub> (4)   |         | 4.6      |         | 6.5            |     | -       | ns   |

| t <sub>ZXBIDIR</sub> (4)   |         | 4.6      |         | 6.5            |     | -       | ns   |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) These parameters are specified by characterization.

(3) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

(4) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

| Symbol           | -1 Spee | d Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------|---------|---------|----------------|-----|----------------|-----|------|

|                  | Min     | Max     | Min            | Max | Min            | Мах |      |

| t <sub>H</sub>   | 0.9     |         | 1.1            |     | 1.5            |     | ns   |

| t <sub>PRE</sub> |         | 0.5     |                | 0.6 |                | 0.8 | ns   |

| t <sub>CLR</sub> |         | 0.5     |                | 0.6 |                | 0.8 | ns   |

| t <sub>CH</sub>  | 2.0     |         | 2.5            |     | 3.0            |     | ns   |

| t <sub>CL</sub>  | 2.0     |         | 2.5            |     | 3.0            |     | ns   |

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|---------------------|----------------|-----|----------------|-----|----------------|------|------|

|                     | Min            | Max | Min            | Max | Min            | Max  |      |

| t <sub>IOD</sub>    |                | 1.6 |                | 1.9 |                | 2.6  | ns   |

| t <sub>IOC</sub>    |                | 0.3 |                | 0.3 |                | 0.5  | ns   |

| t <sub>IOCO</sub>   |                | 1.6 |                | 1.9 |                | 2.6  | ns   |

| t <sub>IOCOMB</sub> |                | 0.5 |                | 0.6 |                | 0.8  | ns   |

| t <sub>IOSU</sub>   | 0.8            |     | 0.9            |     | 1.2            |      | ns   |

| t <sub>IOH</sub>    | 0.7            |     | 0.8            |     | 1.1            |      | ns   |

| t <sub>IOCLR</sub>  |                | 0.2 |                | 0.2 |                | 0.3  | ns   |

| t <sub>OD1</sub>    |                | 0.6 |                | 0.7 |                | 0.9  | ns   |

| t <sub>OD2</sub>    |                | 0.1 |                | 0.2 |                | 0.7  | ns   |

| t <sub>OD3</sub>    |                | 2.5 |                | 3.0 |                | 3.9  | ns   |

| t <sub>XZ</sub>     |                | 4.4 |                | 5.3 |                | 7.1  | ns   |

| t <sub>ZX1</sub>    |                | 4.4 |                | 5.3 |                | 7.1  | ns   |

| t <sub>ZX2</sub>    |                | 3.9 |                | 4.8 |                | 6.9  | ns   |

| t <sub>ZX3</sub>    |                | 6.3 |                | 7.6 |                | 10.1 | ns   |

| t <sub>INREG</sub>  |                | 4.8 |                | 5.7 |                | 7.7  | ns   |

| t <sub>IOFD</sub>   |                | 1.5 |                | 1.8 |                | 2.4  | ns   |

| t <sub>INCOMB</sub> |                | 1.5 |                | 1.8 |                | 2.4  | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABDATA1</sub>  |                | 1.7 |                | 2.4 |                | 3.2 | ns   |

| t <sub>EABDATA2</sub>  |                | 0.4 |                | 0.6 |                | 0.8 | ns   |

| t <sub>EABWE1</sub>    |                | 1.0 |                | 1.4 |                | 1.9 | ns   |

| t <sub>EABWE2</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABRE1</sub>    |                | 0.0 |                | 0.0 |                | 0.0 |      |

| t <sub>EABRE2</sub>    |                | 0.4 |                | 0.6 |                | 0.8 |      |

| t <sub>EABCLK</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABCO</sub>     |                | 0.8 |                | 1.1 |                | 1.5 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABSU</sub>     | 0.7            |     | 1.0            |     | 1.3            |     | ns   |

| t <sub>EABH</sub>      | 0.4            |     | 0.6            |     | 0.8            |     | ns   |

| t <sub>EABCLR</sub>    | 0.8            |     | 1.1            |     | 1.5            |     |      |

| t <sub>AA</sub>        |                | 2.0 |                | 2.8 |                | 3.8 | ns   |

| t <sub>WP</sub>        | 2.0            |     | 2.8            |     | 3.8            |     | ns   |

| t <sub>RP</sub>        | 1.0            |     | 1.4            |     | 1.9            |     |      |

| t <sub>WDSU</sub>      | 0.5            |     | 0.7            |     | 0.9            |     | ns   |

| t <sub>WDH</sub>       | 0.1            |     | 0.1            |     | 0.2            |     | ns   |

| twasu                  | 1.0            |     | 1.4            |     | 1.9            |     | ns   |

| t <sub>WAH</sub>       | 1.5            |     | 2.1            |     | 2.9            |     | ns   |

| t <sub>RASU</sub>      | 1.5            |     | 2.1            |     | 2.8            |     |      |

| t <sub>RAH</sub>       | 0.1            |     | 0.1            |     | 0.2            |     |      |

| t <sub>WO</sub>        |                | 2.1 |                | 2.9 |                | 4.0 | ns   |

| t <sub>DD</sub>        |                | 2.1 |                | 2.9 |                | 4.0 | ns   |

| t <sub>EABOUT</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABCH</sub>     | 1.5            |     | 2.0            |     | 2.5            |     | ns   |

| t <sub>EABCL</sub>     | 1.5            |     | 2.0            |     | 2.5            |     | ns   |

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|---------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                     | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>LUT</sub>    |                | 0.7 |                | 0.8 |                | 1.2 | ns   |

| t <sub>CLUT</sub>   |                | 0.4 |                | 0.5 |                | 0.6 | ns   |

| t <sub>RLUT</sub>   |                | 0.5 |                | 0.7 |                | 0.9 | ns   |

| t <sub>PACKED</sub> |                | 0.4 |                | 0.5 |                | 0.7 | ns   |

| t <sub>EN</sub>     |                | 0.6 |                | 0.5 |                | 0.6 | ns   |

| tcico               |                | 0.1 |                | 0.2 |                | 0.3 | ns   |

| t <sub>CGEN</sub>   |                | 0.3 |                | 0.4 |                | 0.6 | ns   |

| t <sub>CGENR</sub>  |                | 0.1 |                | 0.2 |                | 0.3 | ns   |

| t <sub>CASC</sub>   |                | 0.7 |                | 0.8 |                | 1.2 | ns   |

| t <sub>C</sub>      |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| <sup>t</sup> co     |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| tсомв               |                | 0.3 |                | 0.6 |                | 0.8 | ns   |

| t <sub>SU</sub>     | 0.4            |     | 0.6            |     | 0.7            |     | ns   |

| tн                  | 1.0            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>PRE</sub>    |                | 0.4 |                | 0.6 |                | 0.8 | ns   |

| t <sub>CLR</sub>    |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| <sup>t</sup> CH     | 2.0            |     | 2.5            |     | 3.0            |     | ns   |

| ĊL                  | 2.0            |     | 2.5            |     | 3.0            |     | ns   |

Table 74. EPF10K200S Device IOE Timing Microparameters (Part 1 of 2)

Note (1)

| Symbol              | -1 Spee | ed Grade | -2 Spee | ed Grade | -3 Spee | ed Grade | Unit |

|---------------------|---------|----------|---------|----------|---------|----------|------|

|                     | Min     | Max      | Min     | Max      | Min     | Max      |      |

| t <sub>IOD</sub>    |         | 1.8      |         | 1.9      |         | 2.6      | ns   |

| t <sub>IOC</sub>    |         | 0.3      |         | 0.3      |         | 0.5      | ns   |

| t <sub>IOCO</sub>   |         | 1.7      |         | 1.9      |         | 2.6      | ns   |

| t <sub>IOCOMB</sub> |         | 0.5      |         | 0.6      |         | 0.8      | ns   |

| t <sub>IOSU</sub>   | 0.8     |          | 0.9     |          | 1.2     |          | ns   |

| t <sub>IOH</sub>    | 0.4     |          | 0.8     |          | 1.1     |          | ns   |

| t <sub>IOCLR</sub>  |         | 0.2      |         | 0.2      |         | 0.3      | ns   |

| t <sub>OD1</sub>    |         | 1.3      |         | 0.7      |         | 0.9      | ns   |

| t <sub>OD2</sub>    |         | 0.8      |         | 0.2      |         | 0.4      | ns   |

| t <sub>OD3</sub>    |         | 2.9      |         | 3.0      |         | 3.9      | ns   |

| t <sub>XZ</sub>     |         | 5.0      |         | 5.3      |         | 7.1      | ns   |

| t <sub>ZX1</sub>    |         | 5.0      |         | 5.3      |         | 7.1      | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABAA</sub>     |                | 3.9 |                | 6.4 |                | 8.4 | ns   |

| t <sub>EABRCOMB</sub>  | 3.9            |     | 6.4            |     | 8.4            |     | ns   |

| t <sub>EABRCREG</sub>  | 3.6            |     | 5.7            |     | 7.6            |     | ns   |

| t <sub>EABWP</sub>     | 2.1            |     | 4.0            |     | 5.3            |     | ns   |

| t <sub>EABWCOMB</sub>  | 4.8            |     | 8.1            |     | 10.7           |     | ns   |

| t <sub>EABWCREG</sub>  | 5.4            |     | 8.0            |     | 10.6           |     | ns   |

| t <sub>EABDD</sub>     |                | 3.8 |                | 5.1 |                | 6.7 | ns   |

| t <sub>EABDATACO</sub> |                | 0.8 |                | 1.0 |                | 1.3 | ns   |

| t <sub>EABDATASU</sub> | 1.1            |     | 1.6            |     | 2.1            |     | ns   |

| t <sub>EABDATAH</sub>  | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>EABWESU</sub>   | 0.7            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>EABWEH</sub>    | 0.4            |     | 0.5            |     | 0.6            |     | ns   |

| t <sub>EABWDSU</sub>   | 1.2            |     | 1.8            |     | 2.4            |     | ns   |

| t <sub>EABWDH</sub>    | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>EABWASU</sub>   | 1.9            |     | 3.6            |     | 4.7            |     | ns   |

| t <sub>EABWAH</sub>    | 0.8            |     | 0.5            |     | 0.7            |     | ns   |

| t <sub>EABWO</sub>     |                | 3.1 |                | 4.4 |                | 5.8 | ns   |

| Symbol                   | -1 Speed Grade |     | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|--------------------------|----------------|-----|----------------|------|----------------|------|------|

|                          | Min            | Мах | Min            | Мах  | Min            | Max  |      |

| t <sub>DIN2IOE</sub>     |                | 4.4 |                | 4.8  |                | 5.5  | ns   |

| t <sub>DIN2LE</sub>      |                | 0.6 |                | 0.6  |                | 0.9  | ns   |

| t <sub>DIN2DATA</sub>    |                | 1.8 |                | 2.1  |                | 2.8  | ns   |

| t <sub>DCLK2IOE</sub>    |                | 1.7 |                | 2.0  |                | 2.8  | ns   |

| t <sub>DCLK2LE</sub>     |                | 0.6 |                | 0.6  |                | 0.9  | ns   |

| t <sub>SAMELAB</sub>     |                | 0.1 |                | 0.1  |                | 0.2  | ns   |

| t <sub>SAMEROW</sub>     |                | 3.0 |                | 4.6  |                | 5.7  | ns   |

| t <sub>SAME</sub> COLUMN |                | 3.5 |                | 4.9  |                | 6.4  | ns   |

| t <sub>DIFFROW</sub>     |                | 6.5 |                | 9.5  |                | 12.1 | ns   |

| t <sub>TWOROWS</sub>     |                | 9.5 |                | 14.1 |                | 17.8 | ns   |

| t <sub>LEPERIPH</sub>    |                | 5.5 |                | 6.2  |                | 7.2  | ns   |

| t <sub>LABCARRY</sub>    |                | 0.3 |                | 0.1  |                | 0.2  | ns   |

| Power<br>Consumption | The supply power (P) for FLEX 10KE de following equation:                                                                                                                                                                                                                 | vices can be calculated with the                                                                   |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| oonoumption          | $P = P_{INT} + P_{IO} = (I_{CCSTANDBY} + I_{CCACTI})$                                                                                                                                                                                                                     | $_{\rm VE}$ ) $	imes$ V <sub>CC</sub> + P <sub>IO</sub>                                            |  |  |  |  |  |

|                      | The $I_{CCACTIVE}$ value depends on the sw<br>application logic. This value is calculated<br>that each LE typically consumes. The $P_{II}$<br>device output load characteristics and so<br>calculated using the guidelines given in<br><i>Power for Altera Devices</i> ). | d based on the amount of current $_{\rm D}$ value, which depends on the witching frequency, can be |  |  |  |  |  |

|                      | Compared to the rest of the device, the onegligible amount of power. Therefore, ignored when calculating supply current                                                                                                                                                   | the embedded array can be                                                                          |  |  |  |  |  |

|                      | The $I_{\mbox{\scriptsize CCACTIVE}}$ value can be calculated with the following equation:                                                                                                                                                                                |                                                                                                    |  |  |  |  |  |

|                      | $I_{CCACTIVE} = K \times f_{MAX} \times N \times tog_{LC} \times \frac{1}{MH}$                                                                                                                                                                                            | $\mu A$<br>Iz × LE                                                                                 |  |  |  |  |  |

|                      | Where:                                                                                                                                                                                                                                                                    |                                                                                                    |  |  |  |  |  |

|                      | <ul> <li>f<sub>MAX</sub> = Maximum operating frequence</li> <li>N = Total number of LEs used in tog<sub>LC</sub> = Average percent of LEs tog (typically 12.5%)</li> <li>K = Constant</li> </ul>                                                                          | n the device<br>gling at each clock                                                                |  |  |  |  |  |

|                      | Table 80 provides the constant (K) value                                                                                                                                                                                                                                  | S for FLEX TUKE devices.                                                                           |  |  |  |  |  |

|                      | Table 80. FLEX 10KE K Constant Values                                                                                                                                                                                                                                     |                                                                                                    |  |  |  |  |  |

|                      | Device                                                                                                                                                                                                                                                                    | K Value                                                                                            |  |  |  |  |  |

|                      | EPF10K30E                                                                                                                                                                                                                                                                 | 4.5                                                                                                |  |  |  |  |  |

|                      | EPF10K50E                                                                                                                                                                                                                                                                 | 4.8                                                                                                |  |  |  |  |  |

|                      | EPF10K50S                                                                                                                                                                                                                                                                 | 4.5                                                                                                |  |  |  |  |  |

|                      | EPF10K100E                                                                                                                                                                                                                                                                | 4.5                                                                                                |  |  |  |  |  |

|                      | EPF10K130E                                                                                                                                                                                                                                                                | 4.6                                                                                                |  |  |  |  |  |

|                      | EPF10K200E 4.8                                                                                                                                                                                                                                                            |                                                                                                    |  |  |  |  |  |

EPF10K200S

This calculation provides an  $I_{CC}$  estimate based on typical conditions with no output load. The actual  $I_{CC}$  should be verified during operation because this measurement is sensitive to the actual pattern in the device and the environmental operating conditions.

4.6

| Device<br>Pin-Outs  | See the Altera web site (http://www.altera.com) or the Altera Digital Library for pin-out information.                                                      |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision<br>History | The information contained in the <i>FLEX 10KE Embedded Programmable Logic Data Sheet</i> version 2.5 supersedes information published in previous versions. |

|                     | Version 2.5                                                                                                                                                 |

|                     | The following changes were made to the <i>FLEX 10KE Embedded Programmable Logic Data Sheet</i> version 2.5:                                                 |

|                     | <ul> <li><i>Note (1)</i> added to Figure 23.</li> <li>Text added to "I/O Element" section on page 34.</li> <li>Updated Table 22.</li> </ul>                 |

|                     | Version 2.4                                                                                                                                                 |

|                     | The following changes were made to the FLEX 10KE Embedded                                                                                                   |

Programmable Logic Data Sheet version 2.4: updated text on page 34 and page 63.