Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 216                                                         |

| Number of Logic Elements/Cells | 1728                                                        |

| Total RAM Bits                 | 24576                                                       |

| Number of I/O                  | 147                                                         |

| Number of Gates                | 119000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                             |

| Package / Case                 | 208-BFQFP                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k30eqc208-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Application                                 | Resources Used |      | Performance    |                |                |     |  |

|---------------------------------------------|----------------|------|----------------|----------------|----------------|-----|--|

|                                             | LEs            | EABs | -1 Speed Grade | -2 Speed Grade | -3 Speed Grade |     |  |

| 16-bit loadable counter                     | 16             | 0    | 285            | 250            | 200            | MHz |  |

| 16-bit accumulator                          | 16             | 0    | 285            | 250            | 200            | MHz |  |

| 16-to-1 multiplexer (1)                     | 10             | 0    | 3.5            | 4.9            | 7.0            | ns  |  |

| 16-bit multiplier with 3-stage pipeline (2) | 592            | 0    | 156            | 131            | 93             | MHz |  |

| 256 × 16 RAM read cycle speed (2)           | 0              | 1    | 196            | 154            | 118            | MHz |  |

| 256 × 16 RAM write cycle                    | 0              | 1    | 185            | 143            | 106            | MHz |  |

## Notes:

- (1) This application uses combinatorial inputs and outputs.

- (2) This application uses registered inputs and outputs.

Table 6 shows FLEX 10KE performance for more complex designs. These designs are available as Altera MegaCore $^{\circ}$  functions.

| Table 6. FLEX 10KE Performance for Complex Designs          |          |                |                |                |                |  |  |  |  |

|-------------------------------------------------------------|----------|----------------|----------------|----------------|----------------|--|--|--|--|

| Application                                                 | LEs Used |                | Performance    |                |                |  |  |  |  |

|                                                             |          | -1 Speed Grade | -2 Speed Grade | -3 Speed Grade |                |  |  |  |  |

| 8-bit, 16-tap parallel finite impulse response (FIR) filter | 597      | 192            | 156            | 116            | MSPS           |  |  |  |  |

| 8-bit, 512-point fast Fourier                               | 1,854    | 23.4           | 28.7           | 38.9           | μ <b>s</b> (1) |  |  |  |  |

| transform (FFT) function                                    |          | 113            | 92             | 68             | MHz            |  |  |  |  |

| a16450 universal asynchronous receiver/transmitter (UART)   | 342      | 36             | 28             | 20.5           | MHz            |  |  |  |  |

#### Note:

(1) These values are for calculation time. Calculation time = number of clocks required /  $f_{max}$ . Number of clocks required = ceiling [log 2 (points)/2] × [points +14 + ceiling]

## **Asynchronous Clear**

The flipflop can be cleared by either LABCTRL1 or LABCTRL2. In this mode, the preset signal is tied to VCC to deactivate it.

## **Asynchronous Preset**

An asynchronous preset is implemented as an asynchronous load, or with an asynchronous clear. If DATA3 is tied to VCC, asserting LABCTRL1 asynchronously loads a one into the register. Alternatively, the Altera software can provide preset control by using the clear and inverting the input and output of the register. Inversion control is available for the inputs to both LEs and IOEs. Therefore, if a register is preset by only one of the two LABCTRL signals, the DATA3 input is not needed and can be used for one of the LE operating modes.

## Asynchronous Preset & Clear

When implementing asynchronous clear and preset, LABCTRL1 controls the preset and LABCTRL2 controls the clear. DATA3 is tied to VCC, so that asserting LABCTRL1 asynchronously loads a one into the register, effectively presetting the register. Asserting LABCTRL2 clears the register.

## **Asynchronous Load with Clear**

When implementing an asynchronous load in conjunction with the clear, LABCTRL1 implements the asynchronous load of DATA3 by controlling the register preset and clear. LABCTRL2 implements the clear by controlling the register clear; LABCTRL2 does not have to feed the preset circuits.

## **Asynchronous Load with Preset**

When implementing an asynchronous load in conjunction with preset, the Altera software provides preset control by using the clear and inverting the input and output of the register. Asserting LABCTRL2 presets the register, while asserting LABCTRL1 loads the register. The Altera software inverts the signal that drives DATA3 to account for the inversion of the register's output.

## **Asynchronous Load without Preset or Clear**

When implementing an asynchronous load without preset or clear, LABCTRL1 implements the asynchronous load of DATA3 by controlling the register preset and clear.

On all FLEX 10KE devices (except EPF10K50E and EPF10K200E devices), the input path from the I/O pad to the FastTrack Interconnect has a programmable delay element that can be used to guarantee a zero hold time. EPF10K50S and EPF10K200S devices also support this feature. Depending on the placement of the IOE relative to what it is driving, the designer may choose to turn on the programmable delay to ensure a zero hold time or turn it off to minimize setup time. This feature is used to reduce setup time for complex pin-to-register paths (e.g., PCI designs).

Each IOE selects the clock, clear, clock enable, and output enable controls from a network of I/O control signals called the peripheral control bus. The peripheral control bus uses high-speed drivers to minimize signal skew across the device and provides up to 12 peripheral control signals that can be allocated as follows:

- Up to eight output enable signals

- Up to six clock enable signals

- Up to two clock signals

- Up to two clear signals

If more than six clock enable or eight output enable signals are required, each IOE on the device can be controlled by clock enable and output enable signals driven by specific LEs. In addition to the two clock signals available on the peripheral control bus, each IOE can use one of two dedicated clock pins. Each peripheral control signal can be driven by any of the dedicated input pins or the first LE of each LAB in a particular row. In addition, a LE in a different row can drive a column interconnect, which causes a row interconnect to drive the peripheral control signal. The chipwide reset signal resets all IOE registers, overriding any other control signals.

When a dedicated clock pin drives IOE registers, it can be inverted for all IOEs in the device. All IOEs must use the same sense of the clock. For example, if any IOE uses the inverted clock, all IOEs must use the inverted clock and no IOE can use the non-inverted clock. However, LEs can still use the true or complement of the clock on a LAB-by-LAB basis.

The incoming signal may be inverted at the dedicated clock pin and will drive all IOEs. For the true and complement of a clock to be used to drive IOEs, drive it into both global clock pins. One global clock pin will supply the true, and the other will supply the complement.

When the true and complement of a dedicated input drives IOE clocks, two signals on the peripheral control bus are consumed, one for each sense of the clock.

| Symbol                | Parameter                                                               | Condition            | Min | Тур | Max        | Unit |

|-----------------------|-------------------------------------------------------------------------|----------------------|-----|-----|------------|------|

| $t_R$                 | Input rise time                                                         |                      |     |     | 5          | ns   |

| t <sub>F</sub>        | Input fall time                                                         |                      |     |     | 5          | ns   |

| t <sub>INDUTY</sub>   | Input duty cycle                                                        |                      | 40  |     | 60         | %    |

| f <sub>CLK1</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 1) |                      | 25  |     | 75         | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2) |                      | 16  |     | 37.5       | MHz  |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the MAX+PLUS II software (1) |                      |     |     | 25,000 (2) | PPM  |

| t <sub>INCLKSTB</sub> | Input clock stability (measured between adjacent clocks)                |                      |     |     | 100        | ps   |

| t <sub>LOCK</sub>     | Time required for ClockLock or ClockBoost to acquire lock (3)           |                      |     |     | 10         | μs   |

| t <sub>JITTER</sub>   | Jitter on ClockLock or ClockBoost-                                      | $t_{INCLKSTB} < 100$ |     |     | 250        | ps   |

|                       | generated clock (4)                                                     | $t_{INCLKSTB} < 50$  |     |     | 200 (4)    | ps   |

| t <sub>OUTDUTY</sub>  | Duty cycle for ClockLock or<br>ClockBoost-generated clock               |                      | 40  | 50  | 60         | %    |

- (1) To implement the ClockLock and ClockBoost circuitry with the MAX+PLUS II software, designers must specify the input frequency. The Altera software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The f<sub>CLKDEV</sub> parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) Twenty-five thousand parts per million (PPM) equates to 2.5% of input clock period.

- (3) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration because the t<sub>LOCK</sub> value is less than the time required for configuration.

- (4) The  $t_{IITTER}$  specification is measured under long-term observation. The maximum value for  $t_{IITTER}$  is 200 ps if  $t_{INCLKSTB}$  is lower than 50 ps.

# I/O Configuration

This section discusses the peripheral component interconnect (PCI) pull-up clamping diode option, slew-rate control, open-drain output option, and MultiVolt I/O interface for FLEX 10KE devices. The PCI pull-up clamping diode, slew-rate control, and open-drain output options are controlled pin-by-pin via Altera software logic options. The MultiVolt I/O interface is controlled by connecting  $V_{\rm CCIO}$  to a different voltage than  $V_{\rm CCINT}.$  Its effect can be simulated in the Altera software via the **Global Project Device Options** dialog box (Assign menu).

to Be Driven

Figure 20. FLEX 10KE JTAG Waveforms TMS TDI t<sub>JPSU</sub> TCK t<sub>JPZX</sub> t <sub>JPXZ</sub>  $\mathbf{t}_{\mathsf{JPCO}}$ TDO t<sub>JSH</sub> t<sub>JSSU</sub> Signal to Be Captured t<sub>JSCO</sub>t<sub>JSZX</sub> t<sub>JSXZ</sub> Signal

Figure 20 shows the timing requirements for the JTAG signals.

Table 18 shows the timing parameters and values for FLEX 10KE devices.

| Table 1           | 8. FLEX 10KE JTAG Timing Parameters & Values   |     |     |      |

|-------------------|------------------------------------------------|-----|-----|------|

| Symbol            | Parameter                                      | Min | Max | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output |     | 35  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |

## **Generic Testing**

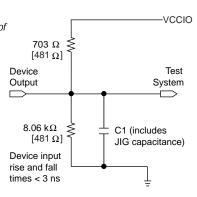

Each FLEX 10KE device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for FLEX 10KE devices are made under conditions equivalent to those shown in Figure 21. Multiple test patterns can be used to configure devices during all stages of the production flow.

Figure 21. FLEX 10KE AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast-groundcurrent transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result. Numbers in brackets are for 2.5-V devices or outputs. Numbers without brackets are for 3.3-V. devices or outputs.

## Operating Conditions

Tables 19 through 23 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 2.5-V FLEX 10KE devices.

| Symbol            | Parameter                  | Conditions                        | Min    | Max   | Unit  |

|-------------------|----------------------------|-----------------------------------|--------|-------|-------|

|                   | 1 di diffictor             | Conditions                        | 141111 | IVIGA | Oiiit |

| $V_{CCINT}$       | Supply voltage             | With respect to ground (2)        | -0.5   | 3.6   | V     |

| V <sub>CCIO</sub> |                            |                                   | -0.5   | 4.6   | V     |

| V <sub>I</sub>    | DC input voltage           |                                   | -2.0   | 5.75  | V     |

| I <sub>OUT</sub>  | DC output current, per pin |                                   | -25    | 25    | mA    |

| T <sub>STG</sub>  | Storage temperature        | No bias                           | -65    | 150   | ° C   |

| T <sub>AMB</sub>  | Ambient temperature        | Under bias                        | -65    | 135   | °C    |

| TJ                | Junction temperature       | PQFP, TQFP, BGA, and FineLine BGA |        | 135   | °C    |

|                   |                            | packages, under bias              |        |       |       |

|                   |                            | Ceramic PGA packages, under bias  |        | 150   | °C    |

Timing simulation and delay prediction are available with the Altera Simulator and Timing Analyzer, or with industry-standard EDA tools. The Simulator offers both pre-synthesis functional simulation to evaluate logic design accuracy and post-synthesis timing simulation with 0.1-ns resolution. The Timing Analyzer provides point-to-point timing delay information, setup and hold time analysis, and device-wide performance analysis.

Figure 24 shows the overall timing model, which maps the possible paths to and from the various elements of the FLEX 10KE device.

Dedicated Clock/Input

Interconnect

Logic Embedded Array Block

Figures 25 through 28 show the delays that correspond to various paths and functions within the LE, IOE, EAB, and bidirectional timing models.

| 3 Timing Macroparameters Note (1), (6)                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                               | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| EAB address access delay                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB asynchronous read cycle time                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB synchronous read cycle time                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB write pulse width                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB asynchronous write cycle time                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB synchronous write cycle time                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB data-in to data-out valid delay                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB clock-to-output delay when using output registers                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB data/address setup time before clock when using input register                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB data/address hold time after clock when using input register                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB WE setup time before clock when using input register                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB WE hold time after clock when using input register                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB data setup time before falling edge of write pulse when not using input registers   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB data hold time after falling edge of write pulse when not using input registers     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB address setup time before rising edge of write pulse when not using input registers |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB address hold time after falling edge of write pulse when not using input registers  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EAB write enable to data output valid delay                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                         | Parameter  EAB address access delay  EAB asynchronous read cycle time  EAB synchronous read cycle time  EAB write pulse width  EAB asynchronous write cycle time  EAB synchronous write cycle time  EAB data-in to data-out valid delay  EAB clock-to-output delay when using output registers  EAB data/address setup time before clock when using input register  EAB we setup time before clock when using input register  EAB we hold time after clock when using input register  EAB data setup time before falling edge of write pulse when not using input registers  EAB data hold time after falling edge of write pulse when not using input registers  EAB address setup time before rising edge of write pulse when not using input registers  EAB address setup time before rising edge of write pulse when not using input registers  EAB address hold time after falling edge of write pulse when not using input registers |

| Table 30. External Bidirectional Timing Parameters Note (9) |                                                                                             |            |  |  |  |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

| Symbol                                                      | Conditions                                                                                  |            |  |  |  |  |  |

| <sup>t</sup> INSUBIDIR                                      | Setup time for bi-directional pins with global clock at same-row or same-column LE register |            |  |  |  |  |  |

| t <sub>INHBIDIR</sub>                                       | Hold time for bidirectional pins with global clock at same-row or same-column LE register   |            |  |  |  |  |  |

| t <sub>INH</sub>                                            | Hold time with global clock at IOE register                                                 |            |  |  |  |  |  |

| <sup>t</sup> OUTCOBIDIR                                     | Clock-to-output delay for bidirectional pins with global clock at IOE register              | C1 = 35 pF |  |  |  |  |  |

| t <sub>XZBIDIR</sub>                                        | Synchronous IOE output buffer disable delay                                                 | C1 = 35 pF |  |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                        | Synchronous IOE output buffer enable delay, slow slew rate= off                             | C1 = 35 pF |  |  |  |  |  |

- Microparameters are timing delays contributed by individual architectural elements. These parameters cannot be measured explicitly.

- (2) Operating conditions: VCCIO =  $3.3 \text{ V} \pm 10\%$  for commercial or industrial use.

- (3) Operating conditions: VCCIO =  $2.5 \text{ V} \pm 5\%$  for commercial or industrial use in EPF10K30E, EPF10K50S, EPF10K100E, EPF10K130E, and EPF10K200S devices.

- (4) Operating conditions: VCCIO = 3.3 V.

- (5) Because the RAM in the EAB is self-timed, this parameter can be ignored when the WE signal is registered.

- (6) EAB macroparameters are internal parameters that can simplify predicting the behavior of an EAB at its boundary; these parameters are calculated by summing selected microparameters.

- (7) These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

- (8) Contact Altera Applications for test circuit specifications and test conditions.

- (9) This timing parameter is sample-tested only.

- (10) This parameter is measured with the measurement and test conditions, including load, specified in the PCI Local Bus Specification, revision 2.2.

| Table 50. EPF10K100E External Timing Parameters Notes (1), (2) |         |                |     |                |     |          |      |  |

|----------------------------------------------------------------|---------|----------------|-----|----------------|-----|----------|------|--|

| Symbol                                                         | -1 Spec | -1 Speed Grade |     | -2 Speed Grade |     | ed Grade | Unit |  |

|                                                                | Min     | Max            | Min | Max            | Min | Max      | ]    |  |

| t <sub>DRR</sub>                                               |         | 9.0            |     | 12.0           |     | 16.0     | ns   |  |

| t <sub>INSU</sub> (3)                                          | 2.0     |                | 2.5 |                | 3.3 |          | ns   |  |

| t <sub>INH</sub> (3)                                           | 0.0     |                | 0.0 |                | 0.0 |          | ns   |  |

| t <sub>outco</sub> (3)                                         | 2.0     | 5.2            | 2.0 | 6.9            | 2.0 | 9.1      | ns   |  |

| t <sub>INSU</sub> (4)                                          | 2.0     |                | 2.2 |                | -   |          | ns   |  |

| t <sub>INH</sub> (4)                                           | 0.0     |                | 0.0 |                | -   |          | ns   |  |

| t <sub>OUTCO</sub> (4)                                         | 0.5     | 3.0            | 0.5 | 4.6            | -   | -        | ns   |  |

| t <sub>PCISU</sub>                                             | 3.0     |                | 6.2 |                | -   |          | ns   |  |

| t <sub>PCIH</sub>                                              | 0.0     |                | 0.0 |                | _   |          | ns   |  |

| t <sub>PCICO</sub>                                             | 2.0     | 6.0            | 2.0 | 6.9            | _   | _        | ns   |  |

| Table 51. EPF10K100E External Bidirectional Timing Parameters    Notes (1), (2) |                |     |         |                |     |          |      |  |

|---------------------------------------------------------------------------------|----------------|-----|---------|----------------|-----|----------|------|--|

| Symbol                                                                          | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |  |

|                                                                                 | Min            | Max | Min     | Max            | Min | Max      |      |  |

| t <sub>INSUBIDIR</sub> (3)                                                      | 1.7            |     | 2.5     |                | 3.3 |          | ns   |  |

| t <sub>INHBIDIR</sub> (3)                                                       | 0.0            |     | 0.0     |                | 0.0 |          | ns   |  |

| t <sub>INSUBIDIR</sub> (4)                                                      | 2.0            |     | 2.8     |                | _   |          | ns   |  |

| t <sub>INHBIDIR</sub> (4)                                                       | 0.0            |     | 0.0     |                | _   |          | ns   |  |

| toutcobidir (3)                                                                 | 2.0            | 5.2 | 2.0     | 6.9            | 2.0 | 9.1      | ns   |  |

| t <sub>XZBIDIR</sub> (3)                                                        |                | 5.6 |         | 7.5            |     | 10.1     | ns   |  |

| t <sub>ZXBIDIR</sub> (3)                                                        |                | 5.6 |         | 7.5            |     | 10.1     | ns   |  |

| toutcobidir (4)                                                                 | 0.5            | 3.0 | 0.5     | 4.6            | _   | -        | ns   |  |

| t <sub>XZBIDIR</sub> (4)                                                        |                | 4.6 |         | 6.5            |     | -        | ns   |  |

| t <sub>ZXBIDIR</sub> (4)                                                        |                | 4.6 |         | 6.5            |     | _        | ns   |  |

- (1) All timing parameters are described in Tables 24 through 30 in this data sheet.

- (2) These parameters are specified by characterization.

- (3) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

- (4) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

Tables 52 through 58 show EPF10K130E device internal and external timing parameters.

| Table 52. EPF10K130E Device LE Timing Microparameters Note (1) |                |     |         |                |     |          |      |  |  |

|----------------------------------------------------------------|----------------|-----|---------|----------------|-----|----------|------|--|--|

| Symbol                                                         | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |  |  |

|                                                                | Min            | Max | Min     | Max            | Min | Max      |      |  |  |

| $t_{LUT}$                                                      |                | 0.6 |         | 0.9            |     | 1.3      | ns   |  |  |

| t <sub>CLUT</sub>                                              |                | 0.6 |         | 0.8            |     | 1.0      | ns   |  |  |

| t <sub>RLUT</sub>                                              |                | 0.7 |         | 0.9            |     | 0.2      | ns   |  |  |

| t <sub>PACKED</sub>                                            |                | 0.3 |         | 0.5            |     | 0.6      | ns   |  |  |

| t <sub>EN</sub>                                                |                | 0.2 |         | 0.3            |     | 0.4      | ns   |  |  |

| t <sub>CICO</sub>                                              |                | 0.1 |         | 0.1            |     | 0.2      | ns   |  |  |

| t <sub>CGEN</sub>                                              |                | 0.4 |         | 0.6            |     | 0.8      | ns   |  |  |

| t <sub>CGENR</sub>                                             |                | 0.1 |         | 0.1            |     | 0.2      | ns   |  |  |

| t <sub>CASC</sub>                                              |                | 0.6 |         | 0.9            |     | 1.2      | ns   |  |  |

| $t_{C}$                                                        |                | 0.3 |         | 0.5            |     | 0.6      | ns   |  |  |

| t <sub>CO</sub>                                                |                | 0.5 |         | 0.7            |     | 0.8      | ns   |  |  |

| t <sub>COMB</sub>                                              |                | 0.3 |         | 0.5            |     | 0.6      | ns   |  |  |

| t <sub>SU</sub>                                                | 0.5            |     | 0.7     |                | 0.8 |          | ns   |  |  |

| $t_H$                                                          | 0.6            |     | 0.7     |                | 1.0 |          | ns   |  |  |

| t <sub>PRE</sub>                                               |                | 0.9 |         | 1.2            |     | 1.6      | ns   |  |  |

| t <sub>CLR</sub>                                               |                | 0.9 |         | 1.2            |     | 1.6      | ns   |  |  |

| t <sub>CH</sub>                                                | 1.5            |     | 1.5     |                | 2.5 |          | ns   |  |  |

| t <sub>CL</sub>                                                | 1.5            |     | 1.5     |                | 2.5 |          | ns   |  |  |

| Symbol               | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|----------------------|----------------|-----|---------|----------------|-----|----------|------|

|                      | Min            | Max | Min     | Max            | Min | Max      |      |

| $t_{IOD}$            |                | 1.3 |         | 1.5            |     | 2.0      | ns   |

| t <sub>IOC</sub>     |                | 0.0 |         | 0.0            |     | 0.0      | ns   |

| t <sub>ioco</sub>    |                | 0.6 |         | 0.8            |     | 1.0      | ns   |

| t <sub>I</sub> OCOMB |                | 0.6 |         | 0.8            |     | 1.0      | ns   |

| iosu                 | 1.0            |     | 1.2     |                | 1.6 |          | ns   |

| t <sub>IOH</sub>     | 0.9            |     | 0.9     |                | 1.4 |          | ns   |

| t <sub>IOCLR</sub>   |                | 0.6 |         | 0.8            |     | 1.0      | ns   |

| OD1                  |                | 2.8 |         | 4.1            |     | 5.5      | ns   |

| $t_{OD2}$            |                | 2.8 |         | 4.1            |     | 5.5      | ns   |

| Table 54. EPF10     | K130E Device | EAB Intern     | al Micropara | ameters (Pa    | art 2 of 2) | Note (1) |      |

|---------------------|--------------|----------------|--------------|----------------|-------------|----------|------|

| Symbol              | -1 Spee      | -1 Speed Grade |              | -2 Speed Grade |             | ed Grade | Unit |

|                     | Min          | Max            | Min          | Max            | Min         | Max      |      |

| $t_{DD}$            |              | 1.5            |              | 2.0            |             | 2.6      | ns   |

| t <sub>EABOUT</sub> |              | 0.2            |              | 0.3            |             | 0.3      | ns   |

| t <sub>EABCH</sub>  | 1.5          |                | 2.0          |                | 2.5         |          | ns   |

| t <sub>EABCL</sub>  | 2.7          |                | 3.5          |                | 4.7         |          | ns   |

| Table 55. EPF10K130E Device EAB Internal Timing Macroparameters Note (1) |                |     |         |                |      |          |      |  |  |

|--------------------------------------------------------------------------|----------------|-----|---------|----------------|------|----------|------|--|--|

| Symbol                                                                   | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |      | ed Grade | Unit |  |  |

|                                                                          | Min            | Max | Min     | Max            | Min  | Max      |      |  |  |

| t <sub>EABAA</sub>                                                       |                | 5.9 |         | 7.5            |      | 9.9      | ns   |  |  |

| t <sub>EABRCOMB</sub>                                                    | 5.9            |     | 7.5     |                | 9.9  |          | ns   |  |  |

| t <sub>EABRCREG</sub>                                                    | 5.1            |     | 6.4     |                | 8.5  |          | ns   |  |  |

| t <sub>EABWP</sub>                                                       | 2.7            |     | 3.5     |                | 4.7  |          | ns   |  |  |

| t <sub>EABWCOMB</sub>                                                    | 5.9            |     | 7.7     |                | 10.3 |          | ns   |  |  |

| t <sub>EABWCREG</sub>                                                    | 5.4            |     | 7.0     |                | 9.4  |          | ns   |  |  |

| t <sub>EABDD</sub>                                                       |                | 3.4 |         | 4.5            |      | 5.9      | ns   |  |  |

| t <sub>EABDATACO</sub>                                                   |                | 0.5 |         | 0.7            |      | 0.8      | ns   |  |  |

| t <sub>EABDATASU</sub>                                                   | 0.8            |     | 1.0     |                | 1.4  |          | ns   |  |  |

| t <sub>EABDATAH</sub>                                                    | 0.1            |     | 0.1     |                | 0.2  |          | ns   |  |  |

| t <sub>EABWESU</sub>                                                     | 1.1            |     | 1.4     |                | 1.9  |          | ns   |  |  |

| t <sub>EABWEH</sub>                                                      | 0.0            |     | 0.0     |                | 0.0  |          | ns   |  |  |

| t <sub>EABWDSU</sub>                                                     | 1.0            |     | 1.3     |                | 1.7  |          | ns   |  |  |

| t <sub>EABWDH</sub>                                                      | 0.2            |     | 0.2     |                | 0.3  |          | ns   |  |  |

| t <sub>EABWASU</sub>                                                     | 4.1            |     | 5.1     |                | 6.8  |          | ns   |  |  |

| t <sub>EABWAH</sub>                                                      | 0.0            |     | 0.0     |                | 0.0  |          | ns   |  |  |

| t <sub>EABWO</sub>                                                       |                | 3.4 |         | 4.5            |      | 5.9      | ns   |  |  |

| Table 59. EPF10K200E Device LE Timing Microparameters (Part 2 of 2)   Note (1) |         |         |                |     |                |     |      |  |  |  |

|--------------------------------------------------------------------------------|---------|---------|----------------|-----|----------------|-----|------|--|--|--|

| Symbol                                                                         | -1 Spee | d Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |  |  |

|                                                                                | Min     | Max     | Min            | Max | Min            | Max |      |  |  |  |

| $t_H$                                                                          | 0.9     |         | 1.1            |     | 1.5            |     | ns   |  |  |  |

| t <sub>PRE</sub>                                                               |         | 0.5     |                | 0.6 |                | 0.8 | ns   |  |  |  |

| t <sub>CLR</sub>                                                               |         | 0.5     |                | 0.6 |                | 0.8 | ns   |  |  |  |

| t <sub>CH</sub>                                                                | 2.0     |         | 2.5            |     | 3.0            |     | ns   |  |  |  |

| $t_{CL}$                                                                       | 2.0     |         | 2.5            |     | 3.0            |     | ns   |  |  |  |

| Table 60. EPF10K200E Device IOE Timing Microparameters Note (1) |                |     |                |     |                |      |      |  |  |

|-----------------------------------------------------------------|----------------|-----|----------------|-----|----------------|------|------|--|--|

| Symbol                                                          | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |  |  |

|                                                                 | Min            | Max | Min            | Max | Min            | Max  |      |  |  |

| t <sub>IOD</sub>                                                |                | 1.6 |                | 1.9 |                | 2.6  | ns   |  |  |

| $t_{IOC}$                                                       |                | 0.3 |                | 0.3 |                | 0.5  | ns   |  |  |

| t <sub>IOCO</sub>                                               |                | 1.6 |                | 1.9 |                | 2.6  | ns   |  |  |

| t <sub>IOCOMB</sub>                                             |                | 0.5 |                | 0.6 |                | 0.8  | ns   |  |  |

| t <sub>IOSU</sub>                                               | 0.8            |     | 0.9            |     | 1.2            |      | ns   |  |  |

| t <sub>IOH</sub>                                                | 0.7            |     | 0.8            |     | 1.1            |      | ns   |  |  |

| t <sub>IOCLR</sub>                                              |                | 0.2 |                | 0.2 |                | 0.3  | ns   |  |  |

| t <sub>OD1</sub>                                                |                | 0.6 |                | 0.7 |                | 0.9  | ns   |  |  |

| t <sub>OD2</sub>                                                |                | 0.1 |                | 0.2 |                | 0.7  | ns   |  |  |

| t <sub>OD3</sub>                                                |                | 2.5 |                | 3.0 |                | 3.9  | ns   |  |  |

| $t_{XZ}$                                                        |                | 4.4 |                | 5.3 |                | 7.1  | ns   |  |  |

| t <sub>ZX1</sub>                                                |                | 4.4 |                | 5.3 |                | 7.1  | ns   |  |  |

| $t_{ZX2}$                                                       |                | 3.9 |                | 4.8 |                | 6.9  | ns   |  |  |

| $t_{ZX3}$                                                       |                | 6.3 |                | 7.6 |                | 10.1 | ns   |  |  |

| t <sub>INREG</sub>                                              |                | 4.8 |                | 5.7 |                | 7.7  | ns   |  |  |

| t <sub>IOFD</sub>                                               |                | 1.5 |                | 1.8 |                | 2.4  | ns   |  |  |

| t <sub>INCOMB</sub>                                             |                | 1.5 |                | 1.8 |                | 2.4  | ns   |  |  |

| Symbol                  | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | ed Grade | Unit |

|-------------------------|---------|---------|---------|---------|---------|----------|------|

|                         | Min     | Max     | Min     | Max     | Min     | Max      |      |

| t <sub>EABWCOMB</sub>   | 6.7     |         | 8.1     |         | 10.7    |          | ns   |

| t <sub>EABWCREG</sub>   | 6.6     |         | 8.0     |         | 10.6    |          | ns   |

| t <sub>EABDD</sub>      |         | 4.0     |         | 5.1     |         | 6.7      | ns   |

| t <sub>EABDATA</sub> CO |         | 0.8     |         | 1.0     |         | 1.3      | ns   |

| t <sub>EABDATASU</sub>  | 1.3     |         | 1.6     |         | 2.1     |          | ns   |

| t <sub>EABDATAH</sub>   | 0.0     |         | 0.0     |         | 0.0     |          | ns   |

| t <sub>EABWESU</sub>    | 0.9     |         | 1.1     |         | 1.5     |          | ns   |

| t <sub>EABWEH</sub>     | 0.4     |         | 0.5     |         | 0.6     |          | ns   |

| t <sub>EABWDSU</sub>    | 1.5     |         | 1.8     |         | 2.4     |          | ns   |

| t <sub>EABWDH</sub>     | 0.0     |         | 0.0     |         | 0.0     |          | ns   |

| t <sub>EABWASU</sub>    | 3.0     |         | 3.6     |         | 4.7     |          | ns   |

| t <sub>EABWAH</sub>     | 0.4     |         | 0.5     |         | 0.7     |          | ns   |

| t <sub>EABW</sub> O     |         | 3.4     |         | 4.4     |         | 5.8      | ns   |

| Table 63. EPF10k        | K200E Device   | Interconne | ct Timing M | licroparame | ters No        | te (1) |      |

|-------------------------|----------------|------------|-------------|-------------|----------------|--------|------|

| Symbol                  | -1 Speed Grade |            | -2 Spec     | ed Grade    | -3 Speed Grade |        | Unit |

|                         | Min            | Max        | Min         | Max         | Min            | Max    |      |

| t <sub>DIN2IOE</sub>    |                | 4.2        |             | 4.6         |                | 5.7    | ns   |

| t <sub>DIN2LE</sub>     |                | 1.7        |             | 1.7         |                | 2.0    | ns   |

| t <sub>DIN2DATA</sub>   |                | 1.9        |             | 2.1         |                | 3.0    | ns   |

| t <sub>DCLK2IOE</sub>   |                | 2.5        |             | 2.9         |                | 4.0    | ns   |

| t <sub>DCLK2LE</sub>    |                | 1.7        |             | 1.7         |                | 2.0    | ns   |

| t <sub>SAMELAB</sub>    |                | 0.1        |             | 0.1         |                | 0.2    | ns   |

| t <sub>SAMEROW</sub>    |                | 2.3        |             | 2.6         |                | 3.6    | ns   |

| t <sub>SAMECOLUMN</sub> |                | 2.5        |             | 2.7         |                | 4.1    | ns   |

| t <sub>DIFFROW</sub>    |                | 4.8        |             | 5.3         |                | 7.7    | ns   |

| t <sub>TWOROWS</sub>    |                | 7.1        |             | 7.9         |                | 11.3   | ns   |

| t <sub>LEPERIPH</sub>   |                | 7.0        |             | 7.6         |                | 9.0    | ns   |

| t <sub>LABCARRY</sub>   |                | 0.1        |             | 0.1         |                | 0.2    | ns   |

| t <sub>LABCASC</sub>    |                | 0.9        |             | 1.0         |                | 1.4    | ns   |

| Table 64. EPF10    | K200E Extern | al Timing Pa   | arameters | Notes (1),     | (2) |         |      |

|--------------------|--------------|----------------|-----------|----------------|-----|---------|------|

| Symbol             | -1 Spec      | -1 Speed Grade |           | -2 Speed Grade |     | d Grade | Unit |

|                    | Min          | Max            | Min       | Max            | Min | Max     |      |

| t <sub>DRR</sub>   |              | 10.0           |           | 12.0           |     | 16.0    | ns   |

| t <sub>INSU</sub>  | 2.8          |                | 3.4       |                | 4.4 |         | ns   |

| t <sub>INH</sub>   | 0.0          |                | 0.0       |                | 0.0 |         | ns   |

| t <sub>оитсо</sub> | 2.0          | 4.5            | 2.0       | 5.3            | 2.0 | 7.8     | ns   |

| t <sub>PCISU</sub> | 3.0          |                | 6.2       |                | -   |         | ns   |

| t <sub>PCIH</sub>  | 0.0          |                | 0.0       |                | -   |         | ns   |

| t <sub>PCICO</sub> | 2.0          | 6.0            | 2.0       | 8.9            | -   | -       | ns   |

| Table 65. EPF10K200E External Bidirectional Timing Parameters    Notes (1), (2) |         |         |                |     |                |      |      |  |  |  |  |

|---------------------------------------------------------------------------------|---------|---------|----------------|-----|----------------|------|------|--|--|--|--|

| Symbol                                                                          | -1 Spee | d Grade | -2 Speed Grade |     | -3 Speed Grade |      | Unit |  |  |  |  |

|                                                                                 | Min     | Max     | Min            | Max | Min            | Max  |      |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                                          | 3.0     |         | 4.0            |     | 5.5            |      | ns   |  |  |  |  |

| t <sub>INHBIDIR</sub>                                                           | 0.0     |         | 0.0            |     | 0.0            |      | ns   |  |  |  |  |

| t <sub>OUTCOBIDIR</sub>                                                         | 2.0     | 4.5     | 2.0            | 5.3 | 2.0            | 7.8  | ns   |  |  |  |  |

| t <sub>XZBIDIR</sub>                                                            |         | 8.1     |                | 9.5 |                | 13.0 | ns   |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                                            |         | 8.1     |                | 9.5 |                | 13.0 | ns   |  |  |  |  |

- (1) All timing parameters are described in Tables 24 through 30 in this data sheet.

- (2) These parameters are specified by characterization.

Tables 66 through 79 show EPF10K50S and EPF10K200S device external timing parameters.

| Table 66. EPF10k    | (50S Device | LE Timing N | 1icroparame | eters (Part 1  | of 2) No | ote (1) |      |

|---------------------|-------------|-------------|-------------|----------------|----------|---------|------|

| Symbol              | -1 Spec     | ed Grade    | -2 Spee     | -2 Speed Grade |          | d Grade | Unit |

|                     | Min         | Max         | Min         | Max            | Min      | Max     |      |

| $t_{LUT}$           |             | 0.6         |             | 0.8            |          | 1.1     | ns   |

| t <sub>CLUT</sub>   |             | 0.5         |             | 0.6            |          | 0.8     | ns   |

| t <sub>RLUT</sub>   |             | 0.6         |             | 0.7            |          | 0.9     | ns   |

| t <sub>PACKED</sub> |             | 0.2         |             | 0.3            |          | 0.4     | ns   |

| $t_{EN}$            |             | 0.6         |             | 0.7            |          | 0.9     | ns   |

| t <sub>CICO</sub>   |             | 0.1         |             | 0.1            |          | 0.1     | ns   |

| t <sub>CGEN</sub>   |             | 0.4         |             | 0.5            |          | 0.6     | ns   |

| Table 66. EPF10K50S Device LE Timing Microparameters (Part 2 of 2) Note (1) |         |                |     |                |     |         |      |  |  |

|-----------------------------------------------------------------------------|---------|----------------|-----|----------------|-----|---------|------|--|--|

| Symbol                                                                      | -1 Spec | -1 Speed Grade |     | -2 Speed Grade |     | d Grade | Unit |  |  |

|                                                                             | Min     | Max            | Min | Max            | Min | Max     |      |  |  |

| t <sub>CGENR</sub>                                                          |         | 0.1            |     | 0.1            |     | 0.1     | ns   |  |  |

| t <sub>CASC</sub>                                                           |         | 0.5            |     | 0.8            |     | 1.0     | ns   |  |  |

| $t_{\mathbb{C}}$                                                            |         | 0.5            |     | 0.6            |     | 0.8     | ns   |  |  |

| $t_{CO}$                                                                    |         | 0.6            |     | 0.6            |     | 0.7     | ns   |  |  |

| t <sub>COMB</sub>                                                           |         | 0.3            |     | 0.4            |     | 0.5     | ns   |  |  |

| $t_{SU}$                                                                    | 0.5     |                | 0.6 |                | 0.7 |         | ns   |  |  |

| $t_H$                                                                       | 0.5     |                | 0.6 |                | 0.8 |         | ns   |  |  |

| t <sub>PRE</sub>                                                            |         | 0.4            |     | 0.5            |     | 0.7     | ns   |  |  |

| t <sub>CLR</sub>                                                            |         | 0.8            |     | 1.0            |     | 1.2     | ns   |  |  |

| t <sub>CH</sub>                                                             | 2.0     |                | 2.5 |                | 3.0 |         | ns   |  |  |

| $t_{CL}$                                                                    | 2.0     |                | 2.5 |                | 3.0 |         | ns   |  |  |

| Table 67. EPF10K50S Device IOE Timing Microparameters   Note (1) |                |     |                |     |                |     |      |  |  |

|------------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|--|

| Symbol                                                           | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |  |

|                                                                  | Min            | Max | Min            | Max | Min            | Max |      |  |  |

| $t_{IOD}$                                                        |                | 1.3 |                | 1.3 |                | 1.9 | ns   |  |  |

| $t_{IOC}$                                                        |                | 0.3 |                | 0.4 |                | 0.4 | ns   |  |  |

| t <sub>IOCO</sub>                                                |                | 1.7 |                | 2.1 |                | 2.6 | ns   |  |  |

| t <sub>IOCOMB</sub>                                              |                | 0.5 |                | 0.6 |                | 0.8 | ns   |  |  |

| t <sub>IOSU</sub>                                                | 0.8            |     | 1.0            |     | 1.3            |     | ns   |  |  |

| t <sub>IOH</sub>                                                 | 0.4            |     | 0.5            |     | 0.6            |     | ns   |  |  |

| t <sub>IOCLR</sub>                                               |                | 0.2 |                | 0.2 |                | 0.4 | ns   |  |  |

| t <sub>OD1</sub>                                                 |                | 1.2 |                | 1.2 |                | 1.9 | ns   |  |  |

| t <sub>OD2</sub>                                                 |                | 0.7 |                | 0.8 |                | 1.7 | ns   |  |  |

| t <sub>OD3</sub>                                                 |                | 2.7 |                | 3.0 |                | 4.3 | ns   |  |  |

| $t_{XZ}$                                                         |                | 4.7 |                | 5.7 |                | 7.5 | ns   |  |  |

| $t_{ZX1}$                                                        |                | 4.7 |                | 5.7 |                | 7.5 | ns   |  |  |

| $t_{ZX2}$                                                        |                | 4.2 |                | 5.3 |                | 7.3 | ns   |  |  |

| $t_{ZX3}$                                                        |                | 6.2 |                | 7.5 |                | 9.9 | ns   |  |  |

| t <sub>INREG</sub>                                               |                | 3.5 |                | 4.2 |                | 5.6 | ns   |  |  |

| t <sub>IOFD</sub>                                                |                | 1.1 |                | 1.3 |                | 1.8 | ns   |  |  |

| t <sub>INCOMB</sub>                                              |                | 1.1 |                | 1.3 |                | 1.8 | ns   |  |  |

| Table 69. EPF10        | K50S Device    | EAB Interna | l Timing Ma    | croparamet | ers Note       | (1) |      |

|------------------------|----------------|-------------|----------------|------------|----------------|-----|------|

| Symbol                 | -1 Speed Grade |             | -2 Speed Grade |            | -3 Speed Grade |     | Unit |

|                        | Min            | Max         | Min            | Max        | Min            | Max |      |

| t <sub>EABAA</sub>     |                | 3.7         |                | 5.2        |                | 7.0 | ns   |

| t <sub>EABRCCOMB</sub> | 3.7            |             | 5.2            |            | 7.0            |     | ns   |

| t <sub>EABRCREG</sub>  | 3.5            |             | 4.9            |            | 6.6            |     | ns   |

| t <sub>EABWP</sub>     | 2.0            |             | 2.8            |            | 3.8            |     | ns   |

| t <sub>EABWCCOMB</sub> | 4.5            |             | 6.3            |            | 8.6            |     | ns   |

| t <sub>EABWCREG</sub>  | 5.6            |             | 7.8            |            | 10.6           |     | ns   |

| t <sub>EABDD</sub>     |                | 3.8         |                | 5.3        |                | 7.2 | ns   |

| t <sub>EABDATACO</sub> |                | 0.8         |                | 1.1        |                | 1.5 | ns   |

| t <sub>EABDATASU</sub> | 1.1            |             | 1.6            |            | 2.1            |     | ns   |

| t <sub>EABDATAH</sub>  | 0.0            |             | 0.0            |            | 0.0            |     | ns   |

| t <sub>EABWESU</sub>   | 0.7            |             | 1.0            |            | 1.3            |     | ns   |

| t <sub>EABWEH</sub>    | 0.4            |             | 0.6            |            | 0.8            |     | ns   |

| t <sub>EABWDSU</sub>   | 1.2            |             | 1.7            |            | 2.2            |     | ns   |

| t <sub>EABWDH</sub>    | 0.0            |             | 0.0            |            | 0.0            |     | ns   |

| t <sub>EABWASU</sub>   | 1.6            |             | 2.3            |            | 3.0            |     | ns   |

| t <sub>EABWAH</sub>    | 0.9            |             | 1.2            |            | 1.8            |     | ns   |

| t <sub>EABWO</sub>     |                | 3.1         |                | 4.3        |                | 5.9 | ns   |

| Table 70. EPF10K50S Device Interconnect Timing Microparameters         Note (1) |                |     |                |     |                |     |      |

|---------------------------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|

| Symbol                                                                          | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|                                                                                 | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>DIN2IOE</sub>                                                            |                | 3.1 |                | 3.7 |                | 4.6 | ns   |

| t <sub>DIN2LE</sub>                                                             |                | 1.7 |                | 2.1 |                | 2.7 | ns   |

| t <sub>DIN2DATA</sub>                                                           |                | 2.7 |                | 3.1 |                | 5.1 | ns   |

| t <sub>DCLK2IOE</sub>                                                           |                | 1.6 |                | 1.9 |                | 2.6 | ns   |

| t <sub>DCLK2LE</sub>                                                            |                | 1.7 |                | 2.1 |                | 2.7 | ns   |