Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 216                                                          |

| Number of Logic Elements/Cells | 1728                                                         |

| Total RAM Bits                 | 24576                                                        |

| Number of I/O                  | 147                                                          |

| Number of Gates                | 119000                                                       |

| Voltage - Supply               | 2.375V ~ 2.625V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                              |

| Package / Case                 | 208-BFQFP                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k30eqc208-3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

For more information on FLEX device configuration, see the following documents:

- Configuration Devices for APEX & FLEX Devices Data Sheet

- BitBlaster Serial Download Cable Data Sheet

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- MasterBlaster Download Cable Data Sheet

- Application Note 116 (Configuring APEX 20K, FLEX 10K, & FLEX 6000 Devices)

FLEX 10KE devices are supported by the Altera development systems, which are integrated packages that offer schematic, text (including AHDL), and waveform design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, and device configuration. The Altera software provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX workstation-based EDA tools

The Altera software works easily with common gate array EDA tools for synthesis and simulation. For example, the Altera software can generate Verilog HDL files for simulation with tools such as Cadence Verilog-XL. Additionally, the Altera software contains EDA libraries that use device-specific features such as carry chains, which are used for fast counter and arithmetic functions. For instance, the Synopsys Design Compiler library supplied with the Altera development system includes DesignWare functions that are optimized for the FLEX 10KE architecture.

The Altera development system runs on Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800.

See the MAX+PLUS II Programmable Logic Development System & Software Data Sheet and the Quartus Programmable Logic Development System & Software Data Sheet for more information.

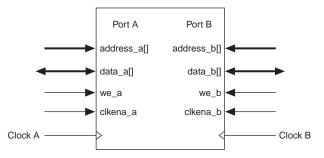

The EAB can also use Altera megafunctions to implement dual-port RAM applications where both ports can read or write, as shown in Figure 3.

Figure 3. FLEX 10KE EAB in Dual-Port RAM Mode

The FLEX 10KE EAB can be used in a single-port mode, which is useful for backward-compatibility with FLEX 10K designs (see Figure 4).

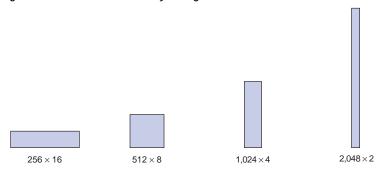

When used as RAM, each EAB can be configured in any of the following sizes:  $256 \times 16$ ,  $512 \times 8$ ,  $1,024 \times 4$ , or  $2,048 \times 2$  (see Figure 5).

Figure 5. FLEX 10KE EAB Memory Configurations

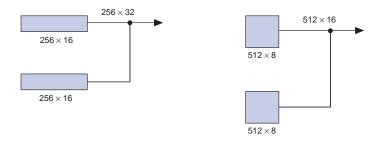

Larger blocks of RAM are created by combining multiple EABs. For example, two  $256\times16$  RAM blocks can be combined to form a  $256\times32$  block; two  $512\times8$  RAM blocks can be combined to form a  $512\times16$  block (see Figure 6).

Figure 6. Examples of Combining FLEX 10KE EABs

If necessary, all EABs in a device can be cascaded to form a single RAM block. EABs can be cascaded to form RAM blocks of up to 2,048 words without impacting timing. The Altera software automatically combines EABs to meet a designer's RAM specifications.

#### Clearable Counter Mode

The clearable counter mode is similar to the up/down counter mode, but supports a synchronous clear instead of the up/down control. The clear function is substituted for the cascade-in signal in the up/down counter mode. Use 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. Synchronous loading is provided by a 2-to-1 multiplexer. The output of this multiplexer is ANDed with a synchronous clear signal.

### Internal Tri-State Emulation

Internal tri-state emulation provides internal tri-states without the limitations of a physical tri-state bus. In a physical tri-state bus, the tri-state buffers' output enable (OE) signals select which signal drives the bus. However, if multiple OE signals are active, contending signals can be driven onto the bus. Conversely, if no OE signals are active, the bus will float. Internal tri-state emulation resolves contending tri-state buffers to a low value and floating buses to a high value, thereby eliminating these problems. The Altera software automatically implements tri-state bus functionality with a multiplexer.

## Clear & Preset Logic Control

Logic for the programmable register's clear and preset functions is controlled by the DATA3, LABCTRL1, and LABCTRL2 inputs to the LE. The clear and preset control structure of the LE asynchronously loads signals into a register. Either LABCTRL1 or LABCTRL2 can control the asynchronous clear. Alternatively, the register can be set up so that LABCTRL1 implements an asynchronous load. The data to be loaded is driven to DATA3; when LABCTRL1 is asserted, DATA3 is loaded into the register.

During compilation, the Altera Compiler automatically selects the best control signal implementation. Because the clear and preset functions are active-low, the Compiler automatically assigns a logic high to an unused clear or preset.

The clear and preset logic is implemented in one of the following six modes chosen during design entry:

- Asynchronous clear

- Asynchronous preset

- Asynchronous clear and preset

- Asynchronous load with clear

- Asynchronous load with preset

- Asynchronous load without clear or preset

When dedicated inputs drive non-inverted and inverted peripheral clears, clock enables, and output enables, two signals on the peripheral control bus will be used.

Tables 8 and 9 list the sources for each peripheral control signal, and show how the output enable, clock enable, clock, and clear signals share 12 peripheral control signals. The tables also show the rows that can drive global signals.

| Peripheral<br>Control Signal | EPF10K30E | EPF10K50E<br>EPF10K50S |

|------------------------------|-----------|------------------------|

| OE0                          | Row A     | Row A                  |

| OE1                          | Row B     | Row B                  |

| OE2                          | Row C     | Row D                  |

| OE3                          | Row D     | Row F                  |

| OE4                          | Row E     | Row H                  |

| OE5                          | Row F     | Row J                  |

| CLKENA0/CLK0/GLOBAL0         | Row A     | Row A                  |

| CLKENA1/OE6/GLOBAL1          | Row B     | Row C                  |

| CLKENA2/CLR0                 | Row C     | Row E                  |

| CLKENA3/OE7/GLOBAL2          | Row D     | Row G                  |

| CLKENA4/CLR1                 | Row E     | Row I                  |

| CLKENA5/CLK1/GLOBAL3         | Row F     | Row J                  |

| Peripheral<br>Control Signal | EPF10K100E | EPF10K130E | EPF10K200E<br>EPF10K200S |

|------------------------------|------------|------------|--------------------------|

| OE0                          | Row A      | Row C      | Row G                    |

| OE1                          | Row C      | Row E      | Row I                    |

| OE2                          | Row E      | Row G      | Row K                    |

| OE3                          | Row L      | Row N      | Row R                    |

| OE4                          | Row I      | Row K      | Row O                    |

| OE5                          | Row K      | Row M      | Row Q                    |

| CLKENA0/CLK0/GLOBAL0         | Row F      | Row H      | Row L                    |

| CLKENA1/OE6/GLOBAL1          | Row D      | Row F      | Row J                    |

| CLKENA2/CLR0                 | Row B      | Row D      | Row H                    |

| CLKENA3/OE7/GLOBAL2          | Row H      | Row J      | Row N                    |

| CLKENA4/CLR1                 | Row J      | Row L      | Row P                    |

| CLKENA5/CLK1/GLOBAL3         | Row G      | Row I      | Row M                    |

Signals on the peripheral control bus can also drive the four global signals, referred to as <code>GLOBALO</code> through <code>GLOBALO</code> in Tables 8 and 9. An internally generated signal can drive a global signal, providing the same low-skew, low-delay characteristics as a signal driven by an input pin. An LE drives the global signal by driving a row line that drives the peripheral bus, which then drives the global signal. This feature is ideal for internally generated clear or clock signals with high fan-out. However, internally driven global signals offer no advantage over the general-purpose interconnect for routing data signals. The dedicated input pin should be driven to a known logic state (such as ground) and not be allowed to float.

The chip-wide output enable pin is an active-high pin ( $DEV_OE$ ) that can be used to tri-state all pins on the device. This option can be set in the Altera software. On EPF10K50E and EPF10K200E devices, the built-in I/O pin pull-up resistors (which are active during configuration) are active when the chip-wide output enable pin is asserted. The registers in the IOE can also be reset by the chip-wide reset pin.

## ClockLock & ClockBoost Features

To support high-speed designs, FLEX 10KE devices offer optional ClockLock and ClockBoost circuitry containing a phase-locked loop (PLL) used to increase design speed and reduce resource usage. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by resource sharing within the device. The ClockBoost feature allows the designer to distribute a low-speed clock and multiply that clock on-device. Combined, the ClockLock and ClockBoost features provide significant improvements in system performance and bandwidth.

All FLEX 10KE devices, except EPF10K50E and EPF10K200E devices, support ClockLock and ClockBoost circuitry. EPF10K50S and EPF10K200S devices support this circuitry. Devices that support ClockLock and ClockBoost circuitry are distinguished with an "X" suffix in the ordering code; for instance, the EPF10K200SFC672-1X device supports this circuit.

The ClockLock and ClockBoost features in FLEX 10KE devices are enabled through the Altera software. External devices are not required to use these features. The output of the ClockLock and ClockBoost circuits is not available at any of the device pins.

The ClockLock and ClockBoost circuitry locks onto the rising edge of the incoming clock. The circuit output can drive the clock inputs of registers only; the generated clock cannot be gated or inverted.

The dedicated clock pin (GCLK1) supplies the clock to the ClockLock and ClockBoost circuitry. When the dedicated clock pin is driving the ClockLock or ClockBoost circuitry, it cannot drive elsewhere in the device.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to the GCLK1 pin. In the Altera software, the GCLK1 pin can feed both the ClockLock and ClockBoost circuitry in the FLEX 10KE device. However, when both circuits are used, the other clock pin cannot be used.

| Table 17. 32-            | Bit IDCOD           | E for FLEX 10KE Devices | Note (1)                          |                  |  |  |  |  |

|--------------------------|---------------------|-------------------------|-----------------------------------|------------------|--|--|--|--|

| Device                   |                     | IDCODE (32 Bits)        |                                   |                  |  |  |  |  |

|                          | Version<br>(4 Bits) | Part Number (16 Bits)   | Manufacturer's Identity (11 Bits) | 1 (1 Bit)<br>(2) |  |  |  |  |

| EPF10K30E                | 0001                | 0001 0000 0011 0000     | 00001101110                       | 1                |  |  |  |  |

| EPF10K50E<br>EPF10K50S   | 0001                | 0001 0000 0101 0000     | 00001101110                       | 1                |  |  |  |  |

| EPF10K100E               | 0010                | 0000 0001 0000 0000     | 00001101110                       | 1                |  |  |  |  |

| EPF10K130E               | 0001                | 0000 0001 0011 0000     | 00001101110                       | 1                |  |  |  |  |

| EPF10K200E<br>EPF10K200S | 0001                | 0000 0010 0000 0000     | 00001101110                       | 1                |  |  |  |  |

#### Notes:

- (1) The most significant bit (MSB) is on the left.

- (2) The least significant bit (LSB) for all JTAG IDCODEs is 1.

FLEX 10KE devices include weak pull-up resistors on the JTAG pins.

For more information, see the following documents:

- Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- BitBlaster Serial Download Cable Data Sheet

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- Jam Programming & Test Language Specification

| Symbol            | Parameter                                   | Conditions                                                                          | Min                              | Тур | Max                                 | Unit |

|-------------------|---------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------|-----|-------------------------------------|------|

| V <sub>IH</sub>   | High-level input voltage                    |                                                                                     | 1.7, 0.5 × V <sub>CCIO</sub> (8) |     | 5.75                                | V    |

| V <sub>IL</sub>   | Low-level input voltage                     |                                                                                     | -0.5                             |     | 0.8,<br>0.3 × V <sub>CCIO</sub> (8) | V    |

| V <sub>OH</sub>   | 3.3-V high-level TTL output voltage         | $I_{OH} = -8 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ V } (9)$                    | 2.4                              |     |                                     | V    |

|                   | 3.3-V high-level CMOS output voltage        | $I_{OH} = -0.1 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ V } (9)$                  | V <sub>CCIO</sub> – 0.2          |     |                                     | V    |

|                   | 3.3-V high-level PCI output voltage         | $I_{OH} = -0.5 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{ V } (9)$ | 0.9 × V <sub>CCIO</sub>          |     |                                     | V    |

|                   | 2.5-V high-level output voltage             | $I_{OH} = -0.1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (9)$                  | 2.1                              |     |                                     | V    |

|                   |                                             | $I_{OH} = -1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (9)$                    | 2.0                              |     |                                     | V    |

|                   |                                             | $I_{OH} = -2 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (9)$                    | 1.7                              |     |                                     | V    |

| V <sub>OL</sub>   | 3.3-V low-level TTL output voltage          | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (10)                      |                                  |     | 0.45                                | V    |

|                   | 3.3-V low-level CMOS output voltage         | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (10)                     |                                  |     | 0.2                                 | V    |

|                   | 3.3-V low-level PCI output voltage          | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>(10)          |                                  |     | 0.1 × V <sub>CCIO</sub>             | V    |

|                   | 2.5-V low-level output voltage              | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                     |                                  |     | 0.2                                 | V    |

|                   |                                             | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                       |                                  |     | 0.4                                 | V    |

|                   |                                             | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                       |                                  |     | 0.7                                 | V    |

| I <sub>I</sub>    | Input pin leakage current                   | $V_I = V_{CCIOmax}$ to 0 V (11)                                                     | -10                              |     | 10                                  | μA   |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current          | $V_O = V_{CCIOmax}$ to 0 V (11)                                                     | -10                              |     | 10                                  | μA   |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current (standby)    | V <sub>I</sub> = ground, no load, no toggling inputs                                |                                  | 5   |                                     | mA   |

|                   |                                             | V <sub>I</sub> = ground, no load, no toggling inputs (12)                           |                                  | 10  |                                     | mA   |

| R <sub>CONF</sub> | Value of I/O pin pull-                      | V <sub>CCIO</sub> = 3.0 V (13)                                                      | 20                               |     | 50                                  | k¾   |

|                   | up resistor before and during configuration | V <sub>CCIO</sub> = 2.3 V (13)                                                      | 30                               |     | 80                                  | k¾   |

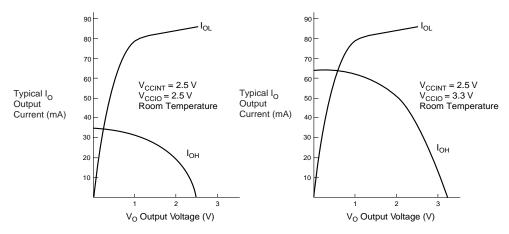

Figure 23. Output Drive Characteristics of FLEX 10KE Devices Note (1)

#### Note:

These are transient (AC) currents.

## **Timing Model**

The continuous, high-performance FastTrack Interconnect routing resources ensure predictable performance and accurate simulation and timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

Device performance can be estimated by following the signal path from a source, through the interconnect, to the destination. For example, the registered performance between two LEs on the same row can be calculated by adding the following parameters:

- LE register clock-to-output delay ( $t_{CO}$ )

- Interconnect delay ( $t_{SAMEROW}$ )

- LE look-up table delay  $(t_{LUT})$

- LE register setup time  $(t_{SI})$

The routing delay depends on the placement of the source and destination LEs. A more complex registered path may involve multiple combinatorial LEs between the source and destination LEs.

Timing simulation and delay prediction are available with the Altera Simulator and Timing Analyzer, or with industry-standard EDA tools. The Simulator offers both pre-synthesis functional simulation to evaluate logic design accuracy and post-synthesis timing simulation with 0.1-ns resolution. The Timing Analyzer provides point-to-point timing delay information, setup and hold time analysis, and device-wide performance analysis.

Figure 24 shows the overall timing model, which maps the possible paths to and from the various elements of the FLEX 10KE device.

Dedicated Clock/Input

Interconnect

Logic Embedded Array Block

Figures 25 through 28 show the delays that correspond to various paths and functions within the LE, IOE, EAB, and bidirectional timing models.

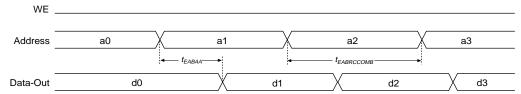

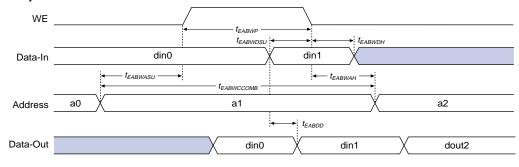

Figures 29 and 30 show the asynchronous and synchronous timing waveforms, respectively, or the EAB macroparameters in Tables 26 and 27.

Figure 29. EAB Asynchronous Timing Waveforms

## **EAB Asynchronous Read**

## **EAB Asynchronous Write**

| Table 38. EPF10K | 50E Device | LE Timing M | licroparame | ters (Part 2 | of 2) No | te (1)  |      |

|------------------|------------|-------------|-------------|--------------|----------|---------|------|

| Symbol           | -1 Spee    | d Grade     | -2 Spee     | d Grade      | -3 Spee  | d Grade | Unit |

|                  | Min        | Max         | Min         | Max          | Min      | Max     |      |

| $t_H$            | 0.9        |             | 1.0         |              | 1.4      |         | ns   |

| t <sub>PRE</sub> |            | 0.5         |             | 0.6          |          | 0.8     | ns   |

| t <sub>CLR</sub> |            | 0.5         |             | 0.6          |          | 0.8     | ns   |

| t <sub>CH</sub>  | 2.0        |             | 2.5         |              | 3.0      |         | ns   |

| $t_{CL}$         | 2.0        |             | 2.5         |              | 3.0      |         | ns   |

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | ed Grade | Unit |

|---------------------|----------------|-----|----------------|-----|---------|----------|------|

|                     | Min            | Max | Min            | Max | Min     | Max      |      |

| $t_{IOD}$           |                | 2.2 |                | 2.4 |         | 3.3      | ns   |

| t <sub>IOC</sub>    |                | 0.3 |                | 0.3 |         | 0.5      | ns   |

| t <sub>IOCO</sub>   |                | 1.0 |                | 1.0 |         | 1.4      | ns   |

| $t_{IOCOMB}$        |                | 0.0 |                | 0.0 |         | 0.2      | ns   |

| t <sub>IOSU</sub>   | 1.0            |     | 1.2            |     | 1.7     |          | ns   |

| $t_{IOH}$           | 0.3            |     | 0.3            |     | 0.5     |          | ns   |

| $t_{IOCLR}$         |                | 0.9 |                | 1.0 |         | 1.4      | ns   |

| $t_{OD1}$           |                | 0.8 |                | 0.9 |         | 1.2      | ns   |

| $t_{OD2}$           |                | 0.3 |                | 0.4 |         | 0.7      | ns   |

| t <sub>OD3</sub>    |                | 3.0 |                | 3.5 |         | 3.5      | ns   |

| $t_{XZ}$            |                | 1.4 |                | 1.7 |         | 2.3      | ns   |

| $t_{ZX1}$           |                | 1.4 |                | 1.7 |         | 2.3      | ns   |

| $t_{ZX2}$           |                | 0.9 |                | 1.2 |         | 1.8      | ns   |

| t <sub>ZX3</sub>    |                | 3.6 |                | 4.3 |         | 4.6      | ns   |

| t <sub>INREG</sub>  |                | 4.9 |                | 5.8 |         | 7.8      | ns   |

| t <sub>IOFD</sub>   |                | 2.8 |                | 3.3 |         | 4.5      | ns   |

| t <sub>INCOMB</sub> |                | 2.8 |                | 3.3 |         | 4.5      | ns   |

| Table 50. EPF10        | K100E Extern   | al Timing P | arameters | Notes (1),     | (2) |          |      |

|------------------------|----------------|-------------|-----------|----------------|-----|----------|------|

| Symbol                 | -1 Speed Grade |             | -2 Spee   | -2 Speed Grade |     | ed Grade | Unit |

|                        | Min            | Max         | Min       | Max            | Min | Max      | ]    |

| t <sub>DRR</sub>       |                | 9.0         |           | 12.0           |     | 16.0     | ns   |

| t <sub>INSU</sub> (3)  | 2.0            |             | 2.5       |                | 3.3 |          | ns   |

| t <sub>INH</sub> (3)   | 0.0            |             | 0.0       |                | 0.0 |          | ns   |

| t <sub>outco</sub> (3) | 2.0            | 5.2         | 2.0       | 6.9            | 2.0 | 9.1      | ns   |

| t <sub>INSU</sub> (4)  | 2.0            |             | 2.2       |                | -   |          | ns   |

| t <sub>INH</sub> (4)   | 0.0            |             | 0.0       |                | -   |          | ns   |

| t <sub>OUTCO</sub> (4) | 0.5            | 3.0         | 0.5       | 4.6            | -   | -        | ns   |

| t <sub>PCISU</sub>     | 3.0            |             | 6.2       |                | -   |          | ns   |

| t <sub>PCIH</sub>      | 0.0            |             | 0.0       |                | _   |          | ns   |

| t <sub>PCICO</sub>     | 2.0            | 6.0         | 2.0       | 6.9            | _   | _        | ns   |

| Table 51. EPF10K           | K100E External Bidirectional Timing Parameters Notes (1), (2) |     |         |                |     |          |      |

|----------------------------|---------------------------------------------------------------|-----|---------|----------------|-----|----------|------|

| Symbol                     | -1 Speed Grade                                                |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|                            | Min                                                           | Max | Min     | Max            | Min | Max      |      |

| t <sub>INSUBIDIR</sub> (3) | 1.7                                                           |     | 2.5     |                | 3.3 |          | ns   |

| t <sub>INHBIDIR</sub> (3)  | 0.0                                                           |     | 0.0     |                | 0.0 |          | ns   |

| t <sub>INSUBIDIR</sub> (4) | 2.0                                                           |     | 2.8     |                | _   |          | ns   |

| t <sub>INHBIDIR</sub> (4)  | 0.0                                                           |     | 0.0     |                | _   |          | ns   |

| toutcobidir (3)            | 2.0                                                           | 5.2 | 2.0     | 6.9            | 2.0 | 9.1      | ns   |

| t <sub>XZBIDIR</sub> (3)   |                                                               | 5.6 |         | 7.5            |     | 10.1     | ns   |

| t <sub>ZXBIDIR</sub> (3)   |                                                               | 5.6 |         | 7.5            |     | 10.1     | ns   |

| toutcobidir (4)            | 0.5                                                           | 3.0 | 0.5     | 4.6            | _   | -        | ns   |

| t <sub>XZBIDIR</sub> (4)   |                                                               | 4.6 |         | 6.5            |     | -        | ns   |

| t <sub>ZXBIDIR</sub> (4)   |                                                               | 4.6 |         | 6.5            |     | _        | ns   |

## Notes to tables:

- (1) All timing parameters are described in Tables 24 through 30 in this data sheet.

- (2) These parameters are specified by characterization.

- (3) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

- (4) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

| Symbol                  | -1 Spee | ed Grade | -2 Spee | ed Grade | -3 Spee | ed Grade | Unit |

|-------------------------|---------|----------|---------|----------|---------|----------|------|

|                         | Min     | Max      | Min     | Max      | Min     | Max      |      |

| t <sub>DIN2IOE</sub>    |         | 2.8      |         | 3.5      |         | 4.4      | ns   |

| t <sub>DIN2LE</sub>     |         | 0.7      |         | 1.2      |         | 1.6      | ns   |

| t <sub>DIN2DATA</sub>   |         | 1.6      |         | 1.9      |         | 2.2      | ns   |

| t <sub>DCLK2IOE</sub>   |         | 1.6      |         | 2.1      |         | 2.7      | ns   |

| t <sub>DCLK2LE</sub>    |         | 0.7      |         | 1.2      |         | 1.6      | ns   |

| t <sub>SAMELAB</sub>    |         | 0.1      |         | 0.2      |         | 0.2      | ns   |

| t <sub>SAMEROW</sub>    |         | 1.9      |         | 3.4      |         | 5.1      | ns   |

| t <sub>SAMECOLUMN</sub> |         | 0.9      |         | 2.6      |         | 4.4      | ns   |

| t <sub>DIFFROW</sub>    |         | 2.8      |         | 6.0      |         | 9.5      | ns   |

| t <sub>TWOROWS</sub>    |         | 4.7      |         | 9.4      |         | 14.6     | ns   |

| t <sub>LEPERIPH</sub>   |         | 3.1      |         | 4.7      |         | 6.9      | ns   |

| t <sub>LABCARRY</sub>   |         | 0.6      |         | 0.8      |         | 1.0      | ns   |

| t <sub>LABCASC</sub>    |         | 0.9      |         | 1.2      |         | 1.6      | ns   |

| Table 57. EPF10K       | 130E Extern    | al Timing Pa | arameters | Notes (1),     | (2) |         |      |  |

|------------------------|----------------|--------------|-----------|----------------|-----|---------|------|--|

| Symbol                 | -1 Speed Grade |              | -2 Spee   | -2 Speed Grade |     | d Grade | Unit |  |

|                        | Min            | Max          | Min       | Max            | Min | Max     |      |  |

| t <sub>DRR</sub>       |                | 9.0          |           | 12.0           |     | 16.0    | ns   |  |

| t <sub>INSU</sub> (3)  | 1.9            |              | 2.1       |                | 3.0 |         | ns   |  |

| t <sub>INH</sub> (3)   | 0.0            |              | 0.0       |                | 0.0 |         | ns   |  |

| t <sub>оитсо</sub> (3) | 2.0            | 5.0          | 2.0       | 7.0            | 2.0 | 9.2     | ns   |  |

| t <sub>INSU</sub> (4)  | 0.9            |              | 1.1       |                | -   |         | ns   |  |

| t <sub>INH</sub> (4)   | 0.0            |              | 0.0       |                | -   |         | ns   |  |

| t <sub>OUTCO</sub> (4) | 0.5            | 4.0          | 0.5       | 6.0            | -   | -       | ns   |  |

| t <sub>PCISU</sub>     | 3.0            |              | 6.2       |                | -   |         | ns   |  |

| t <sub>PCIH</sub>      | 0.0            |              | 0.0       |                | -   |         | ns   |  |

| t <sub>PCICO</sub>     | 2.0            | 6.0          | 2.0       | 6.9            | _   | _       | ns   |  |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABDATA1</sub>  |                | 2.0 |                | 2.4 |                | 3.2 | ns   |

| t <sub>EABDATA1</sub>  |                | 0.4 |                | 0.5 |                | 0.6 | ns   |

| EABWE1                 |                | 1.4 |                | 1.7 |                | 2.3 | ns   |

| t <sub>EABWE2</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABRE1</sub>    |                | 0   |                | 0   |                | 0   | ns   |

| t <sub>EABRE2</sub>    |                | 0.4 |                | 0.5 |                | 0.6 | ns   |

| t <sub>EABCLK</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABCO</sub>     |                | 0.8 |                | 0.9 |                | 1.2 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.0 |                | 0.1 |                | 0.1 | ns   |

| t <sub>EABSU</sub>     | 0.9            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>EABH</sub>      | 0.4            |     | 0.5            |     | 0.6            |     | ns   |

| t <sub>EABCLR</sub>    | 0.8            |     | 0.9            |     | 1.2            |     | ns   |

| t <sub>AA</sub>        |                | 3.1 |                | 3.7 |                | 4.9 | ns   |

| $t_{WP}$               | 3.3            |     | 4.0            |     | 5.3            |     | ns   |

| $t_{RP}$               | 0.9            |     | 1.1            |     | 1.5            |     | ns   |

| twosu                  | 0.9            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>WDH</sub>       | 0.1            |     | 0.1            |     | 0.1            |     | ns   |

| <sup>t</sup> wasu      | 1.3            |     | 1.6            |     | 2.1            |     | ns   |

| t <sub>WAH</sub>       | 2.1            |     | 2.5            |     | 3.3            |     | ns   |

| t <sub>RASU</sub>      | 2.2            |     | 2.6            |     | 3.5            |     | ns   |

| $t_{RAH}$              | 0.1            |     | 0.1            |     | 0.2            |     | ns   |

| t <sub>wo</sub>        |                | 2.0 |                | 2.4 |                | 3.2 | ns   |

| t <sub>DD</sub>        |                | 2.0 |                | 2.4 |                | 3.2 | ns   |

| t <sub>EABOUT</sub>    |                | 0.0 |                | 0.1 |                | 0.1 | ns   |

| t <sub>EABCH</sub>     | 1.5            |     | 2.0            |     | 2.5            |     | ns   |

| EABCL                  | 3.3            |     | 4.0            |     | 5.3            |     | ns   |

| Table 62. EPF10K      | 200E Device    | EAB Interna | al Timing Ma   | acroparame | ters (Part 1   | <b>of 2)</b> No | te (1) |

|-----------------------|----------------|-------------|----------------|------------|----------------|-----------------|--------|

| Symbol                | -1 Speed Grade |             | -2 Speed Grade |            | -3 Speed Grade |                 | Unit   |

|                       | Min            | Max         | Min            | Max        | Min            | Max             |        |

| t <sub>EABAA</sub>    |                | 5.1         |                | 6.4        |                | 8.4             | ns     |

| t <sub>EABRCOMB</sub> | 5.1            |             | 6.4            |            | 8.4            |                 | ns     |

| t <sub>EABRCREG</sub> | 4.8            |             | 5.7            |            | 7.6            |                 | ns     |

| t <sub>EABWP</sub>    | 3.3            |             | 4.0            |            | 5.3            |                 | ns     |

| Table 73. EPF10I    | K200S Devic    | e Internal & | External Tii   | ming Parame | eters N        | ote (1) |      |

|---------------------|----------------|--------------|----------------|-------------|----------------|---------|------|

| Symbol              | -1 Speed Grade |              | -2 Speed Grade |             | -3 Speed Grade |         | Unit |

|                     | Min            | Max          | Min            | Max         | Min            | Max     |      |

| $t_{LUT}$           |                | 0.7          |                | 0.8         |                | 1.2     | ns   |

| t <sub>CLUT</sub>   |                | 0.4          |                | 0.5         |                | 0.6     | ns   |

| $t_{RLUT}$          |                | 0.5          |                | 0.7         |                | 0.9     | ns   |

| t <sub>PACKED</sub> |                | 0.4          |                | 0.5         |                | 0.7     | ns   |

| $t_{EN}$            |                | 0.6          |                | 0.5         |                | 0.6     | ns   |

| $t_{CICO}$          |                | 0.1          |                | 0.2         |                | 0.3     | ns   |

| t <sub>CGEN</sub>   |                | 0.3          |                | 0.4         |                | 0.6     | ns   |

| $t_{CGENR}$         |                | 0.1          |                | 0.2         |                | 0.3     | ns   |

| $t_{CASC}$          |                | 0.7          |                | 0.8         |                | 1.2     | ns   |

| $t_{\mathbb{C}}$    |                | 0.5          |                | 0.6         |                | 0.8     | ns   |

| $t_{\rm CO}$        |                | 0.5          |                | 0.6         |                | 0.8     | ns   |

| t <sub>COMB</sub>   |                | 0.3          |                | 0.6         |                | 0.8     | ns   |

| $t_{SU}$            | 0.4            |              | 0.6            |             | 0.7            |         | ns   |

| t <sub>H</sub>      | 1.0            |              | 1.1            |             | 1.5            |         | ns   |

| t <sub>PRE</sub>    |                | 0.4          |                | 0.6         |                | 0.8     | ns   |

| $t_{CLR}$           |                | 0.5          |                | 0.6         |                | 0.8     | ns   |

| t <sub>CH</sub>     | 2.0            |              | 2.5            |             | 3.0            |         | ns   |

| $t_{CL}$            | 2.0            |              | 2.5            |             | 3.0            |         | ns   |

| Table 74. EPF10K200S Device IOE Timing Microparameters (Part 1 of 2) Note (1) |                |     |                |     |                |     |      |

|-------------------------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|

| Symbol                                                                        | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|                                                                               | Min            | Max | Min            | Max | Min            | Max |      |

| $t_{IOD}$                                                                     |                | 1.8 |                | 1.9 |                | 2.6 | ns   |

| t <sub>IOC</sub>                                                              |                | 0.3 |                | 0.3 |                | 0.5 | ns   |

| t <sub>IOCO</sub>                                                             |                | 1.7 |                | 1.9 |                | 2.6 | ns   |

| t <sub>IOCOMB</sub>                                                           |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| t <sub>IOSU</sub>                                                             | 0.8            |     | 0.9            |     | 1.2            |     | ns   |

| t <sub>IOH</sub>                                                              | 0.4            |     | 0.8            |     | 1.1            |     | ns   |

| t <sub>IOCLR</sub>                                                            |                | 0.2 |                | 0.2 |                | 0.3 | ns   |

| t <sub>OD1</sub>                                                              |                | 1.3 |                | 0.7 |                | 0.9 | ns   |

| t <sub>OD2</sub>                                                              |                | 0.8 |                | 0.2 |                | 0.4 | ns   |

| t <sub>OD3</sub>                                                              |                | 2.9 |                | 3.0 |                | 3.9 | ns   |

| $t_{XZ}$                                                                      |                | 5.0 |                | 5.3 |                | 7.1 | ns   |

| t <sub>ZX1</sub>                                                              |                | 5.0 |                | 5.3 |                | 7.1 | ns   |

| Table 74. EPF10k    | 200S Device    | e IOE Timing | Microparar     | neters (Par | t 2 of 2)      | Note (1) |      |

|---------------------|----------------|--------------|----------------|-------------|----------------|----------|------|

| Symbol              | -1 Speed Grade |              | -2 Speed Grade |             | -3 Speed Grade |          | Unit |

|                     | Min            | Max          | Min            | Max         | Min            | Max      |      |

| $t_{ZX2}$           |                | 4.5          |                | 4.8         |                | 6.6      | ns   |

| $t_{ZX3}$           |                | 6.6          |                | 7.6         |                | 10.1     | ns   |

| t <sub>INREG</sub>  |                | 3.7          |                | 5.7         |                | 7.7      | ns   |

| t <sub>IOFD</sub>   |                | 1.8          |                | 3.4         |                | 4.0      | ns   |

| t <sub>INCOMB</sub> |                | 1.8          |                | 3.4         |                | 4.0      | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABDATA1</sub>  |                | 1.8 |                | 2.4 |                | 3.2 | ns   |

| t <sub>EABDATA1</sub>  |                | 0.4 |                | 0.5 |                | 0.6 | ns   |

| t <sub>EABWE1</sub>    |                | 1.1 |                | 1.7 |                | 2.3 | ns   |

| t <sub>EABWE2</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABRE1</sub>    |                | 0   |                | 0   |                | 0   | ns   |

| t <sub>EABRE2</sub>    |                | 0.4 |                | 0.5 |                | 0.6 | ns   |

| t <sub>EABCLK</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABCO</sub>     |                | 0.8 |                | 0.9 |                | 1.2 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.0 |                | 0.1 |                | 0.1 | ns   |

| t <sub>EABSU</sub>     | 0.7            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>EABH</sub>      | 0.4            |     | 0.5            |     | 0.6            |     | ns   |

| t <sub>EABCLR</sub>    | 0.8            |     | 0.9            |     | 1.2            |     | ns   |

| t <sub>AA</sub>        |                | 2.1 |                | 3.7 |                | 4.9 | ns   |

| t <sub>WP</sub>        | 2.1            |     | 4.0            |     | 5.3            |     | ns   |

| t <sub>RP</sub>        | 1.1            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>WDSU</sub>      | 0.5            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>WDH</sub>       | 0.1            |     | 0.1            |     | 0.1            |     | ns   |

| t <sub>WASU</sub>      | 1.1            |     | 1.6            |     | 2.1            |     | ns   |

| t <sub>WAH</sub>       | 1.6            |     | 2.5            |     | 3.3            |     | ns   |

| t <sub>RASU</sub>      | 1.6            |     | 2.6            |     | 3.5            |     | ns   |

| t <sub>RAH</sub>       | 0.1            |     | 0.1            |     | 0.2            |     | ns   |

| t <sub>wo</sub>        |                | 2.0 |                | 2.4 |                | 3.2 | ns   |

| t <sub>DD</sub>        |                | 2.0 |                | 2.4 |                | 3.2 | ns   |

| t <sub>EABOUT</sub>    |                | 0.0 |                | 0.1 |                | 0.1 | ns   |

| t <sub>EABCH</sub>     | 1.5            |     | 2.0            |     | 2.5            |     | ns   |

| t <sub>EABCL</sub>     | 2.1            |     | 2.8            |     | 3.8            |     | ns   |

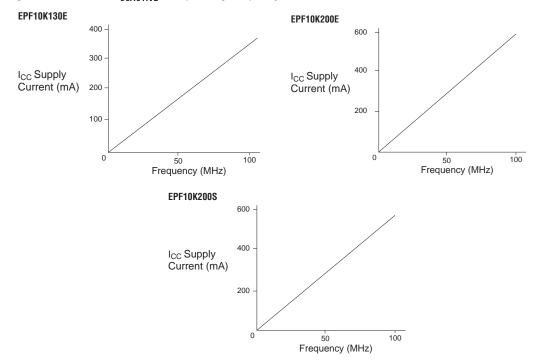

Figure 31. FLEX 10KE I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 2 of 2)

# Configuration & Operation

The FLEX 10KE architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

## **Operating Modes**

The FLEX 10KE architecture uses SRAM configuration elements that require configuration data to be loaded every time the circuit powers up. The process of physically loading the SRAM data into the device is called *configuration*. Before configuration, as  $V_{CC}$  rises, the device initiates a Power-On Reset (POR). This POR event clears the device and prepares it for configuration. The FLEX 10KE POR time does not exceed 50  $\mu s$ .

When configuring with a configuration device, refer to the respective configuration device data sheet for POR timing information.

During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.

SRAM configuration elements allow FLEX 10KE devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming user-mode operation. The entire reconfiguration process requires less than 85 ms and can be used to reconfigure an entire system dynamically. In-field upgrades can be performed by distributing new configuration files.

Before and during configuration, all I/O pins (except dedicated inputs, clock, or configuration pins) are pulled high by a weak pull-up resistor.

## **Programming Files**

Despite being function- and pin-compatible, FLEX 10KE devices are not programming- or configuration file-compatible with FLEX 10K or FLEX 10KA devices. A design therefore must be recompiled before it is transferred from a FLEX 10K or FLEX 10KA device to an equivalent FLEX 10KE device. This recompilation should be performed both to create a new programming or configuration file and to check design timing in FLEX 10KE devices, which has different timing characteristics than FLEX 10K or FLEX 10KA devices.

FLEX 10KE devices are generally pin-compatible with equivalent FLEX 10KA devices. In some cases, FLEX 10KE devices have fewer I/O pins than the equivalent FLEX 10KA devices. Table 81 shows which FLEX 10KE devices have fewer I/O pins than equivalent FLEX 10KA devices. However, power, ground, JTAG, and configuration pins are the same on FLEX 10KA and FLEX 10KE devices, enabling migration from a FLEX 10KA design to a FLEX 10KE design.