# E·XFI

# Altera - EPF10K50SQC240-2X Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Det | ta | i | S |

|-----|----|---|---|

|     |    |   |   |

| Detalls                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Active                                                         |

| Number of LABs/CLBs            | 360                                                            |

| Number of Logic Elements/Cells |                                                                |

| Total RAM Bits                 | - ·                                                            |

| Number of I/O                  | 189                                                            |

| Number of Gates                | - ·                                                            |

| Voltage - Supply               | 2.375V ~ 2.625V                                                |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                |

| Package / Case                 | 240-BFQFP                                                      |

| Supplier Device Package        | 240-PQFP (32x32)                                               |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=epf10k50sqc240-2x |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

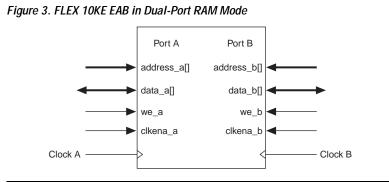

The EAB can also use Altera megafunctions to implement dual-port RAM applications where both ports can read or write, as shown in Figure 3.

The FLEX 10KE EAB can be used in a single-port mode, which is useful for backward-compatibility with FLEX 10K designs (see Figure 4).

Each LAB provides four control signals with programmable inversion that can be used in all eight LEs. Two of these signals can be used as clocks, the other two can be used for clear/preset control. The LAB clocks can be driven by the dedicated clock input pins, global signals, I/O signals, or internal signals via the LAB local interconnect. The LAB preset and clear control signals can be driven by the global signals, I/O signals, or internal signals via the LAB local interconnect. The global control signals are typically used for global clock, clear, or preset signals because they provide asynchronous control with very low skew across the device. If logic is required on a control signal, it can be generated in one or more LE in any LAB and driven into the local interconnect of the target LAB. In addition, the global control signals can be generated from LE outputs.

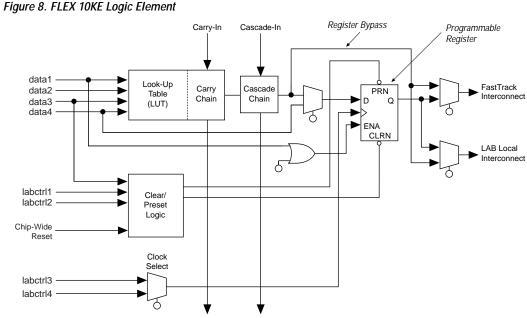

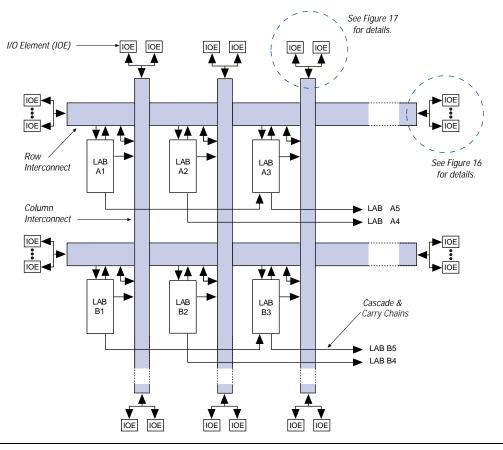

# Logic Element

The LE, the smallest unit of logic in the FLEX 10KE architecture, has a compact size that provides efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can quickly compute any function of four variables. In addition, each LE contains a programmable flipflop with a synchronous clock enable, a carry chain, and a cascade chain. Each LE drives both the local and the FastTrack Interconnect routing structure (see Figure 8).

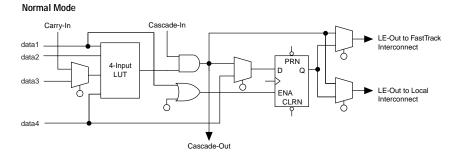

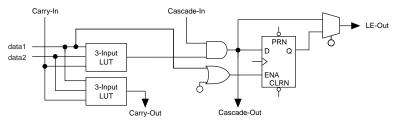

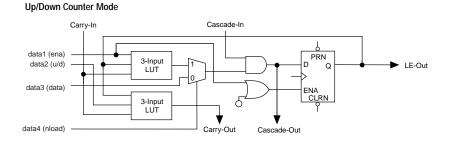

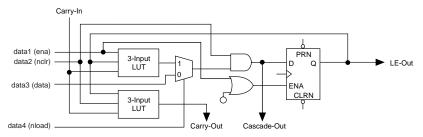

# Figure 11. FLEX 10KE LE Operating Modes

#### **Clearable Counter Mode**

#### Normal Mode

The normal mode is suitable for general logic applications and wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Altera Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. Either the register or the LUT can be used to drive both the local interconnect and the FastTrack Interconnect routing structure at the same time.

The LUT and the register in the LE can be used independently (register packing). To support register packing, the LE has two outputs; one drives the local interconnect, and the other drives the FastTrack Interconnect routing structure. The DATA4 signal can drive the register directly, allowing the LUT to compute a function that is independent of the registered signal; a three-input function can be computed in the LUT, and a fourth independent signal can be registered. Alternatively, a four-input function can be generated, and one of the inputs to this function can be used to drive the register. The register in a packed LE can still use the clock enable, clear, and preset signals in the LE. In a packed LE, the register can drive the FastTrack Interconnect routing structure while the LUT drives the local interconnect, or vice versa.

#### Arithmetic Mode

The arithmetic mode offers 2 three-input LUTs that are ideal for implementing adders, accumulators, and comparators. One LUT computes a three-input function; the other generates a carry output. As shown in Figure 11 on page 22, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, in an adder, this output is the sum of three signals: a, b, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain.

#### **Up/Down Counter Mode**

The up/down counter mode offers counter enable, clock enable, synchronous up/down control, and data loading options. These control signals are generated by the data inputs from the LAB local interconnect, the carry-in signal, and output feedback from the programmable register. Use 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading. Data can also be loaded asynchronously with the clear and preset register control signals without using the LUT resources.

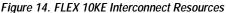

# I/O Element

An IOE contains a bidirectional I/O buffer and a register that can be used either as an input register for external data that requires a fast setup time, or as an output register for data that requires fast clock-to-output performance. In some cases, using an LE register for an input register will result in a faster setup time than using an IOE register. IOEs can be used as input, output, or bidirectional pins. For bidirectional registered I/O implementation, the output register should be in the IOE, and the data input and output enable registers should be LE registers placed adjacent to the bidirectional pin. The Altera Compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. Figure 15 shows the bidirectional I/O registers.

Figure 15. FLEX 10KE Bidirectional I/O Registers

#### Note:

(1) All FLEX 10KE devices (except the EPF10K50E and EPF10K200E devices) have a programmable input delay buffer on the input path.

#### **Altera Corporation**

| Peripheral<br>Control Signal | EPF10K100E | EPF10K130E | EPF10K200E<br>EPF10K200S |  |

|------------------------------|------------|------------|--------------------------|--|

| OE0                          | Row A      | Row C      | Row G                    |  |

| OE1                          | Row C      | Row E      | Row I                    |  |

| OE2                          | Row E      | Row G      | Row K                    |  |

| OE 3                         | Row L      | Row N      | Row R                    |  |

| OE4                          | Row I      | Row K      | Row O                    |  |

| OE5                          | Row K      | Row M      | Row Q                    |  |

| CLKENA0/CLK0/GLOBAL0         | Row F      | Row H      | Row L                    |  |

| CLKENA1/OE6/GLOBAL1          | Row D      | Row F      | Row J                    |  |

| CLKENA2/CLR0                 | Row B      | Row D      | Row H                    |  |

| CLKENA3/OE7/GLOBAL2          | Row H      | Row J      | Row N                    |  |

| CLKENA4/CLR1                 | Row J      | Row L      | Row P                    |  |

| CLKENA5/CLK1/GLOBAL3         | Row G      | Row I      | Row M                    |  |

Signals on the peripheral control bus can also drive the four global signals, referred to as GLOBAL0 through GLOBAL3 in Tables 8 and 9. An internally generated signal can drive a global signal, providing the same low-skew, low-delay characteristics as a signal driven by an input pin. An LE drives the global signal by driving a row line that drives the peripheral bus, which then drives the global signal. This feature is ideal for internally generated clear or clock signals with high fan-out. However, internally driven global signals offer no advantage over the general-purpose interconnect for routing data signals. The dedicated input pin should be driven to a known logic state (such as ground) and not be allowed to float.

The chip-wide output enable pin is an active-high pin (DEV\_OE) that can be used to tri-state all pins on the device. This option can be set in the Altera software. On EPF10K50E and EPF10K200E devices, the built-in I/O pin pull-up resistors (which are active during configuration) are active when the chip-wide output enable pin is asserted. The registers in the IOE can also be reset by the chip-wide reset pin.

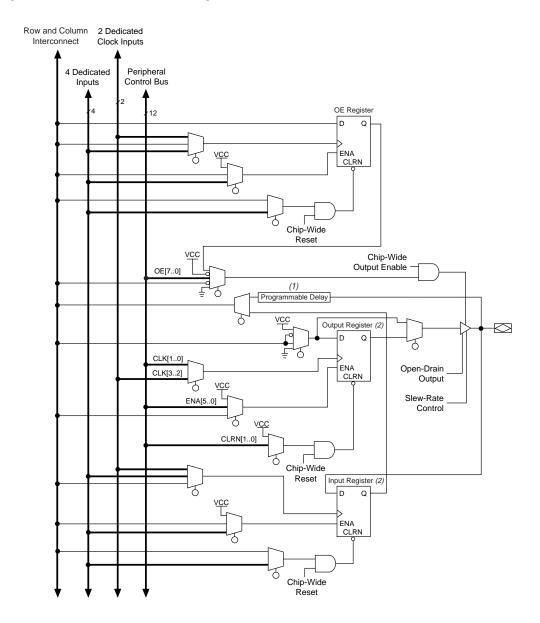

Row-to-IOE Connections

When an IOE is used as an input signal, it can drive two separate row channels. The signal is accessible by all LEs within that row. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the row channels. Up to eight IOEs connect to each side of each row channel (see Figure 16).

# Figure 16. FLEX 10KE Row-to-IOE Connections The values for m and n are provided in Table 10.

m loe1

| Table 10 lists the FLEX 10KE row-to-IOE interco | onnect resources. |

|-------------------------------------------------|-------------------|

|-------------------------------------------------|-------------------|

| Table 10. FLEX 10K | Table 10. FLEX 10KE Row-to-IOE Interconnect Resources |                          |  |  |  |  |  |  |  |

|--------------------|-------------------------------------------------------|--------------------------|--|--|--|--|--|--|--|

| Device             | Channels per Row (n)                                  | Row Channels per Pin (m) |  |  |  |  |  |  |  |

| EPF10K30E          | 216                                                   | 27                       |  |  |  |  |  |  |  |

| EPF10K50E          | 216                                                   | 27                       |  |  |  |  |  |  |  |

| EPF10K50S          |                                                       |                          |  |  |  |  |  |  |  |

| EPF10K100E         | 312                                                   | 39                       |  |  |  |  |  |  |  |

| EPF10K130E         | 312                                                   | 39                       |  |  |  |  |  |  |  |

| EPF10K200E         | 312                                                   | 39                       |  |  |  |  |  |  |  |

| EPF10K200S         |                                                       |                          |  |  |  |  |  |  |  |

$\bigcirc$

# ClockLock & ClockBoost Features

To support high-speed designs, FLEX 10KE devices offer optional ClockLock and ClockBoost circuitry containing a phase-locked loop (PLL) used to increase design speed and reduce resource usage. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by resource sharing within the device. The ClockBoost feature allows the designer to distribute a low-speed clock and multiply that clock on-device. Combined, the ClockLock and ClockBoost features provide significant improvements in system performance and bandwidth.

All FLEX 10KE devices, except EPF10K50E and EPF10K200E devices, support ClockLock and ClockBoost circuitry. EPF10K50S and EPF10K200S devices support this circuitry. Devices that support Clock-Lock and ClockBoost circuitry are distinguished with an "X" suffix in the ordering code; for instance, the EPF10K200SFC672-1X device supports this circuit.

The ClockLock and ClockBoost features in FLEX 10KE devices are enabled through the Altera software. External devices are not required to use these features. The output of the ClockLock and ClockBoost circuits is not available at any of the device pins.

The ClockLock and ClockBoost circuitry locks onto the rising edge of the incoming clock. The circuit output can drive the clock inputs of registers only; the generated clock cannot be gated or inverted.

The dedicated clock pin (GCLK1) supplies the clock to the ClockLock and ClockBoost circuitry. When the dedicated clock pin is driving the ClockLock or ClockBoost circuitry, it cannot drive elsewhere in the device.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to the GCLK1 pin. In the Altera software, the GCLK1 pin can feed both the ClockLock and ClockBoost circuitry in the FLEX 10KE device. However, when both circuits are used, the other clock pin cannot be used.

| Symbol             | -1 Spee | d Grade | -2 Speed Grade |     | -3 Spee | ed Grade | Unit |

|--------------------|---------|---------|----------------|-----|---------|----------|------|

|                    | Min     | Max     | Min            | Max | Min     | Max      |      |

| t <sub>CGENR</sub> |         | 0.1     |                | 0.1 |         | 0.2      | ns   |

| t <sub>CASC</sub>  |         | 0.6     |                | 0.8 |         | 1.0      | ns   |

| t <sub>C</sub>     |         | 0.0     |                | 0.0 |         | 0.0      | ns   |

| t <sub>CO</sub>    |         | 0.3     |                | 0.4 |         | 0.5      | ns   |

| t <sub>COMB</sub>  |         | 0.4     |                | 0.4 |         | 0.6      | ns   |

| t <sub>SU</sub>    | 0.4     |         | 0.6            |     | 0.6     |          | ns   |

| t <sub>H</sub>     | 0.7     |         | 1.0            |     | 1.3     |          | ns   |

| PRE                |         | 0.8     |                | 0.9 |         | 1.2      | ns   |

| t <sub>CLR</sub>   |         | 0.8     |                | 0.9 |         | 1.2      | ns   |

| сн                 | 2.0     |         | 2.5            |     | 2.5     |          | ns   |

| ĊL                 | 2.0     |         | 2.5            |     | 2.5     |          | ns   |

| Symbol              | -1 Spee | ed Grade | -2 Spee | d Grade | -3 Spee | ed Grade | Unit |

|---------------------|---------|----------|---------|---------|---------|----------|------|

|                     | Min     | Max      | Min     | Max     | Min     | Max      |      |

| t <sub>IOD</sub>    |         | 2.4      |         | 2.8     |         | 3.8      | ns   |

| t <sub>IOC</sub>    |         | 0.3      |         | 0.4     |         | 0.5      | ns   |

| t <sub>IOCO</sub>   |         | 1.0      |         | 1.1     |         | 1.6      | ns   |

| t <sub>IOCOMB</sub> |         | 0.0      |         | 0.0     |         | 0.0      | ns   |

| t <sub>IOSU</sub>   | 1.2     |          | 1.4     |         | 1.9     |          | ns   |

| t <sub>IOH</sub>    | 0.3     |          | 0.4     |         | 0.5     |          | ns   |

| t <sub>IOCLR</sub>  |         | 1.0      |         | 1.1     |         | 1.6      | ns   |

| t <sub>OD1</sub>    |         | 1.9      |         | 2.3     |         | 3.0      | ns   |

| t <sub>OD2</sub>    |         | 1.4      |         | 1.8     |         | 2.5      | ns   |

| t <sub>OD3</sub>    |         | 4.4      |         | 5.2     |         | 7.0      | ns   |

| t <sub>XZ</sub>     |         | 2.7      |         | 3.1     |         | 4.3      | ns   |

| t <sub>ZX1</sub>    |         | 2.7      |         | 3.1     |         | 4.3      | ns   |

| t <sub>ZX2</sub>    |         | 2.2      |         | 2.6     |         | 3.8      | ns   |

| t <sub>ZX3</sub>    |         | 5.2      |         | 6.0     |         | 8.3      | ns   |

| t <sub>INREG</sub>  |         | 3.4      |         | 4.1     |         | 5.5      | ns   |

| t <sub>IOFD</sub>   |         | 0.8      |         | 1.3     |         | 2.4      | ns   |

| t <sub>INCOMB</sub> |         | 0.8      |         | 1.3     |         | 2.4      | ns   |

| Symbol                  | -1 Spee | d Grade | -2 Speed Grade |     | -3 Spee | ed Grade | Unit |

|-------------------------|---------|---------|----------------|-----|---------|----------|------|

|                         | Min     | Max     | Min            | Max | Min     | Max      |      |

| t <sub>DIN2IOE</sub>    |         | 1.8     |                | 2.4 |         | 2.9      | ns   |

| t <sub>DIN2LE</sub>     |         | 1.5     |                | 1.8 |         | 2.4      | ns   |

| t <sub>DIN2DATA</sub>   |         | 1.5     |                | 1.8 |         | 2.2      | ns   |

| t <sub>DCLK2IOE</sub>   |         | 2.2     |                | 2.6 |         | 3.0      | ns   |

| t <sub>DCLK2LE</sub>    |         | 1.5     |                | 1.8 |         | 2.4      | ns   |

| t <sub>SAMELAB</sub>    |         | 0.1     |                | 0.2 |         | 0.3      | ns   |

| t <sub>SAMEROW</sub>    |         | 2.0     |                | 2.4 |         | 2.7      | ns   |

| t <sub>SAMECOLUMN</sub> |         | 0.7     |                | 1.0 |         | 0.8      | ns   |

| t <sub>DIFFROW</sub>    |         | 2.7     |                | 3.4 |         | 3.5      | ns   |

| t <sub>TWOROWS</sub>    |         | 4.7     |                | 5.8 |         | 6.2      | ns   |

| t <sub>LEPERIPH</sub>   |         | 2.7     |                | 3.4 |         | 3.8      | ns   |

| t <sub>LABCARRY</sub>   |         | 0.3     |                | 0.4 |         | 0.5      | ns   |

| t <sub>LABCASC</sub>    |         | 0.8     |                | 0.8 |         | 1.1      | ns   |

| Table 36. EPF10K30E External Timing Parameters       Notes (1), (2) |                |     |         |                |     |          |      |  |

|---------------------------------------------------------------------|----------------|-----|---------|----------------|-----|----------|------|--|

| Symbol                                                              | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |  |

|                                                                     | Min            | Max | Min     | Max            | Min | Max      |      |  |

| t <sub>DRR</sub>                                                    |                | 8.0 |         | 9.5            |     | 12.5     | ns   |  |

| t <sub>INSU</sub> (3)                                               | 2.1            |     | 2.5     |                | 3.9 |          | ns   |  |

| t <sub>INH</sub> (3)                                                | 0.0            |     | 0.0     |                | 0.0 |          | ns   |  |

| <b>t</b> оитсо (3)                                                  | 2.0            | 4.9 | 2.0     | 5.9            | 2.0 | 7.6      | ns   |  |

| t <sub>INSU</sub> (4)                                               | 1.1            |     | 1.5     |                | -   |          | ns   |  |

| t <sub>INH</sub> (4)                                                | 0.0            |     | 0.0     |                | -   |          | ns   |  |

| <b>t</b> оитсо (4)                                                  | 0.5            | 3.9 | 0.5     | 4.9            | -   | -        | ns   |  |

| t <sub>PCISU</sub>                                                  | 3.0            |     | 4.2     |                | -   |          | ns   |  |

| t <sub>PCIH</sub>                                                   | 0.0            |     | 0.0     |                | -   |          | ns   |  |

| t <sub>PCICO</sub>                                                  | 2.0            | 6.0 | 2.0     | 7.5            | -   | -        | ns   |  |

| Table 38. EPF10K | 50E Device | LE Timing N | licroparame | eters (Part 2 | ? of 2) No     | te (1) |      |

|------------------|------------|-------------|-------------|---------------|----------------|--------|------|

| Symbol           | -1 Spee    | d Grade     | -2 Spee     | d Grade       | -3 Speed Grade |        | Unit |

|                  | Min        | Max         | Min         | Max           | Min            | Max    |      |

| t <sub>H</sub>   | 0.9        |             | 1.0         |               | 1.4            |        | ns   |

| t <sub>PRE</sub> |            | 0.5         |             | 0.6           |                | 0.8    | ns   |

| t <sub>CLR</sub> |            | 0.5         |             | 0.6           |                | 0.8    | ns   |

| t <sub>CH</sub>  | 2.0        |             | 2.5         |               | 3.0            |        | ns   |

| t <sub>CL</sub>  | 2.0        |             | 2.5         |               | 3.0            |        | ns   |

| Table 39. EPF10     | 1              |     | -<br>I  |                | te (1) | i        |      |

|---------------------|----------------|-----|---------|----------------|--------|----------|------|

| Symbol              | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |        | ed Grade | Unit |

|                     | Min            | Max | Min     | Max            | Min    | Max      |      |

| t <sub>IOD</sub>    |                | 2.2 |         | 2.4            |        | 3.3      | ns   |

| t <sub>IOC</sub>    |                | 0.3 |         | 0.3            |        | 0.5      | ns   |

| t <sub>IOCO</sub>   |                | 1.0 |         | 1.0            |        | 1.4      | ns   |

| t <sub>IOCOMB</sub> |                | 0.0 |         | 0.0            |        | 0.2      | ns   |

| t <sub>IOSU</sub>   | 1.0            |     | 1.2     |                | 1.7    |          | ns   |

| t <sub>IOH</sub>    | 0.3            |     | 0.3     |                | 0.5    |          | ns   |

| t <sub>IOCLR</sub>  |                | 0.9 |         | 1.0            |        | 1.4      | ns   |

| t <sub>OD1</sub>    |                | 0.8 |         | 0.9            |        | 1.2      | ns   |

| t <sub>OD2</sub>    |                | 0.3 |         | 0.4            |        | 0.7      | ns   |

| t <sub>OD3</sub>    |                | 3.0 |         | 3.5            |        | 3.5      | ns   |

| t <sub>XZ</sub>     |                | 1.4 |         | 1.7            |        | 2.3      | ns   |

| t <sub>ZX1</sub>    |                | 1.4 |         | 1.7            |        | 2.3      | ns   |

| t <sub>ZX2</sub>    |                | 0.9 |         | 1.2            |        | 1.8      | ns   |

| t <sub>ZX3</sub>    |                | 3.6 |         | 4.3            |        | 4.6      | ns   |

| t <sub>INREG</sub>  |                | 4.9 |         | 5.8            |        | 7.8      | ns   |

| t <sub>IOFD</sub>   |                | 2.8 |         | 3.3            |        | 4.5      | ns   |

| t <sub>INCOMB</sub> |                | 2.8 |         | 3.3            |        | 4.5      | ns   |

| Symbol                 | -1 Spee | ed Grade | -2 Spee | -2 Speed Grade |     | d Grade | Unit |

|------------------------|---------|----------|---------|----------------|-----|---------|------|

|                        | Min     | Max      | Min     | Max            | Min | Max     |      |

| t <sub>DRR</sub>       |         | 9.0      |         | 12.0           |     | 16.0    | ns   |

| t <sub>INSU</sub> (3)  | 2.0     |          | 2.5     |                | 3.3 |         | ns   |

| t <sub>INH</sub> (3)   | 0.0     |          | 0.0     |                | 0.0 |         | ns   |

| t <sub>оитсо</sub> (3) | 2.0     | 5.2      | 2.0     | 6.9            | 2.0 | 9.1     | ns   |

| t <sub>INSU</sub> (4)  | 2.0     |          | 2.2     |                | -   |         | ns   |

| t <sub>INH</sub> (4)   | 0.0     |          | 0.0     |                | -   |         | ns   |

| t <sub>оитсо</sub> (4) | 0.5     | 3.0      | 0.5     | 4.6            | -   | -       | ns   |

| t <sub>PCISU</sub>     | 3.0     |          | 6.2     |                | -   |         | ns   |

| t <sub>PCIH</sub>      | 0.0     |          | 0.0     |                | -   |         | ns   |

| t <sub>PCICO</sub>     | 2.0     | 6.0      | 2.0     | 6.9            | -   | _       | ns   |

Table 51. EPF10K100E External Bidirectional Timing Parameters

Notes (1), (2)

| Symbol                     | -1 Spee | ed Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|----------------------------|---------|----------|---------|---------|---------|---------|------|

|                            | Min     | Max      | Min     | Max     | Min     | Max     |      |

| t <sub>INSUBIDIR</sub> (3) | 1.7     |          | 2.5     |         | 3.3     |         | ns   |

| t <sub>inhbidir</sub> (3)  | 0.0     |          | 0.0     |         | 0.0     |         | ns   |

| t <sub>INSUBIDIR</sub> (4) | 2.0     |          | 2.8     |         | -       |         | ns   |

| t <sub>INHBIDIR</sub> (4)  | 0.0     |          | 0.0     |         | -       |         | ns   |

| toutcobidir (3)            | 2.0     | 5.2      | 2.0     | 6.9     | 2.0     | 9.1     | ns   |

| t <sub>XZBIDIR</sub> (3)   |         | 5.6      |         | 7.5     |         | 10.1    | ns   |

| t <sub>ZXBIDIR</sub> (3)   |         | 5.6      |         | 7.5     |         | 10.1    | ns   |

| toutcobidir (4)            | 0.5     | 3.0      | 0.5     | 4.6     | -       | -       | ns   |

| t <sub>XZBIDIR</sub> (4)   |         | 4.6      |         | 6.5     |         | -       | ns   |

| t <sub>ZXBIDIR</sub> (4)   |         | 4.6      |         | 6.5     |         | -       | ns   |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) These parameters are specified by characterization.

(3) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

(4) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

| Table 54. EPF10K130E Device EAB Internal Microparameters (Part 2 of 2)       Note (1) |         |         |         |         |         |         |      |  |  |

|---------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|------|--|--|

| Symbol                                                                                | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |  |  |

|                                                                                       | Min     | Max     | Min     | Max     | Min     | Max     |      |  |  |

| t <sub>DD</sub>                                                                       |         | 1.5     |         | 2.0     |         | 2.6     | ns   |  |  |

| t <sub>EABOUT</sub>                                                                   |         | 0.2     |         | 0.3     |         | 0.3     | ns   |  |  |

| t <sub>EABCH</sub>                                                                    | 1.5     |         | 2.0     |         | 2.5     |         | ns   |  |  |

| t <sub>EABCL</sub>                                                                    | 2.7     |         | 3.5     |         | 4.7     |         | ns   |  |  |

| Table 55. EPF10K130E Device EAB Internal Timing Macroparameters       Note (1) |         |         |         |          |         |          |      |  |

|--------------------------------------------------------------------------------|---------|---------|---------|----------|---------|----------|------|--|

| Symbol                                                                         | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | ed Grade | Unit |  |

|                                                                                | Min     | Max     | Min     | Max      | Min     | Max      |      |  |

| t <sub>EABAA</sub>                                                             |         | 5.9     |         | 7.5      |         | 9.9      | ns   |  |

| t <sub>EABRCOMB</sub>                                                          | 5.9     |         | 7.5     |          | 9.9     |          | ns   |  |

| t <sub>EABRCREG</sub>                                                          | 5.1     |         | 6.4     |          | 8.5     |          | ns   |  |

| t <sub>EABWP</sub>                                                             | 2.7     |         | 3.5     |          | 4.7     |          | ns   |  |

| t <sub>EABWCOMB</sub>                                                          | 5.9     |         | 7.7     |          | 10.3    |          | ns   |  |

| t <sub>EABWCREG</sub>                                                          | 5.4     |         | 7.0     |          | 9.4     |          | ns   |  |

| t <sub>EABDD</sub>                                                             |         | 3.4     |         | 4.5      |         | 5.9      | ns   |  |

| t <sub>EABDATACO</sub>                                                         |         | 0.5     |         | 0.7      |         | 0.8      | ns   |  |

| t <sub>EABDATASU</sub>                                                         | 0.8     |         | 1.0     |          | 1.4     |          | ns   |  |

| t <sub>EABDATAH</sub>                                                          | 0.1     |         | 0.1     |          | 0.2     |          | ns   |  |

| t <sub>EABWESU</sub>                                                           | 1.1     |         | 1.4     |          | 1.9     |          | ns   |  |

| t <sub>EABWEH</sub>                                                            | 0.0     |         | 0.0     |          | 0.0     |          | ns   |  |

| t <sub>EABWDSU</sub>                                                           | 1.0     |         | 1.3     |          | 1.7     |          | ns   |  |

| t <sub>EABWDH</sub>                                                            | 0.2     |         | 0.2     |          | 0.3     |          | ns   |  |

| t <sub>EABWASU</sub>                                                           | 4.1     |         | 5.1     |          | 6.8     |          | ns   |  |

| t <sub>EABWAH</sub>                                                            | 0.0     |         | 0.0     |          | 0.0     |          | ns   |  |

| t <sub>EABWO</sub>                                                             |         | 3.4     |         | 4.5      |         | 5.9      | ns   |  |

| Symbol             | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|--------------------|----------------|------|----------------|------|----------------|------|------|

|                    | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>DRR</sub>   |                | 10.0 |                | 12.0 |                | 16.0 | ns   |

| t <sub>INSU</sub>  | 2.8            |      | 3.4            |      | 4.4            |      | ns   |

| t <sub>INH</sub>   | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>оuтco</sub> | 2.0            | 4.5  | 2.0            | 5.3  | 2.0            | 7.8  | ns   |

| t <sub>PCISU</sub> | 3.0            |      | 6.2            |      | -              |      | ns   |

| t <sub>PCIH</sub>  | 0.0            |      | 0.0            |      | -              |      | ns   |

| t <sub>PCICO</sub> | 2.0            | 6.0  | 2.0            | 8.9  | -              | -    | ns   |

Table 65. EPF10K200E External Bidirectional Timing Parameters Notes (1), (2)

| Symbol                  | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|-------------------------|---------|---------|---------|---------|---------|---------|------|

|                         | Min     | Max     | Min     | Max     | Min     | Max     |      |

| t <sub>INSUBIDIR</sub>  | 3.0     |         | 4.0     |         | 5.5     |         | ns   |

| t <sub>INHBIDIR</sub>   | 0.0     |         | 0.0     |         | 0.0     |         | ns   |

| t <sub>OUTCOBIDIR</sub> | 2.0     | 4.5     | 2.0     | 5.3     | 2.0     | 7.8     | ns   |

| t <sub>XZBIDIR</sub>    |         | 8.1     |         | 9.5     |         | 13.0    | ns   |

| t <sub>ZXBIDIR</sub>    |         | 8.1     |         | 9.5     |         | 13.0    | ns   |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) These parameters are specified by characterization.

Tables 66 through 79 show EPF10K50S and EPF10K200S device external timing parameters.

| Table 66. EPF10K50S Device LE Timing Microparameters (Part 1 of 2)       Note (1) |                |     |                |     |                |     |      |  |  |

|-----------------------------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|--|

| Symbol                                                                            | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |  |

|                                                                                   | Min            | Max | Min            | Max | Min            | Max |      |  |  |

| t <sub>LUT</sub>                                                                  |                | 0.6 |                | 0.8 |                | 1.1 | ns   |  |  |

| t <sub>CLUT</sub>                                                                 |                | 0.5 |                | 0.6 |                | 0.8 | ns   |  |  |

| t <sub>RLUT</sub>                                                                 |                | 0.6 |                | 0.7 |                | 0.9 | ns   |  |  |

| t <sub>PACKED</sub>                                                               |                | 0.2 |                | 0.3 |                | 0.4 | ns   |  |  |

| t <sub>EN</sub>                                                                   |                | 0.6 |                | 0.7 |                | 0.9 | ns   |  |  |

| t <sub>CICO</sub>                                                                 |                | 0.1 |                | 0.1 |                | 0.1 | ns   |  |  |

| t <sub>CGEN</sub>                                                                 |                | 0.4 |                | 0.5 |                | 0.6 | ns   |  |  |

| Symbol                       | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|------------------------------|----------------|-----|---------|----------------|-----|----------|------|

|                              | Min            | Max | Min     | Max            | Min | Max      |      |

| t <sub>DRR</sub>             |                | 8.0 |         | 9.5            |     | 12.5     | ns   |

| t <sub>INSU</sub> (2)        | 2.4            |     | 2.9     |                | 3.9 |          | ns   |

| t <sub>INH</sub> (2)         | 0.0            |     | 0.0     |                | 0.0 |          | ns   |

| t <sub>оитсо</sub> (2)       | 2.0            | 4.3 | 2.0     | 5.2            | 2.0 | 7.3      | ns   |

| t <sub>INSU</sub> (3)        | 2.4            |     | 2.9     |                |     |          | ns   |

| t <sub>INH</sub> (3)         | 0.0            |     | 0.0     |                |     |          | ns   |

| <b>t<sub>оитсо (3)</sub></b> | 0.5            | 3.3 | 0.5     | 4.1            |     |          | ns   |

| t <sub>PCISU</sub>           | 2.4            |     | 2.9     |                | -   |          | ns   |

| t <sub>PCIH</sub>            | 0.0            |     | 0.0     |                | -   |          | ns   |

| t <sub>PCICO</sub>           | 2.0            | 6.0 | 2.0     | 7.7            | -   | -        | ns   |

Table 72. EPF10K50S External Bidirectional Timing Parameters

Note (1)

| Symbol                     | -1 Spee | ed Grade | -2 Spee | ed Grade | -3 Spee | ed Grade | Unit |

|----------------------------|---------|----------|---------|----------|---------|----------|------|

|                            | Min     | Мах      | Min     | Max      | Min     | Max      |      |

| t <sub>INSUBIDIR</sub> (2) | 2.7     |          | 3.2     |          | 4.3     |          | ns   |

| t <sub>INHBIDIR</sub> (2)  | 0.0     |          | 0.0     |          | 0.0     |          | ns   |

| t <sub>inhbidir</sub> (3)  | 0.0     |          | 0.0     |          | -       |          | ns   |

| t <sub>insubidir</sub> (3) | 3.7     |          | 4.2     |          | -       |          | ns   |

| toutcobidir (2)            | 2.0     | 4.5      | 2.0     | 5.2      | 2.0     | 7.3      | ns   |

| t <sub>XZBIDIR</sub> (2)   |         | 6.8      |         | 7.8      |         | 10.1     | ns   |

| t <sub>ZXBIDIR</sub> (2)   |         | 6.8      |         | 7.8      |         | 10.1     | ns   |

| toutcobidir (3)            | 0.5     | 3.5      | 0.5     | 4.2      | -       | -        |      |

| t <sub>XZBIDIR</sub> (3)   |         | 6.8      |         | 8.4      |         | -        | ns   |

| t <sub>ZXBIDIR</sub> (3)   |         | 6.8      |         | 8.4      |         | -        | ns   |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30.

(2) This parameter is measured without use of the ClockLock or ClockBoost circuits.

(3) This parameter is measured with use of the ClockLock or ClockBoost circuits

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | d Grade | Unit |

|---------------------|----------------|-----|----------------|-----|---------|---------|------|

|                     | Min            | Max | Min            | Max | Min     | Max     |      |

| t <sub>LUT</sub>    |                | 0.7 |                | 0.8 |         | 1.2     | ns   |

| t <sub>CLUT</sub>   |                | 0.4 |                | 0.5 |         | 0.6     | ns   |

| t <sub>RLUT</sub>   |                | 0.5 |                | 0.7 |         | 0.9     | ns   |

| t <sub>PACKED</sub> |                | 0.4 |                | 0.5 |         | 0.7     | ns   |

| t <sub>EN</sub>     |                | 0.6 |                | 0.5 |         | 0.6     | ns   |

| tcico               |                | 0.1 |                | 0.2 |         | 0.3     | ns   |

| tCGEN               |                | 0.3 |                | 0.4 |         | 0.6     | ns   |

| t <sub>CGENR</sub>  |                | 0.1 |                | 0.2 |         | 0.3     | ns   |

| t <sub>CASC</sub>   |                | 0.7 |                | 0.8 |         | 1.2     | ns   |

| t <sub>C</sub>      |                | 0.5 |                | 0.6 |         | 0.8     | ns   |

| <sup>t</sup> co     |                | 0.5 |                | 0.6 |         | 0.8     | ns   |

| t <sub>COMB</sub>   |                | 0.3 |                | 0.6 |         | 0.8     | ns   |

| t <sub>SU</sub>     | 0.4            |     | 0.6            |     | 0.7     |         | ns   |

| tн                  | 1.0            |     | 1.1            |     | 1.5     |         | ns   |

| t <sub>PRE</sub>    |                | 0.4 |                | 0.6 |         | 0.8     | ns   |

| t <sub>CLR</sub>    |                | 0.5 |                | 0.6 |         | 0.8     | ns   |

| <sup>t</sup> CH     | 2.0            |     | 2.5            |     | 3.0     |         | ns   |

| ĊL                  | 2.0            |     | 2.5            |     | 3.0     |         | ns   |

Table 74. EPF10K200S Device IOE Timing Microparameters (Part 1 of 2)

Note (1)

| Symbol              | -1 Spee | ed Grade | -2 Spee | ed Grade | -3 Spee | ed Grade | Unit |

|---------------------|---------|----------|---------|----------|---------|----------|------|

|                     | Min     | Max      | Min     | Мах      | Min     | Max      |      |

| t <sub>IOD</sub>    |         | 1.8      |         | 1.9      |         | 2.6      | ns   |

| t <sub>IOC</sub>    |         | 0.3      |         | 0.3      |         | 0.5      | ns   |

| t <sub>IOCO</sub>   |         | 1.7      |         | 1.9      |         | 2.6      | ns   |

| t <sub>IOCOMB</sub> |         | 0.5      |         | 0.6      |         | 0.8      | ns   |

| t <sub>IOSU</sub>   | 0.8     |          | 0.9     |          | 1.2     |          | ns   |

| t <sub>IOH</sub>    | 0.4     |          | 0.8     |          | 1.1     |          | ns   |

| t <sub>IOCLR</sub>  |         | 0.2      |         | 0.2      |         | 0.3      | ns   |

| t <sub>OD1</sub>    |         | 1.3      |         | 0.7      |         | 0.9      | ns   |

| t <sub>OD2</sub>    |         | 0.8      |         | 0.2      |         | 0.4      | ns   |

| t <sub>OD3</sub>    |         | 2.9      |         | 3.0      |         | 3.9      | ns   |

| t <sub>XZ</sub>     |         | 5.0      |         | 5.3      |         | 7.1      | ns   |

| t <sub>ZX1</sub>    |         | 5.0      |         | 5.3      |         | 7.1      | ns   |

| Power<br>Consumption | The supply power (P) for FLEX 10KE de following equation:                                                                                                                                                                                                                 | vices can be calculated with the                                                                   |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| oonoumption          | $P = P_{INT} + P_{IO} = (I_{CCSTANDBY} + I_{CCACTI})$                                                                                                                                                                                                                     | $_{\rm VE}$ ) $	imes$ V <sub>CC</sub> + P <sub>IO</sub>                                            |  |  |  |  |

|                      | The $I_{CCACTIVE}$ value depends on the sw<br>application logic. This value is calculated<br>that each LE typically consumes. The $P_{II}$<br>device output load characteristics and so<br>calculated using the guidelines given in<br><i>Power for Altera Devices</i> ). | d based on the amount of current $_{\rm D}$ value, which depends on the witching frequency, can be |  |  |  |  |

|                      | Compared to the rest of the device, the embedded array consumes a negligible amount of power. Therefore, the embedded array can be ignored when calculating supply current.                                                                                               |                                                                                                    |  |  |  |  |

|                      | The I <sub>CCACTIVE</sub> value can be calculated v                                                                                                                                                                                                                       | vith the following equation:                                                                       |  |  |  |  |

|                      | $I_{CCACTIVE} = K \times \mathbf{f}_{MAX} \times N \times \mathbf{tog}_{LC} \times \frac{\mu A}{MHz \times LE}$                                                                                                                                                           |                                                                                                    |  |  |  |  |

|                      | Where:                                                                                                                                                                                                                                                                    |                                                                                                    |  |  |  |  |

|                      |                                                                                                                                                                                                                                                                           |                                                                                                    |  |  |  |  |

|                      | Table 80 provides the constant (K) value                                                                                                                                                                                                                                  | S for FLEX TUKE devices.                                                                           |  |  |  |  |

|                      | Table 80. FLEX 10KE K Constant Values                                                                                                                                                                                                                                     |                                                                                                    |  |  |  |  |

|                      | Device                                                                                                                                                                                                                                                                    | K Value                                                                                            |  |  |  |  |

|                      | EPF10K30E                                                                                                                                                                                                                                                                 | 4.5                                                                                                |  |  |  |  |

|                      | EPF10K50E                                                                                                                                                                                                                                                                 | 4.8                                                                                                |  |  |  |  |

|                      | EPF10K50S                                                                                                                                                                                                                                                                 | 4.5                                                                                                |  |  |  |  |

|                      | EPF10K100E                                                                                                                                                                                                                                                                | 4.5                                                                                                |  |  |  |  |

|                      | EPF10K130E                                                                                                                                                                                                                                                                | 4.6                                                                                                |  |  |  |  |

|                      | EPF10K200E                                                                                                                                                                                                                                                                | 4.8                                                                                                |  |  |  |  |

EPF10K200S

This calculation provides an  $I_{CC}$  estimate based on typical conditions with no output load. The actual  $I_{CC}$  should be verified during operation because this measurement is sensitive to the actual pattern in the device and the environmental operating conditions.

4.6

Additionally, the Altera software offers several features that help plan for future device migration by preventing the use of conflicting I/O pins.

| Table 81. I/O Counts | for FLEX 10KA & | FLEX 10KE Devices |           |  |  |

|----------------------|-----------------|-------------------|-----------|--|--|

| FLEX 10              | KA              | FLEX 10KE         |           |  |  |

| Device               | I/O Count       | Device            | I/O Count |  |  |

| EPF10K30AF256        | 191             | EPF10K30EF256     | 176       |  |  |

| EPF10K30AF484        | 246             | EPF10K30EF484     | 220       |  |  |

| EPF10K50VB356        | 274             | EPF10K50SB356     | 220       |  |  |

| EPF10K50VF484        | 291             | EPF10K50EF484     | 254       |  |  |

| EPF10K50VF484        | 291             | EPF10K50SF484     | 254       |  |  |

| EPF10K100AF484       | 369             | EPF10K100EF484    | 338       |  |  |

**Configuration Schemes**

The configuration data for a FLEX 10KE device can be loaded with one of five configuration schemes (see Table 82), chosen on the basis of the target application. An EPC1, EPC2, or EPC16 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of a FLEX 10KE device, allowing automatic configuration on system power-up.

Multiple FLEX 10KE devices can be configured in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device. Additional FLEX 10K, FLEX 10KA, FLEX 10KE, and FLEX 6000 devices can be configured in the same serial chain.

| Table 82. Data Sources for FLEX 10KE Configuration |                                                                                                     |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Configuration Scheme                               | Data Source                                                                                         |

| Configuration device                               | EPC1, EPC2, or EPC16 configuration device                                                           |

| Passive serial (PS)                                | BitBlaster, ByteBlasterMV, or MasterBlaster download cables, or serial data source                  |

| Passive parallel asynchronous (PPA)                | Parallel data source                                                                                |

| Passive parallel synchronous (PPS)                 | Parallel data source                                                                                |

| JTAG                                               | BitBlaster or ByteBlasterMV download cables, or<br>microprocessor with a Jam STAPL file or JBC file |

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: lit\_reg@altera.com Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending

applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Altera Corporation

100