Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 360                                                         |

| Number of Logic Elements/Cells | 2880                                                        |

| Total RAM Bits                 | 40960                                                       |

| Number of I/O                  | 189                                                         |

| Number of Gates                | 199000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                             |

| Package / Case                 | 240-BFQFP                                                   |

| Supplier Device Package        | 240-PQFP (32x32)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k50sqc240-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Figure 1 shows a block diagram of the FLEX 10KE architecture. Each group of LEs is combined into an LAB; groups of LABs are arranged into rows and columns. Each row also contains a single EAB. The LABs and EABs are interconnected by the FastTrack Interconnect routing structure. IOEs are located at the end of each row and column of the FastTrack Interconnect routing structure.

Embedded Array Block (EAB) I/O Element IOE IOE IOE IOE IOE IOE IOE IOE IOE (IOE) IOE Column Logic Array Interconnect EAB Logic Array Block (LAB) IOE Logic Element (LE) Row EAB Interconnect Local Interconnect Logic Array

Figure 1. FLEX 10KE Device Block Diagram

IOE

IOE

IOE

IOE

IOE

IOE

Embedded Array

FLEX 10KE devices provide six dedicated inputs that drive the flipflops' control inputs and ensure the efficient distribution of high-speed, low-skew (less than 1.5 ns) control signals. These signals use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect routing structure. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device.

IOE

IOE

| Peripheral<br>Control Signal | EPF10K100E | EPF10K130E | EPF10K200E<br>EPF10K200S |

|------------------------------|------------|------------|--------------------------|

| OE0                          | Row A      | Row C      | Row G                    |

| OE1                          | Row C      | Row E      | Row I                    |

| OE2                          | Row E      | Row G      | Row K                    |

| OE3                          | Row L      | Row N      | Row R                    |

| OE4                          | Row I      | Row K      | Row O                    |

| OE5                          | Row K      | Row M      | Row Q                    |

| CLKENA0/CLK0/GLOBAL0         | Row F      | Row H      | Row L                    |

| CLKENA1/OE6/GLOBAL1          | Row D      | Row F      | Row J                    |

| CLKENA2/CLR0                 | Row B      | Row D      | Row H                    |

| CLKENA3/OE7/GLOBAL2          | Row H      | Row J      | Row N                    |

| CLKENA4/CLR1                 | Row J      | Row L      | Row P                    |

| CLKENA5/CLK1/GLOBAL3         | Row G      | Row I      | Row M                    |

Signals on the peripheral control bus can also drive the four global signals, referred to as <code>GLOBALO</code> through <code>GLOBALO</code> in Tables 8 and 9. An internally generated signal can drive a global signal, providing the same low-skew, low-delay characteristics as a signal driven by an input pin. An LE drives the global signal by driving a row line that drives the peripheral bus, which then drives the global signal. This feature is ideal for internally generated clear or clock signals with high fan-out. However, internally driven global signals offer no advantage over the general-purpose interconnect for routing data signals. The dedicated input pin should be driven to a known logic state (such as ground) and not be allowed to float.

The chip-wide output enable pin is an active-high pin ( $DEV_OE$ ) that can be used to tri-state all pins on the device. This option can be set in the Altera software. On EPF10K50E and EPF10K200E devices, the built-in I/O pin pull-up resistors (which are active during configuration) are active when the chip-wide output enable pin is asserted. The registers in the IOE can also be reset by the chip-wide reset pin.

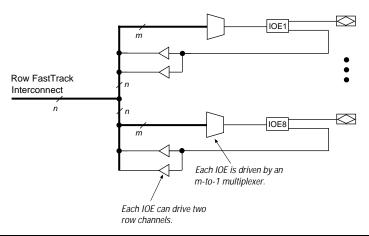

#### Row-to-IOE Connections

When an IOE is used as an input signal, it can drive two separate row channels. The signal is accessible by all LEs within that row. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the row channels. Up to eight IOEs connect to each side of each row channel (see Figure 16).

Figure 16. FLEX 10KE Row-to-IOE Connections

The values for m and n are provided in Table 10.

Table 10 lists the FLEX 10KE row-to-IOE interconnect resources.

| Table 10. FLEX 10Ki      | Table 10. FLEX 10KE Row-to-IOE Interconnect Resources |                          |  |  |  |  |  |

|--------------------------|-------------------------------------------------------|--------------------------|--|--|--|--|--|

| Device                   | Channels per Row (n)                                  | Row Channels per Pin (m) |  |  |  |  |  |

| EPF10K30E                | 216                                                   | 27                       |  |  |  |  |  |

| EPF10K50E<br>EPF10K50S   | 216                                                   | 27                       |  |  |  |  |  |

| EPF10K100E               | 312                                                   | 39                       |  |  |  |  |  |

| EPF10K130E               | 312                                                   | 39                       |  |  |  |  |  |

| EPF10K200E<br>EPF10K200S | 312                                                   | 39                       |  |  |  |  |  |

## ClockLock & ClockBoost Features

To support high-speed designs, FLEX 10KE devices offer optional ClockLock and ClockBoost circuitry containing a phase-locked loop (PLL) used to increase design speed and reduce resource usage. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by resource sharing within the device. The ClockBoost feature allows the designer to distribute a low-speed clock and multiply that clock on-device. Combined, the ClockLock and ClockBoost features provide significant improvements in system performance and bandwidth.

All FLEX 10KE devices, except EPF10K50E and EPF10K200E devices, support ClockLock and ClockBoost circuitry. EPF10K50S and EPF10K200S devices support this circuitry. Devices that support ClockLock and ClockBoost circuitry are distinguished with an "X" suffix in the ordering code; for instance, the EPF10K200SFC672-1X device supports this circuit.

The ClockLock and ClockBoost features in FLEX 10KE devices are enabled through the Altera software. External devices are not required to use these features. The output of the ClockLock and ClockBoost circuits is not available at any of the device pins.

The ClockLock and ClockBoost circuitry locks onto the rising edge of the incoming clock. The circuit output can drive the clock inputs of registers only; the generated clock cannot be gated or inverted.

The dedicated clock pin (GCLK1) supplies the clock to the ClockLock and ClockBoost circuitry. When the dedicated clock pin is driving the ClockLock or ClockBoost circuitry, it cannot drive elsewhere in the device.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to the GCLK1 pin. In the Altera software, the GCLK1 pin can feed both the ClockLock and ClockBoost circuitry in the FLEX 10KE device. However, when both circuits are used, the other clock pin cannot be used.

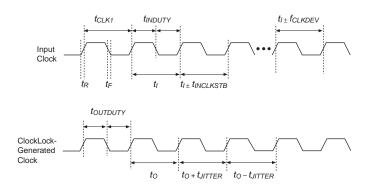

### ClockLock & ClockBoost Timing Parameters

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. Figure 19 shows the incoming and generated clock specifications.

Figure 19. Specifications for Incoming & Generated Clocks

The  $t_l$  parameter refers to the nominal input clock period; the  $t_0$  parameter refers to the nominal output clock period.

## IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All FLEX 10KE devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. FLEX 10KE devices can also be configured using the JTAG pins through the BitBlaster or ByteBlasterMV download cable, or via hardware that uses the Jam<sup>TM</sup> STAPL programming and test language. JTAG boundary-scan testing can be performed before or after configuration, but not during configuration. FLEX 10KE devices support the JTAG instructions shown in Table 15.

| Table 15. FLEX 10KE | TTAG Instructions                                                                                                                                                                                                    |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction    | Description                                                                                                                                                                                                          |

| SAMPLE/PRELOAD      | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins.                                     |

| EXTEST              | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                               |

| BYPASS              | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through a selected device to adjacent devices during normal device operation.                         |

| USERCODE            | Selects the user electronic signature (USERCODE) register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                       |

| IDCODE              | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                |

| ICR Instructions    | These instructions are used when configuring a FLEX 10KE device via JTAG ports with a BitBlaster or ByteBlasterMV download cable, or using a Jam File (.jam) or Jam Byte-Code File (.jbc) via an embedded processor. |

The instruction register length of FLEX 10KE devices is 10 bits. The USERCODE register length in FLEX 10KE devices is 32 bits; 7 bits are determined by the user, and 25 bits are pre-determined. Tables 16 and 17 show the boundary-scan register length and device IDCODE information for FLEX 10KE devices.

| Table 16. FLEX 10KE Boundary- | Table 16. FLEX 10KE Boundary-Scan Register Length |  |  |  |  |

|-------------------------------|---------------------------------------------------|--|--|--|--|

| Device                        | Boundary-Scan Register Length                     |  |  |  |  |

| EPF10K30E                     | 690                                               |  |  |  |  |

| EPF10K50E<br>EPF10K50S        | 798                                               |  |  |  |  |

| EPF10K100E                    | 1,050                                             |  |  |  |  |

| EPF10K130E                    | 1,308                                             |  |  |  |  |

| EPF10K200E<br>EPF10K200S      | 1,446                                             |  |  |  |  |

to Be Driven

Figure 20. FLEX 10KE JTAG Waveforms TMS TDI t<sub>JPSU</sub> TCK t<sub>JPZX</sub> t <sub>JPXZ</sub>  $\mathbf{t}_{\mathsf{JPCO}}$ TDO t<sub>JSH</sub> t<sub>JSSU</sub> Signal to Be Captured t<sub>JSCO</sub>t<sub>JSZX</sub> t<sub>JSXZ</sub> Signal

Figure 20 shows the timing requirements for the JTAG signals.

Table 18 shows the timing parameters and values for FLEX 10KE devices.

| Table 1           | 8. FLEX 10KE JTAG Timing Parameters & Values   |     |     |      |

|-------------------|------------------------------------------------|-----|-----|------|

| Symbol            | Parameter                                      | Min | Max | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output |     | 35  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |

## **Generic Testing**

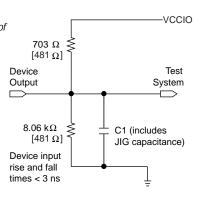

Each FLEX 10KE device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for FLEX 10KE devices are made under conditions equivalent to those shown in Figure 21. Multiple test patterns can be used to configure devices during all stages of the production flow.

Figure 21. FLEX 10KE AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast-groundcurrent transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result. Numbers in brackets are for 2.5-V devices or outputs. Numbers without brackets are for 3.3-V. devices or outputs.

## Operating Conditions

Tables 19 through 23 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 2.5-V FLEX 10KE devices.

| Symbol            | Parameter                  | Conditions                        | Min    | Max   | Unit  |

|-------------------|----------------------------|-----------------------------------|--------|-------|-------|

|                   | 1 di diffictor             | Conditions                        | 141111 | IVIGA | Oiiit |

| $V_{CCINT}$       | Supply voltage             | With respect to ground (2)        | -0.5   | 3.6   | V     |

| V <sub>CCIO</sub> |                            |                                   | -0.5   | 4.6   | V     |

| V <sub>I</sub>    | DC input voltage           |                                   | -2.0   | 5.75  | V     |

| I <sub>OUT</sub>  | DC output current, per pin |                                   | -25    | 25    | mA    |

| T <sub>STG</sub>  | Storage temperature        | No bias                           | -65    | 150   | ° C   |

| T <sub>AMB</sub>  | Ambient temperature        | Under bias                        | -65    | 135   | °C    |

| TJ                | Junction temperature       | PQFP, TQFP, BGA, and FineLine BGA |        | 135   | °C    |

|                   |                            | packages, under bias              |        |       |       |

|                   |                            | Ceramic PGA packages, under bias  |        | 150   | °C    |

| Symbol            | Parameter                                   | Conditions                                                                          | Min                              | Тур | Max                                 | Unit |

|-------------------|---------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------|-----|-------------------------------------|------|

| V <sub>IH</sub>   | High-level input voltage                    |                                                                                     | 1.7, 0.5 × V <sub>CCIO</sub> (8) |     | 5.75                                | V    |

| V <sub>IL</sub>   | Low-level input voltage                     |                                                                                     | -0.5                             |     | 0.8,<br>0.3 × V <sub>CCIO</sub> (8) | V    |

| V <sub>OH</sub>   | 3.3-V high-level TTL output voltage         | $I_{OH} = -8 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ V } (9)$                    | 2.4                              |     |                                     | V    |

|                   | 3.3-V high-level CMOS output voltage        | $I_{OH} = -0.1 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ V } (9)$                  | V <sub>CCIO</sub> – 0.2          |     |                                     | V    |

|                   | 3.3-V high-level PCI output voltage         | $I_{OH} = -0.5 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{ V } (9)$ | 0.9 × V <sub>CCIO</sub>          |     |                                     | V    |

|                   | 2.5-V high-level output voltage             | $I_{OH} = -0.1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (9)$                  | 2.1                              |     |                                     | V    |

|                   |                                             | $I_{OH} = -1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (9)$                    | 2.0                              |     |                                     | V    |

|                   |                                             | $I_{OH} = -2 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (9)$                    | 1.7                              |     |                                     | V    |

| V <sub>OL</sub>   | 3.3-V low-level TTL output voltage          | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (10)                      |                                  |     | 0.45                                | V    |

|                   | 3.3-V low-level CMOS output voltage         | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (10)                     |                                  |     | 0.2                                 | V    |

|                   | 3.3-V low-level PCI output voltage          | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>(10)          |                                  |     | 0.1 × V <sub>CCIO</sub>             | V    |

|                   | 2.5-V low-level output voltage              | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                     |                                  |     | 0.2                                 | V    |

|                   |                                             | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                       |                                  |     | 0.4                                 | V    |

|                   |                                             | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (10)                       |                                  |     | 0.7                                 | V    |

| I <sub>I</sub>    | Input pin leakage current                   | $V_I = V_{CCIOmax}$ to 0 V (11)                                                     | -10                              |     | 10                                  | μA   |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current          | $V_O = V_{CCIOmax}$ to 0 V (11)                                                     | -10                              |     | 10                                  | μA   |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current (standby)    | V <sub>I</sub> = ground, no load, no toggling inputs                                |                                  | 5   |                                     | mA   |

|                   |                                             | V <sub>I</sub> = ground, no load, no toggling inputs (12)                           |                                  | 10  |                                     | mA   |

| R <sub>CONF</sub> | Value of I/O pin pull-                      | V <sub>CCIO</sub> = 3.0 V (13)                                                      | 20                               |     | 50                                  | k¾   |

|                   | up resistor before and during configuration | V <sub>CCIO</sub> = 2.3 V (13)                                                      | 30                               |     | 80                                  | k¾   |

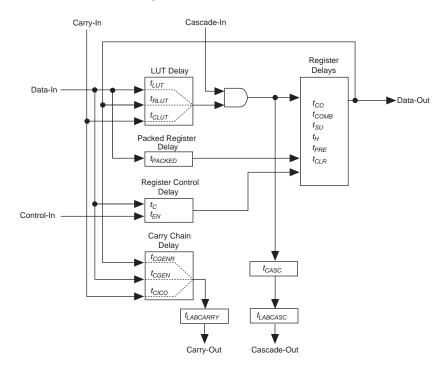

Figure 25. FLEX 10KE Device LE Timing Model

| Table 28. Inte           | rconnect Timing Microparameters Note (1)                                                                             |            |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------|

| Symbol                   | Parameter                                                                                                            | Conditions |

| t <sub>DIN2IOE</sub>     | Delay from dedicated input pin to IOE control input                                                                  | (7)        |

| t <sub>DIN2LE</sub>      | Delay from dedicated input pin to LE or EAB control input                                                            | (7)        |

| t <sub>DCLK2IOE</sub>    | Delay from dedicated clock pin to IOE clock                                                                          | (7)        |

| t <sub>DCLK2LE</sub>     | Delay from dedicated clock pin to LE or EAB clock                                                                    | (7)        |

| t <sub>DIN2DATA</sub>    | Delay from dedicated input or clock to LE or EAB data                                                                | (7)        |

| t <sub>SAMELAB</sub>     | Routing delay for an LE driving another LE in the same LAB                                                           |            |

| t <sub>SAMEROW</sub>     | Routing delay for a row IOE, LE, or EAB driving a row IOE, LE, or EAB in the same row                                | (7)        |

| t <sub>SAME</sub> COLUMN | Routing delay for an LE driving an IOE in the same column                                                            | (7)        |

| t <sub>DIFFROW</sub>     | Routing delay for a column IOE, LE, or EAB driving an LE or EAB in a different row                                   | (7)        |

| t <sub>TWOROWS</sub>     | Routing delay for a row IOE or EAB driving an LE or EAB in a different row                                           | (7)        |

| t <sub>LEPERIPH</sub>    | Routing delay for an LE driving a control signal of an IOE via the peripheral control bus                            | (7)        |

| t <sub>LABCARRY</sub>    | Routing delay for the carry-out signal of an LE driving the carry-in signal of a different LE in a different LAB     |            |

| t <sub>LABCASC</sub>     | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |

| Table 29. Exte     | ernal Timing Parameters                                                                        |            |

|--------------------|------------------------------------------------------------------------------------------------|------------|

| Symbol             | Parameter                                                                                      | Conditions |

| t <sub>DRR</sub>   | Register-to-register delay via four LEs, three row interconnects, and four local interconnects | (8)        |

| t <sub>INSU</sub>  | Setup time with global clock at IOE register                                                   | (9)        |

| t <sub>INH</sub>   | Hold time with global clock at IOE register                                                    | (9)        |

| tоитсо             | Clock-to-output delay with global clock at IOE register                                        | (9)        |

| t <sub>PCISU</sub> | Setup time with global clock for registers used in PCI designs                                 | (9),(10)   |

| t <sub>PCIH</sub>  | Hold time with global clock for registers used in PCI designs                                  | (9),(10)   |

| t <sub>PCICO</sub> | Clock-to-output delay with global clock for registers used in PCI designs                      | (9),(10)   |

| Symbol                 | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | -3 Speed Grade |    |

|------------------------|----------------|-----|---------|----------------|-----|----------------|----|

|                        | Min            | Max | Min     | Max            | Min | Max            |    |

| t <sub>EABDATA1</sub>  |                | 1.7 |         | 2.0            |     | 2.3            | ns |

| t <sub>EABDATA1</sub>  |                | 0.6 |         | 0.7            |     | 0.8            | ns |

| t <sub>EABWE1</sub>    |                | 1.1 |         | 1.3            |     | 1.4            | ns |

| t <sub>EABWE2</sub>    |                | 0.4 |         | 0.4            |     | 0.5            | ns |

| t <sub>EABRE1</sub>    |                | 0.8 |         | 0.9            |     | 1.0            | ns |

| t <sub>EABRE2</sub>    |                | 0.4 |         | 0.4            |     | 0.5            | ns |

| t <sub>EABCLK</sub>    |                | 0.0 |         | 0.0            |     | 0.0            | ns |

| t <sub>EABCO</sub>     |                | 0.3 |         | 0.3            |     | 0.4            | ns |

| t <sub>EABBYPASS</sub> |                | 0.5 |         | 0.6            |     | 0.7            | ns |

| t <sub>EABSU</sub>     | 0.9            |     | 1.0     |                | 1.2 |                | ns |

| t <sub>EABH</sub>      | 0.4            |     | 0.4     |                | 0.5 |                | ns |

| t <sub>EABCLR</sub>    | 0.3            |     | 0.3     |                | 0.3 |                | ns |

| $t_{AA}$               |                | 3.2 |         | 3.8            |     | 4.4            | ns |

| $t_{WP}$               | 2.5            |     | 2.9     |                | 3.3 |                | ns |

| $t_{RP}$               | 0.9            |     | 1.1     |                | 1.2 |                | ns |

| t <sub>WDSU</sub>      | 0.9            |     | 1.0     |                | 1.1 |                | ns |

| t <sub>WDH</sub>       | 0.1            |     | 0.1     |                | 0.1 |                | ns |

| t <sub>WASU</sub>      | 1.7            |     | 2.0     |                | 2.3 |                | ns |

| t <sub>WAH</sub>       | 1.8            |     | 2.1     |                | 2.4 |                | ns |

| t <sub>RASU</sub>      | 3.1            |     | 3.7     |                | 4.2 |                | ns |

| t <sub>RAH</sub>       | 0.2            |     | 0.2     |                | 0.2 |                | ns |

| t <sub>WO</sub>        |                | 2.5 |         | 2.9            |     | 3.3            | ns |

| t <sub>DD</sub>        |                | 2.5 |         | 2.9            |     | 3.3            | ns |

| t <sub>EABOUT</sub>    |                | 0.5 |         | 0.6            |     | 0.7            | ns |

| t <sub>EABCH</sub>     | 1.5            |     | 2.0     |                | 2.3 |                | ns |

| t <sub>EABCL</sub>     | 2.5            |     | 2.9     |                | 3.3 |                | ns |

| Symbol                   | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|--------------------------|----------------|-----|---------|----------------|-----|----------|------|

|                          | Min            | Max | Min     | Max            | Min | Max      |      |

| t <sub>DIN2IOE</sub>     |                | 1.8 |         | 2.4            |     | 2.9      | ns   |

| t <sub>DIN2LE</sub>      |                | 1.5 |         | 1.8            |     | 2.4      | ns   |

| t <sub>DIN2DATA</sub>    |                | 1.5 |         | 1.8            |     | 2.2      | ns   |

| t <sub>DCLK2IOE</sub>    |                | 2.2 |         | 2.6            |     | 3.0      | ns   |

| t <sub>DCLK2LE</sub>     |                | 1.5 |         | 1.8            |     | 2.4      | ns   |

| t <sub>SAMELAB</sub>     |                | 0.1 |         | 0.2            |     | 0.3      | ns   |

| t <sub>SAMEROW</sub>     |                | 2.0 |         | 2.4            |     | 2.7      | ns   |

| t <sub>SAME</sub> COLUMN |                | 0.7 |         | 1.0            |     | 0.8      | ns   |

| t <sub>DIFFROW</sub>     |                | 2.7 |         | 3.4            |     | 3.5      | ns   |

| t <sub>TWOROWS</sub>     |                | 4.7 |         | 5.8            |     | 6.2      | ns   |

| t <sub>LEPERIPH</sub>    |                | 2.7 |         | 3.4            |     | 3.8      | ns   |

| t <sub>LABCARRY</sub>    |                | 0.3 |         | 0.4            |     | 0.5      | ns   |

| t <sub>LABCASC</sub>     |                | 0.8 |         | 0.8            |     | 1.1      | ns   |

| Symbol                        | -1 Spec | ed Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|-------------------------------|---------|----------|---------|---------|---------|---------|------|

|                               | Min     | Max      | Min     | Max     | Min     | Max     |      |

| t <sub>DRR</sub>              |         | 8.0      |         | 9.5     |         | 12.5    | ns   |

| t <sub>INSU</sub> (3)         | 2.1     |          | 2.5     |         | 3.9     |         | ns   |

| t <sub>INH</sub> (3)          | 0.0     |          | 0.0     |         | 0.0     |         | ns   |

| t <sub>оитсо</sub> (3)        | 2.0     | 4.9      | 2.0     | 5.9     | 2.0     | 7.6     | ns   |

| t <sub>INSU</sub> (4)         | 1.1     |          | 1.5     |         | -       |         | ns   |

| t <sub>INH</sub> (4)          | 0.0     |          | 0.0     |         | -       |         | ns   |

| t <sub>оитсо</sub> <i>(4)</i> | 0.5     | 3.9      | 0.5     | 4.9     | -       | -       | ns   |

| t <sub>PCISU</sub>            | 3.0     |          | 4.2     |         | -       |         | ns   |

| РСІН                          | 0.0     |          | 0.0     |         | -       |         | ns   |

| t <sub>PCICO</sub>            | 2.0     | 6.0      | 2.0     | 7.5     | _       | -       | ns   |

| Table 43. EPF10K50E External Timing Parameters Notes (1), (2) |                |     |         |                |     |         |      |  |  |  |  |

|---------------------------------------------------------------|----------------|-----|---------|----------------|-----|---------|------|--|--|--|--|

| Symbol                                                        | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | d Grade | Unit |  |  |  |  |

|                                                               | Min            | Max | Min     | Max            | Min | Max     |      |  |  |  |  |

| t <sub>DRR</sub>                                              |                | 8.5 |         | 10.0           |     | 13.5    | ns   |  |  |  |  |

| t <sub>INSU</sub>                                             | 2.7            |     | 3.2     |                | 4.3 |         | ns   |  |  |  |  |

| t <sub>INH</sub>                                              | 0.0            |     | 0.0     |                | 0.0 |         | ns   |  |  |  |  |

| t <sub>outco</sub>                                            | 2.0            | 4.5 | 2.0     | 5.2            | 2.0 | 7.3     | ns   |  |  |  |  |

| t <sub>PCISU</sub>                                            | 3.0            |     | 4.2     |                | -   |         | ns   |  |  |  |  |

| t <sub>PCIH</sub>                                             | 0.0            |     | 0.0     |                | -   |         | ns   |  |  |  |  |

| t <sub>PCICO</sub>                                            | 2.0            | 6.0 | 2.0     | 7.7            | -   | -       | ns   |  |  |  |  |

| Table 44. EPF10K50E External Bidirectional Timing Parameters Notes (1), (2) |                |     |         |                |     |         |      |  |  |  |  |

|-----------------------------------------------------------------------------|----------------|-----|---------|----------------|-----|---------|------|--|--|--|--|

| Symbol                                                                      | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | d Grade | Unit |  |  |  |  |

|                                                                             | Min            | Max | Min     | Max            | Min | Max     |      |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                                      | 2.7            |     | 3.2     |                | 4.3 |         | ns   |  |  |  |  |

| t <sub>INHBIDIR</sub>                                                       | 0.0            |     | 0.0     |                | 0.0 |         | ns   |  |  |  |  |

| t <sub>OUTCOBIDIR</sub>                                                     | 2.0            | 4.5 | 2.0     | 5.2            | 2.0 | 7.3     | ns   |  |  |  |  |

| t <sub>XZBIDIR</sub>                                                        |                | 6.8 |         | 7.8            |     | 10.1    | ns   |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                                        |                | 6.8 |         | 7.8            |     | 10.1    | ns   |  |  |  |  |

#### Notes to tables:

- (1) All timing parameters are described in Tables 24 through 30 in this data sheet.

- (2) These parameters are specified by characterization.

Tables 45 through 51 show EPF10K100E device internal and external timing parameters.

| Symbol              | -1 Spee | ed Grade | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |

|---------------------|---------|----------|---------|----------------|-----|----------|------|

|                     | Min     | Max      | Min     | Max            | Min | Max      |      |

| $t_{LUT}$           |         | 0.7      |         | 1.0            |     | 1.5      | ns   |

| t <sub>CLUT</sub>   |         | 0.5      |         | 0.7            |     | 0.9      | ns   |

| t <sub>RLUT</sub>   |         | 0.6      |         | 0.8            |     | 1.1      | ns   |

| t <sub>PACKED</sub> |         | 0.3      |         | 0.4            |     | 0.5      | ns   |

| $t_{EN}$            |         | 0.2      |         | 0.3            |     | 0.3      | ns   |

| t <sub>CICO</sub>   |         | 0.1      |         | 0.1            |     | 0.2      | ns   |

| t <sub>CGEN</sub>   |         | 0.4      |         | 0.5            |     | 0.7      | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |      | ed Grade | Unit |

|------------------------|----------------|-----|---------|----------------|------|----------|------|

|                        | Min            | Max | Min     | Max            | Min  | Max      |      |

| t <sub>EABWCOMB</sub>  | 5.9            |     | 7.7     |                | 10.3 |          | ns   |

| t <sub>EABWCREG</sub>  | 5.4            |     | 7.0     |                | 9.4  |          | ns   |

| t <sub>EABDD</sub>     |                | 3.4 |         | 4.5            |      | 5.9      | ns   |

| t <sub>EABDATACO</sub> |                | 0.5 |         | 0.7            |      | 0.8      | ns   |

| t <sub>EABDATASU</sub> | 0.8            |     | 1.0     |                | 1.4  |          | ns   |

| t <sub>EABDATAH</sub>  | 0.1            |     | 0.1     |                | 0.2  |          | ns   |

| t <sub>EABWESU</sub>   | 1.1            |     | 1.4     |                | 1.9  |          | ns   |

| t <sub>EABWEH</sub>    | 0.0            |     | 0.0     |                | 0.0  |          | ns   |

| t <sub>EABWDSU</sub>   | 1.0            |     | 1.3     |                | 1.7  |          | ns   |

| t <sub>EABWDH</sub>    | 0.2            |     | 0.2     |                | 0.3  |          | ns   |

| t <sub>EABWASU</sub>   | 4.1            |     | 5.2     |                | 6.8  |          | ns   |

| t <sub>EABWAH</sub>    | 0.0            |     | 0.0     |                | 0.0  |          | ns   |

| t <sub>EABWO</sub>     |                | 3.4 |         | 4.5            |      | 5.9      | ns   |

| Symbol                   | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|--------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                          | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>DIN2IOE</sub>     |                | 3.1 |                | 3.6 |                | 4.4 | ns   |

| t <sub>DIN2LE</sub>      |                | 0.3 |                | 0.4 |                | 0.5 | ns   |

| t <sub>DIN2DATA</sub>    |                | 1.6 |                | 1.8 |                | 2.0 | ns   |

| t <sub>DCLK2IOE</sub>    |                | 0.8 |                | 1.1 |                | 1.4 | ns   |

| t <sub>DCLK2LE</sub>     |                | 0.3 |                | 0.4 |                | 0.5 | ns   |

| t <sub>SAMELAB</sub>     |                | 0.1 |                | 0.1 |                | 0.2 | ns   |

| t <sub>SAMEROW</sub>     |                | 1.5 |                | 2.5 |                | 3.4 | ns   |

| t <sub>SAME</sub> COLUMN |                | 0.4 |                | 1.0 |                | 1.6 | ns   |

| t <sub>DIFFROW</sub>     |                | 1.9 |                | 3.5 |                | 5.0 | ns   |

| t <sub>TWOROWS</sub>     |                | 3.4 |                | 6.0 |                | 8.4 | ns   |

| t <sub>LEPERIPH</sub>    |                | 4.3 |                | 5.4 |                | 6.5 | ns   |

| t <sub>LABCARRY</sub>    |                | 0.5 |                | 0.7 |                | 0.9 | ns   |

| t <sub>LABCASC</sub>     |                | 0.8 |                | 1.0 |                | 1.4 | ns   |

| Table 50. EPF10K100E External Timing Parameters Notes (1), (2) |                |     |         |                |     |          |      |  |  |  |

|----------------------------------------------------------------|----------------|-----|---------|----------------|-----|----------|------|--|--|--|

| Symbol                                                         | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |  |  |  |

|                                                                | Min            | Max | Min     | Max            | Min | Max      | ]    |  |  |  |

| t <sub>DRR</sub>                                               |                | 9.0 |         | 12.0           |     | 16.0     | ns   |  |  |  |

| t <sub>INSU</sub> (3)                                          | 2.0            |     | 2.5     |                | 3.3 |          | ns   |  |  |  |

| t <sub>INH</sub> (3)                                           | 0.0            |     | 0.0     |                | 0.0 |          | ns   |  |  |  |

| t <sub>оитсо</sub> (3)                                         | 2.0            | 5.2 | 2.0     | 6.9            | 2.0 | 9.1      | ns   |  |  |  |

| t <sub>INSU</sub> (4)                                          | 2.0            |     | 2.2     |                | -   |          | ns   |  |  |  |

| t <sub>INH</sub> (4)                                           | 0.0            |     | 0.0     |                | -   |          | ns   |  |  |  |

| t <sub>OUTCO</sub> (4)                                         | 0.5            | 3.0 | 0.5     | 4.6            | -   | -        | ns   |  |  |  |

| t <sub>PCISU</sub>                                             | 3.0            |     | 6.2     |                | -   |          | ns   |  |  |  |

| t <sub>PCIH</sub>                                              | 0.0            |     | 0.0     |                | _   |          | ns   |  |  |  |

| t <sub>PCICO</sub>                                             | 2.0            | 6.0 | 2.0     | 6.9            | _   | _        | ns   |  |  |  |

| Table 51. EPF10K100E External Bidirectional Timing Parameters Notes (1), (2) |                |     |         |                |     |          |      |  |  |  |

|------------------------------------------------------------------------------|----------------|-----|---------|----------------|-----|----------|------|--|--|--|

| Symbol                                                                       | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | ed Grade | Unit |  |  |  |

|                                                                              | Min            | Max | Min     | Max            | Min | Max      |      |  |  |  |

| t <sub>INSUBIDIR</sub> (3)                                                   | 1.7            |     | 2.5     |                | 3.3 |          | ns   |  |  |  |

| t <sub>INHBIDIR</sub> (3)                                                    | 0.0            |     | 0.0     |                | 0.0 |          | ns   |  |  |  |

| t <sub>INSUBIDIR</sub> (4)                                                   | 2.0            |     | 2.8     |                | _   |          | ns   |  |  |  |

| t <sub>INHBIDIR</sub> (4)                                                    | 0.0            |     | 0.0     |                | _   |          | ns   |  |  |  |

| toutcobidir (3)                                                              | 2.0            | 5.2 | 2.0     | 6.9            | 2.0 | 9.1      | ns   |  |  |  |

| t <sub>XZBIDIR</sub> (3)                                                     |                | 5.6 |         | 7.5            |     | 10.1     | ns   |  |  |  |

| t <sub>ZXBIDIR</sub> (3)                                                     |                | 5.6 |         | 7.5            |     | 10.1     | ns   |  |  |  |

| toutcobidir (4)                                                              | 0.5            | 3.0 | 0.5     | 4.6            | _   | -        | ns   |  |  |  |

| t <sub>XZBIDIR</sub> (4)                                                     |                | 4.6 |         | 6.5            |     | -        | ns   |  |  |  |

| t <sub>ZXBIDIR</sub> (4)                                                     |                | 4.6 |         | 6.5            |     | _        | ns   |  |  |  |

#### Notes to tables:

- (1) All timing parameters are described in Tables 24 through 30 in this data sheet.

- (2) These parameters are specified by characterization.

- (3) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

- (4) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

| Table 54. EPF10K130E Device EAB Internal Microparameters (Part 2 of 2) Note (1) |         |                |     |                |     |         |      |  |  |  |

|---------------------------------------------------------------------------------|---------|----------------|-----|----------------|-----|---------|------|--|--|--|

| Symbol                                                                          | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | d Grade | Unit |  |  |  |

|                                                                                 | Min     | Max            | Min | Max            | Min | Max     |      |  |  |  |

| $t_{DD}$                                                                        |         | 1.5            |     | 2.0            |     | 2.6     | ns   |  |  |  |

| t <sub>EABOUT</sub>                                                             |         | 0.2            |     | 0.3            |     | 0.3     | ns   |  |  |  |

| t <sub>EABCH</sub>                                                              | 1.5     |                | 2.0 |                | 2.5 |         | ns   |  |  |  |

| t <sub>EABCL</sub>                                                              | 2.7     |                | 3.5 |                | 4.7 |         | ns   |  |  |  |

| Table 55. EPF10K130E Device EAB Internal Timing Macroparameters Note (1) |                |     |         |                |      |          |      |  |  |

|--------------------------------------------------------------------------|----------------|-----|---------|----------------|------|----------|------|--|--|

| Symbol                                                                   | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |      | ed Grade | Unit |  |  |

|                                                                          | Min            | Max | Min     | Max            | Min  | Max      |      |  |  |

| t <sub>EABAA</sub>                                                       |                | 5.9 |         | 7.5            |      | 9.9      | ns   |  |  |

| t <sub>EABRCOMB</sub>                                                    | 5.9            |     | 7.5     |                | 9.9  |          | ns   |  |  |

| t <sub>EABRCREG</sub>                                                    | 5.1            |     | 6.4     |                | 8.5  |          | ns   |  |  |

| t <sub>EABWP</sub>                                                       | 2.7            |     | 3.5     |                | 4.7  |          | ns   |  |  |

| t <sub>EABWCOMB</sub>                                                    | 5.9            |     | 7.7     |                | 10.3 |          | ns   |  |  |

| t <sub>EABWCREG</sub>                                                    | 5.4            |     | 7.0     |                | 9.4  |          | ns   |  |  |

| t <sub>EABDD</sub>                                                       |                | 3.4 |         | 4.5            |      | 5.9      | ns   |  |  |

| t <sub>EABDATACO</sub>                                                   |                | 0.5 |         | 0.7            |      | 0.8      | ns   |  |  |

| t <sub>EABDATASU</sub>                                                   | 0.8            |     | 1.0     |                | 1.4  |          | ns   |  |  |

| t <sub>EABDATAH</sub>                                                    | 0.1            |     | 0.1     |                | 0.2  |          | ns   |  |  |

| t <sub>EABWESU</sub>                                                     | 1.1            |     | 1.4     |                | 1.9  |          | ns   |  |  |

| t <sub>EABWEH</sub>                                                      | 0.0            |     | 0.0     |                | 0.0  |          | ns   |  |  |

| t <sub>EABWDSU</sub>                                                     | 1.0            |     | 1.3     |                | 1.7  |          | ns   |  |  |

| t <sub>EABWDH</sub>                                                      | 0.2            |     | 0.2     |                | 0.3  |          | ns   |  |  |

| t <sub>EABWASU</sub>                                                     | 4.1            |     | 5.1     |                | 6.8  |          | ns   |  |  |

| t <sub>EABWAH</sub>                                                      | 0.0            |     | 0.0     |                | 0.0  |          | ns   |  |  |

| t <sub>EABWO</sub>                                                       |                | 3.4 |         | 4.5            |      | 5.9      | ns   |  |  |

| Table 76. EPF10I        | Table 76. EPF10K200S Device EAB Internal Timing Macroparameters Note (1) |     |                |     |                |     |      |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------|-----|----------------|-----|----------------|-----|------|--|--|--|--|

| Symbol                  | -1 Speed Grade                                                           |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |  |  |  |

|                         | Min                                                                      | Max | Min            | Max | Min            | Max |      |  |  |  |  |

| t <sub>EABAA</sub>      |                                                                          | 3.9 |                | 6.4 |                | 8.4 | ns   |  |  |  |  |

| t <sub>EABRCOMB</sub>   | 3.9                                                                      |     | 6.4            |     | 8.4            |     | ns   |  |  |  |  |

| t <sub>EABRCREG</sub>   | 3.6                                                                      |     | 5.7            |     | 7.6            |     | ns   |  |  |  |  |

| t <sub>EABWP</sub>      | 2.1                                                                      |     | 4.0            |     | 5.3            |     | ns   |  |  |  |  |

| t <sub>EABWCOMB</sub>   | 4.8                                                                      |     | 8.1            |     | 10.7           |     | ns   |  |  |  |  |

| t <sub>EABWCREG</sub>   | 5.4                                                                      |     | 8.0            |     | 10.6           |     | ns   |  |  |  |  |

| t <sub>EABDD</sub>      |                                                                          | 3.8 |                | 5.1 |                | 6.7 | ns   |  |  |  |  |

| t <sub>EABDATA</sub> CO |                                                                          | 0.8 |                | 1.0 |                | 1.3 | ns   |  |  |  |  |

| t <sub>EABDATASU</sub>  | 1.1                                                                      |     | 1.6            |     | 2.1            |     | ns   |  |  |  |  |

| t <sub>EABDATAH</sub>   | 0.0                                                                      |     | 0.0            |     | 0.0            |     | ns   |  |  |  |  |

| t <sub>EABWESU</sub>    | 0.7                                                                      |     | 1.1            |     | 1.5            |     | ns   |  |  |  |  |

| t <sub>EABWEH</sub>     | 0.4                                                                      |     | 0.5            |     | 0.6            |     | ns   |  |  |  |  |

| t <sub>EABWDSU</sub>    | 1.2                                                                      |     | 1.8            |     | 2.4            |     | ns   |  |  |  |  |

| t <sub>EABWDH</sub>     | 0.0                                                                      |     | 0.0            |     | 0.0            |     | ns   |  |  |  |  |

| t <sub>EABWASU</sub>    | 1.9                                                                      |     | 3.6            |     | 4.7            |     | ns   |  |  |  |  |

| t <sub>EABWAH</sub>     | 0.8                                                                      |     | 0.5            |     | 0.7            |     | ns   |  |  |  |  |

| t <sub>EABWO</sub>      |                                                                          | 3.1 |                | 4.4 |                | 5.8 | ns   |  |  |  |  |

| Table 77. EPF10K200S Device Interconnect Timing Microparameters (Part 1 of 2) Note (1) |                |     |         |                |     |         |      |  |

|----------------------------------------------------------------------------------------|----------------|-----|---------|----------------|-----|---------|------|--|

| Symbol                                                                                 | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | d Grade | Unit |  |

|                                                                                        | Min            | Max | Min     | Max            | Min | Max     |      |  |

| t <sub>DIN2IOE</sub>                                                                   |                | 4.4 |         | 4.8            |     | 5.5     | ns   |  |

| t <sub>DIN2LE</sub>                                                                    |                | 0.6 |         | 0.6            |     | 0.9     | ns   |  |

| t <sub>DIN2DATA</sub>                                                                  |                | 1.8 |         | 2.1            |     | 2.8     | ns   |  |

| t <sub>DCLK2IOE</sub>                                                                  |                | 1.7 |         | 2.0            |     | 2.8     | ns   |  |

| t <sub>DCLK2LE</sub>                                                                   |                | 0.6 |         | 0.6            |     | 0.9     | ns   |  |

| t <sub>SAMELAB</sub>                                                                   |                | 0.1 |         | 0.1            |     | 0.2     | ns   |  |

| t <sub>SAMEROW</sub>                                                                   |                | 3.0 |         | 4.6            |     | 5.7     | ns   |  |

| t <sub>SAME</sub> COLUMN                                                               |                | 3.5 |         | 4.9            |     | 6.4     | ns   |  |

| t <sub>DIFFROW</sub>                                                                   |                | 6.5 |         | 9.5            |     | 12.1    | ns   |  |

| t <sub>TWOROWS</sub>                                                                   |                | 9.5 |         | 14.1           |     | 17.8    | ns   |  |

| t <sub>LEPERIPH</sub>                                                                  |                | 5.5 |         | 6.2            |     | 7.2     | ns   |  |

| t <sub>LABCARRY</sub>                                                                  |                | 0.3 |         | 0.1            |     | 0.2     | ns   |  |

# Power Consumption

The supply power (P) for FLEX 10KE devices can be calculated with the following equation:

$$P = P_{INT} + P_{IO} = (I_{CCSTANDBY} + I_{CCACTIVE}) \times V_{CC} + P_{IO}$$

The  $I_{CCACTIVE}$  value depends on the switching frequency and the application logic. This value is calculated based on the amount of current that each LE typically consumes. The  $P_{IO}$  value, which depends on the device output load characteristics and switching frequency, can be calculated using the guidelines given in *Application Note 74 (Evaluating Power for Altera Devices)*.

Compared to the rest of the device, the embedded array consumes a negligible amount of power. Therefore, the embedded array can be ignored when calculating supply current.

The I<sub>CCACTIVE</sub> value can be calculated with the following equation:

$$I_{CCACTIVE} = K \times f_{\boldsymbol{MAX}} \times N \times \boldsymbol{tog_{LC}} \times \frac{\mu A}{MHz \times LE}$$

Where:

**f**<sub>MAX</sub> = Maximum operating frequency in MHz N = Total number of LEs used in the device

togLC = Average percent of LEs toggling at each clock

(typically 12.5%)

K = Constant

Table 80 provides the constant (K) values for FLEX 10KE devices.

| Table 80. FLEX 10KE K Constant Values |         |

|---------------------------------------|---------|

| Device                                | K Value |

| EPF10K30E                             | 4.5     |

| EPF10K50E                             | 4.8     |

| EPF10K50S                             | 4.5     |

| EPF10K100E                            | 4.5     |

| EPF10K130E                            | 4.6     |

| EPF10K200E                            | 4.8     |

| EPF10K200S                            | 4.6     |

This calculation provides an  $I_{CC}$  estimate based on typical conditions with no output load. The actual  $I_{CC}$  should be verified during operation because this measurement is sensitive to the actual pattern in the device and the environmental operating conditions.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: lit\_reg@altera.com Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending

applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.