# E·XFL

# Intel - EPF10K50STC144-1 Datasheet

Welcome to E-XFL.COM

# Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

# Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 360                                                         |

| Number of Logic Elements/Cells | 2880                                                        |

| Total RAM Bits                 | 40960                                                       |

| Number of I/O                  | 102                                                         |

| Number of Gates                | 199000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                             |

| Package / Case                 | 144-LQFP                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k50stc144-1 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

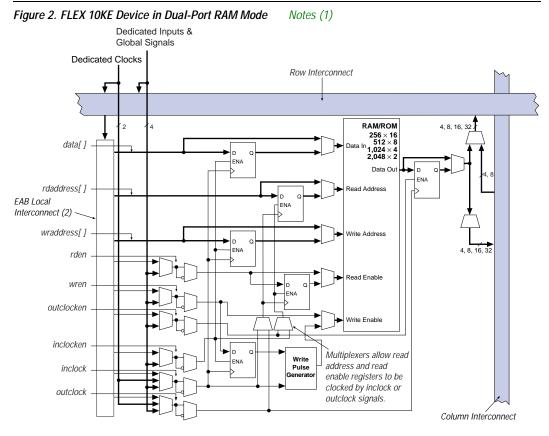

The EAB can also be used for bidirectional, dual-port memory applications where two ports read or write simultaneously. To implement this type of dual-port memory, two EABs are used to support two simultaneous read or writes.

Alternatively, one clock and clock enable can be used to control the input registers of the EAB, while a different clock and clock enable control the output registers (see Figure 2).

### Notes:

- (1) All registers can be asynchronously cleared by EAB local interconnect signals, global signals, or the chip-wide reset.

- (2) EPF10K30E and EPF10K50E devices have 88 EAB local interconnect channels; EPF10K100E, EPF10K130E, and EPF10K200E devices have 104 EAB local interconnect channels.

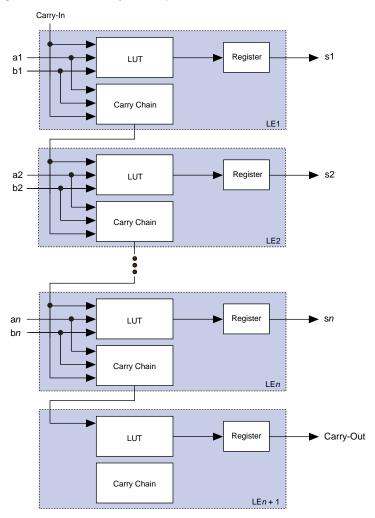

Figure 9 shows how an *n*-bit full adder can be implemented in n + 1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for an accumulator function. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it can be used as a general-purpose signal.

Figure 9. FLEX 10KE Carry Chain Operation (n-Bit Full Adder)

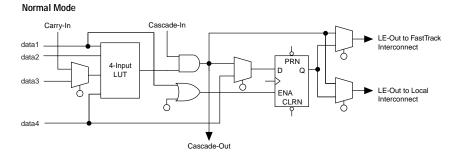

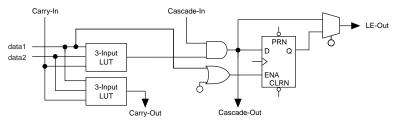

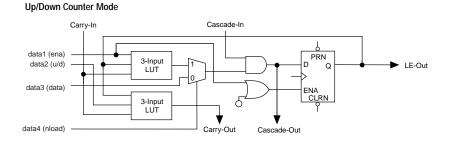

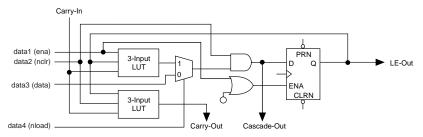

# Figure 11. FLEX 10KE LE Operating Modes

#### **Clearable Counter Mode**

| Peripheral<br>Control Signal | EPF10K100E | EPF10K130E | EPF10K200E<br>EPF10K200S |

|------------------------------|------------|------------|--------------------------|

| OE0                          | Row A      | Row C      | Row G                    |

| OE1                          | Row C      | Row E      | Row I                    |

| OE2                          | Row E      | Row G      | Row K                    |

| OE 3                         | Row L      | Row N      | Row R                    |

| OE4                          | Row I      | Row K      | Row O                    |

| OE5                          | Row K      | Row M      | Row Q                    |

| CLKENA0/CLK0/GLOBAL0         | Row F      | Row H      | Row L                    |

| CLKENA1/OE6/GLOBAL1          | Row D      | Row F      | Row J                    |

| CLKENA2/CLR0                 | Row B      | Row D      | Row H                    |

| CLKENA3/OE7/GLOBAL2          | Row H      | Row J      | Row N                    |

| CLKENA4/CLR1                 | Row J      | Row L      | Row P                    |

| CLKENA5/CLK1/GLOBAL3         | Row G      | Row I      | Row M                    |

Signals on the peripheral control bus can also drive the four global signals, referred to as GLOBAL0 through GLOBAL3 in Tables 8 and 9. An internally generated signal can drive a global signal, providing the same low-skew, low-delay characteristics as a signal driven by an input pin. An LE drives the global signal by driving a row line that drives the peripheral bus, which then drives the global signal. This feature is ideal for internally generated clear or clock signals with high fan-out. However, internally driven global signals offer no advantage over the general-purpose interconnect for routing data signals. The dedicated input pin should be driven to a known logic state (such as ground) and not be allowed to float.

The chip-wide output enable pin is an active-high pin (DEV\_OE) that can be used to tri-state all pins on the device. This option can be set in the Altera software. On EPF10K50E and EPF10K200E devices, the built-in I/O pin pull-up resistors (which are active during configuration) are active when the chip-wide output enable pin is asserted. The registers in the IOE can also be reset by the chip-wide reset pin.

The VCCINT pins must always be connected to a 2.5-V power supply. With a 2.5-V V<sub>CCINT</sub> level, input voltages are compatible with 2.5-V, 3.3-V, and 5.0-V inputs. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is at 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with V<sub>CCIO</sub> levels higher than 3.0 V achieve a faster timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ .

| Table 14. FLEX 10KE MultiVolt I/O Support |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |      |                      |              |     |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|----------------------|--------------|-----|--|--|--|

| V <sub>CCIO</sub> (V)                     | Input Signal (V) Output Signal (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |      |                      |              |     |  |  |  |

|                                           | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3          | 5.0  | 2.5                  | 3.3          | 5.0 |  |  |  |

| 2.5                                       | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ✓(1)         | ✓(1) | <ul> <li></li> </ul> |              |     |  |  |  |

| 3.3                                       | <ul> <li>Image: A start of the start of</li></ul> | $\checkmark$ | ✓(1) | <b>√</b> (2)         | $\checkmark$ | ~   |  |  |  |

Table 14 summarizes FLEX 10KE MultiVolt I/O support.

#### Notes:

(1) The PCI clamping diode must be disabled to drive an input with voltages higher than  $V_{\rm CCIO}$ .

(2) When  $V_{CCIO}$  = 3.3 V, a FLEX 10KE device can drive a 2.5-V device that has 3.3-V tolerant inputs.

Open-drain output pins on FLEX 10KE devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a  $V_{\rm IH}$  of 3.5 V. When the open-drain pin is active, it will drive low. When the pin is inactive, the trace will be pulled up to 5.0 V by the resistor. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The I<sub>OL</sub> current specification should be considered when selecting a pull-up resistor.

# Power Sequencing & Hot-Socketing

Because FLEX 10KE devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  power planes can be powered in any order.

Signals can be driven into FLEX 10KE devices before and during power up without damaging the device. Additionally, FLEX 10KE devices do not drive out during power up. Once operating conditions are reached, FLEX 10KE devices operate as specified by the user.

| Table 2            | Table 23. FLEX 10KE Device Capacitance     Note (14) |                                     |     |     |      |  |  |  |  |  |

|--------------------|------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|--|--|

| Symbol             | Parameter                                            | Conditions                          | Min | Max | Unit |  |  |  |  |  |

| C <sub>IN</sub>    | Input capacitance                                    | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |  |  |  |  |

| C <sub>INCLK</sub> | Input capacitance on<br>dedicated clock pin          | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |  |  |  |

| C <sub>OUT</sub>   | Output capacitance                                   | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |  |  |  |  |  |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before  $V_{CCINT}$  and  $V_{CCIO}$  are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  V or 3.3 V.

- (7) These values are specified under the FLEX 10KE Recommended Operating Conditions shown in Tables 20 and 21.

(8) The FLEX 10KE input buffers are compatible with 2.5-V, 3.3-V (LVTTL and LVCMOS), and 5.0-V TTL and CMOS

- signals. Additionally, the input buffers are 3.3-V PCI compliant when  $V_{CCIO}$  and  $V_{CCINT}$  meet the relationship shown in Figure 22.

- (9) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (10) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (11) This value is specified for normal device operation. The value may vary during power-up.

- (12) This parameter applies to -1 speed-grade commercial-temperature devices and -2 speed-grade-industrial temperature devices.

- (13) Pin pull-up resistance values will be lower if the pin is driven higher than  $V_{CCIO}$  by an external source.

- (14) Capacitance is sample-tested only.

Timing simulation and delay prediction are available with the Altera Simulator and Timing Analyzer, or with industry-standard EDA tools. The Simulator offers both pre-synthesis functional simulation to evaluate logic design accuracy and post-synthesis timing simulation with 0.1-ns resolution. The Timing Analyzer provides point-to-point timing delay information, setup and hold time analysis, and device-wide performance analysis.

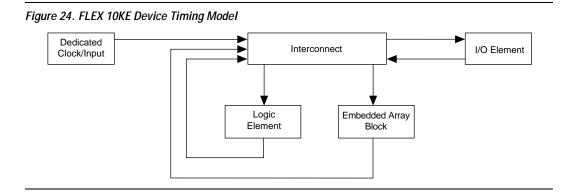

Figure 24 shows the overall timing model, which maps the possible paths to and from the various elements of the FLEX 10KE device.

Figures 25 through 28 show the delays that correspond to various paths and functions within the LE, IOE, EAB, and bidirectional timing models.

| Symbol                 | Parameter                                                              | Conditions |

|------------------------|------------------------------------------------------------------------|------------|

| t <sub>EABDATA1</sub>  | Data or address delay to EAB for combinatorial input                   |            |

| t <sub>EABDATA2</sub>  | Data or address delay to EAB for registered input                      |            |

| t <sub>EABWE1</sub>    | Write enable delay to EAB for combinatorial input                      |            |

| t <sub>EABWE2</sub>    | Write enable delay to EAB for registered input                         |            |

| t <sub>EABRE1</sub>    | Read enable delay to EAB for combinatorial input                       |            |

| t <sub>EABRE2</sub>    | Read enable delay to EAB for registered input                          |            |

| t <sub>EABCLK</sub>    | EAB register clock delay                                               |            |

| t <sub>EABCO</sub>     | EAB register clock-to-output delay                                     |            |

| t <sub>EABBYPASS</sub> | Bypass register delay                                                  |            |

| t <sub>EABSU</sub>     | EAB register setup time before clock                                   |            |

| t <sub>EABH</sub>      | EAB register hold time after clock                                     |            |

| t <sub>EABCLR</sub>    | EAB register asynchronous clear time to output delay                   |            |

| t <sub>AA</sub>        | Address access delay (including the read enable to output delay)       |            |

| t <sub>WP</sub>        | Write pulse width                                                      |            |

| t <sub>RP</sub>        | Read pulse width                                                       |            |

| t <sub>WDSU</sub>      | Data setup time before falling edge of write pulse                     | (5)        |

| t <sub>WDH</sub>       | Data hold time after falling edge of write pulse                       | (5)        |

| t <sub>WASU</sub>      | Address setup time before rising edge of write pulse                   | (5)        |

| t <sub>WAH</sub>       | Address hold time after falling edge of write pulse                    | (5)        |

| t <sub>RASU</sub>      | Address setup time with respect to the falling edge of the read enable |            |

| t <sub>RAH</sub>       | Address hold time with respect to the falling edge of the read enable  |            |

| t <sub>WO</sub>        | Write enable to data output valid delay                                |            |

| t <sub>DD</sub>        | Data-in to data-out valid delay                                        |            |

| t <sub>EABOUT</sub>    | Data-out delay                                                         |            |

| t <sub>EABCH</sub>     | Clock high time                                                        |            |

| t <sub>EABCL</sub>     | Clock low time                                                         |            |

Figures 29 and 30 show the asynchronous and synchronous timing waveforms, respectively, or the EAB macroparameters in Tables 26 and 27.

EAB Asynchronous Read WE \_ a0 a2 Address a1 a3 – t<sub>EABAA</sub>t<sub>EABRCCOMB</sub> Data-Out d0 d3 d1 d2 **EAB Asynchronous Write** WE  $t_{EABWP}$ ► t<sub>EABWDH</sub> t<sub>EABWDSU</sub> ×. din0 din1 Data-In t<sub>EABWASU</sub> t<sub>EABWAH</sub> t<sub>EABWCCOMB</sub> Address a0 a1 a2  $t_{EABDD}$ Data-Out din0 din1 dout2

#### Figure 29. EAB Asynchronous Timing Waveforms

| Symbol             | -1 Spee | d Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|--------------------|---------|---------|----------------|-----|----------------|-----|------|

|                    | Min     | Max     | Min            | Max | Min            | Max |      |

| t <sub>CGENR</sub> |         | 0.1     |                | 0.1 |                | 0.2 | ns   |

| t <sub>CASC</sub>  |         | 0.6     |                | 0.8 |                | 1.0 | ns   |

| t <sub>C</sub>     |         | 0.0     |                | 0.0 |                | 0.0 | ns   |

| t <sub>CO</sub>    |         | 0.3     |                | 0.4 |                | 0.5 | ns   |

| t <sub>COMB</sub>  |         | 0.4     |                | 0.4 |                | 0.6 | ns   |

| t <sub>SU</sub>    | 0.4     |         | 0.6            |     | 0.6            |     | ns   |

| t <sub>H</sub>     | 0.7     |         | 1.0            |     | 1.3            |     | ns   |

| PRE                |         | 0.8     |                | 0.9 |                | 1.2 | ns   |

| t <sub>CLR</sub>   |         | 0.8     |                | 0.9 |                | 1.2 | ns   |

| сн                 | 2.0     |         | 2.5            |     | 2.5            |     | ns   |

| ĊL                 | 2.0     |         | 2.5            |     | 2.5            |     | ns   |

| Symbol              | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | ed Grade | Unit |

|---------------------|---------|----------------|-----|----------------|-----|----------|------|

|                     | Min     | Max            | Min | Max            | Min | Max      |      |

| t <sub>IOD</sub>    |         | 2.4            |     | 2.8            |     | 3.8      | ns   |

| t <sub>IOC</sub>    |         | 0.3            |     | 0.4            |     | 0.5      | ns   |

| t <sub>IOCO</sub>   |         | 1.0            |     | 1.1            |     | 1.6      | ns   |

| t <sub>IOCOMB</sub> |         | 0.0            |     | 0.0            |     | 0.0      | ns   |

| t <sub>IOSU</sub>   | 1.2     |                | 1.4 |                | 1.9 |          | ns   |

| t <sub>IOH</sub>    | 0.3     |                | 0.4 |                | 0.5 |          | ns   |

| t <sub>IOCLR</sub>  |         | 1.0            |     | 1.1            |     | 1.6      | ns   |

| t <sub>OD1</sub>    |         | 1.9            |     | 2.3            |     | 3.0      | ns   |

| t <sub>OD2</sub>    |         | 1.4            |     | 1.8            |     | 2.5      | ns   |

| t <sub>OD3</sub>    |         | 4.4            |     | 5.2            |     | 7.0      | ns   |

| t <sub>XZ</sub>     |         | 2.7            |     | 3.1            |     | 4.3      | ns   |

| t <sub>ZX1</sub>    |         | 2.7            |     | 3.1            |     | 4.3      | ns   |

| t <sub>ZX2</sub>    |         | 2.2            |     | 2.6            |     | 3.8      | ns   |

| t <sub>ZX3</sub>    |         | 5.2            |     | 6.0            |     | 8.3      | ns   |

| t <sub>INREG</sub>  |         | 3.4            |     | 4.1            |     | 5.5      | ns   |

| t <sub>IOFD</sub>   |         | 0.8            |     | 1.3            |     | 2.4      | ns   |

| t <sub>INCOMB</sub> |         | 0.8            |     | 1.3            |     | 2.4      | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABAA</sub>     |                | 6.4 |                | 7.6 |                | 8.8 | ns   |

| t <sub>EABRCOMB</sub>  | 6.4            |     | 7.6            |     | 8.8            |     | ns   |

| t <sub>EABRCREG</sub>  | 4.4            |     | 5.1            |     | 6.0            |     | ns   |

| t <sub>EABWP</sub>     | 2.5            |     | 2.9            |     | 3.3            |     | ns   |

| t <sub>EABWCOMB</sub>  | 6.0            |     | 7.0            |     | 8.0            |     | ns   |

| t <sub>EABWCREG</sub>  | 6.8            |     | 7.8            |     | 9.0            |     | ns   |

| t <sub>EABDD</sub>     |                | 5.7 |                | 6.7 |                | 7.7 | ns   |

| t <sub>EABDATACO</sub> |                | 0.8 |                | 0.9 |                | 1.1 | ns   |

| t <sub>EABDATASU</sub> | 1.5            |     | 1.7            |     | 2.0            |     | ns   |

| t <sub>EABDATAH</sub>  | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>EABWESU</sub>   | 1.3            |     | 1.4            |     | 1.7            |     | ns   |

| t <sub>EABWEH</sub>    | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>EABWDSU</sub>   | 1.5            |     | 1.7            |     | 2.0            |     | ns   |

| t <sub>EABWDH</sub>    | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>EABWASU</sub>   | 3.0            |     | 3.6            |     | 4.3            |     | ns   |

| t <sub>EABWAH</sub>    | 0.5            |     | 0.5            |     | 0.4            |     | ns   |

| t <sub>EABWO</sub>     |                | 5.1 |                | 6.0 |                | 6.8 | ns   |

| Table 37. EPF10K30E External Bidirectional Timing Parameters         Notes (1), (2) |         |                |     |                |     |         |      |  |  |

|-------------------------------------------------------------------------------------|---------|----------------|-----|----------------|-----|---------|------|--|--|

| Symbol                                                                              | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | d Grade | Unit |  |  |

|                                                                                     | Min     | Max            | Min | Max            | Min | Max     |      |  |  |

| t <sub>INSUBIDIR</sub> (3)                                                          | 2.8     |                | 3.9 |                | 5.2 |         | ns   |  |  |

| t <sub>INHBIDIR</sub> (3)                                                           | 0.0     |                | 0.0 |                | 0.0 |         | ns   |  |  |

| t <sub>INSUBIDIR</sub> (4)                                                          | 3.8     |                | 4.9 |                | -   |         | ns   |  |  |

| t <sub>INHBIDIR</sub> (4)                                                           | 0.0     |                | 0.0 |                | -   |         | ns   |  |  |

| t <sub>OUTCOBIDIR</sub> (3)                                                         | 2.0     | 4.9            | 2.0 | 5.9            | 2.0 | 7.6     | ns   |  |  |

| t <sub>XZBIDIR</sub> (3)                                                            |         | 6.1            |     | 7.5            |     | 9.7     | ns   |  |  |

| t <sub>ZXBIDIR</sub> (3)                                                            |         | 6.1            |     | 7.5            |     | 9.7     | ns   |  |  |

| t <sub>OUTCOBIDIR</sub> (4)                                                         | 0.5     | 3.9            | 0.5 | 4.9            | -   | -       | ns   |  |  |

| t <sub>XZBIDIR</sub> (4)                                                            |         | 5.1            |     | 6.5            |     | -       | ns   |  |  |

| t <sub>ZXBIDIR</sub> (4)                                                            |         | 5.1            |     | 6.5            |     | -       | ns   |  |  |

# Notes to tables:

(1) All timing parameters are described in Tables 24 through 30 in this data sheet.

(2) These parameters are specified by characterization.

(3) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

(4) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

# Tables 38 through 44 show EPF10K50E device internal and external timing parameters.

| Symbol              | -1 Spee | d Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|---------------------|---------|---------|----------------|-----|----------------|-----|------|

|                     | Min     | Мах     | Min            | Мах | Min            | Max |      |

| t <sub>LUT</sub>    |         | 0.6     |                | 0.9 |                | 1.3 | ns   |

| t <sub>CLUT</sub>   |         | 0.5     |                | 0.6 |                | 0.8 | ns   |

| t <sub>RLUT</sub>   |         | 0.7     |                | 0.8 |                | 1.1 | ns   |

| t <sub>PACKED</sub> |         | 0.4     |                | 0.5 |                | 0.6 | ns   |

| t <sub>EN</sub>     |         | 0.6     |                | 0.7 |                | 0.9 | ns   |

| t <sub>CICO</sub>   |         | 0.2     |                | 0.2 |                | 0.3 | ns   |

| t <sub>CGEN</sub>   |         | 0.5     |                | 0.5 |                | 0.8 | ns   |

| t <sub>CGENR</sub>  |         | 0.2     |                | 0.2 |                | 0.3 | ns   |

| t <sub>CASC</sub>   |         | 0.8     |                | 1.0 |                | 1.4 | ns   |

| t <sub>C</sub>      |         | 0.5     |                | 0.6 |                | 0.8 | ns   |

| t <sub>CO</sub>     |         | 0.7     |                | 0.7 |                | 0.9 | ns   |

| t <sub>COMB</sub>   |         | 0.5     |                | 0.6 |                | 0.8 | ns   |

| t <sub>SU</sub>     | 0.7     |         | 0.7            |     | 0.8            |     | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABDATA1</sub>  |                | 1.7 |                | 2.0 |                | 2.7 | ns   |

| t <sub>EABDATA1</sub>  |                | 0.6 |                | 0.7 |                | 0.9 | ns   |

| t <sub>EABWE1</sub>    |                | 1.1 |                | 1.3 |                | 1.8 | ns   |

| t <sub>EABWE2</sub>    |                | 0.4 |                | 0.4 |                | 0.6 | ns   |

| t <sub>EABRE1</sub>    |                | 0.8 |                | 0.9 |                | 1.2 | ns   |

| t <sub>EABRE2</sub>    |                | 0.4 |                | 0.4 |                | 0.6 | ns   |

| t <sub>EABCLK</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABCO</sub>     |                | 0.3 |                | 0.3 |                | 0.5 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| t <sub>EABSU</sub>     | 0.9            |     | 1.0            |     | 1.4            |     | ns   |

| t <sub>EABH</sub>      | 0.4            |     | 0.4            |     | 0.6            |     | ns   |

| t <sub>EABCLR</sub>    | 0.3            |     | 0.3            |     | 0.5            |     | ns   |

| t <sub>AA</sub>        |                | 3.2 |                | 3.8 |                | 5.1 | ns   |

| t <sub>WP</sub>        | 2.5            |     | 2.9            |     | 3.9            |     | ns   |

| t <sub>RP</sub>        | 0.9            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>WDSU</sub>      | 0.9            |     | 1.0            |     | 1.4            |     | ns   |

| t <sub>WDH</sub>       | 0.1            |     | 0.1            |     | 0.2            |     | ns   |

| t <sub>WASU</sub>      | 1.7            |     | 2.0            |     | 2.7            |     | ns   |

| t <sub>WAH</sub>       | 1.8            |     | 2.1            |     | 2.9            |     | ns   |

| t <sub>RASU</sub>      | 3.1            |     | 3.7            |     | 5.0            |     | ns   |

| t <sub>RAH</sub>       | 0.2            |     | 0.2            |     | 0.3            |     | ns   |

| t <sub>WO</sub>        |                | 2.5 |                | 2.9 |                | 3.9 | ns   |

| t <sub>DD</sub>        |                | 2.5 |                | 2.9 |                | 3.9 | ns   |

| t <sub>EABOUT</sub>    |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| t <sub>EABCH</sub>     | 1.5            |     | 2.0            |     | 2.5            |     | ns   |

| t <sub>EABCL</sub>     | 2.5            |     | 2.9            |     | 3.9            |     | ns   |

Tables 52 through 58 show EPF10K130E device internal and external timing parameters.

| Table 52. EPF10     | K130E Device | e LE Timing | Microparan | neters N | lote (1) |          |      |

|---------------------|--------------|-------------|------------|----------|----------|----------|------|

| Symbol              | -1 Spee      | d Grade     | -2 Spe     | ed Grade | -3 Spee  | ed Grade | Unit |

|                     | Min          | Max         | Min        | Max      | Min      | Мах      |      |

| t <sub>LUT</sub>    |              | 0.6         |            | 0.9      |          | 1.3      | ns   |

| t <sub>CLUT</sub>   |              | 0.6         |            | 0.8      |          | 1.0      | ns   |

| t <sub>RLUT</sub>   |              | 0.7         |            | 0.9      |          | 0.2      | ns   |

| t <sub>PACKED</sub> |              | 0.3         |            | 0.5      |          | 0.6      | ns   |

| t <sub>EN</sub>     |              | 0.2         |            | 0.3      |          | 0.4      | ns   |

| t <sub>CICO</sub>   |              | 0.1         |            | 0.1      |          | 0.2      | ns   |

| t <sub>CGEN</sub>   |              | 0.4         |            | 0.6      |          | 0.8      | ns   |

| t <sub>CGENR</sub>  |              | 0.1         |            | 0.1      |          | 0.2      | ns   |

| tCASC               |              | 0.6         |            | 0.9      |          | 1.2      | ns   |

| t <sub>C</sub>      |              | 0.3         |            | 0.5      |          | 0.6      | ns   |

| t <sub>CO</sub>     |              | 0.5         |            | 0.7      |          | 0.8      | ns   |

| t <sub>COMB</sub>   |              | 0.3         |            | 0.5      |          | 0.6      | ns   |

| t <sub>SU</sub>     | 0.5          |             | 0.7        |          | 0.8      |          | ns   |

| t <sub>H</sub>      | 0.6          |             | 0.7        |          | 1.0      |          | ns   |

| t <sub>PRE</sub>    |              | 0.9         |            | 1.2      |          | 1.6      | ns   |

| t <sub>CLR</sub>    |              | 0.9         |            | 1.2      |          | 1.6      | ns   |

| t <sub>CH</sub>     | 1.5          |             | 1.5        |          | 2.5      |          | ns   |

| t <sub>CL</sub>     | 1.5          |             | 1.5        |          | 2.5      |          | ns   |

Table 53. EPF10K130E Device IOE Timing Microparameters

Note (1)

| Symbol              | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | ed Grade | Unit |  |

|---------------------|---------|----------------|-----|----------------|-----|----------|------|--|

|                     | Min     | Max            | Min | Max            | Min | Max      |      |  |

| t <sub>IOD</sub>    |         | 1.3            |     | 1.5            |     | 2.0      | ns   |  |

| t <sub>IOC</sub>    |         | 0.0            |     | 0.0            |     | 0.0      | ns   |  |

| t <sub>IOCO</sub>   |         | 0.6            |     | 0.8            |     | 1.0      | ns   |  |

| t <sub>IOCOMB</sub> |         | 0.6            |     | 0.8            |     | 1.0      | ns   |  |

| t <sub>IOSU</sub>   | 1.0     |                | 1.2 |                | 1.6 |          | ns   |  |

| t <sub>IOH</sub>    | 0.9     |                | 0.9 |                | 1.4 |          | ns   |  |

| t <sub>IOCLR</sub>  |         | 0.6            |     | 0.8            |     | 1.0      | ns   |  |

| t <sub>OD1</sub>    |         | 2.8            |     | 4.1            |     | 5.5      | ns   |  |

| t <sub>OD2</sub>    |         | 2.8            |     | 4.1            |     | 5.5      | ns   |  |

| Symbol           | -1 Spee | d Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------|---------|---------|----------------|-----|----------------|-----|------|

|                  | Min     | Max     | Min            | Max | Min            | Мах |      |

| t <sub>H</sub>   | 0.9     |         | 1.1            |     | 1.5            |     | ns   |

| t <sub>PRE</sub> |         | 0.5     |                | 0.6 |                | 0.8 | ns   |

| t <sub>CLR</sub> |         | 0.5     |                | 0.6 |                | 0.8 | ns   |

| t <sub>CH</sub>  | 2.0     |         | 2.5            |     | 3.0            |     | ns   |

| t <sub>CL</sub>  | 2.0     |         | 2.5            |     | 3.0            |     | ns   |

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | ed Grade | Unit |

|---------------------|----------------|-----|----------------|-----|---------|----------|------|

|                     | Min            | Max | Min            | Max | Min     | Max      |      |

| t <sub>IOD</sub>    |                | 1.6 |                | 1.9 |         | 2.6      | ns   |

| t <sub>IOC</sub>    |                | 0.3 |                | 0.3 |         | 0.5      | ns   |

| t <sub>IOCO</sub>   |                | 1.6 |                | 1.9 |         | 2.6      | ns   |

| t <sub>IOCOMB</sub> |                | 0.5 |                | 0.6 |         | 0.8      | ns   |

| t <sub>IOSU</sub>   | 0.8            |     | 0.9            |     | 1.2     |          | ns   |

| t <sub>IOH</sub>    | 0.7            |     | 0.8            |     | 1.1     |          | ns   |

| t <sub>IOCLR</sub>  |                | 0.2 |                | 0.2 |         | 0.3      | ns   |

| t <sub>OD1</sub>    |                | 0.6 |                | 0.7 |         | 0.9      | ns   |

| t <sub>OD2</sub>    |                | 0.1 |                | 0.2 |         | 0.7      | ns   |

| t <sub>OD3</sub>    |                | 2.5 |                | 3.0 |         | 3.9      | ns   |

| t <sub>XZ</sub>     |                | 4.4 |                | 5.3 |         | 7.1      | ns   |

| t <sub>ZX1</sub>    |                | 4.4 |                | 5.3 |         | 7.1      | ns   |

| t <sub>ZX2</sub>    |                | 3.9 |                | 4.8 |         | 6.9      | ns   |

| t <sub>ZX3</sub>    |                | 6.3 |                | 7.6 |         | 10.1     | ns   |

| t <sub>INREG</sub>  |                | 4.8 |                | 5.7 |         | 7.7      | ns   |

| t <sub>IOFD</sub>   |                | 1.5 |                | 1.8 |         | 2.4      | ns   |

| t <sub>INCOMB</sub> |                | 1.5 |                | 1.8 |         | 2.4      | ns   |

| Symbol                 | -1 Spee | d Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|---------|---------|----------------|-----|----------------|-----|------|

|                        | Min     | Max     | Min            | Max | Min            | Max |      |

| t <sub>EABDATA1</sub>  |         | 2.0     |                | 2.4 |                | 3.2 | ns   |

| t <sub>EABDATA1</sub>  |         | 0.4     |                | 0.5 |                | 0.6 | ns   |

| t <sub>EABWE1</sub>    |         | 1.4     |                | 1.7 |                | 2.3 | ns   |

| t <sub>EABWE2</sub>    |         | 0.0     |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABRE1</sub>    |         | 0       |                | 0   |                | 0   | ns   |

| t <sub>EABRE2</sub>    |         | 0.4     |                | 0.5 |                | 0.6 | ns   |

| t <sub>EABCLK</sub>    |         | 0.0     |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABCO</sub>     |         | 0.8     |                | 0.9 |                | 1.2 | ns   |

| t <sub>EABBYPASS</sub> |         | 0.0     |                | 0.1 |                | 0.1 | ns   |

| t <sub>EABSU</sub>     | 0.9     |         | 1.1            |     | 1.5            |     | ns   |

| t <sub>EABH</sub>      | 0.4     |         | 0.5            |     | 0.6            |     | ns   |

| t <sub>EABCLR</sub>    | 0.8     |         | 0.9            |     | 1.2            |     | ns   |

| t <sub>AA</sub>        |         | 3.1     |                | 3.7 |                | 4.9 | ns   |

| t <sub>WP</sub>        | 3.3     |         | 4.0            |     | 5.3            |     | ns   |

| t <sub>RP</sub>        | 0.9     |         | 1.1            |     | 1.5            |     | ns   |

| t <sub>WDSU</sub>      | 0.9     |         | 1.1            |     | 1.5            |     | ns   |

| t <sub>WDH</sub>       | 0.1     |         | 0.1            |     | 0.1            |     | ns   |

| t <sub>WASU</sub>      | 1.3     |         | 1.6            |     | 2.1            |     | ns   |

| t <sub>WAH</sub>       | 2.1     |         | 2.5            |     | 3.3            |     | ns   |

| t <sub>RASU</sub>      | 2.2     |         | 2.6            |     | 3.5            |     | ns   |

| t <sub>RAH</sub>       | 0.1     |         | 0.1            |     | 0.2            |     | ns   |

| t <sub>WO</sub>        |         | 2.0     |                | 2.4 |                | 3.2 | ns   |

| t <sub>DD</sub>        |         | 2.0     |                | 2.4 |                | 3.2 | ns   |

| t <sub>EABOUT</sub>    |         | 0.0     |                | 0.1 |                | 0.1 | ns   |

| t <sub>EABCH</sub>     | 1.5     |         | 2.0            |     | 2.5            |     | ns   |

| t <sub>EABCL</sub>     | 3.3     |         | 4.0            |     | 5.3            | İ   | ns   |

Table 62. EPF10K200E Device EAB Internal Timing Macroparameters (Part 1 of 2)

| Note | (1) |

|------|-----|

|      | (1) |

| Symbol                | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|-----------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                       | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABAA</sub>    |                | 5.1 |                | 6.4 |                | 8.4 | ns   |

| t <sub>EABRCOMB</sub> | 5.1            |     | 6.4            |     | 8.4            |     | ns   |

| t <sub>EABRCREG</sub> | 4.8            |     | 5.7            |     | 7.6            |     | ns   |

| t <sub>EABWP</sub>    | 3.3            |     | 4.0            |     | 5.3            |     | ns   |

| Symbol                       | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|------------------------------|----------------|-----|----------------|-----|----------------|------|------|

|                              | Min            | Max | Min            | Max | Min            | Max  |      |

| t <sub>DRR</sub>             |                | 8.0 |                | 9.5 |                | 12.5 | ns   |

| t <sub>INSU</sub> (2)        | 2.4            |     | 2.9            |     | 3.9            |      | ns   |

| t <sub>INH</sub> (2)         | 0.0            |     | 0.0            |     | 0.0            |      | ns   |

| t <sub>оитсо</sub> (2)       | 2.0            | 4.3 | 2.0            | 5.2 | 2.0            | 7.3  | ns   |

| t <sub>INSU</sub> (3)        | 2.4            |     | 2.9            |     |                |      | ns   |

| t <sub>INH</sub> (3)         | 0.0            |     | 0.0            |     |                |      | ns   |

| <b>t<sub>оитсо (3)</sub></b> | 0.5            | 3.3 | 0.5            | 4.1 |                |      | ns   |

| t <sub>PCISU</sub>           | 2.4            |     | 2.9            |     | -              |      | ns   |

| t <sub>PCIH</sub>            | 0.0            |     | 0.0            |     | -              |      | ns   |

| t <sub>PCICO</sub>           | 2.0            | 6.0 | 2.0            | 7.7 | -              | -    | ns   |

Table 72. EPF10K50S External Bidirectional Timing Parameters

Note (1)

| Symbol                     | -1 Spee | ed Grade | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|----------------------------|---------|----------|----------------|-----|----------------|------|------|

|                            | Min     | Max      | Min            | Max | Min            | Max  |      |

| t <sub>INSUBIDIR</sub> (2) | 2.7     |          | 3.2            |     | 4.3            |      | ns   |

| t <sub>INHBIDIR</sub> (2)  | 0.0     |          | 0.0            |     | 0.0            |      | ns   |

| t <sub>inhbidir</sub> (3)  | 0.0     |          | 0.0            |     | -              |      | ns   |

| t <sub>insubidir</sub> (3) | 3.7     |          | 4.2            |     | -              |      | ns   |

| toutcobidir (2)            | 2.0     | 4.5      | 2.0            | 5.2 | 2.0            | 7.3  | ns   |

| t <sub>XZBIDIR</sub> (2)   |         | 6.8      |                | 7.8 |                | 10.1 | ns   |

| t <sub>ZXBIDIR</sub> (2)   |         | 6.8      |                | 7.8 |                | 10.1 | ns   |

| toutcobidir (3)            | 0.5     | 3.5      | 0.5            | 4.2 | -              | -    |      |

| t <sub>XZBIDIR</sub> (3)   |         | 6.8      |                | 8.4 |                | -    | ns   |

| t <sub>ZXBIDIR</sub> (3)   |         | 6.8      |                | 8.4 |                | -    | ns   |

#### Notes to tables:

(1) All timing parameters are described in Tables 24 through 30.

(2) This parameter is measured without use of the ClockLock or ClockBoost circuits.

(3) This parameter is measured with use of the ClockLock or ClockBoost circuits

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABAA</sub>     |                | 3.9 |                | 6.4 |                | 8.4 | ns   |

| t <sub>EABRCOMB</sub>  | 3.9            |     | 6.4            |     | 8.4            |     | ns   |

| t <sub>EABRCREG</sub>  | 3.6            |     | 5.7            |     | 7.6            |     | ns   |

| t <sub>EABWP</sub>     | 2.1            |     | 4.0            |     | 5.3            |     | ns   |

| t <sub>EABWCOMB</sub>  | 4.8            |     | 8.1            |     | 10.7           |     | ns   |

| t <sub>EABWCREG</sub>  | 5.4            |     | 8.0            |     | 10.6           |     | ns   |

| t <sub>EABDD</sub>     |                | 3.8 |                | 5.1 |                | 6.7 | ns   |

| t <sub>EABDATACO</sub> |                | 0.8 |                | 1.0 |                | 1.3 | ns   |

| t <sub>EABDATASU</sub> | 1.1            |     | 1.6            |     | 2.1            |     | ns   |

| t <sub>EABDATAH</sub>  | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>EABWESU</sub>   | 0.7            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>EABWEH</sub>    | 0.4            |     | 0.5            |     | 0.6            |     | ns   |

| t <sub>EABWDSU</sub>   | 1.2            |     | 1.8            |     | 2.4            |     | ns   |

| t <sub>EABWDH</sub>    | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>EABWASU</sub>   | 1.9            |     | 3.6            |     | 4.7            |     | ns   |

| t <sub>EABWAH</sub>    | 0.8            |     | 0.5            |     | 0.7            |     | ns   |

| t <sub>EABWO</sub>     |                | 3.1 |                | 4.4 |                | 5.8 | ns   |

| Symbol                   | -1 Speed Grade |     | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|--------------------------|----------------|-----|----------------|------|----------------|------|------|

|                          | Min            | Мах | Min            | Мах  | Min            | Max  |      |

| t <sub>DIN2IOE</sub>     |                | 4.4 |                | 4.8  |                | 5.5  | ns   |

| t <sub>DIN2LE</sub>      |                | 0.6 |                | 0.6  |                | 0.9  | ns   |

| t <sub>DIN2DATA</sub>    |                | 1.8 |                | 2.1  |                | 2.8  | ns   |

| t <sub>DCLK2IOE</sub>    |                | 1.7 |                | 2.0  |                | 2.8  | ns   |

| t <sub>DCLK2LE</sub>     |                | 0.6 |                | 0.6  |                | 0.9  | ns   |

| t <sub>SAMELAB</sub>     |                | 0.1 |                | 0.1  |                | 0.2  | ns   |

| t <sub>SAMEROW</sub>     |                | 3.0 |                | 4.6  |                | 5.7  | ns   |

| t <sub>SAME</sub> COLUMN |                | 3.5 |                | 4.9  |                | 6.4  | ns   |

| t <sub>DIFFROW</sub>     |                | 6.5 |                | 9.5  |                | 12.1 | ns   |

| t <sub>TWOROWS</sub>     |                | 9.5 |                | 14.1 |                | 17.8 | ns   |

| t <sub>LEPERIPH</sub>    |                | 5.5 |                | 6.2  |                | 7.2  | ns   |

| t <sub>LABCARRY</sub>    |                | 0.3 |                | 0.1  |                | 0.2  | ns   |

| Device<br>Pin-Outs  | See the Altera web site (http://www.altera.com) or the Altera Digital Library for pin-out information.                                                      |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision<br>History | The information contained in the <i>FLEX 10KE Embedded Programmable Logic Data Sheet</i> version 2.5 supersedes information published in previous versions. |

|                     | Version 2.5                                                                                                                                                 |

|                     | The following changes were made to the <i>FLEX 10KE Embedded Programmable Logic Data Sheet</i> version 2.5:                                                 |

|                     | <ul> <li><i>Note (1)</i> added to Figure 23.</li> <li>Text added to "I/O Element" section on page 34.</li> <li>Updated Table 22.</li> </ul>                 |

|                     | Version 2.4                                                                                                                                                 |

|                     | The following changes were made to the FLEX 10KE Embedded                                                                                                   |

Programmable Logic Data Sheet version 2.4: updated text on page 34 and page 63.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: lit\_reg@altera.com Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending

applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Altera Corporation

100