# E·XFL

#### NXP USA Inc. - MC56F84442VLH Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 56800EX                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 60MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                       |

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b, 8x16b                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f84442vlh |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

### 1.1 MC56F844x/5x/7x Product Family

The following table highlights major features, including features that differ among members of the family. Features not listed are shared by all members of the family.

| Part                                                                |                    |                    |                    |                    |                    |                    |                    |                    | MC5                | 6F84               |                    |                    |                    |                    |                    |                    |                    |                    |

|---------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Number                                                              | 789                | 786                | 769                | 766                | 763                | 553                | 550                | 543                | 540                | 587                | 585                | 567                | 565                | 462                | 452                | 451                | 442                | 441                |

| Core<br>frequency<br>(MHz)                                          | 100                | 100                | 100                | 100                | 100                | 80                 | 80                 | 80                 | 80                 | 80                 | 80                 | 80                 | 80                 | 60                 | 60                 | 60                 | 60                 | 60                 |

| Flash<br>memory<br>(KB)                                             | 256                | 256                | 128                | 128                | 128                | 96                 | 96                 | 64                 | 64                 | 256                | 256                | 128                | 128                | 128                | 96                 | 96                 | 64                 | 64                 |

| FlevNVM/<br>FlexRAM<br>(KB)                                         | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               |

| Total flash<br>memory,<br>including<br>FlexNVM<br>(KB) <sup>1</sup> | 288                | 288                | 160                | 160                | 160                | 128                | 128                | 96                 | 96                 | 288                | 288                | 160                | 160                | 160                | 128                | 128                | 96                 | 96                 |

| RAM (KB)                                                            | 32                 | 32                 | 24                 | 24                 | 24                 | 16                 | 16                 | 8                  | 8                  | 32                 | 32                 | 24                 | 24                 | 24                 | 16                 | 16                 | 8                  | 8                  |

| Memory<br>resource<br>protection                                    | Yes                |

| External<br>Watchdog                                                | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  |

| 12-bit<br>Cyclic ADC<br>channels                                    | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x5<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x5<br>(300<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x5<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x5<br>(600<br>ns) |

| 16-bit SAR<br>ADC (with<br>Temp<br>Sensor)<br>channels              | 1x<br>16           | 1x<br>10           | 1x<br>16           | 1x<br>10           | 1x8                | 1x8                | 0                  | 1x8                | 0                  | 1x<br>16           | 1x<br>10           | 1x<br>16           | 1x<br>10           | 0                  | 1x8                | 0                  | 1x8                | 0                  |

| PWMA<br>with input<br>capture:                                      |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |

| High-<br>resolution<br>channels                                     | 1x8                | 1x8                | 1x8                | 1x8                | 1x8                | 1x8                | 1x6                | 1x8                | 1x6                | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  |

| Table 1. 56F844x/5x | /7x Family |

|---------------------|------------|

|---------------------|------------|

Table continues on the next page ...

| Part                                                   |          |     |          |     |     |     |     |     | MC5 | 6F84     |                  |          |                  |     |     |     |     |     |

|--------------------------------------------------------|----------|-----|----------|-----|-----|-----|-----|-----|-----|----------|------------------|----------|------------------|-----|-----|-----|-----|-----|

| Number                                                 | 789      | 786 | 769      | 766 | 763 | 553 | 550 | 543 | 540 | 587      | 585              | 567      | 565              | 462 | 452 | 451 | 442 | 441 |

| Standard channels                                      | 4        | 1   | 4        | 1   | 1   | 1   | 0   | 1   | 0   | 2x<br>12 | 1x<br>12,<br>1x9 | 2x<br>12 | 1x<br>12,<br>1x9 | 1x9 | 1x9 | 1x6 | 1x9 | 1x6 |

| PWMB<br>with input<br>capture:<br>Standard<br>channels | 1x<br>12 | 1x7 | 1x<br>12 | 1x7 | 0   | 0   | 0   | 0   | 0   | 0        | 0                | 0        | 0                | 0   | 0   | 0   | 0   | 0   |

| DAC                                                    | 1        | 1   | 1        | 1   | 1   | 1   | 1   | 1   | 1   | 1        | 1                | 0        | 0                | 1   | 0   | 0   | 0   | 0   |

| Quad<br>Decoder                                        | 1        | 1   | 1        | 1   | 0   | 0   | 0   | 0   | 0   | 1        | 1                | 1        | 1                | 1   | 1   | 1   | 1   | 1   |

| DMA                                                    | Yes      | Yes | Yes      | Yes | Yes | Yes | Yes | Yes | Yes | Yes      | Yes              | Yes      | Yes              | Yes | Yes | Yes | Yes | Yes |

| CMP                                                    | 4        | 4   | 4        | 4   | 4   | 4   | 3   | 4   | 3   | 4        | 4                | 4        | 4                | 4   | 4   | 3   | 4   | 3   |

| QSCI                                                   | 3        | 3   | 3        | 3   | 2   | 2   | 2   | 2   | 2   | 3        | 3                | 3        | 3                | 2   | 2   | 2   | 2   | 2   |

| QSPI                                                   | 3        | 2   | 3        | 2   | 2   | 2   | 2   | 2   | 2   | 3        | 2                | 3        | 2                | 2   | 2   | 2   | 2   | 2   |

| I2C/SMBus                                              | 2        | 2   | 2        | 2   | 2   | 2   | 2   | 2   | 2   | 2        | 2                | 2        | 2                | 2   | 2   | 2   | 2   | 2   |

| FlexCAN                                                | 1        | 1   | 1        | 1   | 1   | 1   | 1   | 1   | 1   | 1        | 1                | 1        | 1                | 1   | 1   | 1   | 0   | 0   |

| LQFP<br>package<br>pin count                           | 100      | 80  | 100      | 80  | 64  | 64  | 48  | 64  | 48  | 100      | 80               | 100      | 80               | 64  | 64  | 48  | 64  | 48  |

Table 1. 56F844x/5x/7x Family (continued)

1. This total assumes no FlexNVM is used with FlexRAM for EEPROM.

### 1.2 56800EX 32-bit Digital Signal Controller Core

- Efficient 32-bit 56800EX Digital Signal Processor (DSP) engine with modified dual Harvard architecture

- Three internal address buses

- Four internal data buses: two 32-bit primary buses, one 16-bit secondary data bus, and one 16-bit instruction bus

- 32-bit data accesses

- Support for concurrent instruction fetches in the same cycle and dual data accesses in the same cycle

- 20 addressing modes

- As many as 60 million instructions per second (MIPS) at 60 MHz core frequency

- 162 basic instructions

- Instruction set supports both fractional arithmetic and integer arithmetic

- 32-bit internal primary data buses supporting 8-bit, 16-bit, and 32-bit data movement, addition, subtraction, and logical operation

- Single-cycle 16 × 16-bit -> 32-bit and 32 x 32-bit -> 64-bit multiplier-accumulator (MAC) with dual parallel moves

#### **1.6.7 Queued Serial Communications Interface (QSCI) Modules**

- Operating clock up to two times CPU operating frequency

- Four-word-deep FIFOs available on both transmit and receive buffers

- Standard mark/space non-return-to-zero (NRZ) format

- 13-bit integer and 3-bit fractional baud rate selection

- Full-duplex or single-wire operation

- Programmable 8-bit or 9-bit data format

- Error detection capability

- Two receiver wakeup methods:

- Idle line

- Address mark

- 1/16 bit-time noise detection

#### 1.6.8 Queued Serial Peripheral Interface (QSPI) Modules

- Maximum 25 Mbps baud rate

- Selectable baud rate clock sources for low baud rate communication

- Baud rate as low as Baudrate\_Freq\_in / 8192

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four-word-deep FIFOs available on transmit and receive buffers

- Programmable length transmissions (2 bits to 16 bits)

- Programmable transmit and receive shift order (MSB as first bit transmitted)

#### 1.6.9 Inter-Integrated Circuit (I2C)/System Management Bus (SMBus) Modules

- Compatible with I2C bus standard

- Support for System Management Bus (SMBus) specification, version2

- Multi-master operation

- General call recognition

- 10-bit address extension

- Dual slave addresses

- Programmable glitch input filter

### 1.6.10 Flex Controller Area Network (FlexCAN) Module

• Clock source from PLL or XOSC/CLKIN

- Implementation of the CAN protocol Version 2.0 A/B

- Standard and extended data frames

- 0-to-8 bytes data length

- Programmable bit rate up to 1 Mbps

- Support for remote frames

- Sixteen Message Buffers, each configurable as receive or transmit, all supporting standard and extended messages

- Individual Rx Mask Registers per Message Buffer

- Internal timer for time-stamping of received and transmitted messages

- Listen-only mode capability

- Programmable loopback mode supporting self-test operation

- Programmable transmission priority scheme: lowest ID, lowest buffer number, or highest priority

- Global network time, synchronized by a specific message

- Low power modes, with programmable wakeup on bus activity

# 1.6.11 Computer Operating Properly (COP) Watchdog

- Programmable timeout period

- Support for operation in all power modes: run mode, wait mode, stop mode

- Causes loss of reference reset 128 cycles after loss of reference clock to the PLL is detected

- Selectable reference clock source in support of EN60730 and IEC61508

- Selectable clock sources:

- External crystal oscillator/external clock source

- On-chip low-power 32 kHz oscillator

- System bus (IPBus up to 60 MHz)

- 8 MHz / 400 kHz ROSC

- Support for interrupt triggered when the counter reaches the timeout value

### 1.6.12 Power Supervisor

- Power-on reset (POR) to reset CPU, peripherals, and JTAG/EOnCE controllers (VDD > 2.1 V)

- Brownout reset (VDD < 1.9 V)

- Critical warn low voltage interrupt (LVI2.0)

- Peripheral low voltage interrupt (LVI2.7)

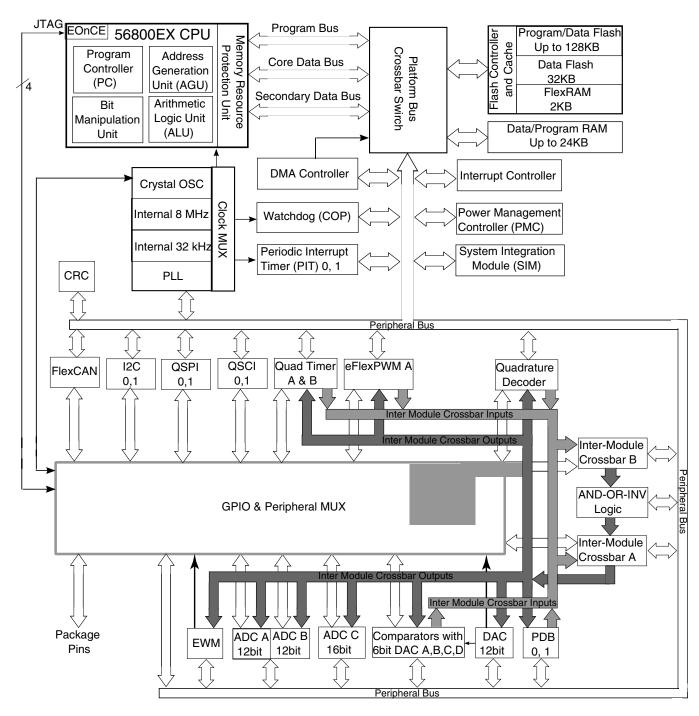

Figure 2. System Diagram

# 2 Signal groups

The input and output signals of the MC56F84xxx are organized into functional groups, as detailed in Table 2.

| Functional Group                                                      | Number<br>of Pins in<br>48LQFP | Number<br>of Pins in<br>64LQFP | Number<br>of Pins in<br>80LQFP | Number<br>of Pins in<br>100LQFP |

|-----------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|---------------------------------|

| Power Inputs (V <sub>DD</sub> , V <sub>DDA</sub> , V <sub>CAP</sub> ) | 5                              | 6                              | 6                              | 6                               |

| Ground (V <sub>SS</sub> , V <sub>SSA</sub> )                          | 4                              | 4                              | 4                              | 4                               |

| Reset                                                                 | 1                              | 1                              | 1                              | 1                               |

| eFlexPWM ports, not including fault pins                              | 6                              | 9                              | N/A                            | N/A                             |

| Queued Serial Peripheral Interface (QSPI) ports                       | 5                              | 6                              | 8                              | 15                              |

| Queued Serial Communications Interface (QSCI) ports                   | 6                              | 9                              | 13                             | 15                              |

| Inter-Integrated Circuit (I <sup>2</sup> C) interface ports           | 4                              | 6                              | 6                              | 6                               |

| 12-bit Analog-to-Digital Converter (Cyclic ADC) inputs                | 10                             | 16                             | 16                             | 16                              |

| 16-bit Analog-to-Digital Converter (SAR ADC) inputs                   | 2                              | 8                              | 10                             | 16                              |

| Analog Comparator inputs/outputs                                      | 10/4                           | 13/6                           | 13/6                           | 16/6                            |

| 12-bit Digital-to-Analog output                                       | 1                              | 1                              | 1                              | 1                               |

| Quad Timer Module (TMR) ports                                         | 6                              | 9                              | 11                             | 13                              |

| Controller Area Network (FlexCAN)                                     | 2                              | 2                              | 2                              | 2                               |

| Inter-Module Crossbar inputs/outputs                                  | 12/2                           | 16/6                           | 19/17                          | 25/19                           |

| Clock inputs/outputs                                                  | 2/2                            | 2/2                            | 2/3                            | 2/3                             |

| JTAG / Enhanced On-Chip Emulation (EOnCE)                             | 4                              | 4                              | 4                              | 4                               |

Table 2. Functional Group Pin Allocations

# 3 Ordering parts

### 3.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to www.freescale.com and perform a part number search for the following device numbers: MC56F84

# 4 Part identification

### 4.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

### 4.2 Format

Part numbers for this device have the following format: Q 56F8 4 C F P T PP N

### 4.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                                                             | Values                                                                                                      |

|-------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status                                                    | <ul> <li>MC = Fully qualified, general market flow</li> <li>PC = Prequalification</li> </ul>                |

| 56F8  | DSC family with flash memory and DSP56800/<br>DSP56800E/DSP56800EX core | • 56F8                                                                                                      |

| 4     | DSC subfamily                                                           | • 4                                                                                                         |

| С     | Maximum CPU frequency (MHz)                                             | <ul> <li>4 = 60 MHz</li> <li>5 = 80 MHz</li> <li>7 = 100 MHz</li> </ul>                                     |

| F     | Primary program flash memory size                                       | <ul> <li>4 = 64 KB</li> <li>5 = 96 KB</li> <li>6 = 128 KB</li> <li>8 = 256 KB</li> </ul>                    |

| P     | Pin count                                                               | <ul> <li>0 and 1 = 48</li> <li>2 and 3 = 64</li> <li>4, 5, and 6 = 80</li> <li>7, 8, and 9 = 100</li> </ul> |

| Т     | Temperature range (°C)                                                  | • V = -40 to 105                                                                                            |

| PP    | Package identifier                                                      | <ul> <li>LF = 48LQFP</li> <li>LH = 64LQFP</li> <li>LK = 80LQFP</li> <li>LL = 100LQFP</li> </ul>             |

| Ν     | Packaging type                                                          | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                                              |

# 4.4 Example

This is an example part number: MC56F84789VLL

# 5 Terminology and guidelines

### 5.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

#### 5.1.1 Example

This is an example of an operating requirement, which you must meet for the accompanying operating behaviors to be guaranteed:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

### 5.2 Definition: Operating behavior

An *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

### 5.2.1 Example

This is an example of an operating behavior, which is guaranteed if you meet the accompanying operating requirements:

| Symbol | Description                                  | Min. | Max. | Unit |

|--------|----------------------------------------------|------|------|------|

|        | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μA   |

### 5.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

#### 5.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

# 5.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

### 5.4.1 Example

This is an example of an operating rating:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 | 1.2  | V    |

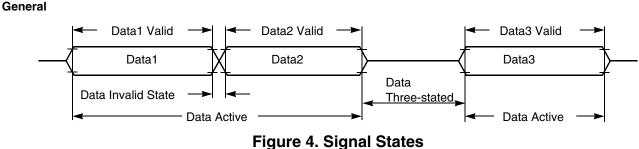

Figure 4. Signal States

### 7.3 Nonswitching electrical specifications

#### 7.3.1 Voltage and current operating requirements

This section includes information about recommended operating conditions.

Recommended  $V_{DD}$  ramp rate is between 1 ms and 200 ms.

NOTE

| Table 5. | Recommended Operating Conditions ( $V_{REFLx} = 0 V$ , $V_{SSA} = 0 V$ , |

|----------|--------------------------------------------------------------------------|

|          | $V_{SS} = 0 V$ )                                                         |

| Characteristic                                                    | Symbol                             | Notes <sup>1</sup> | Min                   | Тур | Мах                    | Unit |

|-------------------------------------------------------------------|------------------------------------|--------------------|-----------------------|-----|------------------------|------|

| Supply voltage <sup>2</sup>                                       | V <sub>DD</sub> , V <sub>DDA</sub> |                    | 2.7                   | 3.3 | 3.6                    | V    |

| ADC (Cyclic) Reference Voltage High                               | V <sub>REFHA</sub>                 |                    | 3.0                   |     | V <sub>DDA</sub>       | V    |

|                                                                   | V <sub>REFHB</sub>                 |                    |                       |     |                        |      |

| ADC (SAR) Reference Voltage High                                  | V <sub>REFHC</sub>                 |                    | 2.0                   |     | V <sub>DDA</sub>       | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub>            | ΔVDD                               |                    | -0.1                  | 0   | 0.1                    | V    |

| Voltage difference $V_{SS}$ to $V_{SSA}$                          | ΔVSS                               |                    | -0.1                  | 0   | 0.1                    | V    |

| Input Voltage High (digital inputs)                               | VIH                                | Pin Groups 1, 2    | 0.7 x V <sub>DD</sub> |     | 5.5                    | V    |

| Input Voltage Low (digital inputs)                                | V <sub>IL</sub>                    | Pin Groups 1, 2    |                       |     | 0.35 x V <sub>DD</sub> | V    |

| Oscillator Input Voltage High                                     | VIHOSC                             | Pin Group 4        | 2.0                   |     | V <sub>DD</sub> + 0.3  | V    |

| XTAL driven by an external clock source                           |                                    |                    |                       |     |                        |      |

| Oscillator Input Voltage Low                                      | VILOSC                             | Pin Group 4        | -0.3                  |     | 0.8                    | V    |

| Output Source Current High (at V <sub>OH</sub> min.) <sup>3</sup> | I <sub>ОН</sub>                    |                    |                       |     |                        |      |

| <ul> <li>Programmed for low drive strength</li> </ul>             |                                    | Pin Group 1        | _                     |     | -2                     | mA   |

| <ul> <li>Programmed for high drive strength</li> </ul>            |                                    | Pin Group 1        | _                     |     | -9                     |      |

| Output Source Current Low (at V <sub>OL</sub> max.) <sup>3</sup>  | I <sub>OL</sub>                    |                    |                       |     |                        |      |

| <ul> <li>Programmed for low drive strength</li> </ul>             |                                    | Pin Groups 1, 2    | _                     |     | 2                      | mA   |

| <ul> <li>Programmed for high drive strength</li> </ul>            |                                    | Pin Groups 1, 2    | _                     |     | 9                      |      |

#### 1. Default Mode

- Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- Pin Group 2: RESET, GPIOA7

- Pin Group 3: ADC and Comparator Analog Inputs

# 7.3.5 Power consumption operating behaviors

|  | Table 9. | Current | Consum | otion |

|--|----------|---------|--------|-------|

|--|----------|---------|--------|-------|

| Mode Maximum<br>Frequency |        |                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | at 3.3 V,<br>°C  | Maximum at 3.6<br>V, 105°C |                  |

|---------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|----------------------------|------------------|

|                           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | I <sub>DDA</sub> | I <sub>DD</sub> 1          | I <sub>DDA</sub> |

| RUN                       | 60 MHz | <ul> <li>60 MHz Device Clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> <li>PLL powered on</li> <li>Continuous MAC instructions with fetches from<br/>Program Flash</li> <li>All peripheral modules enabled.</li> <li>TMRs and SCIs using 1X Clock</li> <li>NanoEdge within PWMA using 2X clock</li> <li>ADC/DAC powered on and clocked at 5 MHz<sup>2</sup></li> <li>Comparator powered on</li> </ul> | TBD | TBD              | TBD                        | TBD              |

| WAIT                      | 60 MHz | <ul> <li>60 MHz Device Clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> <li>PLL powered on</li> <li>Processor Core in WAIT state</li> <li>All Peripheral modules enabled.</li> <li>TMRs and SCIs using 1X Clock</li> <li>NanoEdge within PWMA using 2X clock</li> <li>ADC/DAC/Comparator powered off</li> </ul>                                                                                        | TBD | TBD              | TBD                        | TBD              |

| STOP                      | 4 MHz  | <ul> <li>4 MHz Device Clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> <li>PLL powered off</li> <li>Processor Core in STOP state</li> <li>All peripheral module and core clocks are off</li> <li>ADC/DAC/Comparator powered off</li> </ul>                                                                                                                                                             | TBD | TBD              | TBD                        | TBD              |

| LPRUN<br>(LsRUN)          | 2 MHz  | <ul> <li>200 kHz Device Clock from Relaxation Oscillator<br/>(ROSC)</li> <li>ROSC in standby mode</li> <li>Regulators are in standby</li> <li>PLL disabled</li> <li>Repeat NOP instructions</li> <li>All peripheral modules enabled, except NanoEdge<br/>and cyclic ADCs<sup>3</sup></li> <li>Simple loop with running from platform instruction<br/>buffer</li> </ul>                                                                        | TBD | TBD              | TBD                        | TBD              |

| LPWAIT<br>(LsWAIT)        | 2 MHz  | <ul> <li>200 kHz Device Clock from Relaxation Oscillator<br/>(ROSC)</li> <li>ROSC in standby mode</li> <li>Regulators are in standby</li> <li>PLL disabled</li> <li>All peripheral modules enabled, except NanoEdge<br/>and cyclic ADCs<sup>3</sup></li> <li>Processor core in wait mode</li> </ul>                                                                                                                                           | TBD | TBD              | TBD                        | TBD              |

Table continues on the next page ...

#### General

| Mode               | Maximum<br>Frequency | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   | at 3.3 V,<br>°C  |                   | ım at 3.6<br>05°C |

|--------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-------------------|-------------------|

|                    |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>DD</sub> 1 | I <sub>DDA</sub> | I <sub>DD</sub> 1 | I <sub>DDA</sub>  |

| LPSTOP<br>(LsSTOP) | 2 MHz                | <ul> <li>200 kHz Device Clock from Relaxation Oscillator<br/>(ROSC)</li> <li>ROSC in standby mode</li> <li>Regulators are in standby</li> <li>PLL disabled</li> <li>Only PITs and COP enabled; other peripheral<br/>modules disabled and clocks gated off<sup>3</sup></li> <li>Processor core in stop mode</li> </ul>                                                                                                                        | TBD               | TBD              | TBD               | TBD               |

| VLPRUN             | 200 kHz              | <ul> <li>32 kHz Device Clock</li> <li>Clocked by a 32 kHz external clock source</li> <li>Oscillator in power down</li> <li>All ROSCs disabled</li> <li>Large regulator is in standby</li> <li>Small regulator is disabled</li> <li>PLL disabled</li> <li>Repeat NOP instructions</li> <li>All peripheral modules, except COP and EWM, disabled and clocks gated off</li> <li>Simple loop running from platform instruction buffer</li> </ul> | TBD               | TBD              | TBD               | TBD               |

| VLPWAIT            | 200 kHz              | <ul> <li>32 kHz Device Clock</li> <li>Clocked by a 32 kHz external clock source</li> <li>Oscillator in power down</li> <li>All ROSCs disabled</li> <li>Large regulator is in standby</li> <li>Small regulator is disabled</li> <li>PLL disabled</li> <li>All peripheral modules, except COP, disabled and clocks gated off</li> <li>Processor core in wait mode</li> </ul>                                                                   | TBD               | TBD              | TBD               | TBD               |

| VLPSTOP            | 200 kHz              | <ul> <li>32 kHz Device Clock</li> <li>Clocked by a 32 kHz external clock source</li> <li>Oscillator in power down</li> <li>All ROSCs disabled</li> <li>Large regulator is in standby</li> <li>Small regulator is disabled</li> <li>PLL disabled</li> <li>All peripheral modules, except COP, disabled and clocks gated off</li> <li>Processor core in stop mode</li> </ul>                                                                   | TBD               | TBD              | TBD               | TBD               |

Table 9. Current Consumption (continued)

1. No output switching, all ports configured as inputs, all inputs low, no DC loads

- 2. ADC power consumption at higher frequency can be found in Table 26

- 3. In all chip LP modes and flash memory VLP modes, the maximum frequency for flash memory operation is 500 kHz due to the fixed frequency ratio of 1:4 between the CPU clock and the flash clock.

#### Peripheral operating requirements and behaviors

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air) with the single layer board horizontal. For the LQFP, the board meets the JESD51-3 specification.

- 3. Determined according to JEDEC Standard JESD51-6, *Integrated Circuits Thermal Test Method Environmental Conditions Forced Convection (Moving Air)* with the board horizontal.

- 4. Determined according to JEDEC Standard JESD51-8, *Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board*. Board temperature is measured on the top surface of the board near the package.

- 5. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 6. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

# 8 Peripheral operating requirements and behaviors

#### 8.1 Core modules

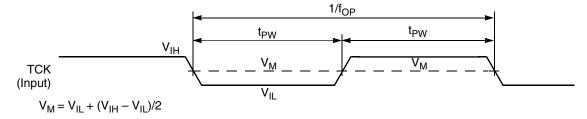

#### 8.1.1 JTAG Timing

|                            |                 | 5   |           |      |               |

|----------------------------|-----------------|-----|-----------|------|---------------|

| Characteristic             | Symbol          | Min | Мах       | Unit | See<br>Figure |

| TCK frequency of operation | f <sub>OP</sub> | DC  | SYS_CLK/8 | MHz  | Figure 5      |

| TCK clock pulse width      | t <sub>PW</sub> | 50  |           | ns   | Figure 5      |

| TMS, TDI data set-up time  | t <sub>DS</sub> | 5   | _         | ns   | Figure 6      |

| TMS, TDI data hold time    | t <sub>DH</sub> | 5   |           | ns   | Figure 6      |

| TCK low to TDO data valid  | t <sub>DV</sub> | —   | 30        | ns   | Figure 6      |

| TCK low to TDO tri-state   | t <sub>TS</sub> | —   | 30        | ns   | Figure 6      |

Figure 5. Test Clock Input Timing Diagram

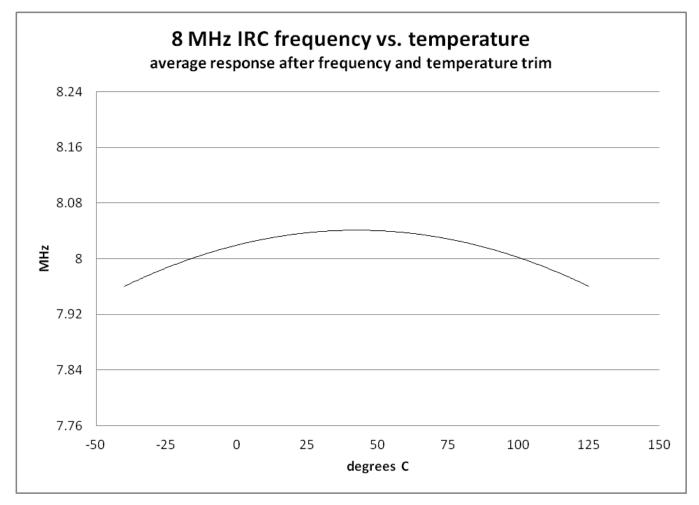

Figure 8. Relaxation Oscillator Temperature Variation (Typical) After Trim (Preliminary)

### 8.4 Memories and memory interfaces

#### 8.4.1 Flash Memory Characteristics Table 22. Flash Timing Parameters

| Characteristic                                  | Symbol        | Min | Тур | Max | Unit |

|-------------------------------------------------|---------------|-----|-----|-----|------|

| Longword Program high-voltage time <sup>1</sup> | thvpgm4       | —   | 63  | 143 | μs   |

| Sector Erase high-voltage time <sup>2</sup>     | thversscr     | —   | 13  | 113 | ms   |

| Erase Block high-voltage time for 256 KB        | thversblk256k | —   | 52  | 452 | ms   |

1. There is additional overhead that is part of the programming sequence. See the device Reference Manual for detail.

2. Specifies page erase time.

7. For guidelines and examples of conversion rate calculation, download the ADC calculator tool: http://cache.freescale.com/ files/soft\_dev\_tools/software/app\_software/converters/ADC\_CALCULATOR\_CNV.zip?fpsp=1

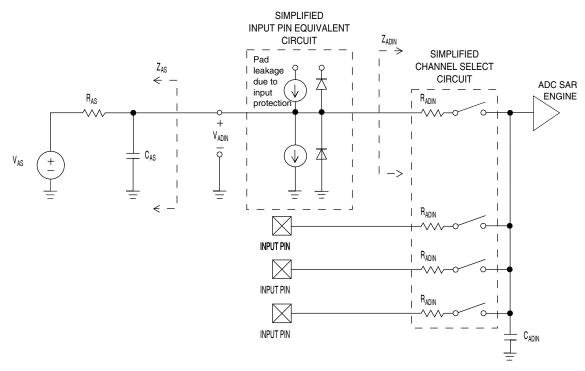

Figure 10. ADC input impedance equivalency diagram

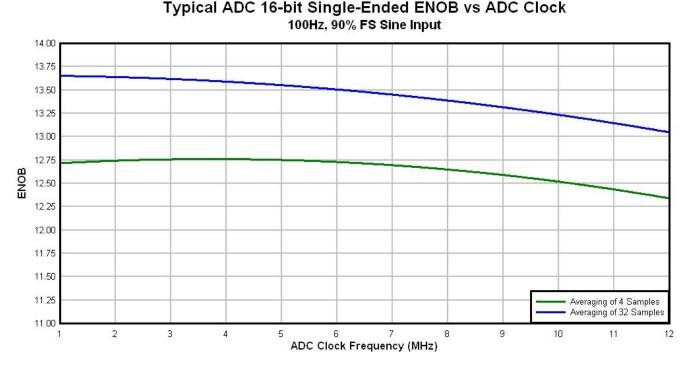

#### 8.5.2.2 16-bit ADC electrical characteristics Table 27. 16-bit ADC characteristics (V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> = V<sub>SSA</sub>)

| Symbol               | Description                  | Conditions <sup>1</sup>              | Min.           | Typ. <sup>2</sup> | Max.         | Unit             | Notes              |

|----------------------|------------------------------|--------------------------------------|----------------|-------------------|--------------|------------------|--------------------|

| I <sub>DDA_ADC</sub> | Supply current               |                                      |                | —                 | 1.7          | mA               | 3                  |

|                      | ADC                          | ADLPC=1, ADHSC=0                     | 1.2            | 2.4               | 3.9          | MHz              | $t_{ADACK} = 1/$   |

|                      | asynchronous<br>clock source | ADLPC=1, ADHSC=1                     | 3.0            | 4.0               | 7.3          | MHz              | f <sub>ADACK</sub> |

| f <sub>ADACK</sub>   |                              | ADLPC=0, ADHSC=0                     | 2.4            | 5.2               | 6.1          | MHz              |                    |

|                      |                              | ADLPC=0, ADHSC=1                     | 4.4            | 6.2               | 9.5          | MHz              |                    |

|                      | Sample Time                  | See Reference Manual chapter         | r for sample t | imes              |              |                  |                    |

| TUE                  | Total unadjusted             | 12 bit modes                         | _              | ±4                | ±6.8         | LSB <sup>4</sup> | 5                  |

|                      | error                        | • <12 bit modes                      |                | ±1.4              | ±2.1         |                  |                    |

| DNL                  | Differential non-            | 16 bit modes                         | _              | -1 to +4          |              | LSB <sup>4</sup> | 5                  |

|                      | linearity                    | 12 bit modes                         | _              | ±0.7              | TBD          |                  |                    |

|                      |                              | • <12 bit modes                      | _              | ±0.2              | -0.3 to 0.5  |                  |                    |

| INL                  | Integral non-                | 16 bit modes                         | _              | ±7.0              |              | LSB <sup>4</sup> | 5                  |

|                      | linearity                    | 12 bit modes                         | —              | ±1.0              | -2.7 to +1.9 |                  |                    |

|                      |                              | <ul> <li>&lt;12 bit modes</li> </ul> |                | ±0.5              | -0.7 to +0.5 |                  |                    |

Table continues on the next page...

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and the ADLPC bit (low power). For lowest power operation the ADLPC bit should be set, the HSC bit should be clear with 1MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{\text{REFH}} V_{\text{REFL}})/2^N$

- 5. ADC conversion clock <16MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock <12MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock <12MHz.

- 8. System Clock = 4 MHz, ADC Clock = 2 MHz, AVG = Max, Long Sampling = Max

Figure 11. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

#### 8.5.3 12-bit Digital-to-Analog Converter (DAC) Parameters Table 28. DAC Parameters

| Parameter                  | Conditions/Comments                                             | Symbol            | Min | Тур | Max | Unit |  |  |

|----------------------------|-----------------------------------------------------------------|-------------------|-----|-----|-----|------|--|--|

| DC Specifications          |                                                                 |                   |     |     |     |      |  |  |

| Resolution                 |                                                                 |                   | 12  | 12  | 12  | bits |  |  |

| Settling time <sup>1</sup> | At output load                                                  |                   | —   | 1   |     | μs   |  |  |

|                            | $RLD = 3 k\Omega$                                               |                   |     |     |     |      |  |  |

| CLD = 400 pf               |                                                                 |                   |     |     |     |      |  |  |

| Power-up time              | Time from release of PWRDWN signal until DACOUT signal is valid | t <sub>DAPU</sub> | _   | _   | 11  | μs   |  |  |

|                            | Αςςι                                                            | iracy             |     |     |     |      |  |  |

Table continues on the next page...

**PWMs and timers**

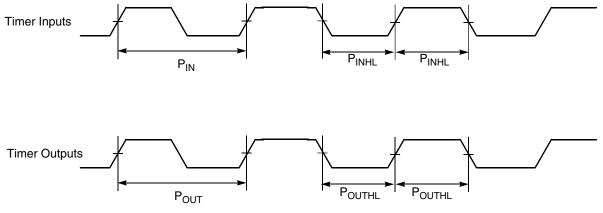

| Characteristic               | Symbol            | Min <sup>1</sup> | Max | Unit | See Figure |

|------------------------------|-------------------|------------------|-----|------|------------|

| Timer input period           | P <sub>IN</sub>   | 2T + 6           | —   | ns   | Figure 14  |

| Timer input high/low period  | P <sub>INHL</sub> | 1T + 3           | —   | ns   | Figure 14  |

| Timer output period          | P <sub>OUT</sub>  | 33               | —   | ns   | Figure 14  |

| Timer output high/low period | POUTHL            | 16.7             |     | ns   | Figure 14  |

Table 31. Timer Timing

1. T = clock cycle. For 60 MHz operation, T = 16.7 ns.

Figure 14. Timer Timing

#### 8.7 Communication interfaces

#### 8.7.1 Queued Serial Peripheral Interface (SPI) Timing

Parameters listed are guaranteed by design.

| Characteristic   | Symbol           | Min  | Max | Unit | See Figure |

|------------------|------------------|------|-----|------|------------|

| Cycle time       | t <sub>C</sub>   |      |     |      | Figure 15  |

| Master           |                  | 55   | _   | ns   | Figure 16  |

| Slave            |                  | 55   | _   | ns   | Figure 17  |

|                  |                  |      |     |      | Figure 18  |

| Enable lead time | t <sub>ELD</sub> |      |     |      | Figure 18  |

| Master           |                  | _    | _   | ns   |            |

| Slave            |                  | 17.5 | _   | ns   |            |

| Enable lag time  | t <sub>ELG</sub> |      |     |      | Figure 18  |

| Master           |                  | _    | —   | ns   |            |

| Slave            |                  | 17.5 | _   | ns   |            |

Table continues on the next page...

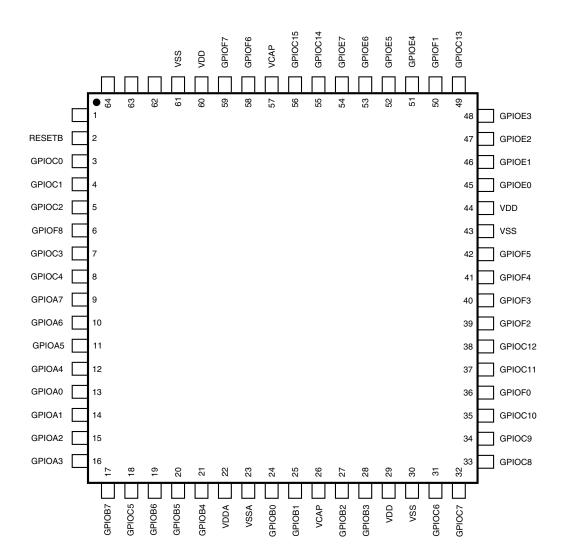

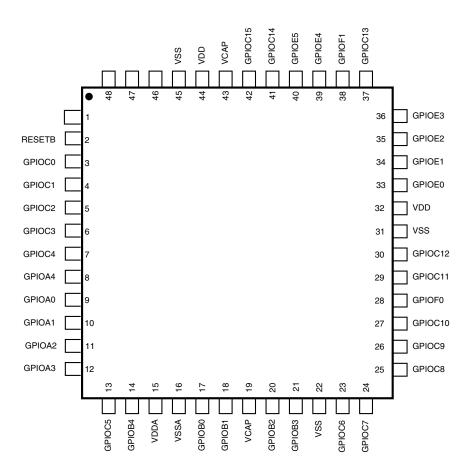

Figure 23. 64-pin LQFP

### **12 Product Documentation**

The documents listed in Table 36 are required for a complete description and proper design with the device. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, or online at http://www.freescale.com.

MC56F844xx Advance Information Data Sheet, Rev. 2, 06/2012.

Freescale Semiconductor, Inc.

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductors products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claims alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-complaint and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

$\label{eq:FreescaleTM} Freescale TM and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.$

© 2012 Freescale Semiconductor, Inc.

Document Number: MC56F844XX Rev. 2, 06/2012 Preliminary General Business Information