Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | 56800EX                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 60MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                        |

| Number of I/O              | 54                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b, 8x16b                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f84442vlhr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

# 1.1 MC56F844x/5x/7x Product Family

The following table highlights major features, including features that differ among members of the family. Features not listed are shared by all members of the family.

| Part                                                                |                    | MC56F84            |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |

|---------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Number                                                              | 789                | 786                | 769                | 766                | 763                | 553                | 550                | 543                | 540                | 587                | 585                | 567                | 565                | 462                | 452                | 451                | 442                | 441                |

| Core<br>frequency<br>(MHz)                                          | 100                | 100                | 100                | 100                | 100                | 80                 | 80                 | 80                 | 80                 | 80                 | 80                 | 80                 | 80                 | 60                 | 60                 | 60                 | 60                 | 60                 |

| Flash<br>memory<br>(KB)                                             | 256                | 256                | 128                | 128                | 128                | 96                 | 96                 | 64                 | 64                 | 256                | 256                | 128                | 128                | 128                | 96                 | 96                 | 64                 | 64                 |

| FlevNVM/<br>FlexRAM<br>(KB)                                         | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               | 32/2               |

| Total flash<br>memory,<br>including<br>FlexNVM<br>(KB) <sup>1</sup> | 288                | 288                | 160                | 160                | 160                | 128                | 128                | 96                 | 96                 | 288                | 288                | 160                | 160                | 160                | 128                | 128                | 96                 | 96                 |

| RAM (KB)                                                            | 32                 | 32                 | 24                 | 24                 | 24                 | 16                 | 16                 | 8                  | 8                  | 32                 | 32                 | 24                 | 24                 | 24                 | 16                 | 16                 | 8                  | 8                  |

| Memory<br>resource<br>protection                                    | Yes                |

| External<br>Watchdog                                                | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  |

| 12-bit<br>Cyclic ADC<br>channels                                    | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x5<br>(300<br>ns) | 2x8<br>(300<br>ns) | 2x5<br>(300<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x5<br>(600<br>ns) | 2x8<br>(600<br>ns) | 2x5<br>(600<br>ns) |

| 16-bit SAR<br>ADC (with<br>Temp<br>Sensor)<br>channels              | 1x<br>16           | 1x<br>10           | 1x<br>16           | 1x<br>10           | 1x8                | 1x8                | 0                  | 1x8                | 0                  | 1x<br>16           | 1x<br>10           | 1x<br>16           | 1x<br>10           | 0                  | 1x8                | 0                  | 1x8                | 0                  |

| PWMA<br>with input<br>capture:                                      |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |

| High-<br>resolution<br>channels                                     | 1x8                | 1x8                | 1x8                | 1x8                | 1x8                | 1x8                | 1x6                | 1x8                | 1x6                | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  |

| Table 1. 56F844x/5x | /7x Family |

|---------------------|------------|

|---------------------|------------|

Table continues on the next page ...

| Part                                                   |          | MC56F84 |          |     |     |     |     |     |     |          |                  |          |                  |     |     |     |     |     |

|--------------------------------------------------------|----------|---------|----------|-----|-----|-----|-----|-----|-----|----------|------------------|----------|------------------|-----|-----|-----|-----|-----|

| Number                                                 | 789      | 786     | 769      | 766 | 763 | 553 | 550 | 543 | 540 | 587      | 585              | 567      | 565              | 462 | 452 | 451 | 442 | 441 |

| Standard channels                                      | 4        | 1       | 4        | 1   | 1   | 1   | 0   | 1   | 0   | 2x<br>12 | 1x<br>12,<br>1x9 | 2x<br>12 | 1x<br>12,<br>1x9 | 1x9 | 1x9 | 1x6 | 1x9 | 1x6 |

| PWMB<br>with input<br>capture:<br>Standard<br>channels | 1x<br>12 | 1x7     | 1x<br>12 | 1x7 | 0   | 0   | 0   | 0   | 0   | 0        | 0                | 0        | 0                | 0   | 0   | 0   | 0   | 0   |

| DAC                                                    | 1        | 1       | 1        | 1   | 1   | 1   | 1   | 1   | 1   | 1        | 1                | 0        | 0                | 1   | 0   | 0   | 0   | 0   |

| Quad<br>Decoder                                        | 1        | 1       | 1        | 1   | 0   | 0   | 0   | 0   | 0   | 1        | 1                | 1        | 1                | 1   | 1   | 1   | 1   | 1   |

| DMA                                                    | Yes      | Yes     | Yes      | Yes | Yes | Yes | Yes | Yes | Yes | Yes      | Yes              | Yes      | Yes              | Yes | Yes | Yes | Yes | Yes |

| CMP                                                    | 4        | 4       | 4        | 4   | 4   | 4   | 3   | 4   | 3   | 4        | 4                | 4        | 4                | 4   | 4   | 3   | 4   | 3   |

| QSCI                                                   | 3        | 3       | 3        | 3   | 2   | 2   | 2   | 2   | 2   | 3        | 3                | 3        | 3                | 2   | 2   | 2   | 2   | 2   |

| QSPI                                                   | 3        | 2       | 3        | 2   | 2   | 2   | 2   | 2   | 2   | 3        | 2                | 3        | 2                | 2   | 2   | 2   | 2   | 2   |

| I2C/SMBus                                              | 2        | 2       | 2        | 2   | 2   | 2   | 2   | 2   | 2   | 2        | 2                | 2        | 2                | 2   | 2   | 2   | 2   | 2   |

| FlexCAN                                                | 1        | 1       | 1        | 1   | 1   | 1   | 1   | 1   | 1   | 1        | 1                | 1        | 1                | 1   | 1   | 1   | 0   | 0   |

| LQFP<br>package<br>pin count                           | 100      | 80      | 100      | 80  | 64  | 64  | 48  | 64  | 48  | 100      | 80               | 100      | 80               | 64  | 64  | 48  | 64  | 48  |

Table 1. 56F844x/5x/7x Family (continued)

1. This total assumes no FlexNVM is used with FlexRAM for EEPROM.

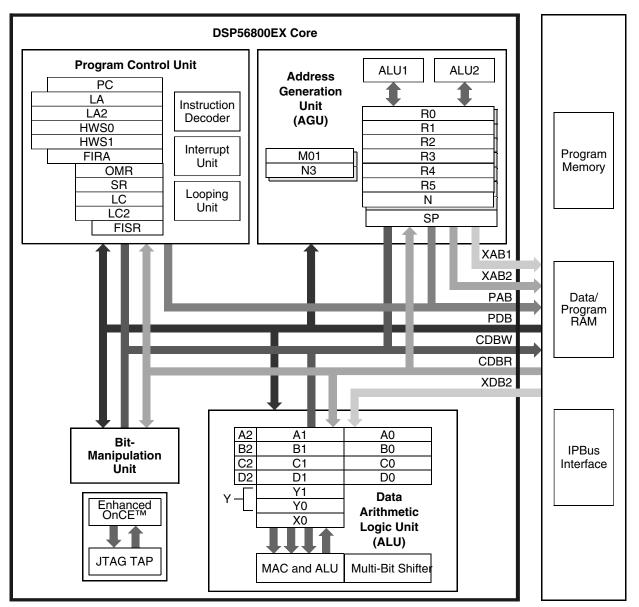

# 1.2 56800EX 32-bit Digital Signal Controller Core

- Efficient 32-bit 56800EX Digital Signal Processor (DSP) engine with modified dual Harvard architecture

- Three internal address buses

- Four internal data buses: two 32-bit primary buses, one 16-bit secondary data bus, and one 16-bit instruction bus

- 32-bit data accesses

- Support for concurrent instruction fetches in the same cycle and dual data accesses in the same cycle

- 20 addressing modes

- As many as 60 million instructions per second (MIPS) at 60 MHz core frequency

- 162 basic instructions

- Instruction set supports both fractional arithmetic and integer arithmetic

- 32-bit internal primary data buses supporting 8-bit, 16-bit, and 32-bit data movement, addition, subtraction, and logical operation

- Single-cycle 16 × 16-bit -> 32-bit and 32 x 32-bit -> 64-bit multiplier-accumulator (MAC) with dual parallel moves

#### Overview

- 32-bit arithmetic and logic multi-bit shifter

- Four 36-bit accumulators, including extension bits

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Bit reverse address mode, effectively supporting DSP and Fast Fourier Transform algorithms

- Full shadowing of the register stack for zero-overhead context saves and restores: nine shadow registers corresponding to the R0, R1, R2, R3, R4, R5, N, N3, and M01 address registers

- Instruction set supporting both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Enhanced bit manipulation instruction set

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- Priority level setting for interrupt levels

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, real-time debugging that is independent of processor speed

# **1.3 Operation Parameters**

- Up to 60 MHz operation at -40 °C to 105 °C ambient temperature

- Single 3.3 V power supply

- Supply range:  $V_{DD}$   $V_{SS}$  = 2.7 V to 3.6 V,  $V_{DDA}$   $V_{SSA}$  = 2.7 V to 3.6 V

# 1.4 On-Chip Memory and Memory Protection

- Modified dual Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Internal flash memory with security and protection to prevent unauthorized access

- Memory resource protection (MRP) unit to protect supervisor programs and resources from user programs

- Programming code can reside in flash memory during flash programming

- The dual-ported RAM controller supports concurrent instruction fetches and data accesses, or dual data accesses, by the DSC core.

- Concurrent accesses provide increased performance.

- The data and instruction arrive at the core in the same cycle, reducing latency.

- On-chip memory

- Up to 128 KW program/data flash memory

- Up to 16 KW dual port data/program RAM

MC56F844xx Advance Information Data Sheet, Rev. 2, 06/2012.

- Up to 16 KW FlexNVM, which can be used as additional program or data flash memory

- Up to 1 KW FlexRAM, which can be configured as enhanced EEPROM (used in conjunction with FlexNVM) or used as additional RAM

# 1.5 Interrupt Controller

- Five interrupt priority levels

- Three user programmable priority levels for each interrupt source: level 0, 1, 2

- Unmaskable level 3 interrupts include: illegal instruction, hardware stack overflow, misaligned data access, SWI3 instruction

- Maskable level 3 interrupts include: EOnCE step counter, EOnCE breakpoint unit, EOnCE trace buffer

- Lowest-priority software interrupt: level LP

- Support for nested interrupt: higher priority level interrupt request can interrupt lower priority interrupt subroutine

- Masking of interrupt priority level managed by the 56800EX core

- Two programmable fast interrupts that can be assigned to any interrupt source

- Notification to System Integration Module (SIM) to restart clock when in wait and stop states

- Ability to relocate interrupt vector table

# 1.6 Peripheral highlights

# 1.6.1 Enhanced Flex Pulse Width Modulator (eFlexPWM)

- Up to 12 output channels in each module

- 16 bits of resolution for center, edge aligned, and asymmetrical PWMs

- PWMA with accumulative fractional clock calculation

- Accumulative fractional clock calculation improves the resolution of the PWM period and edge placement

- Arbitrary PWM edge placement

- Equivalent to 312 ps PWM frequency and duty-cycle resolution on average

- Each complementary pair can operate with its own PWM frequency base and deadtime values

- 4 time base in each PWM module

- Independent top and bottom deadtime insertion for each complementary pair

- PWM outputs can operate as complementary pairs or independent channels

- Independent control of both edges of each PWM output

#### Peripheral highlights

- Enhanced input capture and output compare functionality on each input

- Channels not used for PWM generation can be used for buffered output compare functions

- Channels not used for PWM generation can be used for input capture functions

- Enhanced dual edge capture functionality

- Synchronization to external hardware or other PWM supported

- Double buffered PWM registers

- Integral reload rates from 1 to 16

- Half-cycle reload capability

- Multiple output trigger events can be generated per PWM cycle via hardware

- Support for double switching PWM outputs

- Up to eight fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Individual software control of each PWM output

- All outputs can be programmed to change simultaneously via a FORCE\_OUT event

- PWMX pin can optionally output a third PWM signal from each submodule

- Option to supply the source for each complementary PWM signal pair from any of the following:

- Crossbar module outputs

- External ADC input, taking into account values set in ADC high and low limit registers

# 1.6.2 12-bit Analog-to-Digital Converter (Cyclic type)

- Two independent 12-bit analog-to-digital converters (ADCs)

- 2 x 8-channel external inputs

- Built-in x1, x2, x4 programmable gain pre-amplifier

- Maximum ADC clock frequency is up to 20 MHz with 50 ns period

- Single conversion time of 8.5 ADC clock cycles

- Additional conversion time of 6 ADC clock cycles

- Sequential, parallel, and independent scan mode

- First 8 samples have offset, limit and zero-crossing calculation supported

- ADC conversions can be synchronized by any module connected to internal crossbar module, such as PWM and timer modules and GPIO and comparators

- Support for simultaneous and software triggering conversions

- Support for multi-triggering mode with a programmable number of conversions on each trigger

- Each ADC has ability to scan and store up to 8 conversion results

### 1.6.3 Inter-Module Crossbar and AND-OR-INVERT logic

- Provides generalized connections between and among on-chip peripherals: ADCs, 12-bit DAC, Comparators, Quad Timers, eFlexPWMs, PDBs, EWM, Quadrature Decoder, and select I/O pins

- User-defined input/output pins for all modules connected to crossbar

- DMA request and interrupt generation from crossbar

- Write-once protection for all registers

- AND-OR-INVERT function that provides a universal Boolean function generator using a four-term sum-of-products expression, with each product term containing true or complement values of the four selected inputs (A, B, C, D).

### 1.6.4 Comparator

- Full rail-to-rail comparison range

- Support for high speed mode and low speed mode

- Selectable input source includes external pins and internal DACs

- Programmable output polarity

- 6-bit programmable DAC as voltage reference per comparator

- Three programmable hysteresis levels

- Selectable interrupt on rising edge, falling edge, or toggle of comparator output

### 1.6.5 12-bit Digital-to-Analog Converter

- 12-bit resolution

- Powerdown mode

- Automatic mode allows the DAC to automatically generate pre-programmed output waveforms including square, triangle, and sawtooth waveforms for applications such as slope compensation

- Programmable period, update rate, and range

- Output can be routed to an internal comparator, ADC, or optionally off chip

### 1.6.6 Quad Timer

- Four 16-bit up/down counters with programmable prescaler for each counter

- Operation modes: edge count, gated count, signed count, capture, compare, PWM, signal shot, single pulse, pulse string, cascaded, quadrature decode

- Programmable input filter

- Counting start can be synchronized across counters

**Clock sources**

Figure 1. 56800EX Basic Block Diagram

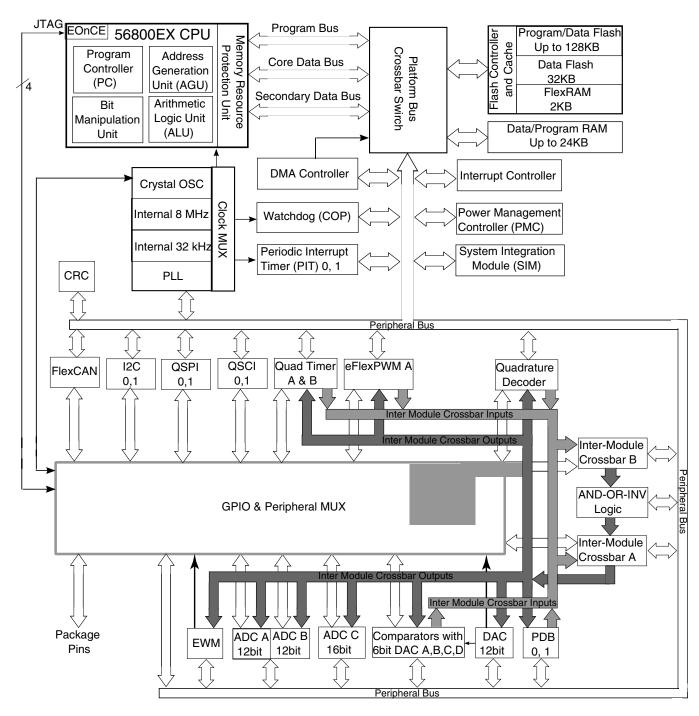

Figure 2. System Diagram

# 6.3 ESD handling ratings

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, use normal handling precautions to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM), and the charge device model (CDM).

All latch-up testing is in conformity with AEC-Q100 Stress Test Qualification.

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Characteristic <sup>1</sup>                      | Min   | Max   | Unit |

|--------------------------------------------------|-------|-------|------|

| ESD for Human Body Model (HBM)                   | -2000 | +2000 | V    |

| ESD for Machine Model (MM)                       | -200  | +200  | V    |

| ESD for Charge Device Model (CDM)                | -500  | +500  | V    |

| Latch-up current at TA= 85°C (I <sub>LAT</sub> ) | -100  | +100  | mA   |

Table 3. ESD/Latch-up Protection

1. Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

# 6.4 Voltage and current operating ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 4 may affect device reliability or cause permanent damage to the device.

| Table 4. | Absolute N | Maximum | Ratings | $(V_{SS} = 0)$ | V, V <sub>SSA</sub> = 0 V) |

|----------|------------|---------|---------|----------------|----------------------------|

|----------|------------|---------|---------|----------------|----------------------------|

| Characteristic                                         | Symbol             | Notes <sup>1</sup> | Min  | Max | Unit |

|--------------------------------------------------------|--------------------|--------------------|------|-----|------|

| Supply Voltage Range                                   | V <sub>DD</sub>    |                    | -0.3 | 4.0 | V    |

| Analog Supply Voltage Range                            | V <sub>DDA</sub>   |                    | -0.3 | 4.0 | V    |

| ADC High Voltage Reference                             | V <sub>REFHx</sub> |                    | -0.3 | 4.0 | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub> | $\Delta V_{DD}$    |                    | -0.3 | 0.3 | V    |

| Voltage difference $V_{SS}$ to $V_{SSA}$               | $\Delta V_{SS}$    |                    | -0.3 | 0.3 | V    |

Table continues on the next page...

- Pin Group 4: XTAL, EXTAL

- Pin Group 5: DAC analog output

- 2. ADC (Cyclic) specifications are not guaranteed when  $V_{\text{DDA}}$  is below 3.0 V.

- 3. Total chip source or sink current cannot exceed 75 mA.

#### 7.3.2 LVD and POR operating requirements Table 6. PMC Low-Voltage Detection (LVD) and Power-On Reset (POR) Parameters

| Characteristic                   | Symbol | Min | Тур  | Max | Unit |

|----------------------------------|--------|-----|------|-----|------|

| POR Assert Voltage <sup>1</sup>  | POR    |     | 2.0  |     | V    |

| POR Release Voltage <sup>2</sup> | POR    |     | 2.7  |     | V    |

| LVI_2p7 Threshold Voltage        |        |     | 2.73 |     | V    |

| LVI_2p2 Threshold Voltage        |        |     | 2.23 |     | V    |

1. During 3.3-volt V<sub>DD</sub> power supply ramp down

2. During 3.3-volt V<sub>DD</sub> power supply ramp up (gated by LVI\_2p7)

### 7.3.3 Voltage and current operating behaviors

The following table provides information about power supply requirements and I/O pin characteristics.

| Characteristic                                               | Symbol                | Notes <sup>1</sup> | Min                   | Тур | Мах     | Unit | Test<br>Conditions                   |

|--------------------------------------------------------------|-----------------------|--------------------|-----------------------|-----|---------|------|--------------------------------------|

| Output Voltage High                                          | V <sub>OH</sub>       | Pin Group 1        | V <sub>DD</sub> - 0.5 |     | _       | V    | I <sub>OH</sub> = I <sub>OHmax</sub> |

| Output Voltage Low                                           | V <sub>OL</sub>       | Pin Groups<br>1, 2 | _                     | —   | 0.5     | V    | $I_{OL} = I_{OLmax}$                 |

| Digital Input Current High<br>pull-up enabled or<br>disabled | Ι <sub>Η</sub>        | Pin Groups<br>1, 2 | _                     | 0   | +/- 2.5 | μA   | V <sub>IN</sub> = 2.4V<br>to 5.5V    |

| Comparator Input Current<br>High                             | I <sub>IHC</sub>      | Pin Group 3        | _                     | 0   | +/- 2   | μA   | $V_{IN} = V_{DDA}$                   |

| Oscillator Input Current<br>High                             | I <sub>IHOSC</sub>    | Pin Group 3        | _                     | 0   | +/- 2   | μΑ   | $V_{IN} = V_{DDA}$                   |

| Internal Pull-Up<br>Resistance                               | R <sub>Pull-Up</sub>  |                    | 20                    | —   | 50      | kΩ   | —                                    |

| Internal Pull-Down<br>Resistance                             | $R_{Pull	ext{-}Down}$ |                    | 20                    | _   | 50      | kΩ   | —                                    |

| Comparator Input Current<br>Low                              | I <sub>ILC</sub>      | Pin Group 3        |                       | 0   | +/- 2   | μA   | $V_{IN} = 0V$                        |

Table 7. DC Electrical Characteristics at Recommended Operating Conditions

Table continues on the next page...

| Characteristic                                      | Symbol             | Notes <sup>1</sup> | Min                                     | Тур | Max                                     | Unit | Test<br>Conditions                                                |

|-----------------------------------------------------|--------------------|--------------------|-----------------------------------------|-----|-----------------------------------------|------|-------------------------------------------------------------------|

| Oscillator Input Current<br>Low                     | I <sub>ILOSC</sub> | Pin Group 3        | —                                       | 0   | +/- 2                                   | μA   | V <sub>IN</sub> = 0V                                              |

| DAC Output Voltage<br>Range                         | V <sub>DAC</sub>   | Pin Group 5        | Typically<br>V <sub>SSA</sub> +<br>40mV | _   | Typically<br>V <sub>DDA</sub> -<br>40mV | V    | $R_{LD} = 3 \text{ k}\Omega \text{ II}$ $C_{LD} = 400 \text{ pf}$ |

| Output Current <sup>1</sup><br>High Impedance State | I <sub>OZ</sub>    | Pin Groups<br>1, 2 |                                         | 0   | +/- 1                                   | μA   | —                                                                 |

| Schmitt Trigger Input<br>Hysteresis                 | V <sub>HYS</sub>   | Pin Groups<br>1, 2 | 0.06 x V <sub>DD</sub>                  | _   | _                                       | V    | _                                                                 |

#### 1. Default Mode

- Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- Pin Group 2: RESET, GPIOA7

- Pin Group 3: ADC and Comparator Analog Inputs

- Pin Group 4: XTAL, EXTAL

- Pin Group 5: DAC

### 7.3.4 Power mode transition operating behaviors

Parameters listed are guaranteed by design.

#### NOTE

All address and data buses described here are internal.

#### Table 8. Reset, Stop, Wait, and Interrupt Timing

| Characteristic                                                              | Symbol           | Typical<br>Min  | Typical<br>Max  | Unit | See<br>Figure |

|-----------------------------------------------------------------------------|------------------|-----------------|-----------------|------|---------------|

| Minimum RESET Assertion Duration                                            | t <sub>RA</sub>  | 16 <sup>1</sup> | —               | ns   | —             |

| RESET deassertion to First Address Fetch                                    | t <sub>RDA</sub> | TBD             | 16 <sup>2</sup> | ns   | —             |

| Delay from Interrupt Assertion to Fetch of first instruction (exiting Stop) | t <sub>IF</sub>  | 361.3           | 570.9           | ns   |               |

1. If Reset pin filter is enabled, minimum pulse assertion must be greater than 21 ns

2. This value is true if the user sets to 1 the RST\_FLT bit in the SIM\_CTRL register.

#### NOTE

In the formulae, T = system clock cycle and  $T_{osc}$  = oscillator clock cycle. For an operating frequency of 60 MHz, T = 16.6 ns. At 4 MHz (used coming out of reset and stop modes), T = 250 ns.

#### General

| Mode               | Maximum<br>Frequency | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              | at 3.3 V,<br>°C  |                   | im at 3.6<br>05°C |

|--------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|-------------------|-------------------|

|                    |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>DD</sub> <sup>1</sup> | I <sub>DDA</sub> | I <sub>DD</sub> 1 | I <sub>DDA</sub>  |

| LPSTOP<br>(LsSTOP) | 2 MHz                | <ul> <li>200 kHz Device Clock from Relaxation Oscillator<br/>(ROSC)</li> <li>ROSC in standby mode</li> <li>Regulators are in standby</li> <li>PLL disabled</li> <li>Only PITs and COP enabled; other peripheral<br/>modules disabled and clocks gated off<sup>3</sup></li> <li>Processor core in stop mode</li> </ul>                                                                                                                        | TBD                          | TBD              | TBD               | TBD               |

| VLPRUN             | 200 kHz              | <ul> <li>32 kHz Device Clock</li> <li>Clocked by a 32 kHz external clock source</li> <li>Oscillator in power down</li> <li>All ROSCs disabled</li> <li>Large regulator is in standby</li> <li>Small regulator is disabled</li> <li>PLL disabled</li> <li>Repeat NOP instructions</li> <li>All peripheral modules, except COP and EWM, disabled and clocks gated off</li> <li>Simple loop running from platform instruction buffer</li> </ul> | TBD                          | TBD              | TBD               | TBD               |

| VLPWAIT            | 200 kHz              | <ul> <li>32 kHz Device Clock</li> <li>Clocked by a 32 kHz external clock source</li> <li>Oscillator in power down</li> <li>All ROSCs disabled</li> <li>Large regulator is in standby</li> <li>Small regulator is disabled</li> <li>PLL disabled</li> <li>All peripheral modules, except COP, disabled and clocks gated off</li> <li>Processor core in wait mode</li> </ul>                                                                   | TBD                          | TBD              | TBD               | TBD               |

| VLPSTOP            | 200 kHz              | <ul> <li>32 kHz Device Clock</li> <li>Clocked by a 32 kHz external clock source</li> <li>Oscillator in power down</li> <li>All ROSCs disabled</li> <li>Large regulator is in standby</li> <li>Small regulator is disabled</li> <li>PLL disabled</li> <li>All peripheral modules, except COP, disabled and clocks gated off</li> <li>Processor core in stop mode</li> </ul>                                                                   | TBD                          | TBD              | TBD               | TBD               |

Table 9. Current Consumption (continued)

1. No output switching, all ports configured as inputs, all inputs low, no DC loads

- 2. ADC power consumption at higher frequency can be found in Table 26

- 3. In all chip LP modes and flash memory VLP modes, the maximum frequency for flash memory operation is 500 kHz due to the fixed frequency ratio of 1:4 between the CPU clock and the flash clock.

# 7.5.2 Thermal attributes

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the MCU design. To account for  $P_{I/O}$  in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  is very small.

| Board type           | Symbol            | Description                                                                                                          | 48 LQFP | 64 LQFP | Unit | Notes |

|----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------|---------|---------|------|-------|

| Single-layer<br>(1s) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection)                                             | 70      | 64      | °C/W | 1, 2  |

| Four-layer<br>(2s2p) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection)                                             | 46      | 46      | °C/W | 1, 3  |

| Single-layer<br>(1s) | R <sub>ejma</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 57      | 52      | °C/W | 1,3   |

| Four-layer<br>(2s2p) | R <sub>ejma</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 39      | 39      | °C/W | 1,3   |

| _                    | R <sub>0JB</sub>  | Thermal<br>resistance,<br>junction to<br>board                                                                       | 23      | 28      | °C/W | 4     |

| _                    | R <sub>θJC</sub>  | Thermal<br>resistance,<br>junction to case                                                                           | 17      | 15      | °C/W | 5     |

| _                    | Ψ <sub>JT</sub>   | Thermal<br>characterization<br>parameter,<br>junction to<br>package top<br>outside center<br>(natural<br>convection) | 3       | 3       | °C/W | 6     |

See Thermal Design Considerations for more detail on thermal design considerations.

# 8.3.3 External Crystal or Resonator Requirement

| Table 20. | Crystal or | Resonator | Requirement |

|-----------|------------|-----------|-------------|

|-----------|------------|-----------|-------------|

| Characteristic         | Symbol            | Min | Тур | Max | Unit |

|------------------------|-------------------|-----|-----|-----|------|

| Frequency of operation | f <sub>xosc</sub> | 4   | 8   | 16  | MHz  |

### 8.3.4 Relaxation Oscillator Timing

#### Table 21. Relaxation Oscillator Electrical Specifications

| Characteristic                                                                  | Symbol | Min  | Тур         | Мах          | Unit |

|---------------------------------------------------------------------------------|--------|------|-------------|--------------|------|

| 8 MHz Output Frequency <sup>1</sup>                                             |        |      |             |              |      |

| RUN Mode<br>• 0°C to 105°C<br>• -40°C to 105°C                                  |        | 7.84 | 8           | 8.16         | MHz  |

| Standby Mode (IRC trimmed @ 8 MHz)<br>• -40°C to 105°C                          |        | 7.76 | 8           | 8.24         |      |

|                                                                                 |        | TBD  | TBD         | TBD          | kHz  |

| 8 MHz Frequency Variation                                                       |        |      |             |              |      |

| RUN Mode                                                                        |        |      |             |              |      |

| Due to temperature<br>• 0°C to 105°C<br>• -40°C to 105°C                        |        |      | +/-1.5      | +/-2<br>+/-3 | %    |

| Standby Mode                                                                    |        |      | Unspecified | +/-3         |      |

| 32 kHz Output Frequency <sup>2</sup>                                            |        |      |             |              |      |

| RUN Mode<br>• -40°C to 105°C                                                    |        |      |             |              |      |

|                                                                                 |        | TBD  | 32          | TBD          | kHz  |

| 32 kHz Output Frequency Variation                                               |        |      |             |              |      |

| RUN Mode                                                                        |        |      |             |              |      |

| Due to temperature<br>• -40°C to 105°C                                          |        |      | +/-2.5      | +/-4         | %    |

| Stabilization Time                                                              | tstab  |      |             |              |      |

| <ul> <li>8 MHz output<sup>3</sup></li> <li>32 kHz output<sup>4</sup></li> </ul> |        |      | 0.12        | 0.4          | μs   |

|                                                                                 |        |      | 14.4        | 16.2         |      |

| Output Duty Cycle                                                               |        | 48   | 50          | 52           | %    |

1. Frequency after application of 8 MHz trim

2. Frequency after application of 32 kHz trim

3. Standby to run mode transition

4. Power down to run mode transition

#### System modules

|                         |                                                          |            |              | -    | -    |       |

|-------------------------|----------------------------------------------------------|------------|--------------|------|------|-------|

| Symbol                  | Description                                              | Min.       | Тур.         | Max. | Unit | Notes |

|                         | Byte-write to FlexRAM execution time:                    |            |              |      |      |       |

| t <sub>eewr8b8k</sub>   | 8 KB EEPROM backup                                       | —          | 340          | 1700 | μs   |       |

| t <sub>eewr8b16k</sub>  | 16 KB EEPROM backup                                      | _          | 385          | 1800 | μs   |       |

| t <sub>eewr8b32k</sub>  | 32 KB EEPROM backup                                      | _          | 475          | 2000 | μs   |       |

|                         | Word-write to FlexRAM                                    | for EEPRON | I operation  |      |      |       |

| t <sub>eewr16bers</sub> | Word-write to erased FlexRAM location execution time     | _          | 175          | 260  | μs   |       |

|                         | Word-write to FlexRAM execution time:                    |            |              |      |      |       |

| t <sub>eewr16b8k</sub>  | 8 KB EEPROM backup                                       | —          | 340          | 1700 | μs   |       |

| t <sub>eewr16b16k</sub> | 16 KB EEPROM backup                                      | _          | 385          | 1800 | μs   |       |

| t <sub>eewr16b32k</sub> | • 32 KB EEPROM backup                                    | —          | 475          | 2000 | μs   |       |

|                         | Longword-write to FlexRA                                 | M for EEPR | OM operation | ו    | 1    |       |

| t <sub>eewr32bers</sub> | Longword-write to erased FlexRAM location execution time | _          | 360          | 540  | μs   |       |

|                         | Longword-write to FlexRAM execution time:                |            |              |      |      |       |

| t <sub>eewr32b8k</sub>  | 8 KB EEPROM backup                                       | —          | 545          | 1950 | μs   |       |

| t <sub>eewr32b16k</sub> | 16 KB EEPROM backup                                      | _          | 630          | 2050 | μs   |       |

| t <sub>eewr32b32k</sub> | • 32 KB EEPROM backup                                    | —          | 810          | 2250 | μs   |       |

#### Table 23. Flash command timing specifications (continued)

1. Assumes 25MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

3. For byte-writes to an erased FlexRAM location, the aligned word containing the byte must be erased.

#### 8.4.1.2 Reliability specifications Table 24. NVM reliability specifications

| Symbol                   | Description                                  | Min.     | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|--------------------------|----------------------------------------------|----------|-------------------|------|--------|-------|

|                          | Progra                                       | n Flash  |                   |      | •      |       |

| t <sub>nvmretp10k</sub>  | Data retention after up to 10 K cycles       | 5        | 50                | _    | years  |       |

| t <sub>nvmretp1k</sub>   | Data retention after up to 1 K cycles        | 20       | 100               | _    | years  |       |

| n <sub>nvmcycp</sub>     | Cycling endurance                            | 10 K     | 50 K              | _    | cycles | 2     |

|                          | Data                                         | Flash    |                   |      |        |       |

| t <sub>nvmretd10k</sub>  | Data retention after up to 10 K cycles       | 5        | 50                | _    | years  |       |

| t <sub>nvmretd1k</sub>   | Data retention after up to 1 K cycles        | 20       | 100               | —    | years  |       |

| n <sub>nvmcycd</sub>     | Cycling endurance                            | 10 K     | 50 K              | —    | cycles | 2     |

|                          | FlexRAM a                                    | s EEPROM |                   |      |        |       |

| t <sub>nvmretee100</sub> | Data retention up to 100% of write endurance | 5        | 50                | _    | years  |       |

| t <sub>nvmretee10</sub>  | Data retention up to 10% of write endurance  | 20       | 100               | _    | years  |       |

Table continues on the next page...

| Description                                             | Min.                                                                                                                                                                                                                        | Typ. <sup>1</sup>                                                                                                                                                                          | Max.                                                                                                                                                                                           | Unit                                                                                                                                                                                                                   | Notes                                                                                                                                                                                                                                                |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write endurance                                         |                                                                                                                                                                                                                             |                                                                                                                                                                                            |                                                                                                                                                                                                |                                                                                                                                                                                                                        | 3                                                                                                                                                                                                                                                    |

| <ul> <li>EEPROM backup to FlexRAM ratio = 16</li> </ul> | 35 K                                                                                                                                                                                                                        | 175 K                                                                                                                                                                                      |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

| EEPROM backup to FlexRAM ratio = 128                    | 315 K                                                                                                                                                                                                                       | 1.6 M                                                                                                                                                                                      |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

| EEPROM backup to FlexRAM ratio = 512                    | 1.27 M                                                                                                                                                                                                                      | 6.4 M                                                                                                                                                                                      |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

| • EEPROM backup to FlexRAM ratio = 4096                 | 10 M                                                                                                                                                                                                                        | 50 M                                                                                                                                                                                       |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

| • EEPROM backup to FlexRAM ratio = 8192                 | 20 M                                                                                                                                                                                                                        | 100 M                                                                                                                                                                                      |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

|                                                         | <ul> <li>Write endurance</li> <li>EEPROM backup to FlexRAM ratio = 16</li> <li>EEPROM backup to FlexRAM ratio = 128</li> <li>EEPROM backup to FlexRAM ratio = 512</li> <li>EEPROM backup to FlexRAM ratio = 4096</li> </ul> | Write endurance• EEPROM backup to FlexRAM ratio = 1635 K• EEPROM backup to FlexRAM ratio = 128315 K• EEPROM backup to FlexRAM ratio = 5121.27 M• EEPROM backup to FlexRAM ratio = 409610 M | Write endurance35 K• EEPROM backup to FlexRAM ratio = 1635 K• EEPROM backup to FlexRAM ratio = 128315 K• EEPROM backup to FlexRAM ratio = 5121.27 M• EEPROM backup to FlexRAM ratio = 409610 M | Write endurance35 K175 K• EEPROM backup to FlexRAM ratio = 1635 K175 K• EEPROM backup to FlexRAM ratio = 128315 K1.6 M• EEPROM backup to FlexRAM ratio = 5121.27 M6.4 M• EEPROM backup to FlexRAM ratio = 409610 M50 M | Write endurance35 K175 Kwrites• EEPROM backup to FlexRAM ratio = 1635 K175 Kwrites• EEPROM backup to FlexRAM ratio = 128315 K1.6 Mwrites• EEPROM backup to FlexRAM ratio = 5121.27 M6.4 Mwrites• EEPROM backup to FlexRAM ratio = 409610 M50 Mwrites |

Table 24. NVM reliability specifications (continued)

- Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

- 2. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  T<sub>i</sub>  $\leq$  125°C.

- Write endurance represents the number of writes to each FlexRAM location at -40°C ≤Tj ≤ 125°C influenced by the cycling endurance of the FlexNVM (same value as data flash) and the allocated EEPROM backup. Minimum and typical values assume all byte-writes to FlexRAM.

### 8.5 Analog

#### 8.5.1 12-bit Cyclic Analog-to-Digital Converter (ADC) Parameters Table 25. 12-bit ADC Electrical Specifications

| Characteristic                    | Symbol              | Min               | Тур | Max               | Unit             |

|-----------------------------------|---------------------|-------------------|-----|-------------------|------------------|

| Recommended Operating Conditions  |                     |                   | •   |                   |                  |

| Supply Voltage <sup>1</sup>       | V <sub>DDA</sub>    | 2.7               | 3.3 | 3.6               | V                |

| Vrefh Supply Voltage <sup>2</sup> | Vrefhx              | 3.0               |     | V <sub>DDA</sub>  | V                |

| ADC Conversion Clock <sup>3</sup> | f <sub>ADCCLK</sub> | 0.6               |     | 20                | MHz              |

| Conversion Range                  | R <sub>AD</sub>     | V <sub>REFL</sub> |     | V <sub>REFH</sub> | V                |

| Input Voltage Range <sup>4</sup>  | V <sub>ADIN</sub>   |                   |     |                   | V                |

| External Reference                |                     | V <sub>REFL</sub> |     | V <sub>REFH</sub> |                  |

| Internal Reference                |                     | V <sub>SSA</sub>  |     | V <sub>DDA</sub>  |                  |

| Timing and Power                  |                     |                   |     |                   |                  |

| Conversion Time                   | t <sub>ADC</sub>    |                   | 6   |                   | ADC Clock Cycles |

| Sample Time                       | t <sub>ADS</sub>    | 1                 |     | 5                 | ADC Clock Cycles |

| ADC Power-Up Time (from adc_pdn)  | t <sub>ADPU</sub>   |                   | 13  |                   | ADC Clock Cycles |

Table continues on the next page...

#### System modules

| Table 25. | 12-bit ADC Electrical | Specifications ( | (continued) |

|-----------|-----------------------|------------------|-------------|

|-----------|-----------------------|------------------|-------------|

| Characteristic                                                                                                                                          | Symbol                | Min                  | Тур                   | Мах               | Unit             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|-----------------------|-------------------|------------------|

| ADC RUN Current (per ADC block)                                                                                                                         | I <sub>ADRUN</sub>    |                      |                       |                   | mA               |

| • at 600 kHz ADC Clock, LP mode                                                                                                                         |                       |                      | 1                     |                   |                  |

| • ≤ 8.33 MHz ADC Clock, 00 mode                                                                                                                         |                       |                      | 5                     |                   |                  |

| • ≤ 12.5 MHz ADC Clock, 01 mode                                                                                                                         |                       |                      | 9                     |                   |                  |

| • ≤ 16.67 MHz ADC Clock, 10 mode                                                                                                                        |                       |                      | 15                    |                   |                  |

| <ul> <li>≤ 20 MHz ADC Clock, 11 mode</li> </ul>                                                                                                         |                       |                      | 19                    |                   |                  |

| ADC Powerdown Current (adc_pdn enabled)                                                                                                                 | I <sub>ADPWRDWN</sub> |                      | 0.02                  |                   | μA               |

| V <sub>REFH</sub> Current                                                                                                                               | I <sub>VREFH</sub>    |                      | 0.001                 |                   | μΑ               |

| Accuracy (DC or Absolute)                                                                                                                               |                       |                      | ł                     | · · · · · ·       |                  |

| Integral non-Linearity <sup>5</sup>                                                                                                                     | I <sub>NL</sub>       |                      | +/- 3                 | +/- 5             | LSB <sup>6</sup> |

| Differential non-Linearity <sup>5</sup>                                                                                                                 | DNL                   |                      | +/- 0.6               | +/- 1             | LSB <sup>6</sup> |

| Monotonicity                                                                                                                                            |                       |                      |                       | F F               |                  |

| Offset <sup>7</sup> <ul> <li>≤15 MHz ADC Clock Internal/External<br/>Reference</li> <li>&gt;15 MHz ADC Clock Internal/External<br/>Reference</li> </ul> | V <sub>OFFSET</sub>   | +/- 4.03<br>+/- 7.25 | +/- 8.86<br>+/- 13.70 |                   | mV               |

| Gain Error                                                                                                                                              | E <sub>GAIN</sub>     |                      | 0.801 to<br>0.809     | 0.798 to<br>0.814 | mV               |

| AC Specifications <sup>8</sup>                                                                                                                          |                       |                      |                       | I I               |                  |

| Signal to Noise Ratio                                                                                                                                   | SNR                   |                      | 59                    |                   | dB               |

| Total Harmonic Distortion                                                                                                                               | THD                   |                      | 64                    |                   | dB               |

| Spurious Free Dynamic Range                                                                                                                             | SFDR                  |                      | 65                    |                   | dB               |

| Signal to Noise plus Distortion                                                                                                                         | SINAD                 |                      | 59                    |                   | dB               |

| Effective Number of Bits                                                                                                                                | ENOB                  |                      | 9.5                   |                   | bits             |

| ADC Inputs                                                                                                                                              |                       |                      |                       |                   |                  |

| Input Leakage Current                                                                                                                                   | I <sub>IN</sub>       |                      | 0                     | +/-2              | μA               |

| Input Injection Current <sup>9</sup>                                                                                                                    | I <sub>INJ</sub>      |                      |                       | +/-3              | mA               |

| Input Capacitance                                                                                                                                       | C <sub>ADI</sub>      |                      |                       |                   | pF               |

| Sampling Capacitor                                                                                                                                      |                       |                      |                       |                   |                  |

| • 1x mode                                                                                                                                               |                       |                      | 1.4                   |                   |                  |

| • 2x mode                                                                                                                                               |                       |                      | 2.8                   |                   |                  |

| • 4x mode                                                                                                                                               |                       |                      | 5.6                   |                   |                  |

1. If the ADC's reference is from V<sub>DDA</sub>: When V<sub>DDA</sub> is below 3.0 V, the ADC functions but ADC specifications are not guaranteed.

- 2. When the input is at the  $V_{refi}$  level, the resulting output will be all zeros (hex 000), plus any error contribution due to offset and gain error. When the input is at the V<sub>refh</sub> level the output will be all ones (hex FFF), minus any error contribution due to offset and gain error.

- 3. ADC clock duty cycle min/max is 45/55%

- 4. When V<sub>refh</sub> is supplied externally

- 5.  $I_{NL}$  measured from  $V_{IN} = V_{REFL}$  to  $V_{IN} = V_{REFH}$ . 6. LSB = Least Significant Bit = 0.806 mV at 3.3 V VDDA, x1 Gain Setting

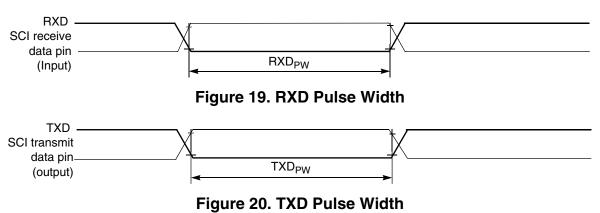

# 8.7.2 Queued Serial Communication Interface (SCI) Timing

Parameters listed are guaranteed by design.

| Characteristic                                                                              | Symbol                   | Min        | Мах                    | Unit                          | See Figure |

|---------------------------------------------------------------------------------------------|--------------------------|------------|------------------------|-------------------------------|------------|

| Baud rate <sup>1</sup>                                                                      | BR                       |            | (f <sub>MAX</sub> /16) | Mbps                          | _          |

| RXD pulse width                                                                             | RXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 19  |

| TXD pulse width                                                                             | TXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 20  |

|                                                                                             | LIN                      | Slave Mode |                        | •                             |            |

| Deviation of slave node clock from nominal<br>clock rate before synchronization             | F <sub>TOL_UNSYNCH</sub> | -14        | 14                     | %                             | _          |

| Deviation of slave node clock relative to<br>the master node clock after<br>synchronization | F <sub>TOL_SYNCH</sub>   | -2         | 2                      | %                             | _          |

| Minimum break character length                                                              | Т <sub>ВRЕАК</sub>       | 13         | _                      | Master<br>node bit<br>periods | _          |

|                                                                                             |                          | 11         | _                      | Slave node bit periods        | _          |

#### Table 33. SCI Timing

1. f<sub>MAX</sub> is the frequency of operation of the SCI clock in MHz, which can be selected system clock (max. 120 MHz depending on part number) or 2x system clock (max. 200 MHz) for the devices.

#### 8.7.3 Freescale's Scalable Controller Area Network (FlexCAN) Table 34. FlexCAN Timing Parameters

| Characteristic                     | Symbol              | Min | Max | Unit |

|------------------------------------|---------------------|-----|-----|------|

| Baud Rate                          | BR <sub>CAN</sub>   | —   | 1   | Mbps |

| CAN Wakeup dominant pulse filtered | T <sub>WAKEUP</sub> | —   | 2   | μs   |

| CAN Wakeup dominant pulse pass     | T <sub>WAKEUP</sub> | 5   | _   | μs   |

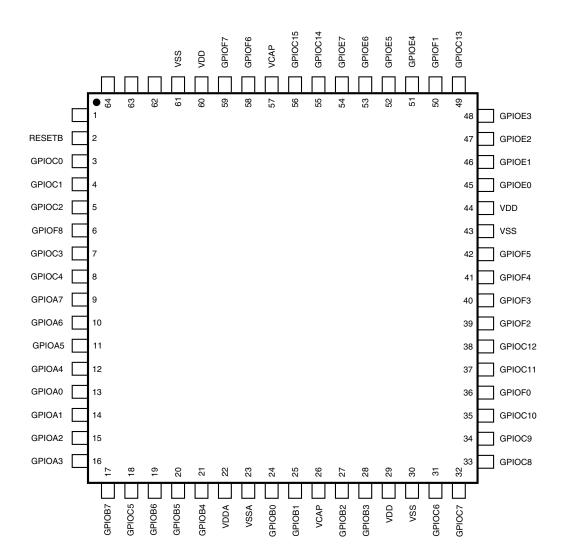

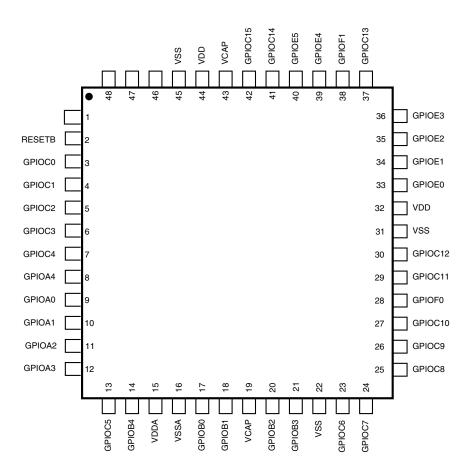

Figure 23. 64-pin LQFP

### **12 Product Documentation**

The documents listed in Table 36 are required for a complete description and proper design with the device. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, or online at http://www.freescale.com.

MC56F844xx Advance Information Data Sheet, Rev. 2, 06/2012.

Freescale Semiconductor, Inc.