# E·XFL

#### NXP USA Inc. - MC56F84452VLH Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 56800EX                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 60MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                       |

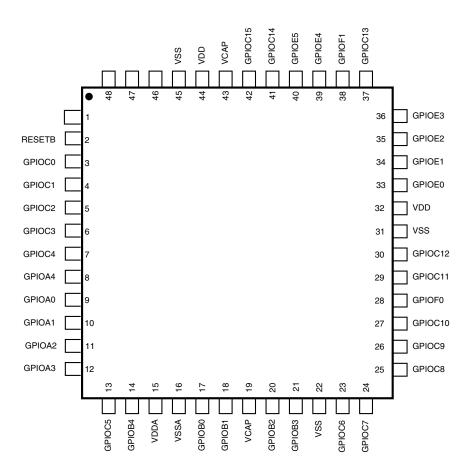

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 96KB (96K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b, 8x16b                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f84452vlh |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Operating characteristics

- Single supply: 3.0 V to 3.6 V

5 V-tolerant I/O

- LQFP packages:

- 48-pin 64-pin

- Up to 16 KW FlexNVM, which can be used as additional program or data flash memory

- Up to 1 KW FlexRAM, which can be configured as enhanced EEPROM (used in conjunction with FlexNVM) or used as additional RAM

## 1.5 Interrupt Controller

- Five interrupt priority levels

- Three user programmable priority levels for each interrupt source: level 0, 1, 2

- Unmaskable level 3 interrupts include: illegal instruction, hardware stack overflow, misaligned data access, SWI3 instruction

- Maskable level 3 interrupts include: EOnCE step counter, EOnCE breakpoint unit, EOnCE trace buffer

- Lowest-priority software interrupt: level LP

- Support for nested interrupt: higher priority level interrupt request can interrupt lower priority interrupt subroutine

- Masking of interrupt priority level managed by the 56800EX core

- Two programmable fast interrupts that can be assigned to any interrupt source

- Notification to System Integration Module (SIM) to restart clock when in wait and stop states

- Ability to relocate interrupt vector table

## 1.6 Peripheral highlights

## 1.6.1 Enhanced Flex Pulse Width Modulator (eFlexPWM)

- Up to 12 output channels in each module

- 16 bits of resolution for center, edge aligned, and asymmetrical PWMs

- PWMA with accumulative fractional clock calculation

- Accumulative fractional clock calculation improves the resolution of the PWM period and edge placement

- Arbitrary PWM edge placement

- Equivalent to 312 ps PWM frequency and duty-cycle resolution on average

- Each complementary pair can operate with its own PWM frequency base and deadtime values

- 4 time base in each PWM module

- Independent top and bottom deadtime insertion for each complementary pair

- PWM outputs can operate as complementary pairs or independent channels

- Independent control of both edges of each PWM output

#### Peripheral highlights

- Enhanced input capture and output compare functionality on each input

- Channels not used for PWM generation can be used for buffered output compare functions

- Channels not used for PWM generation can be used for input capture functions

- Enhanced dual edge capture functionality

- Synchronization to external hardware or other PWM supported

- Double buffered PWM registers

- Integral reload rates from 1 to 16

- Half-cycle reload capability

- Multiple output trigger events can be generated per PWM cycle via hardware

- Support for double switching PWM outputs

- Up to eight fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Individual software control of each PWM output

- All outputs can be programmed to change simultaneously via a FORCE\_OUT event

- PWMX pin can optionally output a third PWM signal from each submodule

- Option to supply the source for each complementary PWM signal pair from any of the following:

- Crossbar module outputs

- External ADC input, taking into account values set in ADC high and low limit registers

## 1.6.2 12-bit Analog-to-Digital Converter (Cyclic type)

- Two independent 12-bit analog-to-digital converters (ADCs)

- 2 x 8-channel external inputs

- Built-in x1, x2, x4 programmable gain pre-amplifier

- Maximum ADC clock frequency is up to 20 MHz with 50 ns period

- Single conversion time of 8.5 ADC clock cycles

- Additional conversion time of 6 ADC clock cycles

- Sequential, parallel, and independent scan mode

- First 8 samples have offset, limit and zero-crossing calculation supported

- ADC conversions can be synchronized by any module connected to internal crossbar module, such as PWM and timer modules and GPIO and comparators

- Support for simultaneous and software triggering conversions

- Support for multi-triggering mode with a programmable number of conversions on each trigger

- Each ADC has ability to scan and store up to 8 conversion results

#### **1.6.7 Queued Serial Communications Interface (QSCI) Modules**

- Operating clock up to two times CPU operating frequency

- Four-word-deep FIFOs available on both transmit and receive buffers

- Standard mark/space non-return-to-zero (NRZ) format

- 13-bit integer and 3-bit fractional baud rate selection

- Full-duplex or single-wire operation

- Programmable 8-bit or 9-bit data format

- Error detection capability

- Two receiver wakeup methods:

- Idle line

- Address mark

- 1/16 bit-time noise detection

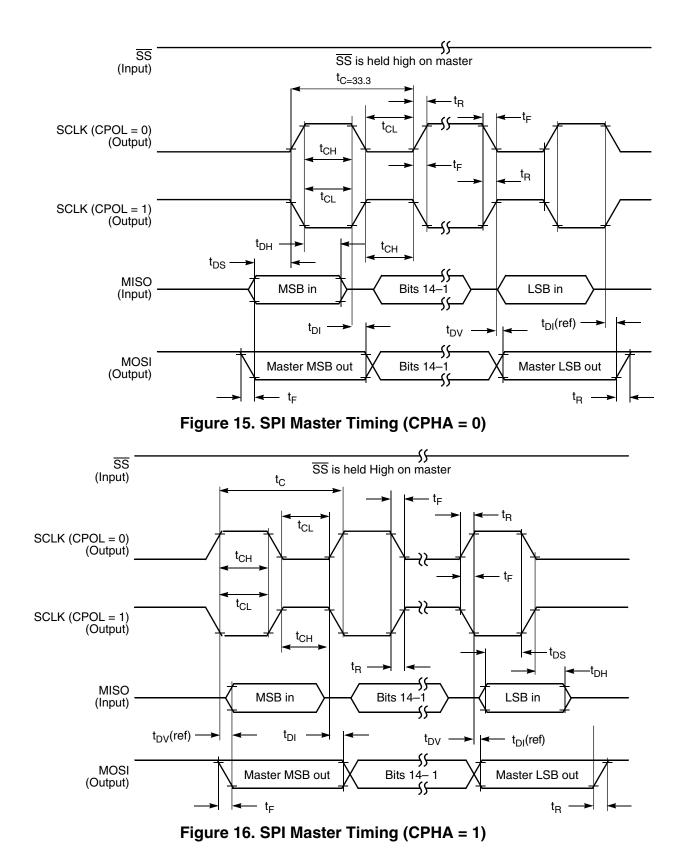

#### 1.6.8 Queued Serial Peripheral Interface (QSPI) Modules

- Maximum 25 Mbps baud rate

- Selectable baud rate clock sources for low baud rate communication

- Baud rate as low as Baudrate\_Freq\_in / 8192

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four-word-deep FIFOs available on transmit and receive buffers

- Programmable length transmissions (2 bits to 16 bits)

- Programmable transmit and receive shift order (MSB as first bit transmitted)

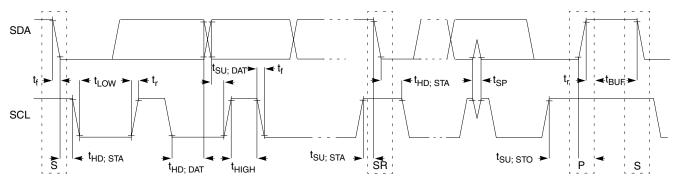

#### 1.6.9 Inter-Integrated Circuit (I2C)/System Management Bus (SMBus) Modules

- Compatible with I2C bus standard

- Support for System Management Bus (SMBus) specification, version2

- Multi-master operation

- General call recognition

- 10-bit address extension

- Dual slave addresses

- Programmable glitch input filter

## 1.6.10 Flex Controller Area Network (FlexCAN) Module

• Clock source from PLL or XOSC/CLKIN

- Implementation of the CAN protocol Version 2.0 A/B

- Standard and extended data frames

- 0-to-8 bytes data length

- Programmable bit rate up to 1 Mbps

- Support for remote frames

- Sixteen Message Buffers, each configurable as receive or transmit, all supporting standard and extended messages

- Individual Rx Mask Registers per Message Buffer

- Internal timer for time-stamping of received and transmitted messages

- Listen-only mode capability

- Programmable loopback mode supporting self-test operation

- Programmable transmission priority scheme: lowest ID, lowest buffer number, or highest priority

- Global network time, synchronized by a specific message

- Low power modes, with programmable wakeup on bus activity

## 1.6.11 Computer Operating Properly (COP) Watchdog

- Programmable timeout period

- Support for operation in all power modes: run mode, wait mode, stop mode

- Causes loss of reference reset 128 cycles after loss of reference clock to the PLL is detected

- Selectable reference clock source in support of EN60730 and IEC61508

- Selectable clock sources:

- External crystal oscillator/external clock source

- On-chip low-power 32 kHz oscillator

- System bus (IPBus up to 60 MHz)

- 8 MHz / 400 kHz ROSC

- Support for interrupt triggered when the counter reaches the timeout value

## 1.6.12 Power Supervisor

- Power-on reset (POR) to reset CPU, peripherals, and JTAG/EOnCE controllers (VDD > 2.1 V)

- Brownout reset (VDD < 1.9 V)

- Critical warn low voltage interrupt (LVI2.0)

- Peripheral low voltage interrupt (LVI2.7)

#### 1.6.13 Phase Locked Loop

- Wide programmable output frequency: 240 MHz to 400 MHz

- Input reference clock frequency: 8 MHz to 16 MHz

- Detection of loss of lock and loss of reference clock

- Ability to power down

#### 1.6.14 Clock sources

#### 1.6.14.1 On-Chip Oscillators

- Tunable 8 MHz relaxation oscillator with 400 kHz at standby mode (divide-by-two output)

- 32 kHz low frequency clock as secondary clock source for COP, EWM, PIT

#### 1.6.14.2 Crystal Oscillator

- Support for both high ESR crystal oscillator (greater than 100-ohm ESR) and ceramic resonator

- 4 MHz to 16 MHz operating frequency

#### 1.6.15 Cyclic Redundancy Check (CRC) Generator

- Hardware 16/32-bit CRC generator

- High-speed hardware CRC calculation

- Programmable initial seed value

- Programmable 16/32-bit polynomial

- Error detection for all single, double, odd, and most multi-bit errors

- Option to transpose input data or output data (CRC result) bitwise or bytewise,<sup>1</sup> which is required for certain CRC standards

- Option for inversion of final CRC result

## 1.6.16 General Purpose I/O (GPIO)

- 5 V tolerance

- Individual control of peripheral mode or GPIO mode for each pin

- Programmable push-pull or open drain output

- Configurable pullup or pulldown on all input pins

<sup>1.</sup> A bytewise transposition is not possible when accessing the CRC data register via 8-bit accesses. In this case, user software must perform the bytewise transposition.

**Clock sources**

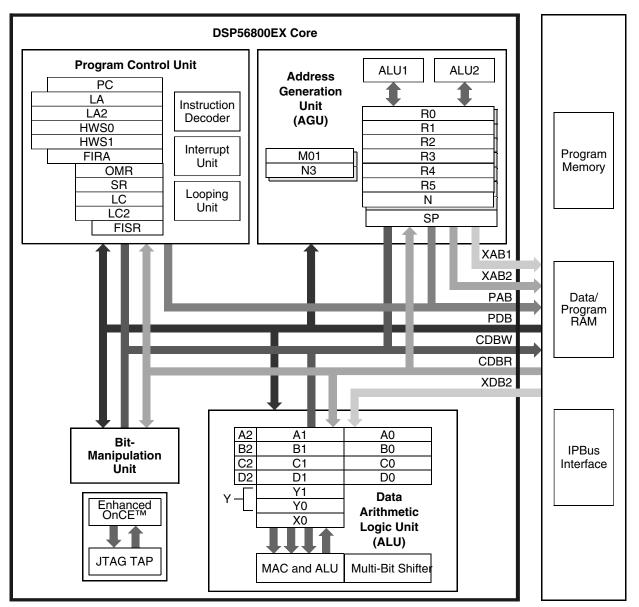

Figure 1. 56800EX Basic Block Diagram

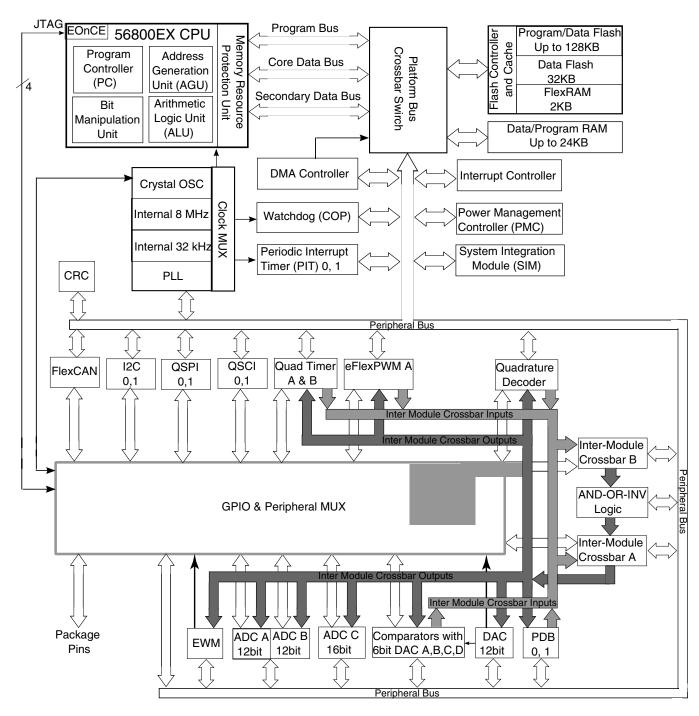

Figure 2. System Diagram

## 5.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

## 5.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol | Description                                    | Min. | Тур. | Max. | Unit |

|--------|------------------------------------------------|------|------|------|------|

|        | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

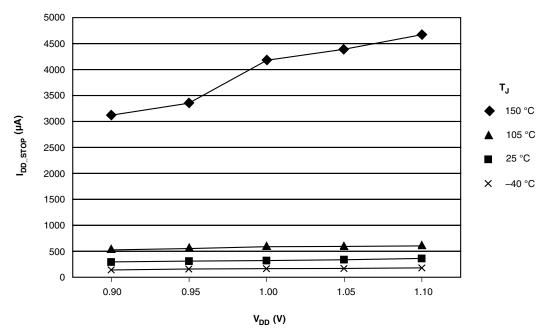

## 5.8.2 Example 2

This is an example of a chart that shows typical values for various voltage and temperature conditions:

MC56F844xx Advance Information Data Sheet, Rev. 2, 06/2012.

Absolute maximum ratings in Table 4 are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond these ratings may affect device reliability or cause permanent damage to the device.

Unless otherwise stated, all specifications within this chapter apply over the temperature range of -40°C to 105°C ambient temperature over the following supply ranges: VSS = VSSA = 0 V, VDD = VDDA = 3.0 V to 3.6 V, CL  $\leq$  50 pF, f<sub>OP</sub> = 60 MHz.

#### CAUTION

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum-rated voltages to this highimpedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

## 7.2 AC Electrical Characteristics

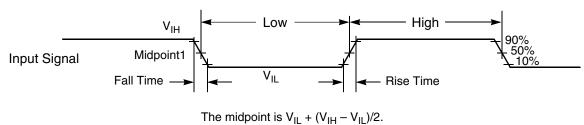

Tests are conducted using the input levels specified in Table 7. Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured between the 10% and 90% points, as shown in Figure 3.

#### Figure 3. Input Signal Measurement References

Figure 4 shows the definitions of the following signal states:

- Active state, when a bus or signal is driven, and enters a low impedance state

- Tri-stated, when a bus or signal is placed in a high impedance state

- Data Valid state, when a signal level has reached  $V_{OL}$  or  $V_{OH}$

- Data Invalid state, when a signal level is in transition between  $V_{\mbox{OL}}$  and  $V_{\mbox{OH}}$

## 7.3.5 Power consumption operating behaviors

|  | Table 9. | Current | Consum | otion |

|--|----------|---------|--------|-------|

|--|----------|---------|--------|-------|

| Mode               | Node Maximum Conditions<br>Frequency |                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | at 3.3 V,<br>°C  | Maximum at 3.6<br>V, 105°C |                  |

|--------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|----------------------------|------------------|

|                    |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | I <sub>DDA</sub> | I <sub>DD</sub> 1          | I <sub>DDA</sub> |

| RUN                | 60 MHz                               | <ul> <li>60 MHz Device Clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> <li>PLL powered on</li> <li>Continuous MAC instructions with fetches from<br/>Program Flash</li> <li>All peripheral modules enabled.</li> <li>TMRs and SCIs using 1X Clock</li> <li>NanoEdge within PWMA using 2X clock</li> <li>ADC/DAC powered on and clocked at 5 MHz<sup>2</sup></li> <li>Comparator powered on</li> </ul> | TBD | TBD              | TBD                        | TBD              |

| WAIT               | 60 MHz                               | <ul> <li>60 MHz Device Clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> <li>PLL powered on</li> <li>Processor Core in WAIT state</li> <li>All Peripheral modules enabled.</li> <li>TMRs and SCIs using 1X Clock</li> <li>NanoEdge within PWMA using 2X clock</li> <li>ADC/DAC/Comparator powered off</li> </ul>                                                                                        | TBD | TBD              | TBD                        | TBD              |

| STOP               | 4 MHz                                | <ul> <li>4 MHz Device Clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> <li>PLL powered off</li> <li>Processor Core in STOP state</li> <li>All peripheral module and core clocks are off</li> <li>ADC/DAC/Comparator powered off</li> </ul>                                                                                                                                                             | TBD | TBD              | TBD                        | TBD              |

| LPRUN<br>(LsRUN)   | 2 MHz                                | <ul> <li>200 kHz Device Clock from Relaxation Oscillator<br/>(ROSC)</li> <li>ROSC in standby mode</li> <li>Regulators are in standby</li> <li>PLL disabled</li> <li>Repeat NOP instructions</li> <li>All peripheral modules enabled, except NanoEdge<br/>and cyclic ADCs<sup>3</sup></li> <li>Simple loop with running from platform instruction<br/>buffer</li> </ul>                                                                        | TBD | TBD              | TBD                        | TBD              |

| LPWAIT<br>(LsWAIT) | 2 MHz                                | <ul> <li>200 kHz Device Clock from Relaxation Oscillator<br/>(ROSC)</li> <li>ROSC in standby mode</li> <li>Regulators are in standby</li> <li>PLL disabled</li> <li>All peripheral modules enabled, except NanoEdge<br/>and cyclic ADCs<sup>3</sup></li> <li>Processor core in wait mode</li> </ul>                                                                                                                                           | TBD | TBD              | TBD                        | TBD              |

Table continues on the next page ...

## 8.3.3 External Crystal or Resonator Requirement

| Table 20. | Crystal or | Resonator | Requirement |

|-----------|------------|-----------|-------------|

|-----------|------------|-----------|-------------|

| Characteristic         | Symbol            | Min | Тур | Max | Unit |

|------------------------|-------------------|-----|-----|-----|------|

| Frequency of operation | f <sub>xosc</sub> | 4   | 8   | 16  | MHz  |

## 8.3.4 Relaxation Oscillator Timing

#### Table 21. Relaxation Oscillator Electrical Specifications

| Characteristic                                                                  | Symbol | Min  | Тур         | Мах          | Unit |

|---------------------------------------------------------------------------------|--------|------|-------------|--------------|------|

| 8 MHz Output Frequency <sup>1</sup>                                             |        |      |             |              |      |

| RUN Mode<br>• 0°C to 105°C<br>• -40°C to 105°C                                  |        | 7.84 | 8           | 8.16         | MHz  |

| Standby Mode (IRC trimmed @ 8 MHz)<br>• -40°C to 105°C                          |        | 7.76 | 8           | 8.24         |      |

|                                                                                 |        | TBD  | TBD         | TBD          | kHz  |

| 8 MHz Frequency Variation                                                       |        |      |             |              |      |

| RUN Mode                                                                        |        |      |             |              |      |

| Due to temperature<br>• 0°C to 105°C<br>• -40°C to 105°C                        |        |      | +/-1.5      | +/-2<br>+/-3 | %    |

| Standby Mode                                                                    |        |      | Unspecified | +/-3         |      |

| 32 kHz Output Frequency <sup>2</sup>                                            |        |      |             |              |      |

| RUN Mode<br>• -40°C to 105°C                                                    |        |      |             |              |      |

|                                                                                 |        | TBD  | 32          | TBD          | kHz  |

| 32 kHz Output Frequency Variation                                               |        |      |             |              |      |

| RUN Mode                                                                        |        |      |             |              |      |

| Due to temperature<br>• -40°C to 105°C                                          |        |      | +/-2.5      | +/-4         | %    |

| Stabilization Time                                                              | tstab  |      |             |              |      |

| <ul> <li>8 MHz output<sup>3</sup></li> <li>32 kHz output<sup>4</sup></li> </ul> |        |      | 0.12        | 0.4          | μs   |

|                                                                                 |        |      | 14.4        | 16.2         |      |

| Output Duty Cycle                                                               |        | 48   | 50          | 52           | %    |

1. Frequency after application of 8 MHz trim

2. Frequency after application of 32 kHz trim

3. Standby to run mode transition

4. Power down to run mode transition

#### System modules

|                         |                                                          |            |              | -    | -    |       |

|-------------------------|----------------------------------------------------------|------------|--------------|------|------|-------|

| Symbol                  | Description                                              | Min.       | Тур.         | Max. | Unit | Notes |

|                         | Byte-write to FlexRAM execution time:                    |            |              |      |      |       |

| t <sub>eewr8b8k</sub>   | 8 KB EEPROM backup                                       | —          | 340          | 1700 | μs   |       |

| t <sub>eewr8b16k</sub>  | 16 KB EEPROM backup                                      | _          | 385          | 1800 | μs   |       |

| t <sub>eewr8b32k</sub>  | 32 KB EEPROM backup                                      | _          | 475          | 2000 | μs   |       |

|                         | Word-write to FlexRAM                                    | for EEPRON | I operation  |      |      |       |

| t <sub>eewr16bers</sub> | Word-write to erased FlexRAM location execution time     | _          | 175          | 260  | μs   |       |

|                         | Word-write to FlexRAM execution time:                    |            |              |      |      |       |

| t <sub>eewr16b8k</sub>  | 8 KB EEPROM backup                                       | —          | 340          | 1700 | μs   |       |

| t <sub>eewr16b16k</sub> | 16 KB EEPROM backup                                      | _          | 385          | 1800 | μs   |       |

| t <sub>eewr16b32k</sub> | • 32 KB EEPROM backup                                    | —          | 475          | 2000 | μs   |       |

|                         | Longword-write to FlexRA                                 | M for EEPR | OM operation | ו    | 1    |       |

| t <sub>eewr32bers</sub> | Longword-write to erased FlexRAM location execution time | _          | 360          | 540  | μs   |       |

|                         | Longword-write to FlexRAM execution time:                |            |              |      |      |       |

| t <sub>eewr32b8k</sub>  | 8 KB EEPROM backup                                       | —          | 545          | 1950 | μs   |       |

| t <sub>eewr32b16k</sub> | 16 KB EEPROM backup                                      | _          | 630          | 2050 | μs   |       |

| t <sub>eewr32b32k</sub> | • 32 KB EEPROM backup                                    | _          | 810          | 2250 | μs   |       |

#### Table 23. Flash command timing specifications (continued)

1. Assumes 25MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

3. For byte-writes to an erased FlexRAM location, the aligned word containing the byte must be erased.

#### 8.4.1.2 Reliability specifications Table 24. NVM reliability specifications

| Symbol                   | Description                                  | Min.     | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|--------------------------|----------------------------------------------|----------|-------------------|------|--------|-------|

|                          | Progra                                       | n Flash  |                   |      | •      |       |

| t <sub>nvmretp10k</sub>  | Data retention after up to 10 K cycles       | 5        | 50                | _    | years  |       |

| t <sub>nvmretp1k</sub>   | Data retention after up to 1 K cycles        | 20       | 100               | _    | years  |       |

| n <sub>nvmcycp</sub>     | Cycling endurance                            | 10 K     | 50 K              | _    | cycles | 2     |

|                          | Data                                         | Flash    |                   |      |        |       |

| t <sub>nvmretd10k</sub>  | Data retention after up to 10 K cycles       | 5        | 50                | _    | years  |       |

| t <sub>nvmretd1k</sub>   | Data retention after up to 1 K cycles        | 20       | 100               | _    | years  |       |

| n <sub>nvmcycd</sub>     | Cycling endurance                            | 10 K     | 50 K              | —    | cycles | 2     |

|                          | FlexRAM a                                    | s EEPROM |                   |      |        |       |

| t <sub>nvmretee100</sub> | Data retention up to 100% of write endurance | 5        | 50                | _    | years  |       |

| t <sub>nvmretee10</sub>  | Data retention up to 10% of write endurance  | 20       | 100               | _    | years  |       |

Table continues on the next page...

| Description                                             | Min.                                                                                                                                                                                                                        | Typ. <sup>1</sup>                                                                                                                                                                          | Max.                                                                                                                                                                                           | Unit                                                                                                                                                                                                                   | Notes                                                                                                                                                                                                                                                |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write endurance                                         |                                                                                                                                                                                                                             |                                                                                                                                                                                            |                                                                                                                                                                                                |                                                                                                                                                                                                                        | 3                                                                                                                                                                                                                                                    |

| <ul> <li>EEPROM backup to FlexRAM ratio = 16</li> </ul> | 35 K                                                                                                                                                                                                                        | 175 K                                                                                                                                                                                      |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

| EEPROM backup to FlexRAM ratio = 128                    | 315 K                                                                                                                                                                                                                       | 1.6 M                                                                                                                                                                                      |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

| EEPROM backup to FlexRAM ratio = 512                    | 1.27 M                                                                                                                                                                                                                      | 6.4 M                                                                                                                                                                                      |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

| • EEPROM backup to FlexRAM ratio = 4096                 | 10 M                                                                                                                                                                                                                        | 50 M                                                                                                                                                                                       |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

| EEPROM backup to FlexRAM ratio = 8192                   | 20 M                                                                                                                                                                                                                        | 100 M                                                                                                                                                                                      |                                                                                                                                                                                                | writes                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |

|                                                         | <ul> <li>Write endurance</li> <li>EEPROM backup to FlexRAM ratio = 16</li> <li>EEPROM backup to FlexRAM ratio = 128</li> <li>EEPROM backup to FlexRAM ratio = 512</li> <li>EEPROM backup to FlexRAM ratio = 4096</li> </ul> | Write endurance• EEPROM backup to FlexRAM ratio = 1635 K• EEPROM backup to FlexRAM ratio = 128315 K• EEPROM backup to FlexRAM ratio = 5121.27 M• EEPROM backup to FlexRAM ratio = 409610 M | Write endurance35 K• EEPROM backup to FlexRAM ratio = 1635 K• EEPROM backup to FlexRAM ratio = 128315 K• EEPROM backup to FlexRAM ratio = 5121.27 M• EEPROM backup to FlexRAM ratio = 409610 M | Write endurance35 K175 K• EEPROM backup to FlexRAM ratio = 1635 K175 K• EEPROM backup to FlexRAM ratio = 128315 K1.6 M• EEPROM backup to FlexRAM ratio = 5121.27 M6.4 M• EEPROM backup to FlexRAM ratio = 409610 M50 M | Write endurance35 K175 Kwrites• EEPROM backup to FlexRAM ratio = 1635 K175 Kwrites• EEPROM backup to FlexRAM ratio = 128315 K1.6 Mwrites• EEPROM backup to FlexRAM ratio = 5121.27 M6.4 Mwrites• EEPROM backup to FlexRAM ratio = 409610 M50 Mwrites |

Table 24. NVM reliability specifications (continued)

- Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

- 2. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  T<sub>i</sub>  $\leq$  125°C.

- Write endurance represents the number of writes to each FlexRAM location at -40°C ≤Tj ≤ 125°C influenced by the cycling endurance of the FlexNVM (same value as data flash) and the allocated EEPROM backup. Minimum and typical values assume all byte-writes to FlexRAM.

#### 8.5 Analog

#### 8.5.1 12-bit Cyclic Analog-to-Digital Converter (ADC) Parameters Table 25. 12-bit ADC Electrical Specifications

| Characteristic                    | Symbol              | Min               | Тур | Max               | Unit             |

|-----------------------------------|---------------------|-------------------|-----|-------------------|------------------|

| Recommended Operating Conditions  |                     |                   | •   |                   |                  |

| Supply Voltage <sup>1</sup>       | V <sub>DDA</sub>    | 2.7               | 3.3 | 3.6               | V                |

| Vrefh Supply Voltage <sup>2</sup> | Vrefhx              | 3.0               |     | V <sub>DDA</sub>  | V                |

| ADC Conversion Clock <sup>3</sup> | f <sub>ADCCLK</sub> | 0.6               |     | 20                | MHz              |

| Conversion Range                  | R <sub>AD</sub>     | V <sub>REFL</sub> |     | V <sub>REFH</sub> | V                |

| Input Voltage Range <sup>4</sup>  | V <sub>ADIN</sub>   |                   |     |                   | V                |

| External Reference                |                     | V <sub>REFL</sub> |     | V <sub>REFH</sub> |                  |

| Internal Reference                |                     | V <sub>SSA</sub>  |     | V <sub>DDA</sub>  |                  |

| Timing and Power                  |                     |                   |     |                   |                  |

| Conversion Time                   | t <sub>ADC</sub>    |                   | 6   |                   | ADC Clock Cycles |

| Sample Time                       | t <sub>ADS</sub>    | 1                 |     | 5                 | ADC Clock Cycles |

| ADC Power-Up Time (from adc_pdn)  | t <sub>ADPU</sub>   |                   | 13  |                   | ADC Clock Cycles |

Table continues on the next page...

#### System modules

| Table 25. | 12-bit ADC Electrical | Specifications ( | (continued) |

|-----------|-----------------------|------------------|-------------|

|-----------|-----------------------|------------------|-------------|

| Characteristic                                                                                                                                          | Symbol                | Min                  | Тур                   | Max                                           | Unit             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|-----------------------|-----------------------------------------------|------------------|

| ADC RUN Current (per ADC block)                                                                                                                         | I <sub>ADRUN</sub>    |                      |                       |                                               | mA               |

| • at 600 kHz ADC Clock, LP mode                                                                                                                         |                       |                      | 1                     |                                               |                  |

| • ≤ 8.33 MHz ADC Clock, 00 mode                                                                                                                         |                       |                      | 5                     |                                               |                  |

| • ≤ 12.5 MHz ADC Clock, 01 mode                                                                                                                         |                       |                      | 9                     |                                               |                  |

| • ≤ 16.67 MHz ADC Clock, 10 mode                                                                                                                        |                       |                      | 15                    |                                               |                  |

| <ul> <li>≤ 20 MHz ADC Clock, 11 mode</li> </ul>                                                                                                         |                       |                      | 19                    |                                               |                  |

| ADC Powerdown Current (adc_pdn enabled)                                                                                                                 | I <sub>ADPWRDWN</sub> |                      | 0.02                  |                                               | μA               |

| V <sub>REFH</sub> Current                                                                                                                               | I <sub>VREFH</sub>    |                      | 0.001                 |                                               | μΑ               |

| Accuracy (DC or Absolute)                                                                                                                               |                       |                      | ł                     |                                               |                  |

| Integral non-Linearity <sup>5</sup>                                                                                                                     | I <sub>NL</sub>       |                      | +/- 3                 | +/- 5                                         | LSB <sup>6</sup> |

| Differential non-Linearity <sup>5</sup>                                                                                                                 | DNL                   |                      | +/- 0.6               | +/- 1                                         | LSB <sup>6</sup> |

| Monotonicity                                                                                                                                            |                       |                      |                       | <b>۲</b> ــــــــــــــــــــــــــــــــــــ |                  |

| Offset <sup>7</sup> <ul> <li>≤15 MHz ADC Clock Internal/External<br/>Reference</li> <li>&gt;15 MHz ADC Clock Internal/External<br/>Reference</li> </ul> | V <sub>OFFSET</sub>   | +/- 4.03<br>+/- 7.25 | +/- 8.86<br>+/- 13.70 |                                               | mV               |

| Gain Error                                                                                                                                              | E <sub>GAIN</sub>     |                      | 0.801 to<br>0.809     | 0.798 to<br>0.814                             | mV               |

| AC Specifications <sup>8</sup>                                                                                                                          |                       |                      |                       | I I                                           |                  |

| Signal to Noise Ratio                                                                                                                                   | SNR                   |                      | 59                    |                                               | dB               |

| Total Harmonic Distortion                                                                                                                               | THD                   |                      | 64                    |                                               | dB               |

| Spurious Free Dynamic Range                                                                                                                             | SFDR                  |                      | 65                    |                                               | dB               |

| Signal to Noise plus Distortion                                                                                                                         | SINAD                 |                      | 59                    |                                               | dB               |

| Effective Number of Bits                                                                                                                                | ENOB                  |                      | 9.5                   |                                               | bits             |

| ADC Inputs                                                                                                                                              |                       |                      |                       |                                               |                  |

| Input Leakage Current                                                                                                                                   | I <sub>IN</sub>       |                      | 0                     | +/-2                                          | μA               |

| Input Injection Current <sup>9</sup>                                                                                                                    | I <sub>INJ</sub>      |                      |                       | +/-3                                          | mA               |

| Input Capacitance                                                                                                                                       | C <sub>ADI</sub>      |                      |                       |                                               | pF               |

| Sampling Capacitor                                                                                                                                      |                       |                      |                       |                                               |                  |

| • 1x mode                                                                                                                                               |                       |                      | 1.4                   |                                               |                  |

| • 2x mode                                                                                                                                               |                       |                      | 2.8                   |                                               |                  |

| • 4x mode                                                                                                                                               |                       |                      | 5.6                   |                                               |                  |

1. If the ADC's reference is from V<sub>DDA</sub>: When V<sub>DDA</sub> is below 3.0 V, the ADC functions but ADC specifications are not guaranteed.

- 2. When the input is at the  $V_{refi}$  level, the resulting output will be all zeros (hex 000), plus any error contribution due to offset and gain error. When the input is at the V<sub>refh</sub> level the output will be all ones (hex FFF), minus any error contribution due to offset and gain error.

- 3. ADC clock duty cycle min/max is 45/55%

- 4. When V<sub>refh</sub> is supplied externally

- 5.  $I_{NL}$  measured from  $V_{IN} = V_{REFL}$  to  $V_{IN} = V_{REFH}$ . 6. LSB = Least Significant Bit = 0.806 mV at 3.3 V VDDA, x1 Gain Setting

| Symbol                                   | Description                                                                                                                  | Min.                  | Тур. | Max.            | Unit             |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------|------------------|

| V <sub>H</sub>                           | Analog comparator hysteresis <sup>1</sup>                                                                                    |                       |      |                 |                  |

|                                          | • CR0[HYSTCTR] = 00                                                                                                          | _                     | 5    | 13              | mV               |

|                                          | • CR0[HYSTCTR] = 01                                                                                                          | _                     | 10   | 48              | mV               |

|                                          | • CR0[HYSTCTR] = 10                                                                                                          | _                     | 20   | 105             | mV               |

|                                          | • CR0[HYSTCTR] = 11                                                                                                          | _                     | 30   | 148             | mV               |

| V <sub>CMPOh</sub>                       | Output high                                                                                                                  | V <sub>DD</sub> – 0.5 | _    | _               | V                |

| V <sub>CMPOI</sub>                       | Output low                                                                                                                   | —                     | _    | 0.5             | V                |

| t <sub>DHS</sub>                         | Propagation delay, high-speed mode (EN=1, PMODE=1) <sup>2</sup>                                                              |                       |      |                 | ns               |

| t <sub>DLS</sub>                         | Propagation delay, low-speed mode (EN=1, PMODE=0)                                                                            |                       | 250  |                 | ns               |

|                                          | Analog comparator initialization delay <sup>3</sup>                                                                          | —                     | _    | 40              | μs               |

| I <sub>DAC6b</sub>                       | 6-bit DAC current adder (enabled)                                                                                            | —                     | 7    | _               | μA               |

|                                          | 6-bit DAC reference inputs, Vin1 and Vin2                                                                                    | V <sub>DDA</sub>      | _    | V <sub>DD</sub> | V                |

|                                          | There are two reference input options selectable (via VRSEL control bit). The reference options must fall within this range. |                       |      |                 |                  |

| INL                                      | 6-bit DAC integral non-linearity                                                                                             | -0.5                  | —    | 0.5             | LSB <sup>4</sup> |

| DNL 6-bit DAC differential non-linearity |                                                                                                                              | -0.3                  | _    | 0.3             | LSB              |

#### Table 29. Comparator and 6-bit DAC electrical specifications (continued)

1. Typical hysteresis is measured with input voltage range limited to 0.6 to V<sub>DD</sub>-0.6V.

2. Signal swing is 100 mV

3. Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

4. 1 LSB =  $V_{reference}/64$

MC56F844xx Advance Information Data Sheet, Rev. 2, 06/2012.

**Design Considerations**

Figure 22. Timing Definition for Fast and Standard Mode Devices on the I<sup>2</sup>C Bus

## 9 Design Considerations

#### 9.1 Thermal Design Considerations

An estimation of the chip junction temperature, TJ, can be obtained from the equation:

$T_J = T_A + (R_{\Theta JA} \times P_D)$

Where,

$T_A$  = Ambient temperature for the package (°C)

$R_{\Theta IA}$  = Junction-to-ambient thermal resistance (°C/W)

$P_D$  = Power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry-standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single-layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low-power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed as the sum of a junction-tocase thermal resistance and a case-to-ambient thermal resistance:

$R_{\Theta JA} = R_{\Theta JC} + R_{\Theta CA}$

Where,

$R_{\Theta JA}$  = Package junction-to-ambient thermal resistance (°C/W)

MC56F844xx Advance Information Data Sheet, Rev. 2, 06/2012.

## **12 Product Documentation**

The documents listed in Table 36 are required for a complete description and proper design with the device. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, or online at http://www.freescale.com.

MC56F844xx Advance Information Data Sheet, Rev. 2, 06/2012.

Freescale Semiconductor, Inc.

| Торіс                                    | Description                                                                                                                       | Document Number  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|

| DSP56800E/DSP56800EX<br>Reference Manual | Detailed description of the 56800EX family architecture, 32-bit digital signal controller core processor, and the instruction set | DSP56800ERM      |

| MC56F844xx Reference Manual              | Detailed functional description and programming model                                                                             | MC56F844XXRM     |

| Serial Bootloader User Guide             | Detailed description of the Serial Bootloader in the DSC family of devices                                                        | TBD              |

| MC56F844xx Data Sheet                    | Electrical and timing specifications, pin descriptions, and package information (this document)                                   | MC56F844XX       |

| MC56F84xxx Errata                        | Details any chip issues that might be present                                                                                     | MC56F84XXX_0N27E |

Table 36.

Device Documentation

## **13 Revision History**

The following table summarizes changes to this document since the release of the previous version.

| Rev. | Date    | Substantial Changes                                          |  |

|------|---------|--------------------------------------------------------------|--|

| 2    | 06/2012 | his is the first publicly released version of this document. |  |