# E·XFL

#### NXP USA Inc. - MC56F84462VLH Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore Processor56800EXCore Size32-Bit Single-CoreSpeed60MHzConnectivityCANbus, I°C, LINbus, SCI, SPIPeripheralsBrown-out Detect/Reset, DMA, LVD, POR, PWM, WDTNumber of I/O54Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 16x12b; D/A 1x12b |                            |                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed60MHzConnectivityCANbus, I²C, LINbus, SCI, SPIPeripheralsBrown-out Detect/Reset, DMA, LVD, POR, PWM, WDTNumber of I/O54Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6V                                                                              | Product Status             | Active                                                                |

| Speed60MHzConnectivityCANbus, I²C, LINbus, SCI, SPIPeripheralsBrown-out Detect/Reset, DMA, LVD, POR, PWM, WDTNumber of I/O54Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6V                                                                                                         | Core Processor             | 56800EX                                                               |

| ConnectivityCANbus, I²C, LINbus, SCI, SPIPeripheralsBrown-out Detect/Reset, DMA, LVD, POR, PWM, WDTNumber of I/O54Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6V                                                                                                                   | Core Size                  | 32-Bit Single-Core                                                    |

| PeripheralsBrown-out Detect/Reset, DMA, LVD, POR, PWM, WDTNumber of I/O54Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6V                                                                                                                                                            | Speed                      | 60MHz                                                                 |

| Number of I/O54Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6V                                                                                                                                                                                                                      | Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6V                                                                                                                                                                                                                                     | Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                       |

| Program Memory TypeFLASHEEPROM Size2K × 8RAM Size24K × 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6V                                                                                                                                                                                                                                                                        | Number of I/O              | 54                                                                    |

| EEPROM Size2K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6V                                                                                                                                                                                                                                                                                                | Program Memory Size        | 128KB (128K x 8)                                                      |

| RAM Size         24K x 8           Voltage - Supply (Vcc/Vdd)         3V ~ 3.6V                                                                                                                                                                                                                                                                                    | Program Memory Type        | FLASH                                                                 |

| Voltage - Supply (Vcc/Vdd) 3V ~ 3.6V                                                                                                                                                                                                                                                                                                                               | EEPROM Size                | 2K x 8                                                                |

|                                                                                                                                                                                                                                                                                                                                                                    | RAM Size                   | 24K x 8                                                               |

| Data Converters     A/D 16x12b; D/A 1x12b                                                                                                                                                                                                                                                                                                                          | Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                             |

|                                                                                                                                                                                                                                                                                                                                                                    | Data Converters            | A/D 16x12b; D/A 1x12b                                                 |

| Oscillator Type Internal                                                                                                                                                                                                                                                                                                                                           | Oscillator Type            | Internal                                                              |

| Operating Temperature -40°C ~ 105°C (TA)                                                                                                                                                                                                                                                                                                                           | Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                                                                                                        | Mounting Type              | Surface Mount                                                         |

| Package / Case 64-LQFP                                                                                                                                                                                                                                                                                                                                             | Package / Case             | 64-LQFP                                                               |

| Supplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                             | Supplier Device Package    | 64-LQFP (10x10)                                                       |

|                                                                                                                                                                                                                                                                                                                                                                    | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f84462vlh |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- 32-bit arithmetic and logic multi-bit shifter

- Four 36-bit accumulators, including extension bits

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Bit reverse address mode, effectively supporting DSP and Fast Fourier Transform algorithms

- Full shadowing of the register stack for zero-overhead context saves and restores: nine shadow registers corresponding to the R0, R1, R2, R3, R4, R5, N, N3, and M01 address registers

- Instruction set supporting both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Enhanced bit manipulation instruction set

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- Priority level setting for interrupt levels

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, real-time debugging that is independent of processor speed

## **1.3 Operation Parameters**

- Up to 60 MHz operation at -40 °C to 105 °C ambient temperature

- Single 3.3 V power supply

- Supply range:  $V_{DD}$   $V_{SS}$  = 2.7 V to 3.6 V,  $V_{DDA}$   $V_{SSA}$  = 2.7 V to 3.6 V

## 1.4 On-Chip Memory and Memory Protection

- Modified dual Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Internal flash memory with security and protection to prevent unauthorized access

- Memory resource protection (MRP) unit to protect supervisor programs and resources from user programs

- Programming code can reside in flash memory during flash programming

- The dual-ported RAM controller supports concurrent instruction fetches and data accesses, or dual data accesses, by the DSC core.

- Concurrent accesses provide increased performance.

- The data and instruction arrive at the core in the same cycle, reducing latency.

- On-chip memory

- Up to 128 KW program/data flash memory

- Up to 16 KW dual port data/program RAM

MC56F844xx Advance Information Data Sheet, Rev. 2, 06/2012.

#### 1.6.13 Phase Locked Loop

- Wide programmable output frequency: 240 MHz to 400 MHz

- Input reference clock frequency: 8 MHz to 16 MHz

- Detection of loss of lock and loss of reference clock

- Ability to power down

### 1.6.14 Clock sources

#### 1.6.14.1 On-Chip Oscillators

- Tunable 8 MHz relaxation oscillator with 400 kHz at standby mode (divide-by-two output)

- 32 kHz low frequency clock as secondary clock source for COP, EWM, PIT

#### 1.6.14.2 Crystal Oscillator

- Support for both high ESR crystal oscillator (greater than 100-ohm ESR) and ceramic resonator

- 4 MHz to 16 MHz operating frequency

### 1.6.15 Cyclic Redundancy Check (CRC) Generator

- Hardware 16/32-bit CRC generator

- High-speed hardware CRC calculation

- Programmable initial seed value

- Programmable 16/32-bit polynomial

- Error detection for all single, double, odd, and most multi-bit errors

- Option to transpose input data or output data (CRC result) bitwise or bytewise,<sup>1</sup> which is required for certain CRC standards

- Option for inversion of final CRC result

## 1.6.16 General Purpose I/O (GPIO)

- 5 V tolerance

- Individual control of peripheral mode or GPIO mode for each pin

- Programmable push-pull or open drain output

- Configurable pullup or pulldown on all input pins

<sup>1.</sup> A bytewise transposition is not possible when accessing the CRC data register via 8-bit accesses. In this case, user software must perform the bytewise transposition.

- All pins except JTAG and RESETB pins default to be GPIO inputs

- 2 mA / 9 mA source/sink capability

- Controllable output slew rate

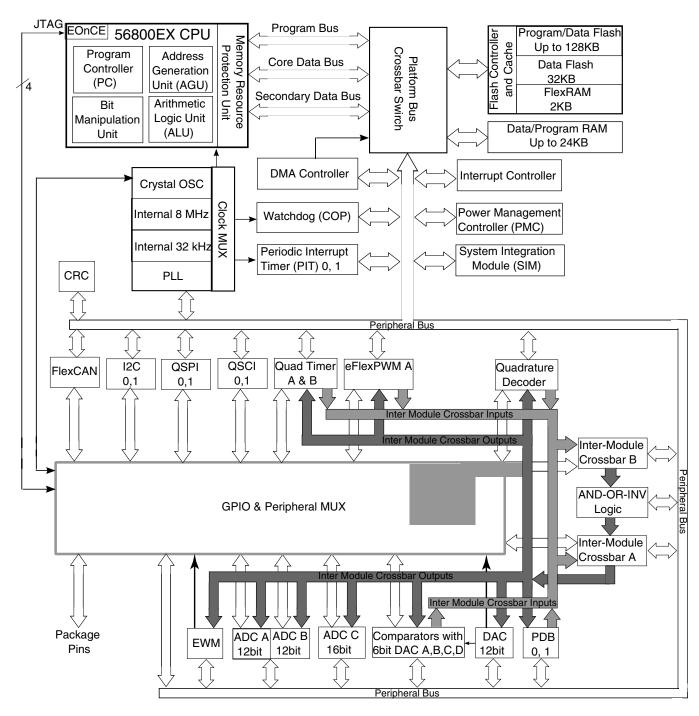

## 1.7 Block Diagrams

The 56800EX core is based on a modified dual Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C compilers to enable rapid development of optimized control applications.

The device's basic architecture appears in Figure 1 and Figure 2. Figure 1 illustrates how the 56800EX system buses communicate with internal memories and the IPBus interface and the internal connections among each unit of the 56800EX core. Figure 2 shows the peripherals and control blocks connected to the IPBus bridge. See the specific device's Reference Manual for details.

Figure 2. System Diagram

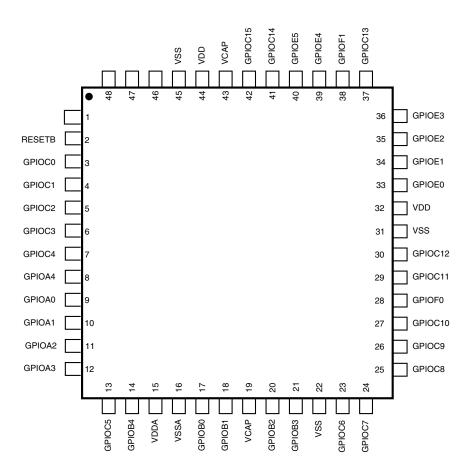

# 2 Signal groups

The input and output signals of the MC56F84xxx are organized into functional groups, as detailed in Table 2.

| Functional Group                                                      | Number<br>of Pins in<br>48LQFP | Number<br>of Pins in<br>64LQFP | Number<br>of Pins in<br>80LQFP | Number<br>of Pins in<br>100LQFP |  |

|-----------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|---------------------------------|--|

| Power Inputs (V <sub>DD</sub> , V <sub>DDA</sub> , V <sub>CAP</sub> ) | 5                              | 6                              | 6                              | 6                               |  |

| Ground (V <sub>SS</sub> , V <sub>SSA</sub> )                          | 4                              | 4                              | 4                              | 4                               |  |

| Reset                                                                 | 1                              | 1                              | 1                              | 1                               |  |

| eFlexPWM ports, not including fault pins                              | 6                              | 9                              | N/A                            | N/A                             |  |

| Queued Serial Peripheral Interface (QSPI) ports                       | 5                              | 6                              | 8                              | 15                              |  |

| Queued Serial Communications Interface (QSCI) ports                   | 6                              | 9                              | 13                             | 15                              |  |

| Inter-Integrated Circuit (I <sup>2</sup> C) interface ports           | 4                              | 6                              | 6                              | 6                               |  |

| 12-bit Analog-to-Digital Converter (Cyclic ADC) inputs                | 10                             | 16                             | 16                             | 16                              |  |

| 16-bit Analog-to-Digital Converter (SAR ADC) inputs                   | 2                              | 8                              | 10                             | 16                              |  |

| Analog Comparator inputs/outputs                                      | 10/4                           | 13/6                           | 13/6                           | 16/6                            |  |

| 12-bit Digital-to-Analog output                                       | 1                              | 1                              | 1                              | 1                               |  |

| Quad Timer Module (TMR) ports                                         | 6                              | 9                              | 11                             | 13                              |  |

| Controller Area Network (FlexCAN)                                     | 2                              | 2                              | 2                              | 2                               |  |

| Inter-Module Crossbar inputs/outputs                                  | 12/2                           | 16/6                           | 19/17                          | 25/19                           |  |

| Clock inputs/outputs                                                  | 2/2                            | 2/2                            | 2/3                            | 2/3                             |  |

| JTAG / Enhanced On-Chip Emulation (EOnCE)                             | 4                              | 4                              | 4                              | 4                               |  |

Table 2. Functional Group Pin Allocations

# 3 Ordering parts

## 3.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to www.freescale.com and perform a part number search for the following device numbers: MC56F84

# 4 Part identification

# 4.4 Example

This is an example part number: MC56F84789VLL

# 5 Terminology and guidelines

## 5.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

### 5.1.1 Example

This is an example of an operating requirement, which you must meet for the accompanying operating behaviors to be guaranteed:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

## 5.2 Definition: Operating behavior

An *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

## 5.2.1 Example

This is an example of an operating behavior, which is guaranteed if you meet the accompanying operating requirements:

| Symbol | Description                                  | Min. | Max. | Unit |

|--------|----------------------------------------------|------|------|------|

|        | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μA   |

## 5.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

## 5.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

# 5.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

## 5.4.1 Example

This is an example of an operating rating:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 | 1.2  | V    |

Absolute maximum ratings in Table 4 are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond these ratings may affect device reliability or cause permanent damage to the device.

Unless otherwise stated, all specifications within this chapter apply over the temperature range of -40°C to 105°C ambient temperature over the following supply ranges: VSS = VSSA = 0 V, VDD = VDDA = 3.0 V to 3.6 V, CL  $\leq$  50 pF, f<sub>OP</sub> = 60 MHz.

#### CAUTION

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum-rated voltages to this highimpedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

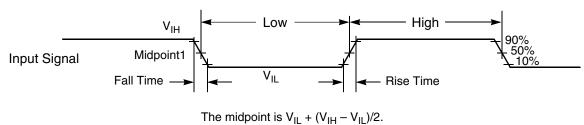

# 7.2 AC Electrical Characteristics

Tests are conducted using the input levels specified in Table 7. Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured between the 10% and 90% points, as shown in Figure 3.

#### Figure 3. Input Signal Measurement References

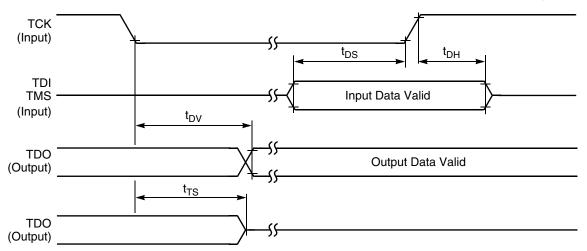

Figure 4 shows the definitions of the following signal states:

- Active state, when a bus or signal is driven, and enters a low impedance state

- Tri-stated, when a bus or signal is placed in a high impedance state

- Data Valid state, when a signal level has reached  $V_{OL}$  or  $V_{OH}$

- Data Invalid state, when a signal level is in transition between  $V_{\mbox{OL}}$  and  $V_{\mbox{OH}}$

Figure 6. Test Access Port Timing Diagram

## 8.2 System modules

#### 8.2.1 Voltage Regulator Specifications

The regulator supplies approximately 1.2 V to the MC56F84xxx's core logic. This regulator requires an external 2.2  $\mu$ F capacitor on each V<sub>CAP</sub> pin for proper operation. Ceramic and tantalum capacitors tend to provide better performance tolerances. The output voltage can be measured directly on the V<sub>CAP</sub> pin. The specifications for this regulator are shown in Table 16.

| Characteristic                                               | Symbol           | Min | Тур  | Max | Unit    |

|--------------------------------------------------------------|------------------|-----|------|-----|---------|

| Output Voltage <sup>1</sup>                                  | V <sub>CAP</sub> | —   | 1.22 | —   | V       |

| Short Circuit Current <sup>2</sup>                           | I <sub>SS</sub>  | —   | 600  | TBD | mA      |

| Short Circuit Tolerance (V <sub>CAP</sub> shorted to ground) | T <sub>RSC</sub> | _   |      | 30  | Minutes |

Table 16. Regulator 1.2 V Parameters

1. Value is after trim

2. Guaranteed by design

| Table 17. | Bandgap | Electrical | <b>Specifications</b> |

|-----------|---------|------------|-----------------------|

|-----------|---------|------------|-----------------------|

| Characteristic                 | Symbol           | Min | Тур  | Max | Unit |

|--------------------------------|------------------|-----|------|-----|------|

| Reference Voltage (after trim) | V <sub>REF</sub> | —   | 1.21 | _   | V    |

## 8.3 Clock modules

# 8.3.3 External Crystal or Resonator Requirement

| Table 20. | Crystal or | Resonator | Requirement |

|-----------|------------|-----------|-------------|

|-----------|------------|-----------|-------------|

| Characteristic         | Symbol            | Min | Тур | Max | Unit |

|------------------------|-------------------|-----|-----|-----|------|

| Frequency of operation | f <sub>xosc</sub> | 4   | 8   | 16  | MHz  |

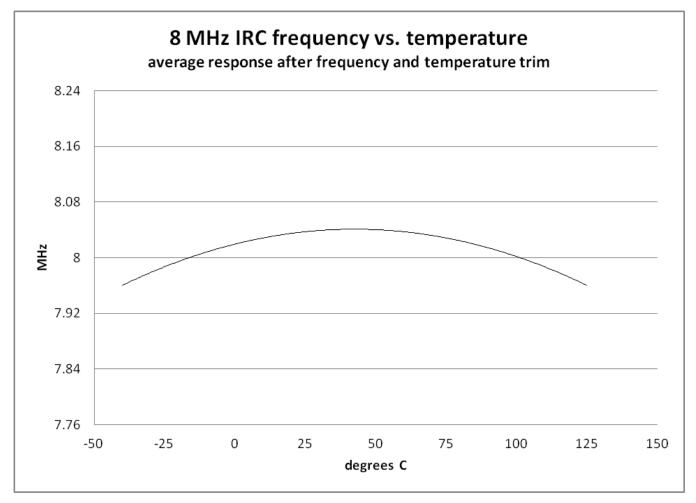

## 8.3.4 Relaxation Oscillator Timing

#### Table 21. Relaxation Oscillator Electrical Specifications

| Characteristic                                                                  | Symbol | Min  | Тур         | Мах          | Unit |

|---------------------------------------------------------------------------------|--------|------|-------------|--------------|------|

| 8 MHz Output Frequency <sup>1</sup>                                             |        |      |             |              |      |

| RUN Mode<br>• 0°C to 105°C<br>• -40°C to 105°C                                  |        | 7.84 | 8           | 8.16         | MHz  |

| Standby Mode (IRC trimmed @ 8 MHz)<br>• -40°C to 105°C                          |        | 7.76 | 8           | 8.24         |      |

|                                                                                 |        | TBD  | TBD         | TBD          | kHz  |

| 8 MHz Frequency Variation                                                       |        |      |             |              |      |

| RUN Mode                                                                        |        |      |             |              |      |

| Due to temperature<br>• 0°C to 105°C<br>• -40°C to 105°C                        |        |      | +/-1.5      | +/-2<br>+/-3 | %    |

| Standby Mode                                                                    |        |      | Unspecified | +/-3         |      |

| 32 kHz Output Frequency <sup>2</sup>                                            |        |      |             |              |      |

| RUN Mode<br>• -40°C to 105°C                                                    |        |      |             |              |      |

|                                                                                 |        | TBD  | 32          | TBD          | kHz  |

| 32 kHz Output Frequency Variation                                               |        |      |             |              |      |

| RUN Mode                                                                        |        |      |             |              |      |

| Due to temperature<br>• -40°C to 105°C                                          |        |      | +/-2.5      | +/-4         | %    |

| Stabilization Time                                                              | tstab  |      |             |              |      |

| <ul> <li>8 MHz output<sup>3</sup></li> <li>32 kHz output<sup>4</sup></li> </ul> |        |      | 0.12        | 0.4          | μs   |

|                                                                                 |        |      | 14.4        | 16.2         |      |

| Output Duty Cycle                                                               |        | 48   | 50          | 52           | %    |

1. Frequency after application of 8 MHz trim

2. Frequency after application of 32 kHz trim

3. Standby to run mode transition

4. Power down to run mode transition

Figure 8. Relaxation Oscillator Temperature Variation (Typical) After Trim (Preliminary)

# 8.4 Memories and memory interfaces

#### 8.4.1 Flash Memory Characteristics Table 22. Flash Timing Parameters

| Characteristic                                  | Symbol        | Min | Тур | Max | Unit |

|-------------------------------------------------|---------------|-----|-----|-----|------|

| Longword Program high-voltage time <sup>1</sup> | thvpgm4       | —   | 63  | 143 | μs   |

| Sector Erase high-voltage time <sup>2</sup>     | thversscr     | —   | 13  | 113 | ms   |

| Erase Block high-voltage time for 256 KB        | thversblk256k | —   | 52  | 452 | ms   |

1. There is additional overhead that is part of the programming sequence. See the device Reference Manual for detail.

2. Specifies page erase time.

## 8.5.2 16-bit SAR ADC electrical specifications

#### 8.5.2.1 16-bit ADC operating conditions Table 26. 16-bit ADC operating conditions

| Symbol            | Description                       | Conditions                                                                                                      | Min.             | Typ. <sup>1</sup> | Max.             | Unit | Notes |

|-------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|-------------------|------------------|------|-------|

| $V_{DDA}$         | Supply voltage                    | Absolute                                                                                                        | 2.7              | _                 | 3.6              | V    |       |

| $\Delta V_{DDA}$  | Supply voltage                    | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDA</sub> )                                                   | -100             | 0                 | +100             | mV   | 2     |

| $\Delta V_{SSA}$  | Ground voltage                    | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSA</sub> )                                                   | -100             | 0                 | +100             | mV   | 2     |

| $V_{REFH}$        | ADC reference voltage high        | Absolute                                                                                                        | V <sub>DDA</sub> | V <sub>DDA</sub>  | V <sub>DDA</sub> | V    | 3     |

| V <sub>REFL</sub> | ADC reference<br>voltage low      | Absolute                                                                                                        | V <sub>SSA</sub> | V <sub>SSA</sub>  | V <sub>SSA</sub> | V    | 4     |

| V <sub>ADIN</sub> | Input voltage                     |                                                                                                                 | V <sub>SSA</sub> | —                 | V <sub>DDA</sub> | V    |       |

| C <sub>ADIN</sub> | Input capacitance                 | 16 bit modes                                                                                                    | _                | 8                 | 10               | pF   |       |

|                   |                                   | • 8/10/12 bit modes                                                                                             | —                | 4                 | 5                |      |       |

| R <sub>ADIN</sub> | Input resistance                  |                                                                                                                 | _                | 2                 | 5                | kΩ   |       |

| R <sub>AS</sub>   | Analog source<br>resistance       | 12 bit modes<br>f <sub>ADCK</sub> < 4MHz                                                                        | _                | _                 | 5                | kΩ   | 5     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | ≤ 12 bit modes                                                                                                  | 1.0              |                   | 18.0             | MHz  | 6     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | 16 bit modes                                                                                                    | 2.0              | _                 | 12.0             | MHz  | 6     |

| C <sub>rate</sub> | ADC conversion<br>rate            | ≤ 12 bit modes<br>No ADC hardware averaging<br>Continuous conversions<br>enabled, subsequent<br>conversion time | 20.000           | _                 | 818.330          | Ksps | 7     |

| C <sub>rate</sub> | ADC conversion<br>rate            | 16 bit modes<br>No ADC hardware averaging<br>Continuous conversions<br>enabled, subsequent<br>conversion time   | 37.037           |                   | 461.467          | Ksps | 7     |

Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- 2. DC potential difference.

- 3.  $V_{\text{REFH}}$  is internally tied to  $V_{\text{DDA}}$ .

- 4.  $V_{\text{REFL}}$  is internally tied to  $V_{\text{SSA}}$ .

- 5. This resistance is external to MCU. The analog source resistance should be kept as low as possible in order to achieve the best results. The results in this datasheet were derived from a system which has <8  $\Omega$  analog source resistance. The R<sub>AS</sub>/ C<sub>AS</sub> time constant should be kept to <1ns.

- 6. To use the maximum ADC conversion clock frequency, the ADHSC bit should be set and the ADLPC bit should be clear.

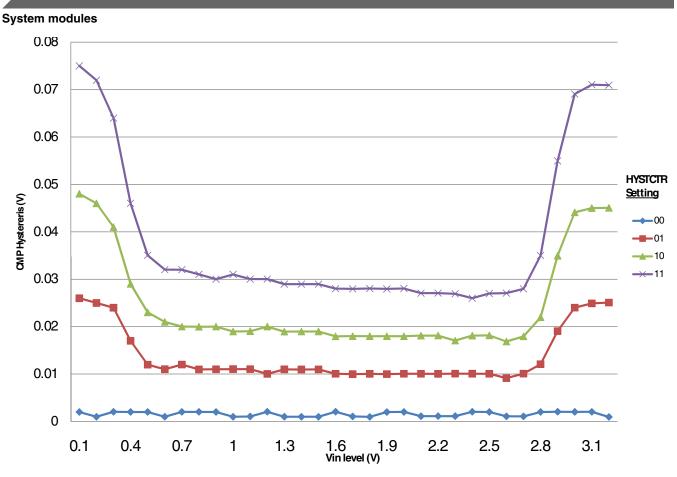

#### System modules

| Symbol             | Description                        | Conditions <sup>1</sup>  | Min. | Typ. <sup>2</sup>       | Max. | Unit             | Notes                                                        |

|--------------------|------------------------------------|--------------------------|------|-------------------------|------|------------------|--------------------------------------------------------------|

| E <sub>FS</sub>    | Full-scale error                   | 12 bit modes             | —    | -4                      | -5.4 | LSB <sup>4</sup> | V <sub>ADIN</sub> =                                          |

|                    | • <12 bit modes                    | _                        | -1.4 | -1.8                    |      | V <sub>DDA</sub> |                                                              |

|                    |                                    |                          |      |                         |      |                  | 5                                                            |

| $E_Q$              | Quantization error                 | 16 bit modes             | _    | -1 to 0                 | —    | LSB <sup>4</sup> |                                                              |

| enor               | 12 bit modes                       | _                        | —    | ±0.5                    |      |                  |                                                              |

| ENOB               | Effective number                   | 16 bit single-ended mode |      |                         |      |                  | 6                                                            |

|                    | of bits                            | • Avg=32                 | 12.2 | 13.9                    | _    | bits             |                                                              |

|                    |                                    | • Avg=4                  | 11.4 | 13.1                    |      | bits             |                                                              |

|                    |                                    | 12 bit single-ended mode |      |                         |      |                  |                                                              |

|                    |                                    | • Avg=32                 |      | 10.8                    |      | bits             |                                                              |

|                    |                                    | • Avg=1                  |      | 10.2                    | _    | bits             |                                                              |

| SINAD              | Signal-to-noise<br>plus distortion | See ENOB                 | 6.02 | 2 × ENOB + <sup>-</sup> | 1.76 | dB               |                                                              |

| THD Total harmonic | 16 bit single-ended mode           |                          |      |                         |      | 7                |                                                              |

|                    | distortion                         | • Avg=32                 | _    | -85                     | _    | dB               |                                                              |

|                    |                                    | 12 bit single-ended mode |      |                         |      |                  |                                                              |

|                    |                                    | • Avg=32                 | _    | -74                     | _    | dB               |                                                              |

| SFDR               | Spurious free                      | 16 bit single-ended mode |      |                         |      |                  | 7                                                            |

|                    | dynamic range                      | • Avg=32                 | 78   | 90                      | _    | dB               |                                                              |

|                    |                                    | 12 bit single-ended mode |      |                         |      |                  |                                                              |

|                    |                                    | • Avg=32                 |      | 78                      |      | dB               |                                                              |

| E <sub>IL</sub>    | Input leakage<br>error             |                          |      | $I_{ln} \times R_{AS}$  |      | mV               | I <sub>In</sub> =<br>leakag<br>curren                        |

|                    |                                    |                          |      |                         |      |                  | (refer t<br>the<br>device<br>voltage<br>and curr<br>operatir |

25°C

–40°C to 105°C

Temp sensor

Temp sensor

slope

voltage

$V_{\text{TEMP25}}$

1. All accuracy numbers assume the ADC is calibrated with  $V_{REFH} = V_{DDA}$ 2. Typical values assume  $V_{DDA} = 3.0 \text{ V}$ , Temp = 25°C,  $f_{ADCK} = 2.0 \text{ MHz}$  unless otherwise stated. Typical values are for reference only and are not tested in production.

\_\_\_\_

1.715

722

\_\_\_\_

\_

mV/°C

mV

8

Figure 12. Typical hysteresis vs. Vin level ( $V_{DD}$  = 3.3 V, PMODE = 0)

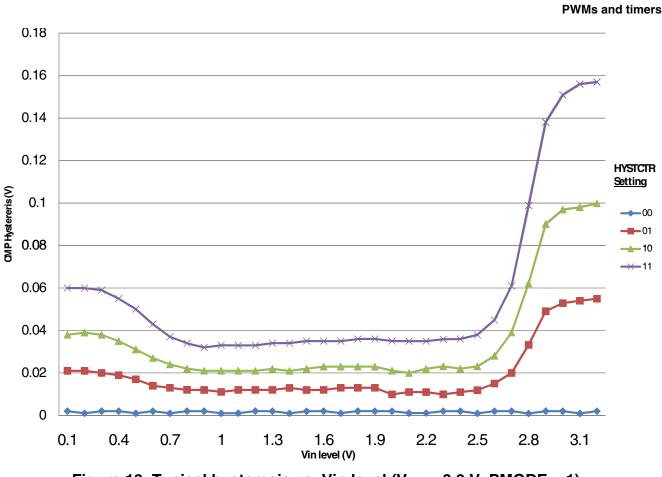

Figure 13. Typical hysteresis vs. Vin level ( $V_{DD}$  = 3.3 V, PMODE = 1)

# 8.6 PWMs and timers

## 8.6.1 PWM Characteristics

Table 30. PWM Timing Parameters

| Characteristic      | Symbol | Min | Тур | Max | Unit |

|---------------------|--------|-----|-----|-----|------|

| PWM clock frequency |        |     | 60  | 100 | MHz  |

# 8.6.2 Quad Timer Timing

Parameters listed are guaranteed by design.

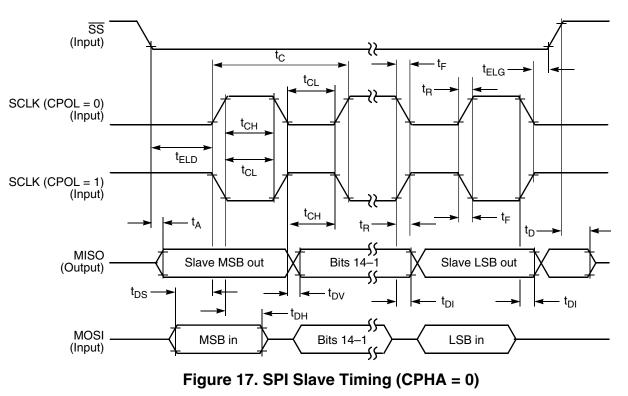

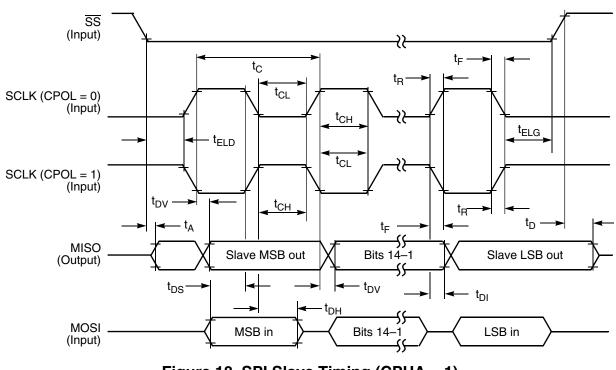

| Characteristic                                       | Symbol          | Min  | Max | Unit | See Figure |

|------------------------------------------------------|-----------------|------|-----|------|------------|

| Clock (SCK) high time                                | t <sub>CH</sub> |      |     |      | Figure 15  |

| Master                                               |                 | 27.6 | _   | ns   | Figure 16  |

| Slave                                                |                 | 27.6 | _   | ns   | Figure 17  |

|                                                      |                 |      |     |      | Figure 18  |

| Clock (SCK) low time                                 | t <sub>CL</sub> |      |     |      | Figure 18  |

| Master                                               |                 | 27.6 | _   | ns   |            |

| Slave                                                |                 | 27.6 | _   | ns   |            |

| Data set-up time required for inputs                 | t <sub>DS</sub> |      |     |      | Figure 15  |

| Master                                               |                 | 27.6 | _   | ns   | Figure 16  |

| Slave                                                |                 | 1    | _   | ns   | Figure 17  |

|                                                      |                 |      |     |      | Figure 18  |

| Data hold time required for inputs                   | t <sub>DH</sub> |      |     |      | Figure 15  |

| Master                                               |                 | 1    | _   | ns   | Figure 16  |

| Slave                                                |                 | 3    | _   | ns   | Figure 17  |

|                                                      |                 |      |     |      | Figure 18  |

| Access time (time to data active                     | t <sub>A</sub>  |      |     |      | Figure 18  |

| from high-impedance state)                           |                 | 5    | _   | ns   |            |

| Slave                                                |                 |      |     |      |            |

| Disable time (hold time to high-<br>impedance state) | t <sub>D</sub>  |      |     |      | Figure 18  |

| Slave                                                |                 | 5    | -   | ns   |            |

| Data valid for outputs                               | t <sub>DV</sub> |      |     |      | Figure 15  |

| Master                                               | ٢D٧             | _    | 8.3 | ns   | Figure 16  |

| Slave (after enable edge)                            |                 | _    | 25  | ns   | Figure 17  |

| Slave (alter enable edge)                            |                 |      | 25  | 113  | Figure 18  |

| Data invalid                                         | t <sub>DI</sub> |      |     |      | Figure 15  |

| Master                                               | וטי             | 0    | _   | ns   | Figure 16  |

| Slave                                                |                 | 0    |     |      | Figure 17  |

| Slave                                                |                 | 0    |     | ns   | Figure 18  |

| Rise time                                            | t_              |      |     |      | Figure 15  |

| Master                                               | t <sub>R</sub>  | _    | 1   | ne   |            |

| Slave                                                |                 | _    | 1   | ns   | Figure 16  |

| Slave                                                |                 | _    |     | ns   | Figure 17  |

| Fall time                                            | +               |      |     |      | Figure 18  |

| Master                                               | t <sub>F</sub>  |      | 4   |      | Figure 15  |

|                                                      |                 | _    | 1   | ns   | Figure 16  |

| Slave                                                |                 | —    | 1   | ns   | Figure 17  |

|                                                      |                 |      |     |      | Figure 18  |

Table 32. SPI Timing (continued)

Figure 18. SPI Slave Timing (CPHA = 1)

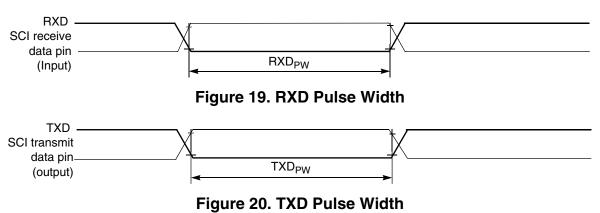

## 8.7.2 Queued Serial Communication Interface (SCI) Timing

Parameters listed are guaranteed by design.

| Characteristic                                                                              | Symbol                   | Min        | Мах                    | Unit                          | See Figure |

|---------------------------------------------------------------------------------------------|--------------------------|------------|------------------------|-------------------------------|------------|

| Baud rate <sup>1</sup>                                                                      | BR                       | _          | (f <sub>MAX</sub> /16) | Mbps                          | _          |

| RXD pulse width                                                                             | RXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 19  |

| TXD pulse width                                                                             | TXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 20  |

|                                                                                             | LIN                      | Slave Mode |                        | •                             |            |

| Deviation of slave node clock from nominal<br>clock rate before synchronization             | F <sub>TOL_UNSYNCH</sub> | -14        | 14                     | %                             | _          |

| Deviation of slave node clock relative to<br>the master node clock after<br>synchronization |                          | -2         | 2                      | %                             | _          |

| Minimum break character length                                                              | Т <sub>ВRЕАК</sub>       | 13         | _                      | Master<br>node bit<br>periods | _          |

|                                                                                             |                          | 11         | _                      | Slave node bit periods        | _          |

#### Table 33. SCI Timing

1. f<sub>MAX</sub> is the frequency of operation of the SCI clock in MHz, which can be selected system clock (max. 120 MHz depending on part number) or 2x system clock (max. 200 MHz) for the devices.

#### 8.7.3 Freescale's Scalable Controller Area Network (FlexCAN) Table 34. FlexCAN Timing Parameters

| Characteristic                     |                   | Min | Max | Unit |

|------------------------------------|-------------------|-----|-----|------|

| Baud Rate                          | BR <sub>CAN</sub> | —   | 1   | Mbps |

| CAN Wakeup dominant pulse filtered |                   | —   | 2   | μs   |

| CAN Wakeup dominant pulse pass     |                   | 5   | _   | μs   |

## **12 Product Documentation**

The documents listed in Table 36 are required for a complete description and proper design with the device. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, or online at http://www.freescale.com.

MC56F844xx Advance Information Data Sheet, Rev. 2, 06/2012.

Freescale Semiconductor, Inc.

| Торіс                                    | Description                                                                                                                       | Document Number  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|

| DSP56800E/DSP56800EX<br>Reference Manual | Detailed description of the 56800EX family architecture, 32-bit digital signal controller core processor, and the instruction set | DSP56800ERM      |

| MC56F844xx Reference Manual              | Detailed functional description and programming model                                                                             | MC56F844XXRM     |

| Serial Bootloader User Guide             | Detailed description of the Serial Bootloader in the DSC family of devices                                                        | TBD              |

| MC56F844xx Data Sheet                    | Electrical and timing specifications, pin descriptions, and package information (this document)                                   | MC56F844XX       |

| MC56F84xxx Errata                        | Details any chip issues that might be present                                                                                     | MC56F84XXX_0N27E |

Table 36.

Device Documentation

# **13 Revision History**

The following table summarizes changes to this document since the release of the previous version.

| Rev. | Date    | Substantial Changes                                           |

|------|---------|---------------------------------------------------------------|

| 2    | 06/2012 | This is the first publicly released version of this document. |