Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XE

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, IrDA, LINbus, UART/USART                                 |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 6K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 4x10b, 4x24b                                                                |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10nledfb-50 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

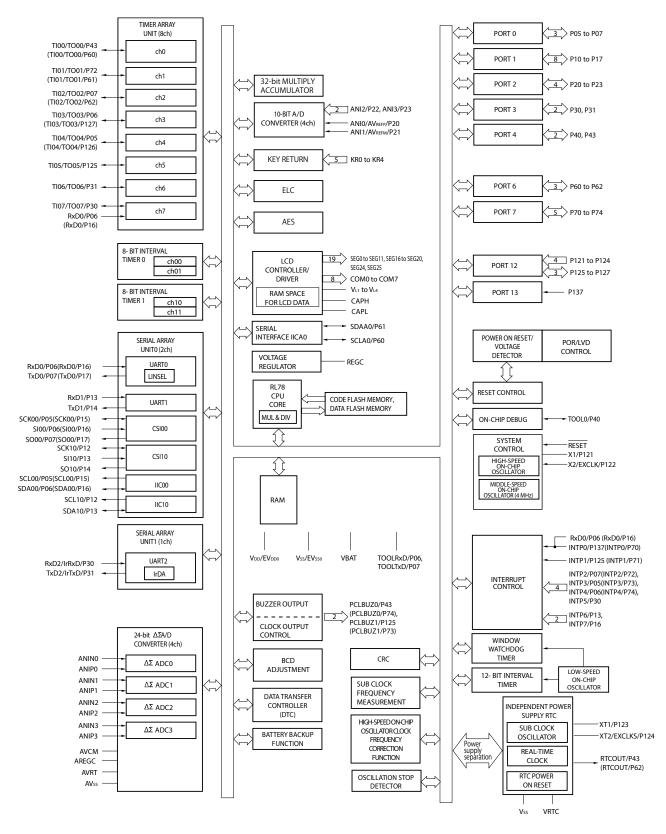

# 1.5 Block Diagram

#### 1.5.1 64-pin products

**Remark** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR0). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR0).

RENESAS

#### 2.3 Connection of Unused Pins

Table 2-3 shows the connections of unused pins.

Remark The pins mounted depend on the product. See 1.3 Pin Configuration (Top View) and 2.1 Port Function List.

| Table 2-3. | Connection of Unused Pins (1/2) |

|------------|---------------------------------|

|------------|---------------------------------|

| Pin Name   | I/O | Recommended Connection of Unused Pins                                                                                                                                                                                                                                                                             |

|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P02 to P07 | I/O | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                                                     |

| P10 to P17 |     | <pre><when i="" o="" port="" setting="" to=""> Input: Independently connect to EV<sub>DD0</sub> or EV<sub>SS0</sub> via a resistor. Output: Leave open. <when output="" segment="" setting="" to=""> Leave open.</when></when></pre>                                                                              |

| P20 to P25 |     | <ul> <li>Input: Independently connect to V<sub>DD</sub> or V<sub>SS</sub> via a resistor. In addition, individually connect to V<sub>SS</sub> via a resistor when using a battery backup function.</li> <li>Output: Leave open.</li> </ul>                                                                        |

| P30 to P37 |     | <when i="" o="" port="" setting="" to="">Input:Independently connect to EV<sub>DD0</sub> or EV<sub>SS0</sub> via a resistor.Output:Leave open.<when output="" segment="" setting="" to="">Leave open.</when></when>                                                                                               |

| P40/TOOL0  |     | Input: Independently connect to EV <sub>DD0</sub> via a resistor or leave open.<br>Output: Leave open.                                                                                                                                                                                                            |

| P41 to P43 |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                                                     |

| P50 to P57 |     | <when i="" o="" port="" setting="" to=""> Input: Independently connect to EV<sub>DD0</sub> or EV<sub>SS0</sub> via a resistor. Output: Leave open. <when output="" segment="" setting="" to=""> Leave open.</when></when>                                                                                         |

| P60 to P62 |     | Input:         Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.           Output:         Set the port's output latch to 0 and leave the pin open, or set the port's output latch to 1 and independently connect the pin to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor. |

Remark For the products that do not have an EVDD0 or EVSS0 pin, replace EVDD0 with VDD, and replace EVSS0 with VSS.

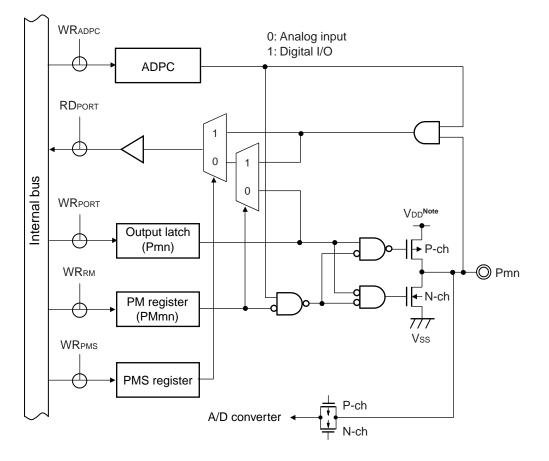

Figure 2-4. Pin Block Diagram for Pin Type 4-3-3

Note Either  $V_{DD}$  or  $V_{BAT}$  selected by the battery backup function.

# 6.3.9 Peripheral enable registers 0, 1, 2 (PER0, PER1, PER2)

These registers are used to enable or disable supplying the clock to the peripheral hardware. Clock supply to the hardware that is not used is also stopped so as to decrease the power consumption and noise. To use the peripheral functions below, which are controlled by these registers, set (1) the bit corresponding to each function before specifying the initial settings of the peripheral functions.

- Timer array unit

- Serial array unit 0

- Serial array unit 1

- Serial interface IICA0

- 10-bit A/D converter

- IrDA

- 24-bit  $\Delta\Sigma$  A/D converter

- DTC

- Frequency measurement circuit

- Independent power supply real-time clock

- 32-bit multiplier and accumulator

- Oscillation stop detection circuit

- 12-bit interval timer

The PER0, PER1, and PER2 registers can be set by a 1-bit or an 8-bit memory manipulation instruction. Reset signal generation clears these registers to 00H.

#### 8.3.8 Timer channel stop register m (TTm)

The TTm register is a trigger register that is used to stop the counting operation of each channel.

When a bit of this register is set to 1, the corresponding bit of timer channel enable status register m (TEm) is cleared to 0. The TTmn, TTHm1, TTHm3 bits are immediately cleared when operation is stopped (TEmn, TTHm1,

TTHm3 = 0), because they are trigger bits.

The TTm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the TTm register can be set with a 1-bit or 8-bit memory manipulation instruction with TTmL. Reset signal generation clears this register to 0000H.

#### Figure 8-19. Format of Timer Channel Stop register m (TTm)

| Address: F01B4H, F01B5H |    |    | After | reset: ( | 0000H | R/W |      |   |     |     |     |     |     |     |     |     |

|-------------------------|----|----|-------|----------|-------|-----|------|---|-----|-----|-----|-----|-----|-----|-----|-----|

| Symbol                  | 15 | 14 | 13    | 12       | 11    | 10  | 9    | 8 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| TTm                     | 0  | 0  | 0     | 0        | TTHm  | 0   | TTHm | 0 | TTm |

|                         |    |    |       |          | 3     |     | 1    |   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| TTH<br>m3 | Trigger to stop operation of the higher 8-bit timer when channel 3 is in the 8-bit timer mode |

|-----------|-----------------------------------------------------------------------------------------------|

| 0         | No trigger operation                                                                          |

| 1         | TEHm3 bit is cleared to 0 and the count operation is stopped.                                 |

| TT<br>m |   | Trigger to stop operation of the higher 8-bit timer when channel 1 is in the 8-bit timer mode |

|---------|---|-----------------------------------------------------------------------------------------------|

| 0       | ) | No trigger operation                                                                          |

| 1       |   | TEHm1 bit is cleared to 0 and the count operation is stopped.                                 |

| TTm | Operation stop trigger of channel n                                                                            |

|-----|----------------------------------------------------------------------------------------------------------------|

| n   |                                                                                                                |

| 0   | No trigger operation                                                                                           |

| 1   | TEmn bit clear to 0, to be count operation stop enable status.                                                 |

|     | This bit is the trigger to stop operation of the lower 8-bit timer for TTm1 and TTm3 when channel 1 or 3 is in |

|     | the 8-bit timer mode.                                                                                          |

Caution Be sure to clear bits 15 to 12, 10, 8 of the TTm register to "0".

Remarks 1. When the TTm register is read, 0 is always read.

**2.** m: Unit number (m = 0),n: Channel number (n = 0 to 7)

# **CHAPTER 12 8-BIT INTERVAL TIMER**

The 8-bit interval timer has two 8-bit timers (channel 0 and channel 1) which operate independently. These timers can be connected to operate as a 16-bit timer.

The 8-bit interval timer contains two units, 8-bit interval timer\_0 and 8-bit interval timer\_1, which have the same function. This chapter describes these units as the 8-bit interval timer unless there are differences among them.

# 12.1 Overview

The 8-bit interval timer is an 8-bit timer that operates using the fsx or fi∟ clock that is asynchronous with the CPU. Table 12 - 1 lists the 8-Bit Interval Timer Specifications and Figure 12 - 1 shows the 8-Bit Interval Timer Block Diagram.

| Item                              | Description                                                                                                                                                                                                                  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Count source<br>(operating clock) | fsx, fsx/2, fsx/4, fsx/8, fsx/16, fsx/32, fsx/64, fsx/128     fiL, fiL/2, fiL/4, fiL/16, fiL/32, fiL/64, fiL/128                                                                                                             |

| Operating mode                    | <ul> <li>8-bit counter mode</li> <li>Channel 0 and channel 1 operate independently as an 8-bit counter</li> <li>16-bit counter mode</li> <li>Channel 0 and channel 1 are connected to operate as a 16-bit counter</li> </ul> |

| Interrupt                         | Output when the counter matches the compare value                                                                                                                                                                            |

#### Table 12 - 1 8-Bit Interval Timer Specifications

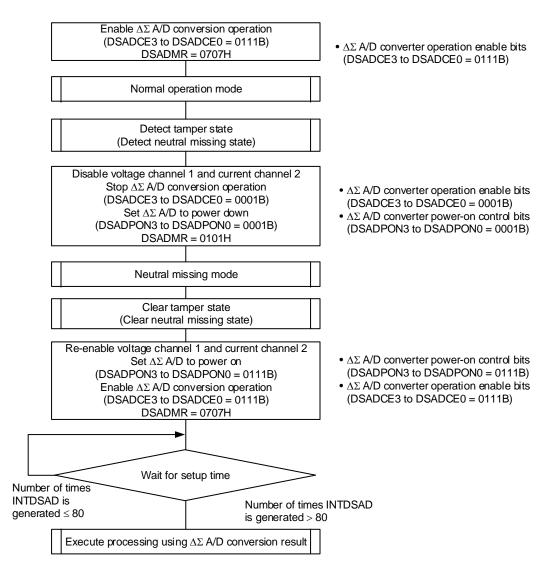

#### 17.3.2 Procedure for switching from normal operation mode to neutral missing mode

Figure 17-22 shows the procedure for switching from normal operation (with anti-tamper) (a total of three: current channel 0, voltage channel 1, and current channel 2 operate) to neutral missing mode (only current channel 0 operates), in single-phase two-wire mode.

In neutral missing mode, there are cases when only current channel 0 operates and only current channel 2 operates. Use the same procedure when switching the mode.

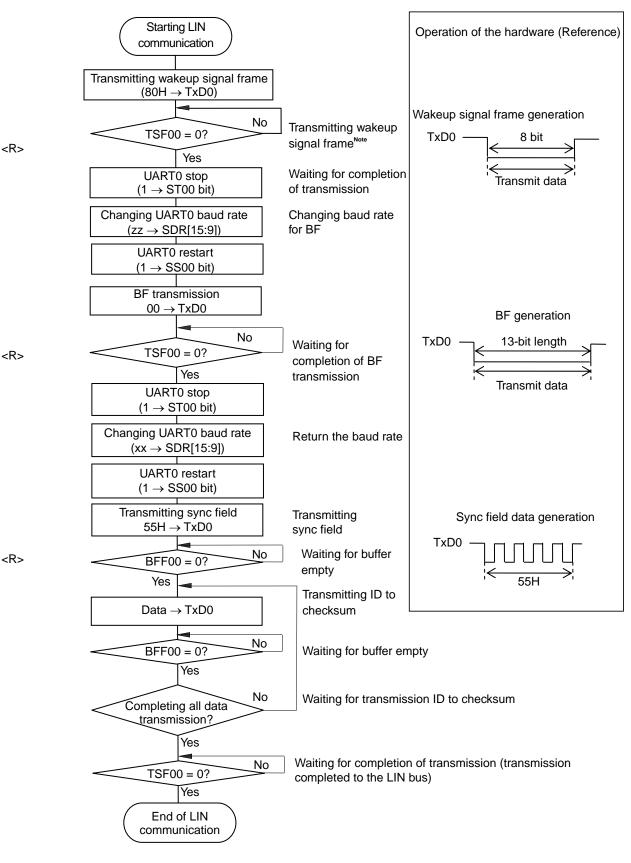

Figure 18-100. Flowchart for LIN Transmission

Note When LIN-bus start from sleep status only

Remark Default setting of the UART is complete, and the flow from the transmission enable status.

#### 19.3.6 IICA control register n1 (IICCTLn1)

This register is used to set the operation mode of I<sup>2</sup>C and detect the statuses of the SCLAn and SDAAn pins.

The IICCTLn1 register can be set by a 1-bit or 8-bit memory manipulation instruction. However, the CLDn and DADn bits are read-only.

Set the IICCTLn1 register, except the WUPn bit, while operation of I<sup>2</sup>C is disabled (bit 7 (IICEn) of IICA control register n0 (IICCTLn0) is 0).

Reset signal generation clears this register to 00H.

#### Figure 19-10. Format of IICA Control Register n1 (IICCTLn1) (1/2)

| Address: F0231H |      | After reset: 00 | OH R/W <sup>Note 1</sup> |      |      |      |   |      |   |

|-----------------|------|-----------------|--------------------------|------|------|------|---|------|---|

| Symbol          | <7>  | 6               | <5>                      | <4>  | <3>  | <2>  | 1 | <0>  | _ |

| IICCTLn1        | WUPn | 0               | CLDn                     | DADn | SMCn | DFCn | 0 | PRSn |   |

| WUPn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Control of address match wakeup                                  |                                                                                                                                                   |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Stops operation of address match wakeup function in STOP mode.   |                                                                                                                                                   |  |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Enables operation of address match wakeup function in STOP mode. |                                                                                                                                                   |  |  |  |  |  |  |  |  |

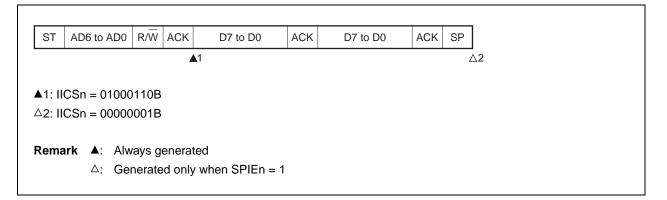

| To shift to STOP mode when WUPn = 1, execute the STOP instruction at least three clocks of fMCK after setting (1) the WUPn bit (see <b>Figure 19-23 Flow When Setting WUPn = 1</b> ).<br>Clear (0) the WUPn bit after the address has matched or an extension code has been received. The subsequent communication can be entered by the clearing (0) WUPn bit. (The wait must be released and transmit data must be written after the WUPn bit has been cleared (0).)<br>The interrupt timing when the address has matched or when an extension code has been received, while WUPn = 1, is identical to the interrupt timing when WUPn = 0. (A delay of the difference of sampling by the clock will occur.) Furthermore, when WUPn = 1, a stop condition interrupt is not generated even if the SPIEn bit is set to 1. |                                                                  |                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Condition for clearing (WUPn = 0) Condition for setting (WUPn = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |                                                                                                                                                   |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | y instruction (after address match or code reception)            | • Set by instruction (when the MSTSn, EXCn, and<br>COIn bits are "0", and the STDn bit also "0"<br>(communication not entered)) <sup>Note 2</sup> |  |  |  |  |  |  |  |  |

Notes 1. Bits 4 and 5 are read-only.

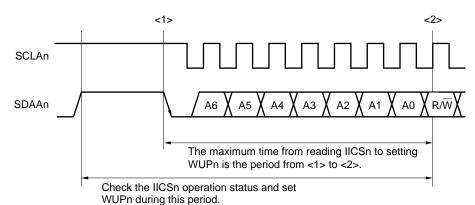

2. The status of the IICA status register n (IICSn) must be checked and the WUPn bit must be set during the period shown below.

Remark n = 0

## (ii) When WTIMn = 1

|             | 400/ 400           |          | 1.01/    |             | 1.01/ |          | 1.01/      |     |

|-------------|--------------------|----------|----------|-------------|-------|----------|------------|-----|

| ST          | AD6 to AD0         | R/W      | ACK      | D7 to D0    | ACK   | D7 to D0 | ACK        | SP  |

|             |                    |          | 1 ▲2     |             | ▲3    | 5        | <b>A</b> 4 | 4 🛆 |

|             |                    |          |          |             |       |          |            |     |

| <b>▲</b> 1: | ICSn = 0110>       | (010B    |          |             |       |          |            |     |

| ▲2:         | ICSn = 0010>       | (110B    |          |             |       |          |            |     |

| ▲3:         | ICSn = 0010>       | (100B    |          |             |       |          |            |     |

| ▲4:         | ICSn = 0010>       | ×00B     |          |             |       |          |            |     |

| ∆5:         | ICSn = 00000       | 001B     |          |             |       |          |            |     |

|             |                    |          |          |             |       |          |            |     |

| Rem         | <b>ark ▲</b> : Alw | /ays ge  | enerated | 1           |       |          |            |     |

|             | ∆: Ge              | nerated  | d only w | hen SPIEn = | 1     |          |            |     |

|             | ×: Do              | n't care | e        |             |       |          |            |     |

|             |                    |          |          |             |       |          |            |     |

#### (6) Operation when arbitration loss occurs (no communication after arbitration loss)

When the device is used as a master in a multi-master system, read the MSTSn bit each time interrupt request signal INTIICAn has occurred to check the arbitration result.

#### (a) When arbitration loss occurs during transmission of slave address data (when WTIMn = 1)

Remark n = 0

#### 20.3.3 Reception

In reception, the IR frame data is converted to the UART frame data through the IrDA and is input to the SAU.

Low-level data is output when the IRRXINV bit is 0 and a high-level pulse is detected, and high-level data is output when no pulse is detected for 1-bit period. Note that a pulse shorter than 1.41  $\mu$ s, which is the minimum pulse width, is identified as a low signal.

#### 20.3.4 Selecting high-level pulse width

When the pulse width should be shorter than the bit rate  $\times$  3/16 for transmission, applicable IRCKS2 to IRCKS0 bit settings (minimum pulse width) and the corresponding high-level pulse widths shown in Table 20-4 can be used.

| fcьк<br>[MHz] | Item                              | <upper row=""> Bit Rate [kbps]<br/><lower row=""> Bit Rate × 3/16 [μs]</lower></upper> |       |      |         |         |                       |  |  |  |  |

|---------------|-----------------------------------|----------------------------------------------------------------------------------------|-------|------|---------|---------|-----------------------|--|--|--|--|

|               |                                   | 2.4                                                                                    | 9.6   | 19.2 | 38.4    | 57.6    | 115.2                 |  |  |  |  |

|               |                                   | 78.13                                                                                  | 19.53 | 9.77 | 4.87    | 3.26    | 1.63                  |  |  |  |  |

| 1             | IRCKS2 to IRCKS0                  | 001                                                                                    | 001   | 001  | _Note 1 | Note 1  | Note 1                |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.00                                                                                   | 2.00  | 2.00 | _Note 1 | _Note 1 | _Note 1               |  |  |  |  |

| 2             | IRCKS2 to IRCKS0                  | 010                                                                                    | 010   | 010  | 010     | 010     | _Note 1               |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.00                                                                                   | 2.00  | 2.00 | 2.00    | 2.00    | _Note 1               |  |  |  |  |

| 3             | IRCKS2 to IRCKS0                  | 011                                                                                    | 011   | 011  | 011     | 011     | Note 1                |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.67                                                                                   | 2.67  | 2.67 | 2.67    | 2.67    | _Note 1               |  |  |  |  |

| 4             | IRCKS2 to IRCKS0                  | 011                                                                                    | 011   | 011  | 011     | 011     | 000 <sup>Note 2</sup> |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.00                                                                                   | 2.00  | 2.00 | 2.00    | 2.00    | 1.50                  |  |  |  |  |

| 6             | IRCKS2 to IRCKS0                  | 100                                                                                    | 100   | 100  | 100     | 100     | 000 <sup>Note 2</sup> |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.67                                                                                   | 2.67  | 2.67 | 2.67    | 2.67    | 1.50                  |  |  |  |  |

| 8             | IRCKS2 to IRCKS0                  | 100                                                                                    | 100   | 100  | 100     | 100     | 000 <sup>Note 2</sup> |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.00                                                                                   | 2.00  | 2.00 | 2.00    | 2.00    | 1.50                  |  |  |  |  |

| 12            | IRCKS2 to IRCKS0                  | 101                                                                                    | 101   | 101  | 101     | 101     | 000 <sup>Note 2</sup> |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.67                                                                                   | 2.67  | 2.67 | 2.67    | 2.67    | 1.50                  |  |  |  |  |

| 16            | IRCKS2 to IRCKS0                  | 101                                                                                    | 101   | 101  | 101     | 101     | 000 <sup>Note 2</sup> |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.00                                                                                   | 2.00  | 2.00 | 2.00    | 2.00    | 1.50                  |  |  |  |  |

| 24            | IRCKS2 to IRCKS0                  | 110                                                                                    | 110   | 110  | 110     | 110     | 000 <sup>Note 2</sup> |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.67                                                                                   | 2.67  | 2.67 | 2.67    | 2.67    | 1.50                  |  |  |  |  |

| 32            | IRCKS2 to IRCKS0                  | 110                                                                                    | 110   | 110  | 110     | 110     | 000 <sup>Note 2</sup> |  |  |  |  |

|               | High-level pulse width [ $\mu$ s] | 2.00                                                                                   | 2.00  | 2.00 | 2.00    | 2.00    | 1.50                  |  |  |  |  |

Table 20-4. IRCKS2 to IRCKS0 Bit Settings

Notes 1. "-" indicates that the communication specification cannot be satisfied.

**2.** The pulse width cannot be shorter than the bit rate  $\times$  3/16.

| Address | : FFF40H At | fter reset: 00H | R/W                             |                 |       |       |       |       |  |

|---------|-------------|-----------------|---------------------------------|-----------------|-------|-------|-------|-------|--|

| Symbol  | 7           | 6               | 5                               | 4               | 3     | 2     | 1     | 0     |  |

| LCDM0   | MDSET1      | MDSET0          | LWAVE                           | LDTY2           | LDTY1 | LDTY0 | LBAS1 | LBAS0 |  |

|         |             |                 |                                 |                 |       |       |       |       |  |

|         | LBAS1       | LBAS0           | LCD display bias mode selection |                 |       |       |       |       |  |

|         | 0           | 0               | 1/2 bias meth                   | 1/2 bias method |       |       |       |       |  |

|         | 0           | 1               | 1/3 bias method                 |                 |       |       |       |       |  |

|         | 1           | 0               | 1/4 bias method                 |                 |       |       |       |       |  |

|         | 1           | 1               | Setting prohibited              |                 |       |       |       |       |  |

## Figure 21-2. Format of LCD Mode Register 0 (LCDM0) (2/2)

Cautions 1. Do not rewrite the LCDM0 value while the SCOC bit of the LCDM1 register = 1.

- 2. When "Static" is selected (LDTY2 to LDTY0 bits = 000B), be sure to set the LBAS1 and LBAS0 bits to the default value (00B). Otherwise, the operation will not be guaranteed.

- 3. Only the combinations of display waveform, number of time slices, and bias method shown in Table 21-4 are supported.

Combinations of settings not shown in Table 21-4 are prohibited.

| Display Mode        |                             |              | Set Value |       |       |       |       |       | Driving Voltage Generation Method  |                                 |                     |  |

|---------------------|-----------------------------|--------------|-----------|-------|-------|-------|-------|-------|------------------------------------|---------------------------------|---------------------|--|

| Display<br>Waveform | Number<br>of Time<br>Slices | Bias<br>Mode | LWAVE     | LDTY2 | LDTY1 | LDTY0 | LBAS1 | LBAS0 | External<br>Resistance<br>Division | Internal<br>Voltage<br>Boosting | Capacitor Split     |  |

| Waveform A          | 8                           | 1/4          | 0         | 1     | 0     | 1     | 1     | 0     | ○<br>(24 to 128 Hz)                | ○<br>(24 to 64 Hz)              | ×                   |  |

| Waveform A          | 6                           | 1/4          | 0         | 1     | 0     | 0     | 1     | 0     | ×                                  | ○<br>(32 to 86 Hz)              | ×                   |  |

| Waveform A          | 8                           | 1/3          | 0         | 1     | 0     | 1     | 0     | 1     | ○<br>(32 to 128 Hz)                | ○<br>(32 to 64 Hz)              | ○<br>(32 to 128 Hz) |  |

| Waveform A          | 6                           | 1/3          | 0         | 1     | 0     | 0     | 0     | 1     | ○<br>(32 to 128 Hz)                | ○<br>(32 to 86 Hz)              | ○<br>(32 to 128 Hz) |  |

| Waveform A          | 4                           | 1/3          | 0         | 0     | 1     | 1     | 0     | 1     | ○<br>(24 to 128 Hz)                | ○<br>(24 to 128 Hz)             | ○<br>(24 to 128 Hz) |  |

| Waveform A          | 3                           | 1/3          | 0         | 0     | 1     | 0     | 0     | 1     | ○<br>(32 to 128 Hz)                | ○<br>(32 to 128 Hz)             | ○<br>(32 to 128 Hz) |  |

| Waveform A          | 3                           | 1/2          | 0         | 0     | 1     | 0     | 0     | 0     | ○<br>(32 to 128 Hz)                | ×                               | ×                   |  |

| Waveform A          | 2                           | 1/2          | 0         | 0     | 0     | 1     | 0     | 0     | (24 to 128 Hz)                     | ×                               | ×                   |  |

| Waveform A          | Sta                         | ıtic         | 0         | 0     | 0     | 0     | 0     | 0     | ○<br>(24 to 128 Hz)                | ×                               | ×                   |  |

| Waveform B          | 8                           | 1/4          | 1         | 1     | 0     | 1     | 1     | 0     | ○<br>(24 to 128 Hz)                | ○<br>(24 to 64 Hz)              | ×                   |  |

| Waveform B          | 8                           | 1/3          | 1         | 1     | 0     | 1     | 0     | 1     | ○<br>(32 to 128 Hz)                | ○<br>(32 to 64 Hz)              | ⊖<br>(32 to 128 Hz) |  |

| Waveform B          | 6                           | 1/3          | 1         | 1     | 0     | 0     | 0     | 1     | ⊖<br>(32 to 128 Hz)                | ⊖<br>(32 to 86 Hz)              | ○<br>(32 to 128 Hz) |  |

| Waveform B          | 4                           | 1/3          | 1         | 0     | 1     | 1     | 0     | 1     | ○<br>(24 to 128 Hz)                | ○<br>(24 to 128 Hz)             | ○<br>(24 to 128 Hz) |  |

| Waveform B          | 3                           | 1/3          | 1         | 0     | 1     | 0     | 0     | 1     | ○<br>(32 to 128 Hz)                | ○<br>(32 to 128 Hz)             | ⊖<br>(32 to 128 Hz) |  |

Remark O: Supported

×: Not supported

# 24.3.4 External interrupt rising edge enable register (EGP0, EGP1), External interrupt falling edge enable register (EGN0, EGN1)

These registers specify the valid edge for INTP0 to INTP7 and RTCIC0 to RTCIC2.

The EGP0, EGP1, EGN0 and EGN1 registers can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears these registers to 00H.

# Figure 24-5. Format of External Interrupt Rising Edge Enable Register (EGP0, EGP1) and External Interrupt Falling Edge Enable Register (EGN0, EGN1)

| Address: FFF38H After reset: 00H R/W |            |            |       |       |      |      |      |      |  |  |

|--------------------------------------|------------|------------|-------|-------|------|------|------|------|--|--|

| Symbol                               | 7          | 6          | 5     | 4     | 3    | 2    | 1    | 0    |  |  |

| EGP0                                 | EGP7       | EGP6       | EGP5  | EGP4  | EGP3 | EGP2 | EGP1 | EGP0 |  |  |

|                                      |            |            |       |       |      |      |      |      |  |  |

| Address: FFF39H After reset: 00H R/W |            |            |       |       |      |      |      |      |  |  |

| Symbol                               | 7          | 6          | 5     | 4     | 3    | 2    | 1    | 0    |  |  |

| EGN0                                 | EGN7       | EGN6       | EGN5  | EGN4  | EGN3 | EGN2 | EGN1 | EGN0 |  |  |

|                                      |            |            |       |       |      |      |      |      |  |  |

| Address: FF                          | F3AH After | reset: 00H | R/W   |       |      |      |      |      |  |  |

| Symbol                               | 7          | 6          | 5     | 4     | 3    | 2    | 1    | 0    |  |  |

| EGP1                                 | 0          | EGP14      | EGP13 | EGP12 | 0    | 0    | 0    | 0    |  |  |

|                                      |            |            |       |       |      |      |      |      |  |  |

| Address: FFF3BH After reset: 00H R/W |            |            |       |       |      |      |      |      |  |  |

| Symbol                               | 7          | 6          | 5     | 4     | 3    | 2    | 1    | 0    |  |  |

| EGN1                                 | 0          | EGN14      | EGN13 | EGN12 | 0    | 0    | 0    | 0    |  |  |

|                                      |            |            |       |       |      |      |      |      |  |  |

<R>

| EGPn | EGNn | INTP0 to INTP7 and RTCIC0 to RTCIC2 pin valid edge selection $(n = 0 \text{ to } 7, 12 \text{ to } 14)$ |  |  |  |  |

|------|------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0    | 0    | dge detection disabled                                                                                  |  |  |  |  |

| 0    | 1    | Falling edge                                                                                            |  |  |  |  |

| 1    | 0    | Rising edge                                                                                             |  |  |  |  |

| 1    | 1    | Both rising and falling edges                                                                           |  |  |  |  |

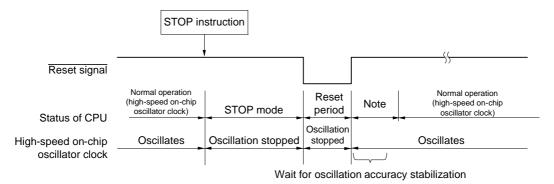

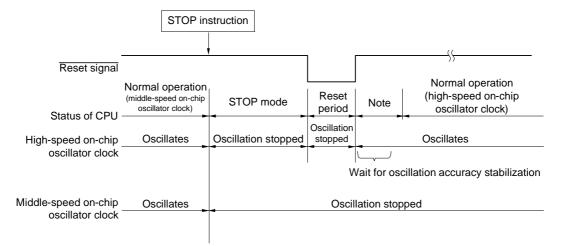

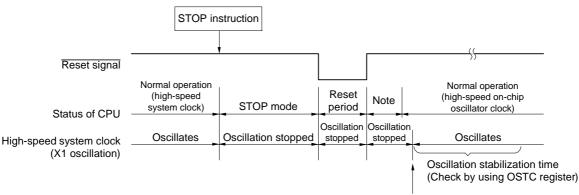

(b) Release by reset signal generation

When the reset signal is generated, STOP mode is released, and then, as in the case with a normal reset operation, the program is executed after branching to the reset vector address.

(1) When high-speed on-chip oscillator clock is used as CPU clock

(2) When middle-speed on-chip oscillator clock is used as CPU clock

(3) When high-speed system clock is used as CPU clock

Starting X1 oscillation is specified by software.

Note

For the reset processing time, see CHAPTER 27 RESET FUNCTION.

For the reset processing time of the power-on-reset circuit (POR) and voltage detector (LVD), see CHAPTER 28

POWER-ON-RESET CIRCUIT.

RENESAS

|                                | Item                                            | When operating CPU with the power of VDD pin supplied | When operating CPU with the<br>power of VBAT pin supplied                                                                          |  |  |  |

|--------------------------------|-------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LCD controller/driver          |                                                 | Operable                                              |                                                                                                                                    |  |  |  |

| Data transfer controller (DT   | C)                                              |                                                       |                                                                                                                                    |  |  |  |

| Event link controller (ELC)    |                                                 |                                                       |                                                                                                                                    |  |  |  |

| Power-on-reset function        |                                                 | Continuous operation                                  |                                                                                                                                    |  |  |  |

| RTC power-on-reset function    | n                                               | Continuous operation                                  |                                                                                                                                    |  |  |  |

| Voltage detection function     | Internal power supply voltage<br>(Internal VDD) |                                                       |                                                                                                                                    |  |  |  |

|                                | VDD, VBAT, VRTC, EXLVD<br>Pin voltage           | Operable                                              |                                                                                                                                    |  |  |  |

| External interrupt             | INTP0                                           | Operable                                              |                                                                                                                                    |  |  |  |

|                                | INTP1 to INTP7                                  | Operable                                              | Operable when the power of<br>EVDD pin is supplied <sup>Note 2</sup> .<br>Not operable when the power of<br>EVDD pin is shut down. |  |  |  |

|                                | RTCIC0 to RTCIC2                                | Operable                                              |                                                                                                                                    |  |  |  |

| Key interrupt input            |                                                 | Operable                                              |                                                                                                                                    |  |  |  |

| CRC operation function         |                                                 |                                                       |                                                                                                                                    |  |  |  |

| 32-bit multiplier and multiply | /accumulator                                    |                                                       |                                                                                                                                    |  |  |  |

| RAM parity error detection f   | function                                        | 1                                                     |                                                                                                                                    |  |  |  |

| RAM guard function             |                                                 | 1                                                     |                                                                                                                                    |  |  |  |

| SFR guard function             |                                                 | 1                                                     |                                                                                                                                    |  |  |  |

| Illegal-memory access dete     | ction function                                  | 1                                                     |                                                                                                                                    |  |  |  |

| AES function                   |                                                 | 1                                                     |                                                                                                                                    |  |  |  |

Table 30-1. Peripheral Circuit Operation State during Battery Backup (2/2)

**Notes 1.** The self-programming function cannot be used.

- 2. When supplying the power from outside to the EVDD pin, it is recommended to backup the VDD and VBAT pins or the VRTC pin with the diode ORing.

- 3. When the power of EVDD is not supplied, set GDIDISO to 1.

- 4. The  $\Delta\Sigma$  A/D converter operable in the backup mode is limited up to 3 channels.

- 5. RTCIC0, RTCIC1, and RTCIC2 pins are included.

- 6. When power supply switching by the battery backup function occurs, access to the data flash memory is prohibited.

- The power is supplied from the V<sub>DD</sub> pin at startup of the power supply. MCU remains reset even when the power is supplied to the VBAT pin earlier than the V<sub>DD</sub> pin.

- The battery backup function is stopped by default. The battery backup mode must be set by the software after startup of the power supply.

- If the V<sub>DD</sub> pin voltage is lower than the detection voltage, the internal power and the power supply for ΔΣ A/D converter can be switched from the V<sub>DD</sub> supply to the VBAT supply. When the V<sub>DD</sub> pin voltage is recovered higher than the detection voltage, the internal power and the power supply for ΔΣ A/D converter can be switched from the VBAT supply to the V<sub>DD</sub> supply.

- Under the condition of VBAT  $\geq$  V<sub>DD</sub>, the software enables to switch the internal power and the power supply for  $\Delta\Sigma$ A/D converter from the VBAT supply to the V<sub>DD</sub> supply.

<R>

<R>

| Operation Mode                        | Multiplication Result Register Name |               |               |              |  |  |

|---------------------------------------|-------------------------------------|---------------|---------------|--------------|--|--|

|                                       | Bits 63 to 48                       | Bits 47 to 32 | Bits 31 to 16 | Bits 15 to 0 |  |  |

| Multiplication mode (unsigned)        | MULR3                               | MULR2         | MULR1         | MULR0        |  |  |

| Multiplication mode (signed)          |                                     |               |               |              |  |  |

| Multiply-accumulation mode (unsigned) |                                     |               |               |              |  |  |

| Multiply-accumulation mode (signed)   |                                     |               |               |              |  |  |

Table 39-4. Relationship between Operation Mode and Register Name

The operation result (multiplication) is stored for the multiplication, and the operation result (accumulation) is stored for the multiply-accumulation. Additionally, the accumulation initial value can be set for the multiply-accumulation.

Table 39-5. Details of Storing of Operation Modes and Multiplication Result Registers

| Operation Mode                        | Setting                               | Operation Result              |  |  |

|---------------------------------------|---------------------------------------|-------------------------------|--|--|

| Multiplication mode (unsigned)        | _                                     | MULR3 to MULR0:               |  |  |

|                                       |                                       | Multiplication (unsigned)     |  |  |

| Multiplication mode (signed)          | _                                     | MULR3 to MULR0:               |  |  |

|                                       |                                       | Multiplication (signed)       |  |  |

| Multiply-accumulation mode (unsigned) | MULR3 to MULR0:                       | MULR3 to MULR0:               |  |  |

|                                       | Accumulation initial value (unsigned) | Accumulation value (unsigned) |  |  |

| Multiply-accumulation mode (signed)   | MULR3 to MULR0:                       | MULR3 to MULR0:               |  |  |

|                                       | Accumulation initial value (signed)   | Accumulation value (signed)   |  |  |

If exceeding the maximum value of the value range that can be handled in 64 bit (= overflow), or if dropping below the minimum value (= underflow), the value is reversed, and the values plus overflow/underflow values are stored in the MULR3 to MULR0 registers.

```

Unsigned

```

```

In case of overflow

```

Processing) 2<sup>64</sup> + MULR[63:0]

```

Example)

```

```

Signed

```

- In case of overflow

- Processing) 2<sup>63</sup> + MULR[62:0]

```

Example)

```

• In case of underflow Processing) -2<sup>63</sup> + MULR[62:0]

```

Example)

```

| Instruction | Mnemonic | Operands        | Bytes | Clocks |        | Clocks                                                |   | Flag | J  |

|-------------|----------|-----------------|-------|--------|--------|-------------------------------------------------------|---|------|----|

| Group       |          |                 |       | Note 1 | Note 2 |                                                       | Z | AC   | CY |

| 8-bit       | ADDC     | A, #byte        | 2     | 1      | -      | A, CY $\leftarrow$ A+byte+CY                          | × | ×    | ×  |

| operation   |          | saddr, #byte    | 3     | 2      | -      | (saddr), CY $\leftarrow$ (saddr) +byte+CY             | × | ×    | ×  |

|             |          | A, rv Note 3    | 2     | 1      | -      | A, CY $\leftarrow$ A + r + CY                         | × | ×    | ×  |

|             |          | r, A            | 2     | 1      | -      | $r, CY \leftarrow r + A + CY$                         | × | ×    | ×  |

|             |          | A, !addr16      | 3     | 1      | 4      | A, CY $\leftarrow$ A + (addr16)+CY                    | × | ×    | ×  |

|             |          | A, ES:!addr16   | 4     | 2      | 5      | A, CY $\leftarrow$ A + (ES, addr16)+CY                | × | ×    | ×  |

|             |          | A, saddr        | 2     | 1      | -      | A, CY $\leftarrow$ A + (saddr)+CY                     | × | ×    | ×  |

|             |          | A, [HL]         | 1     | 1      | 4      | A, CY $\leftarrow$ A+ (HL) + CY                       | × | ×    | ×  |

|             |          | A, ES:[HL]      | 2     | 2      | 5      | $A,CY \leftarrow A \texttt{+} (ES, HL) \texttt{+} CY$ | × | ×    | ×  |

|             |          | A, [HL+byte]    | 2     | 1      | 4      | A, CY $\leftarrow$ A+ (HL+byte) + CY                  | × | ×    | ×  |

|             |          | A, ES:[HL+byte] | 3     | 2      | 5      | $A,CY \leftarrow A+ ((ES, HL)+byte) + CY$             | × | ×    | ×  |

|             |          | A, [HL+B]       | 2     | 1      | 4      | A, CY $\leftarrow$ A+ (HL+B) +CY                      | × | ×    | ×  |

|             |          | A, ES:[HL+B]    | 3     | 2      | 5      | $A,CY \leftarrow A+((ES, HL)+B)+CY$                   | × | ×    | ×  |

|             |          | A, [HL+C]       | 2     | 1      | 4      | A, CY $\leftarrow$ A+ (HL+C)+CY                       | × | ×    | ×  |

|             |          | A, ES:[HL+C]    | 3     | 2      | 5      | $A,CY \leftarrow A+ ((ES, HL)+C)+CY$                  | × | ×    | ×  |

|             | SUB      | A, #byte        | 2     | 1      | -      | A, CY $\leftarrow$ A – byte                           | × | ×    | ×  |

|             |          | saddr, #byte    | 3     | 2      | -      | (saddr), CY $\leftarrow$ (saddr) – byte               | × | ×    | ×  |

|             |          | A, r Note 3     | 2     | 1      | -      | A, CY ← A − r                                         | × | ×    | ×  |

|             |          | r, A            | 2     | 1      | -      | r, CY ← r – A                                         | × | ×    | ×  |

|             |          | A, !addr16      | 3     | 1      | 4      | A, CY $\leftarrow$ A – (addr16)                       | × | ×    | ×  |

|             |          | A, ES:!addr16   | 4     | 2      | 5      | A, CY $\leftarrow$ A – (ES, addr16)                   | × | ×    | ×  |

|             |          | A, saddr        | 2     | 1      | -      | A, CY $\leftarrow$ A – (saddr)                        | × | ×    | ×  |

|             |          | A, [HL]         | 1     | 1      | 4      | A, CY $\leftarrow$ A – (HL)                           | × | ×    | ×  |

|             |          | A, ES:[HL]      | 2     | 2      | 5      | $A,CY \leftarrow A - (ES,HL)$                         | × | ×    | ×  |

|             |          | A, [HL+byte]    | 2     | 1      | 4      | A, CY $\leftarrow$ A – (HL+byte)                      | × | ×    | ×  |

|             |          | A, ES:[HL+byte] | 3     | 2      | 5      | $A,CY \leftarrow A - ((ES, HL)+byte)$                 | × | ×    | ×  |

|             |          | A, [HL+B]       | 2     | 1      | 4      | A, CY $\leftarrow$ A – (HL+B)                         | × | ×    | ×  |

|             |          | A, ES:[HL+B]    | 3     | 2      | 5      | $A,CY \leftarrow A - ((ES,HL){+}B)$                   | × | ×    | ×  |

|             |          | A, [HL+C]       | 2     | 1      | 4      | A, CY $\leftarrow$ A – (HL+C)                         | × | ×    | ×  |

|             |          | A, ES:[HL+C]    | 3     | 2      | 5      | $A,CY \leftarrow A - ((ES, HL)+C)$                    | × | ×    | ×  |

**Notes 1.** Number of CPU clocks (fcLk) when the internal RAM area, SFR area, or extended SFR area is accessed, or when no data is accessed.

2. Number of CPU clocks (fcLk) when the code flash area is accessed.

3. Except r = A

**Remark** Number of clock is when program exists in the internal ROM (flash memory) area. If fetching the instruction from the internal RAM area, the number becomes double number plus 3 clocks at a maximum.

| Instruction | Mnemonic | Operands        | Bytes | Clocks Note 1 Note 2 |   | Clocks                                           | Flag    |

|-------------|----------|-----------------|-------|----------------------|---|--------------------------------------------------|---------|

| Group       |          |                 |       |                      |   |                                                  | Z AC CY |

| 8-bit       | OR       | A, #byte        | 2     | 1                    | _ | $A \leftarrow A \lor byte$                       | ×       |

| operation   |          | saddr, #byte    | 3     | 2                    | _ | $(saddr) \leftarrow (saddr) \lor byte$           | ×       |

|             |          | A, r Note 3     | 2     | 1                    | - | $A \leftarrow A \lor r$                          | ×       |

|             |          | r, A            | 2     | 1                    | - | r ← r∨A                                          | ×       |

|             |          | A, !addr16      | 3     | 1                    | 4 | $A \leftarrow A_{\vee}(addr16)$                  | ×       |

|             |          | A, ES:!addr16   | 4     | 2                    | 5 | $A \leftarrow A \lor (ES:addr16)$                | ×       |

|             |          | A, saddr        | 2     | 1                    | _ | $A \leftarrow A \lor (saddr)$                    | ×       |

|             |          | A, [HL]         | 1     | 1                    | 4 | $A \leftarrow A \lor (H)$                        | ×       |

|             |          | A, ES:[HL]      | 2     | 2                    | 5 | $A \leftarrow A_{\vee}(ES;HL)$                   | ×       |

|             |          | A, [HL+byte]    | 2     | 1                    | 4 | $A \leftarrow A \lor (HL+byte)$                  | ×       |

|             |          | A, ES:[HL+byte] | 3     | 2                    | 5 | $A \leftarrow A \lor ((ES:HL)+byte)$             | ×       |

|             |          | A, [HL+B]       | 2     | 1                    | 4 | A ← A∨(HL+B)                                     | ×       |

|             |          | A, ES:[HL+B]    | 3     | 2                    | 5 | $A \leftarrow A_{\forall}((ES:HL)+B)$            | ×       |

|             |          | A, [HL+C]       | 2     | 1                    | 4 | $A \leftarrow A {\scriptstyle\lor}(HL{+}C)$      | ×       |

|             |          | A, ES:[HL+C]    | 3     | 2                    | 5 | $A \leftarrow A_{\forall}((ES:HL) \text{+} C)$   | ×       |

|             | XOR      | A, #byte        | 2     | 1                    | _ | $A \leftarrow A + byte$                          | ×       |

|             |          | saddr, #byte    | 3     | 2                    | - | $(saddr) \leftarrow (saddr) + byte$              | ×       |

|             |          | A, r Note 3     | 2     | 1                    | _ | $A \leftarrow A \not\sim r$                      | ×       |

|             |          | r, A            | 2     | 1                    | - | r ← r <del>×</del> A                             | ×       |

|             |          | A, !addr16      | 3     | 1                    | 4 | $A \leftarrow A_{\forall}(addr16)$               | ×       |

|             |          | A, ES:!addr16   | 4     | 2                    | 5 | $A \leftarrow A_{\leftrightarrow}(ES:addr16)$    | ×       |

|             |          | A, saddr        | 2     | 1                    | - | $A \leftarrow A_{\forall}(saddr)$                | ×       |

|             |          | A, [HL]         | 1     | 1                    | 4 | $A \leftarrow A_{}(HL)$                          | ×       |

|             |          | A, ES:[HL]      | 2     | 2                    | 5 | $A \leftarrow A_{+}(ES:HL)$                      | ×       |

|             |          | A, [HL+byte]    | 2     | 1                    | 4 | $A \leftarrow A_{+}(HL+byte)$                    | ×       |

|             |          | A, ES:[HL+byte] | 3     | 2                    | 5 | $A \leftarrow A_{\leftrightarrow}((ES:HL)+byte)$ | ×       |

|             |          | A, [HL+B]       | 2     | 1                    | 4 | $A \leftarrow A \not\sim (HL+B)$                 | ×       |

|             |          | A, ES:[HL+B]    | 3     | 2                    | 5 | $A \leftarrow A_{}((ES:HL) + B)$                 | ×       |

|             |          | A, [HL+C]       | 2     | 1                    | 4 | $A \leftarrow A_{}(HL+C)$                        | ×       |

|             |          | A, ES:[HL+C]    | 3     | 2                    | 5 | $A \leftarrow A \not\leftarrow ((ES:HL)+C)$      | ×       |

## Table 40-5. Operation List (9/18)

**Notes 1.** Number of CPU clocks (fcLk) when the internal RAM area, SFR area, or extended SFR area is accessed, or when no data is accessed.

2. Number of CPU clocks (fcLk) when the code flash area is accessed.

3. Except r = A

**Remark** Number of clock is when program exists in the internal ROM (flash memory) area. If fetching the instruction from the internal RAM area, the number becomes double number plus 3 clocks at a maximum.

# (5) Communication at different potential (1.9 V, 2.5 V, 3 V) (UART mode) (1/2)

| $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.9 \text{ V} \le \text{EVDD0} = \text{EVDD1} \le \text{V}$ | $DD^{Note 1} \leq 5.5 V, VSS = EVSS0 = EVSS1 = 0 V$ |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Parameter        | Symbol | Conditions |                                                                                                                               | HS (high-speed main) Mode |                          | LS (low-speed<br>main) Mode |                          | LP (low-power<br>main) Mode |                          | LV (low-voltage main) Mode |                          | Unit |

|------------------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|-----------------------------|--------------------------|-----------------------------|--------------------------|----------------------------|--------------------------|------|

|                  |        |            |                                                                                                                               | MIN.                      | MAX.                     | MIN.                        | MAX.                     | MIN.                        | MAX.                     | MIN.                       | MAX.                     |      |

| Transfer<br>rate |        | Reception  | $\begin{array}{l} 4.0 \ V \leq EV_{\text{DD}} \leq 5.5 \ V, \\ 2.7 \ V \leq V_b \leq 4.0 \ V \end{array} \label{eq:delta_bd}$ |                           | fмск∕6 <sup>№оtе 1</sup> |                             | fмск/6 <sup>Note 1</sup> |                             | fмск/6 <sup>Note 1</sup> |                            | fмск/6 <sup>Note 1</sup> | bps  |

|                  |        |            | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK}^{Note 4}$                                                   |                           | 5.3                      |                             | 1.3                      |                             | 0.1                      |                            | 0.6                      | Mbps |

|                  |        |            | $\begin{array}{l} 2.7 \ V \leq EV_{\text{DD}} < 4.0 \ V, \\ 2.3 \ V \leq V_{\text{b}} \leq 2.7 \ V \end{array}$               |                           | fмск/6 <sup>Note 1</sup> |                             | ƒмск/6 <sup>№оtе 1</sup> |                             | fмск/6 <sup>Note 1</sup> |                            | fмск/6 <sup>Note 1</sup> | bps  |

|                  |        |            | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK}^{Note 4}$                                                   |                           | 5.3                      |                             | 1.3                      |                             | 0.1                      |                            | 0.6                      | Mbps |

|                  |        |            | $\begin{array}{l} 1.9 \ V \leq EV_{\text{DD}} < 3.3 \ V, \\ 1.8 \ V \leq V_{\text{b}} \leq 2.0 \ V \end{array}$               |                           | fMCK/6<br>Notes 1 to 3   |                             | fMCK/6<br>Notes 1, 2     |                             | fMCK/6<br>Notes 1, 2     |                            | fMCK/6<br>Notes 1, 2     | bps  |

|                  |        |            | Theoretical value of<br>the maximum<br>transfer rate<br>$f_{MCK} = f_{CLK}^{Note 4}$                                          |                           | 5.3                      |                             | 1.3                      |                             | 0.1                      |                            | 0.6                      | Mbps |

Notes 1. Transfer rate in the SNOOZE mode is 4800 bps only.

**2.** Use it with  $EV_{DD} \ge V_b$ .

3. The following conditions are required for low voltage interface.  $2.4 \text{ V} \leq \text{EV}_{\text{DD}} < 2.7 \text{ V}$ : MAX. 2.6 Mbps  $1.9 \text{ V} \leq \text{EV}_{\text{DD}} < 2.4 \text{ V}$ : MAX. 1.3 Mbps

4. The maximum operating frequencies of the CPU/peripheral hardware clock (fcLk) are:

$\begin{array}{ll} \text{HS (high-speed main) mode:} & 32 \ \text{MHz} \ (2.8 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}), \ 24 \ \text{MHz} \ (2.7 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}), \\ & 16 \ \text{MHz} \ (2.5 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}), \ 12 \ \text{MHz} \ (2.4 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}), \\ & 6 \ \text{MHz} \ (2.1 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}), \ 12 \ \text{MHz} \ (2.4 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}), \\ & 6 \ \text{MHz} \ (2.1 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}), \ 3 \ \text{MHz} \ (1.9 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}), \ 4 \ \text{MHz} \ (1.9 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}) \\ & 1 \ \text{MHz} \ (1.9 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}) \\ & 1 \ \text{MHz} \ (1.9 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}) \\ & 4 \ \text{MHz} \ (1.7 \ \text{V} \leq \text{EV}_{\text{DD}} \leq 5.5 \ \text{V}) \end{array}$

- Caution Select the TTL input buffer for the RxDq pin and the N-ch open drain output (VDD tolerance) mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg). For VIH and VIL, see the DC characteristics with TTL input buffer selected.

- **Remarks 1.** V<sub>b</sub>[V]: Communication line voltage

- **2.** q: UART number (q = 0 to 3), g: PIM and POM number (g = 0, 1, 3, 5, 8)

- fMCK: Serial array unit operation clock frequency (Operating clock that is set with the serial clock select register m (SPSm) and the CKSmn bit of serial mode register mn (SMRmn).

m: Unit number, n: Channel number (mn = 00 to 03, 10 to 13))